RAMPHAsim Status Update Joel Emer Michael Adler Angshuman

- Slides: 32

RAMP/HAsim Status Update Joel Emer Michael Adler Angshuman Parashar Michael Pellauer Murali Vijayaraghavan VSSAD Group Intel joel. emer@intel. com michael. adler@intel. com angshuman. parashar@intel. com pellauer@csail. mit. edu vmurali@csail. mit. edu CSG Group, CSAIL MIT

Infrastructure Update • AWB Plug N Play – Hardware Language Support • Bluespec, VHDL, Verilog – Software Language Support • C++ • Build Procedure – Updated to scons • Automatic Parallel Build – Common data types between hardware and software • Common Platform 2

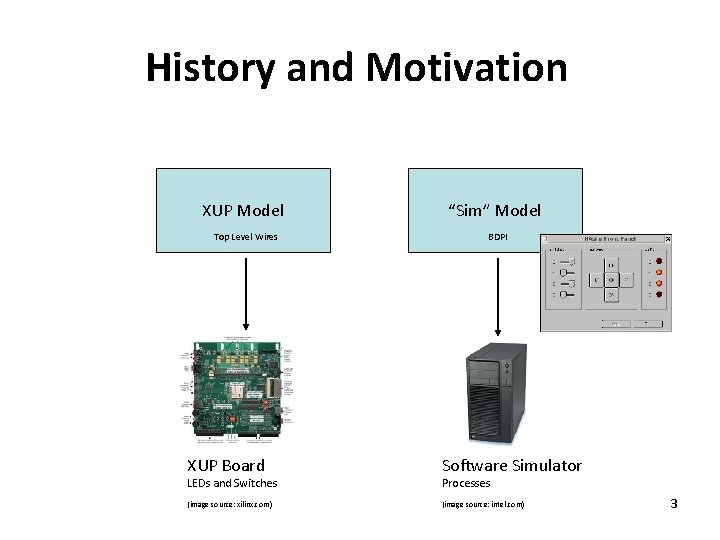

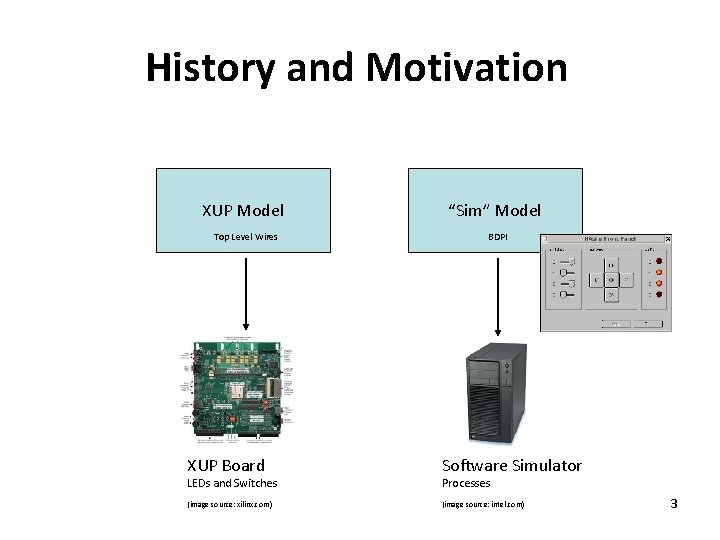

History and Motivation XUP Model Top Level Wires “Sim” Model BDPI XUP Board Software Simulator (image source: xilinx. com) (image source: intel. com) LEDs and Switches Processes 3

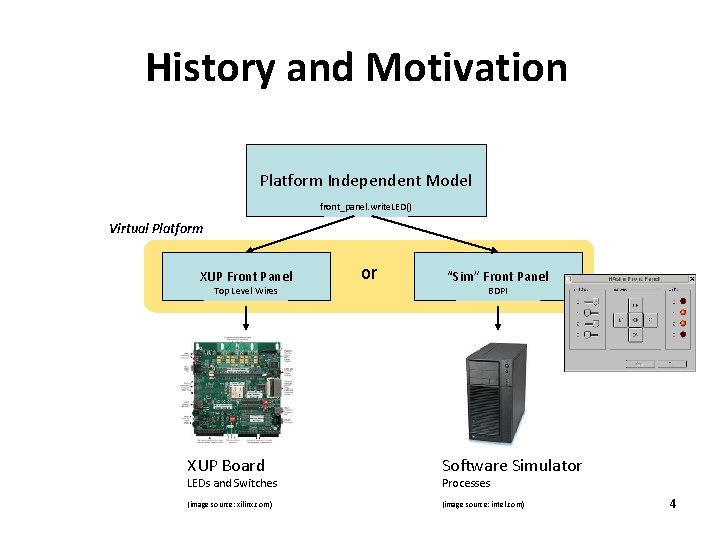

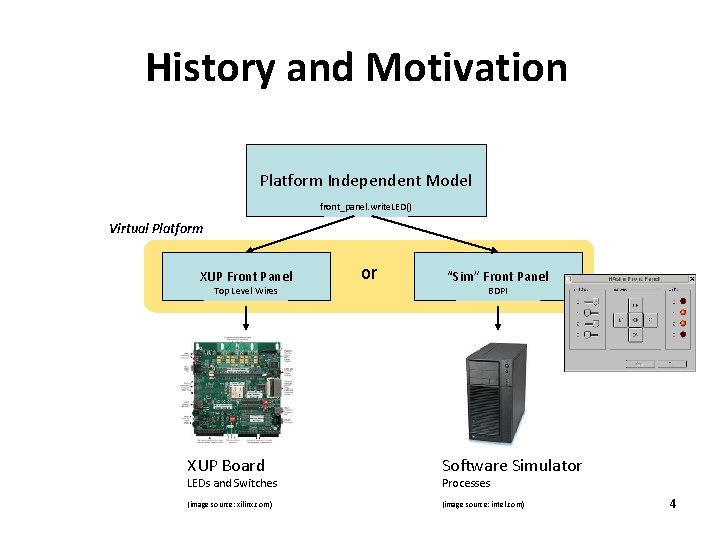

History and Motivation Platform Independent Model front_panel. write. LED() Virtual Platform XUP Front Panel Top Level Wires or “Sim” Front Panel BDPI XUP Board Software Simulator (image source: xilinx. com) (image source: intel. com) LEDs and Switches Processes 4

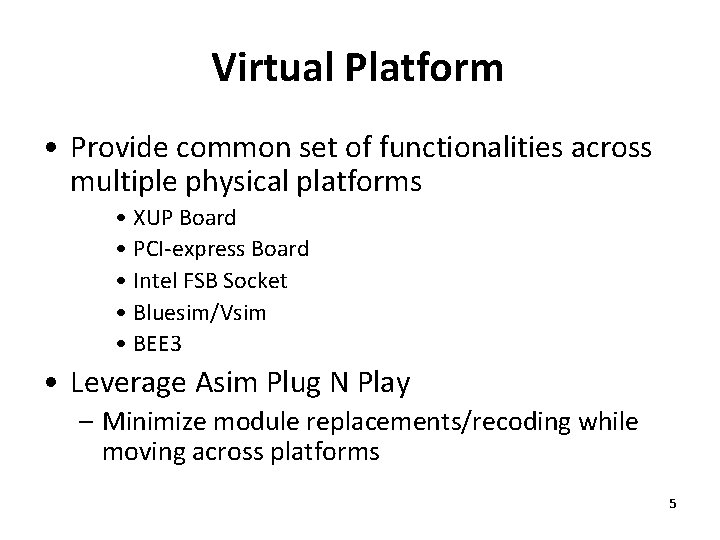

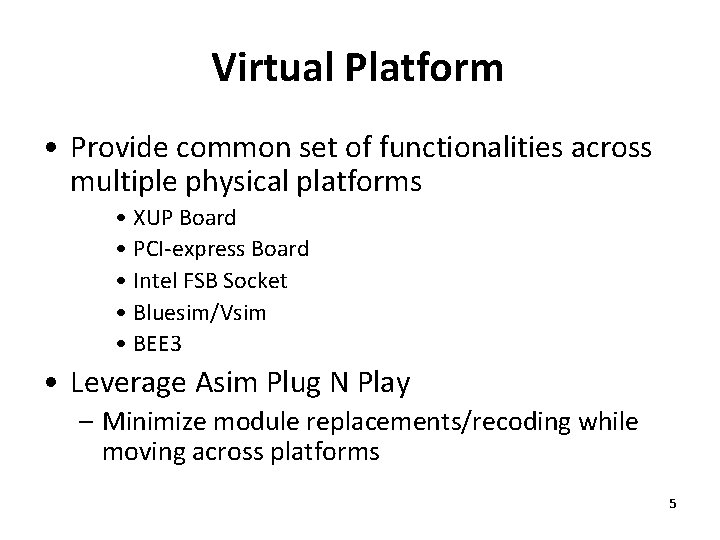

Virtual Platform • Provide common set of functionalities across multiple physical platforms • XUP Board • PCI-express Board • Intel FSB Socket • Bluesim/Vsim • BEE 3 • Leverage Asim Plug N Play – Minimize module replacements/recoding while moving across platforms 5

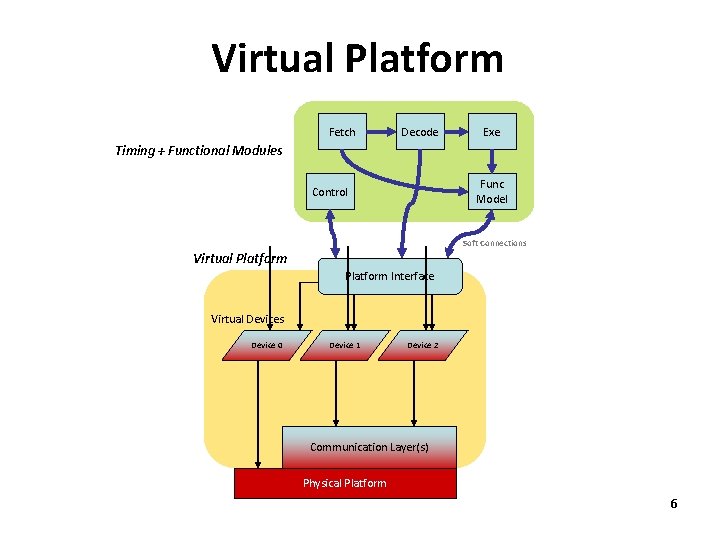

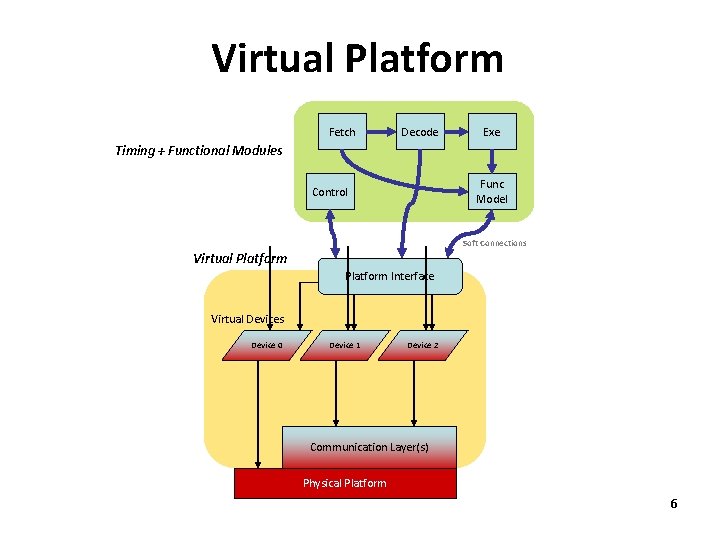

Virtual Platform Fetch Decode Exe Timing + Functional Modules Func Model Control Soft Connections Virtual Platform Interface Virtual Devices Device 0 Device 1 Device 2 Communication Layer(s) Physical Platform 6

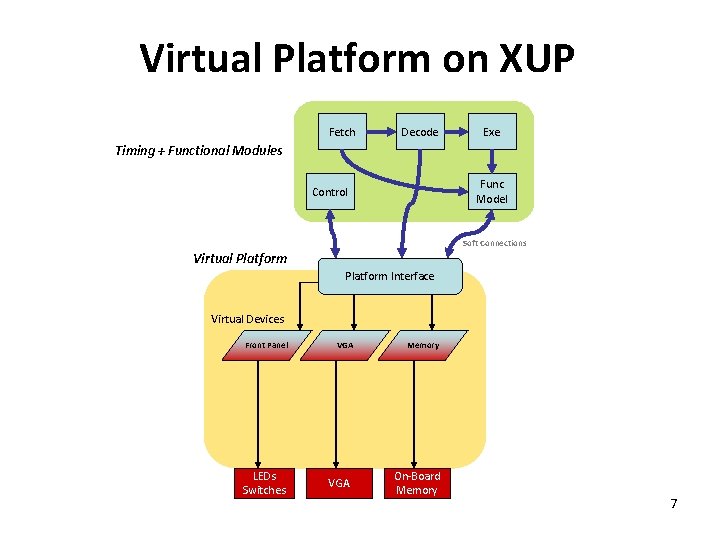

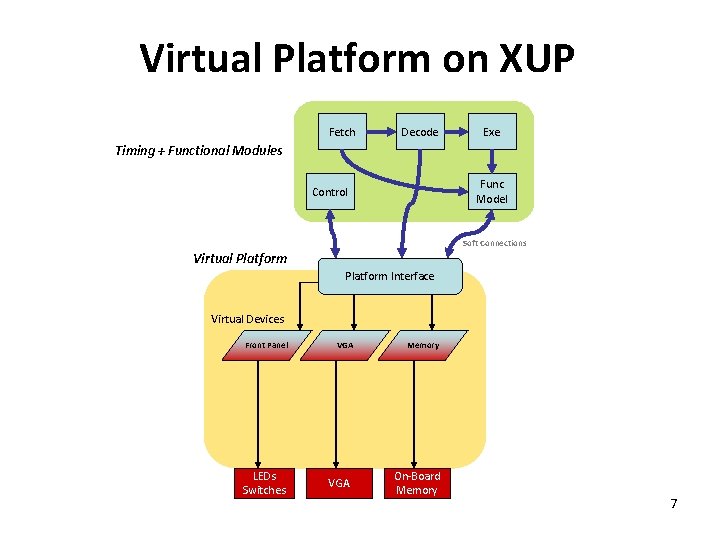

Virtual Platform on XUP Fetch Decode Exe Timing + Functional Modules Func Model Control Soft Connections Virtual Platform Interface Virtual Devices Front Panel LEDs Switches VGA Memory On-Board Memory 7

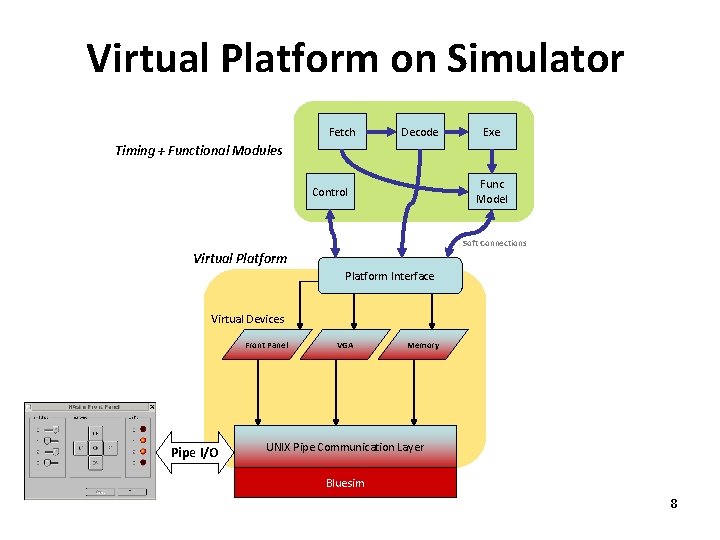

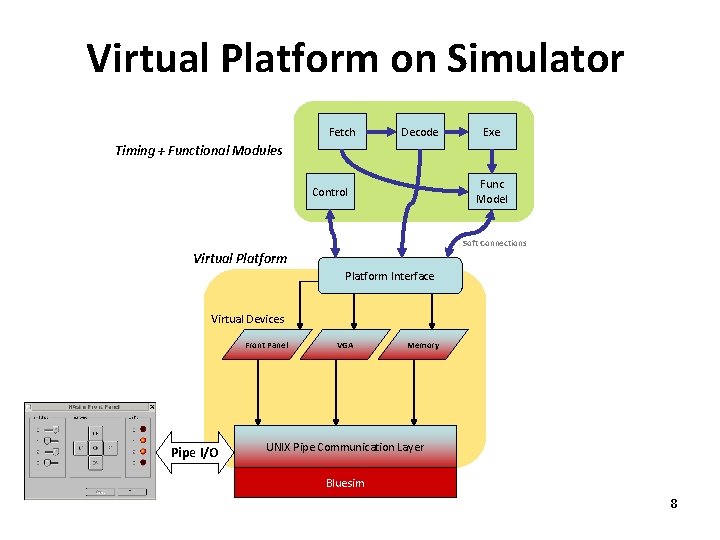

Virtual Platform on Simulator Fetch Decode Exe Timing + Functional Modules Func Model Control Soft Connections Virtual Platform Interface Virtual Devices Front Panel Pipe I/O VGA Memory UNIX Pipe Communication Layer Bluesim 8

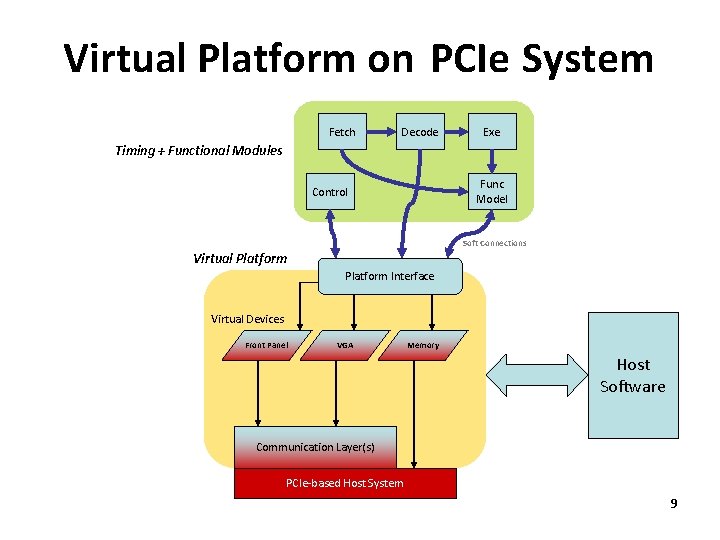

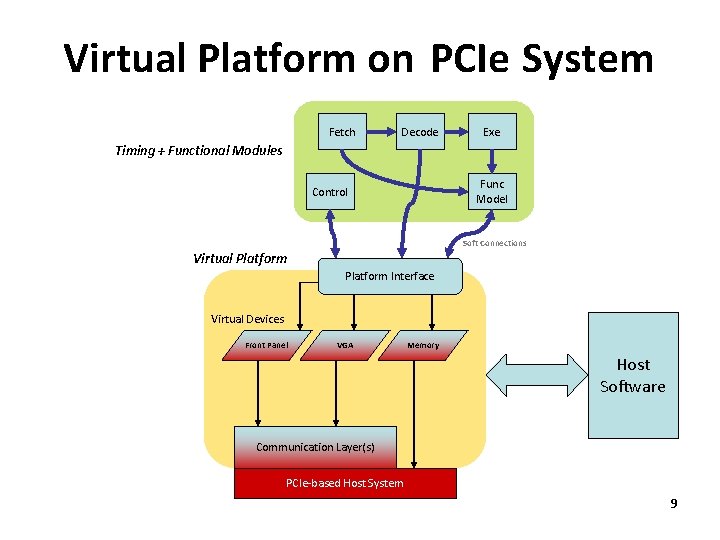

Virtual Platform on PCIe System Fetch Decode Exe Timing + Functional Modules Func Model Control Soft Connections Virtual Platform Interface Virtual Devices Front Panel VGA Memory Host Software Communication Layer(s) PCIe-based Host System 9

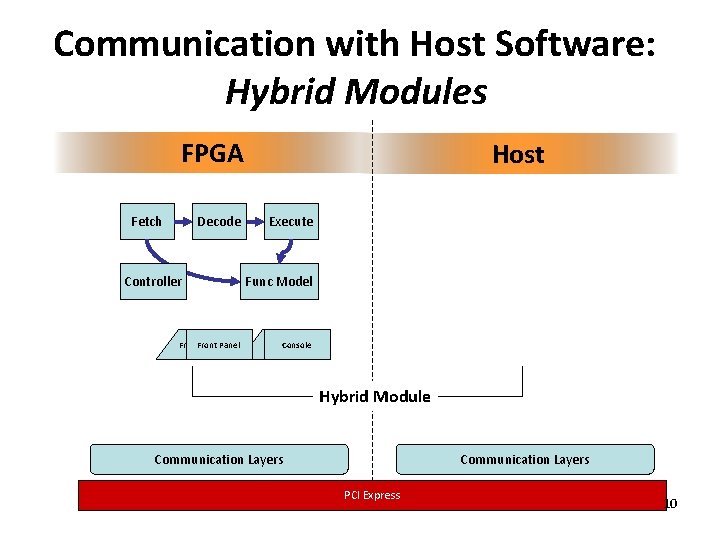

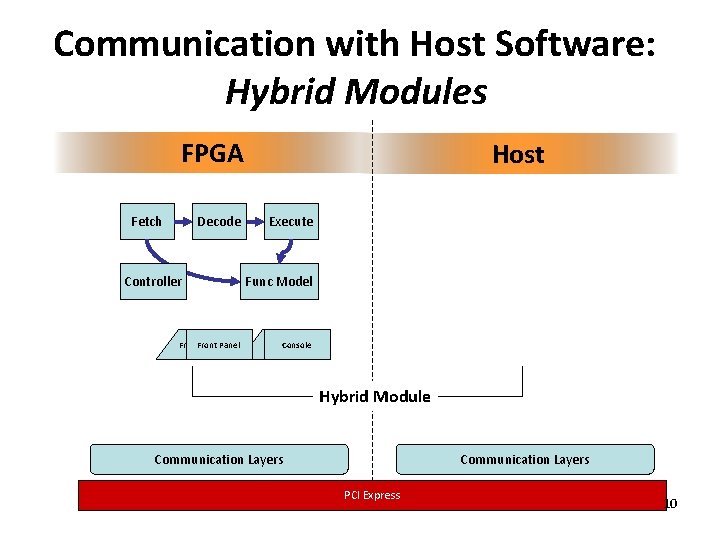

Communication with Host Software: Hybrid Modules FPGA Fetch Decode Controller Front Panel Host Execute Func Model Console Hybrid Module Communication Layers PCI Express 10

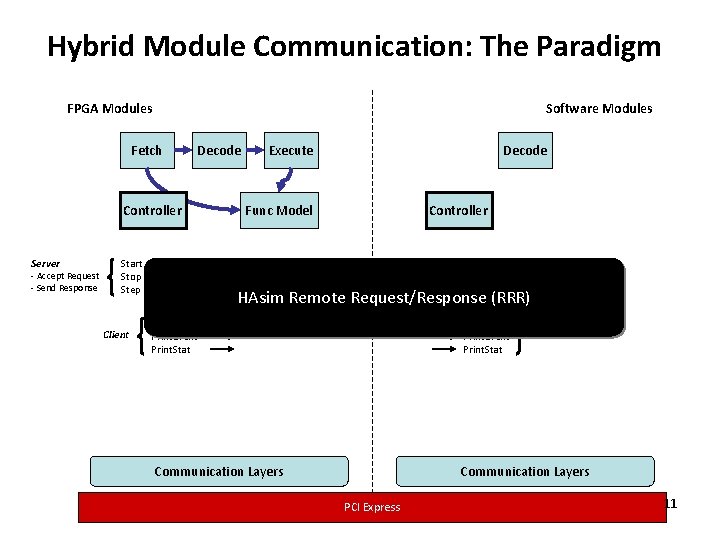

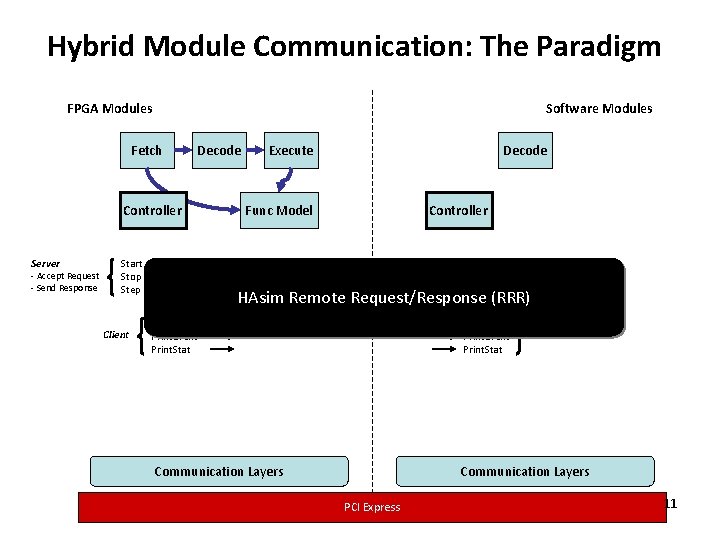

Hybrid Module Communication: The Paradigm FPGA Modules Software Modules Fetch Decode Controller Server - Accept Request - Send Response Start Stop Step Client Execute Decode Func Model Controller Start Stop Step Client - Make Request - Accept Response HAsim Remote Request/Response (RRR) Print. Assert Print. Event Print. Stat Communication Layers PCI Express Server 11

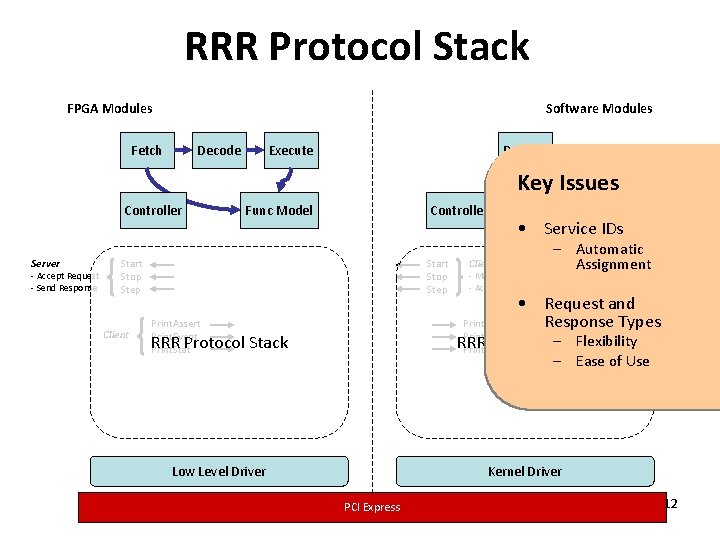

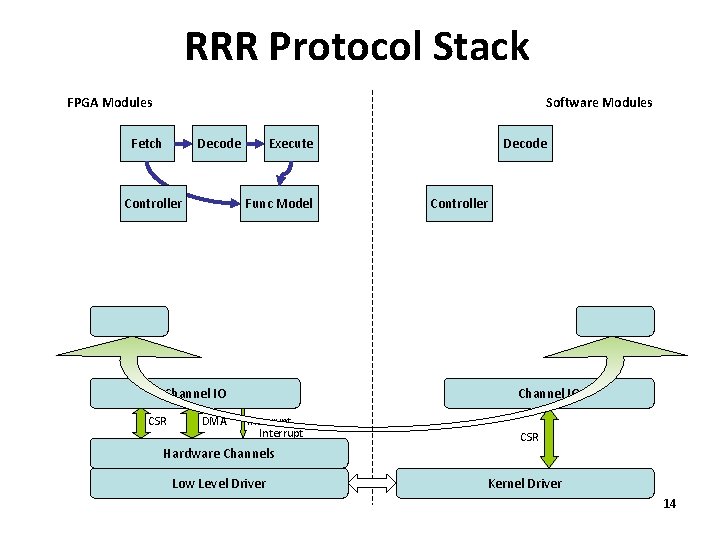

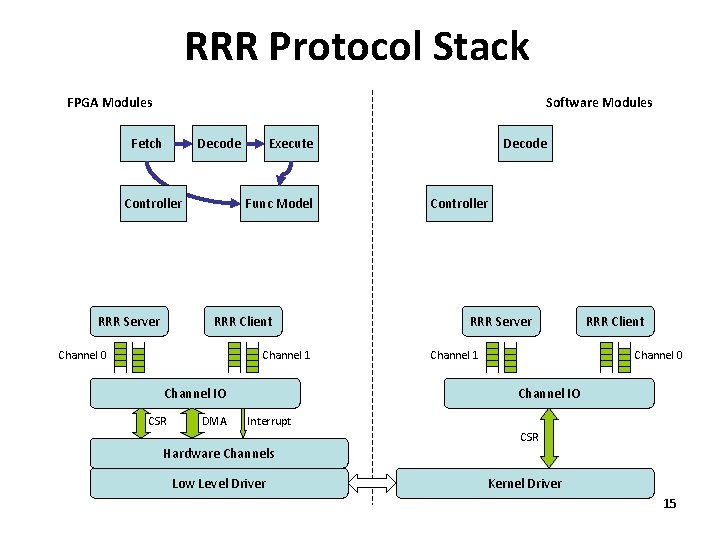

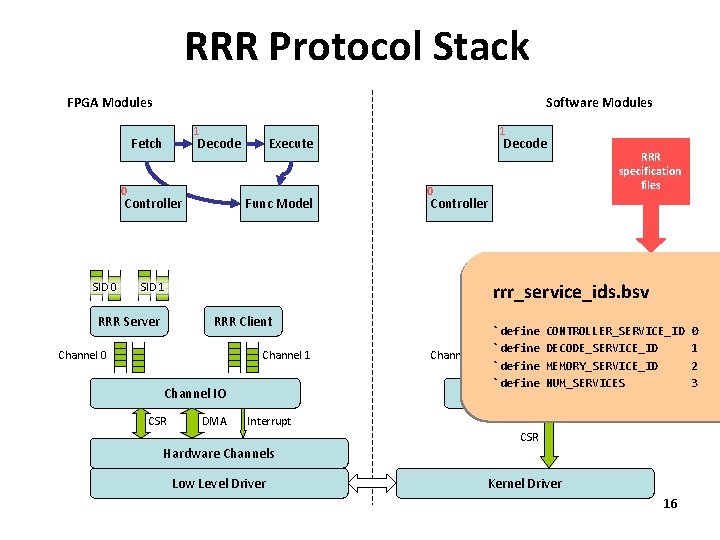

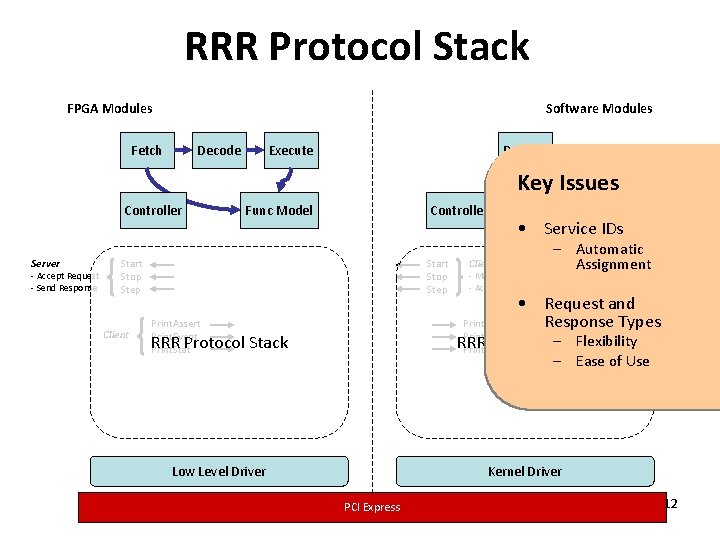

RRR Protocol Stack FPGA Modules Software Modules Fetch Decode Execute Decode Key Issues Controller Server - Accept Request - Send Response Func Model Controller Start Stop Step Client Start Stop Step Print. Assert Print. Event Print. Stat RRR Protocol Stack • Service IDs Client - Make Request - Accept Response – Automatic Assignment • Request and Response Types Print. Assert Server Print. Event Flexibility RRR Protocol –Stack Print. Stat – Ease of Use Low Level Driver Kernel Driver PCI Express 12

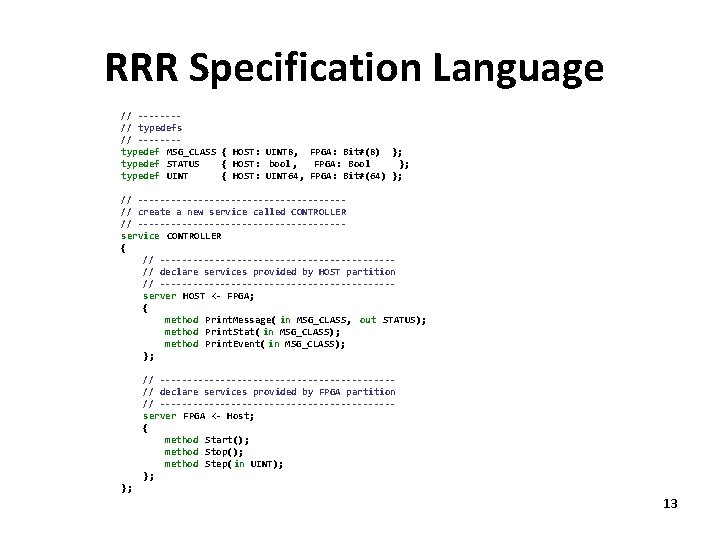

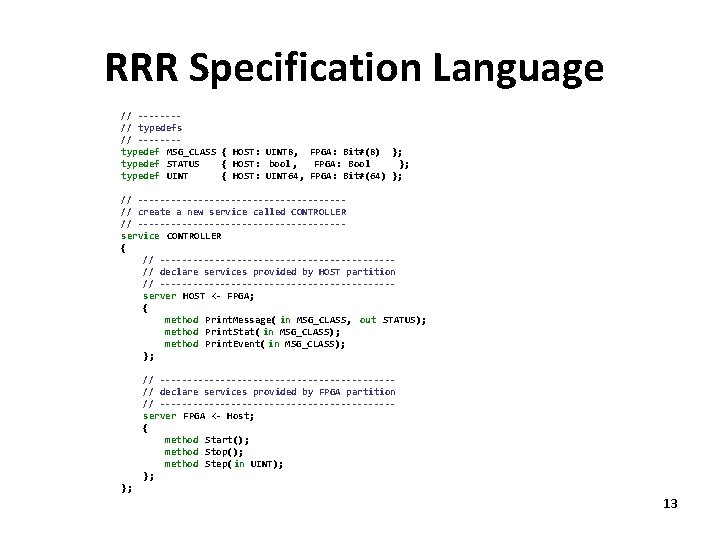

RRR Specification Language // -------// typedefs // -------typedef MSG_CLASS { HOST: UINT 8, FPGA: Bit#(8) }; typedef STATUS { HOST: bool , FPGA: Bool }; typedef UINT { HOST: UINT 64, FPGA: Bit#(64) }; // -------------------// create a new service called CONTROLLER // -------------------service CONTROLLER { // ---------------------// declare services provided by HOST partition // ---------------------server HOST <- FPGA; { method Print. Message( in MSG_CLASS, out STATUS); method Print. Stat( in MSG_CLASS); method Print. Event( in MSG_CLASS); }; // ---------------------// declare services provided by FPGA partition // ---------------------server FPGA <- Host; { method Start(); method Stop(); method Step( in UINT); }; }; 13

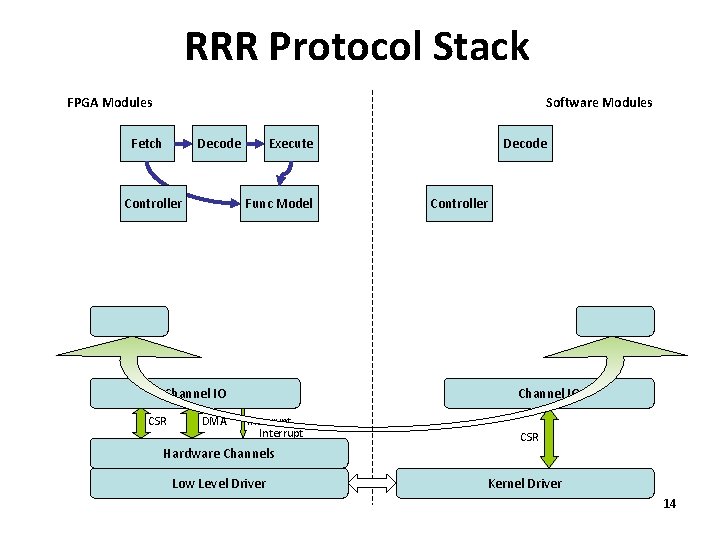

RRR Protocol Stack FPGA Modules Software Modules Fetch Decode Controller Execute Func Model Channel IO CSR DMA Decode Controller Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 14

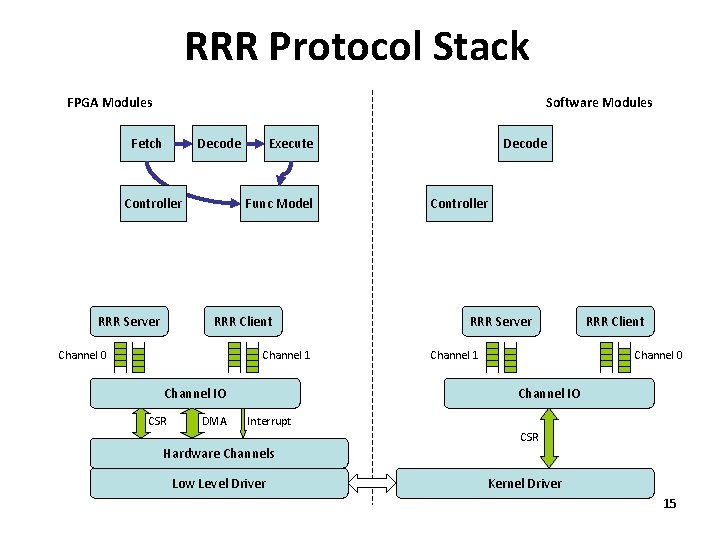

RRR Protocol Stack FPGA Modules Software Modules Fetch Decode Controller RRR Server Execute Func Model RRR Client Channel 0 Channel 1 Channel IO CSR DMA Decode Controller RRR Server Channel 1 RRR Client Channel 0 Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 15

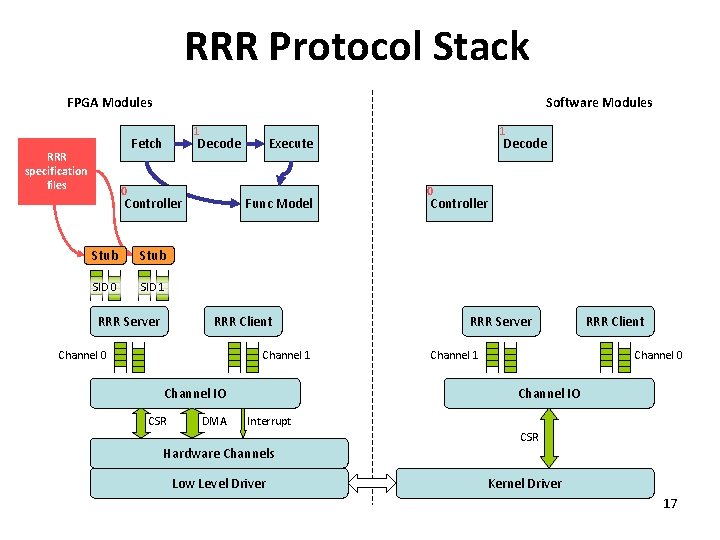

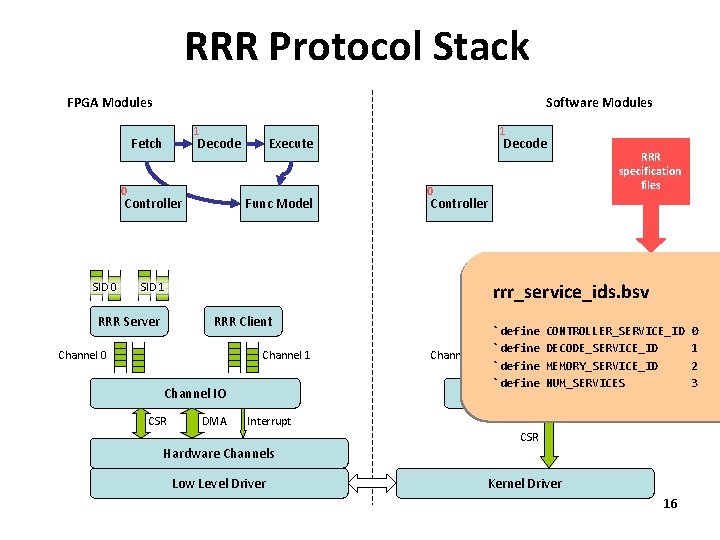

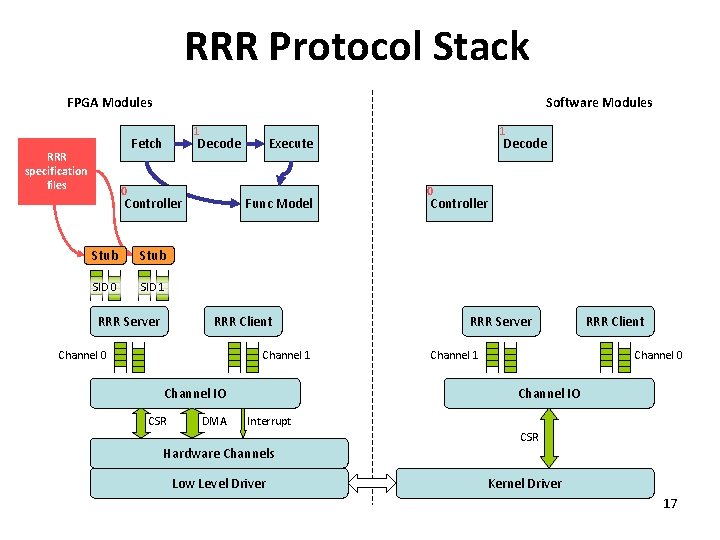

RRR Protocol Stack FPGA Modules Software Modules 1 Fetch Decode 0 Controller SID 0 1 Execute Func Model Decode 0 Controller rrr_service_ids. bsv SID 1 RRR Server RRR Client Channel 0 Channel 1 Channel IO CSR RRR specification files DMA RRR Server Channel 1 `define RRR Client CONTROLLER_SERVICE_ID DECODE_SERVICE_ID Channel 0 MEMORY_SERVICE_ID NUM_SERVICES Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 16 0 1 2 3

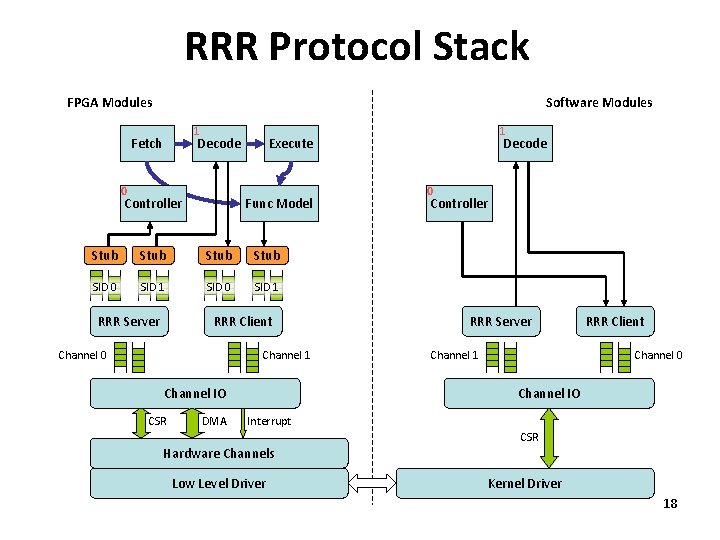

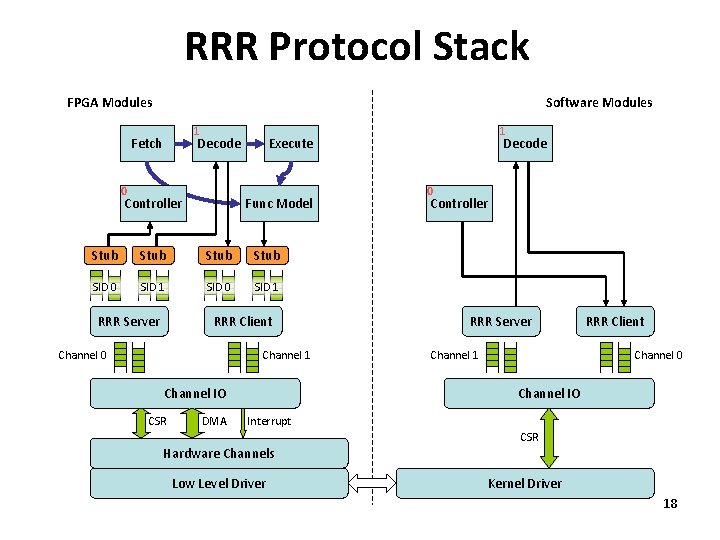

RRR Protocol Stack FPGA Modules Software Modules 1 Fetch RRR specification files Decode 0 Controller Stub SID 0 SID 1 RRR Server Execute Func Model RRR Client Channel 0 Channel 1 Channel IO CSR DMA 1 Decode 0 Controller RRR Server Channel 1 RRR Client Channel 0 Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 17

RRR Protocol Stack FPGA Modules Software Modules 1 Fetch Decode 0 Controller Execute Func Model Stub SID 0 SID 1 RRR Server RRR Client Channel 0 Channel 1 Channel IO CSR DMA 1 Decode 0 Controller RRR Server Channel 1 RRR Client Channel 0 Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 18

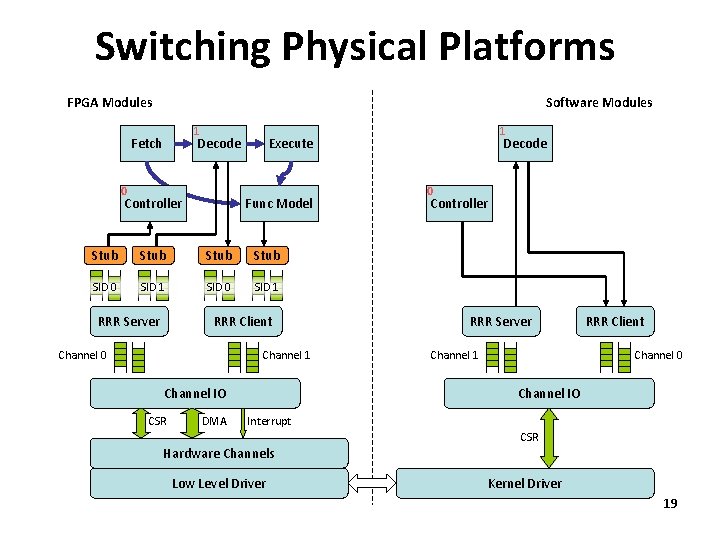

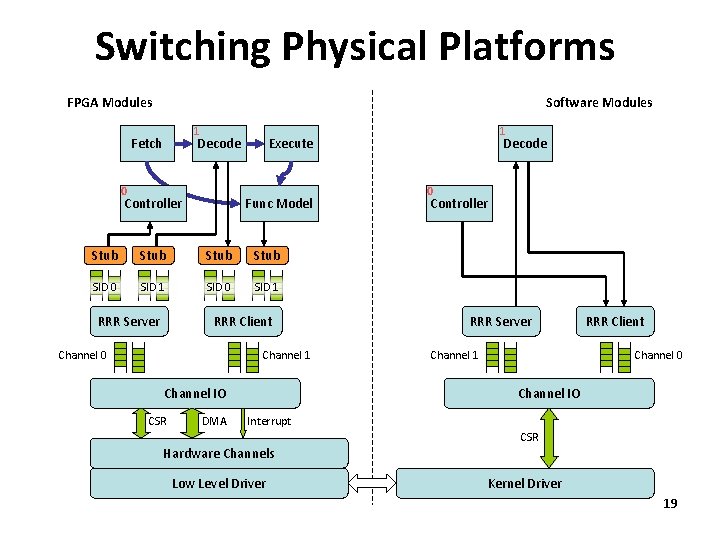

Switching Physical Platforms FPGA Modules Software Modules 1 Fetch Decode 0 Controller Execute Func Model Stub SID 0 SID 1 RRR Server RRR Client Channel 0 Channel 1 Channel IO CSR DMA 1 Decode 0 Controller RRR Server Channel 1 RRR Client Channel 0 Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 19

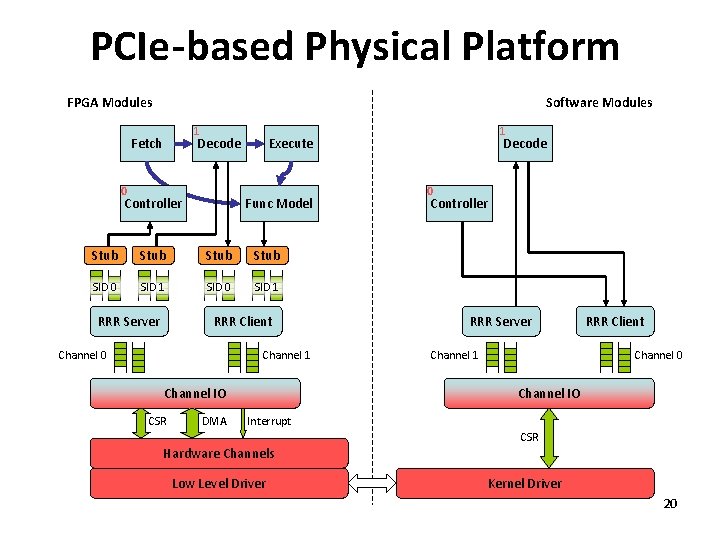

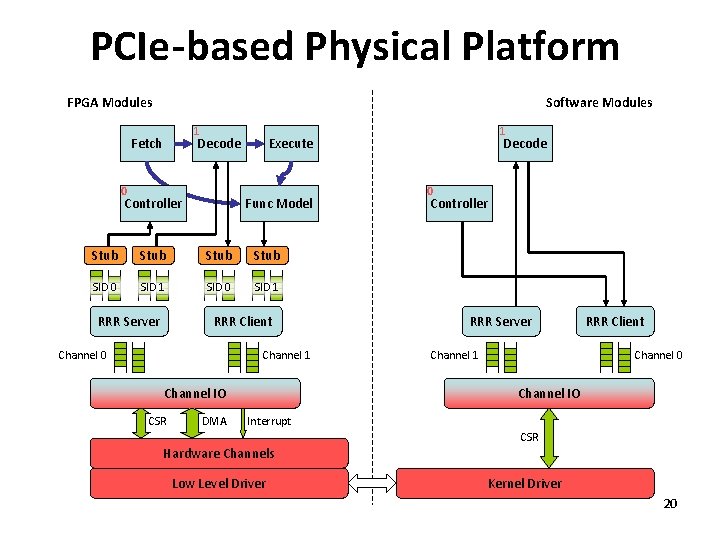

PCIe-based Physical Platform FPGA Modules Software Modules 1 Fetch Decode 0 Controller Execute Func Model Stub SID 0 SID 1 RRR Server RRR Client Channel 0 Channel 1 Channel IO CSR DMA 1 Decode 0 Controller RRR Server Channel 1 RRR Client Channel 0 Channel IO Interrupt CSR Hardware Channels Low Level Driver Kernel Driver 20

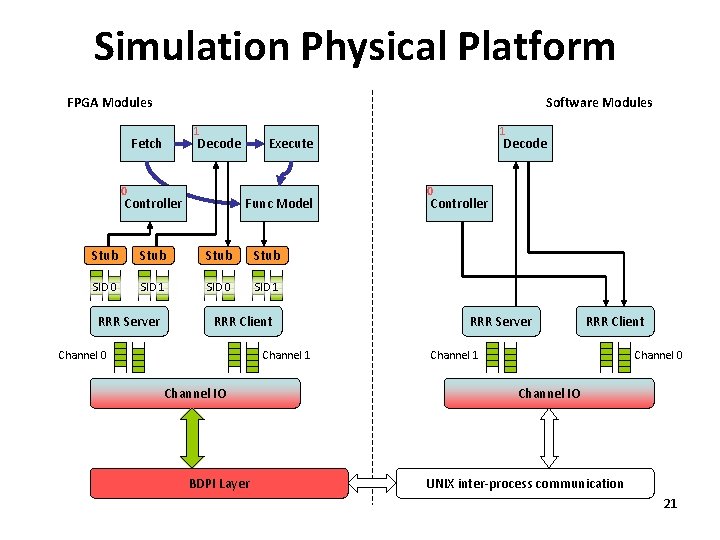

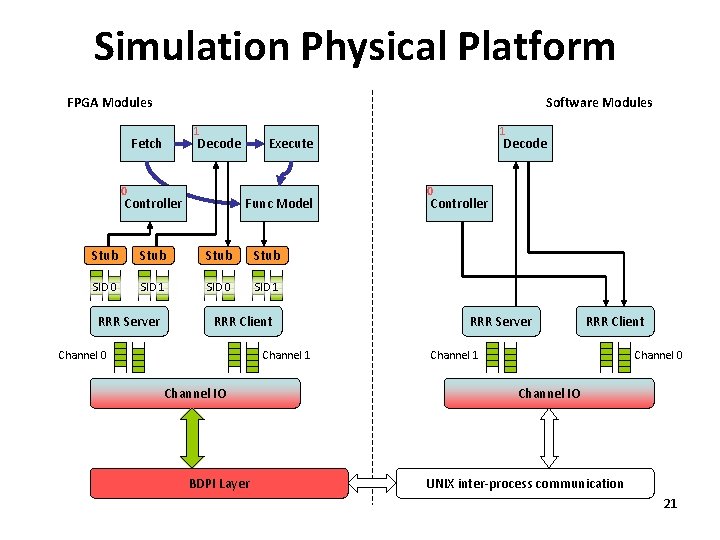

Simulation Physical Platform FPGA Modules Software Modules 1 Fetch Decode 0 Controller Execute Func Model Stub SID 0 SID 1 RRR Server 1 RRR Client Channel 0 Channel 1 Channel IO BDPI Layer Decode 0 Controller RRR Server RRR Client Channel 1 Channel 0 Channel IO UNIX inter-process communication 21

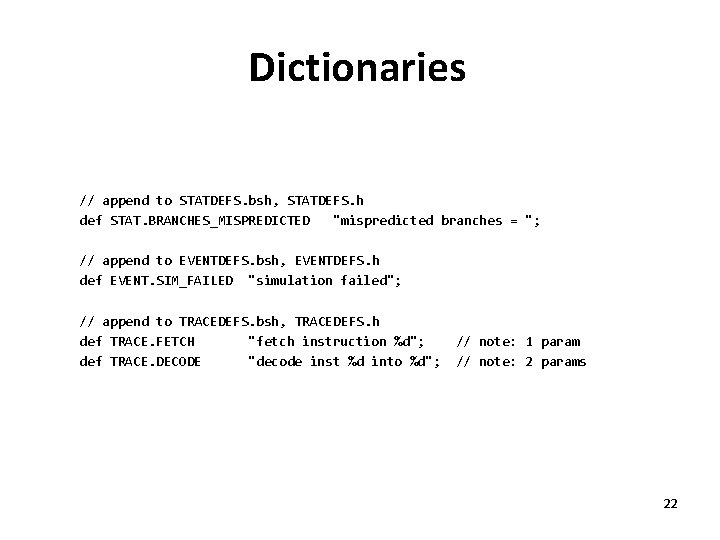

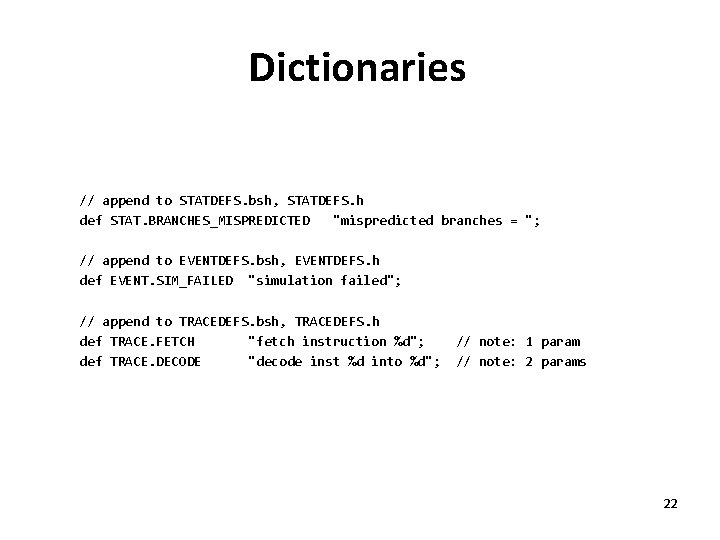

Dictionaries // append to STATDEFS. bsh, STATDEFS. h def STAT. BRANCHES_MISPREDICTED "mispredicted branches = "; // append to EVENTDEFS. bsh, EVENTDEFS. h def EVENT. SIM_FAILED "simulation failed"; // append to TRACEDEFS. bsh, TRACEDEFS. h def TRACE. FETCH "fetch instruction %d"; def TRACE. DECODE "decode inst %d into %d"; // note: 1 param // note: 2 params 22

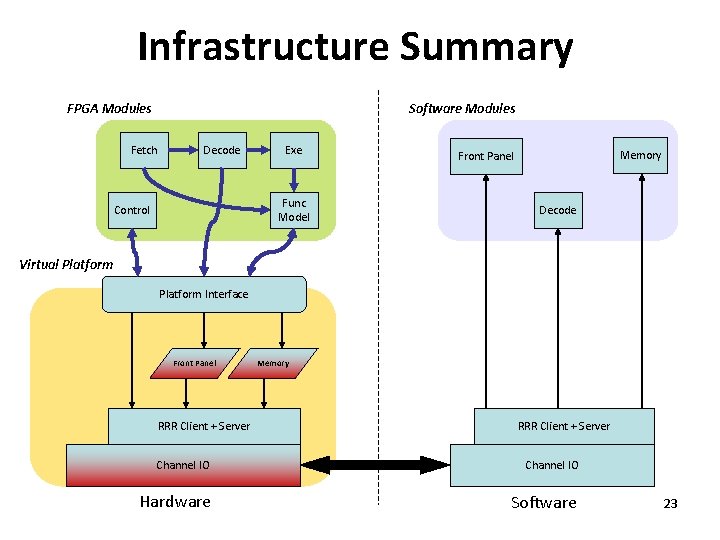

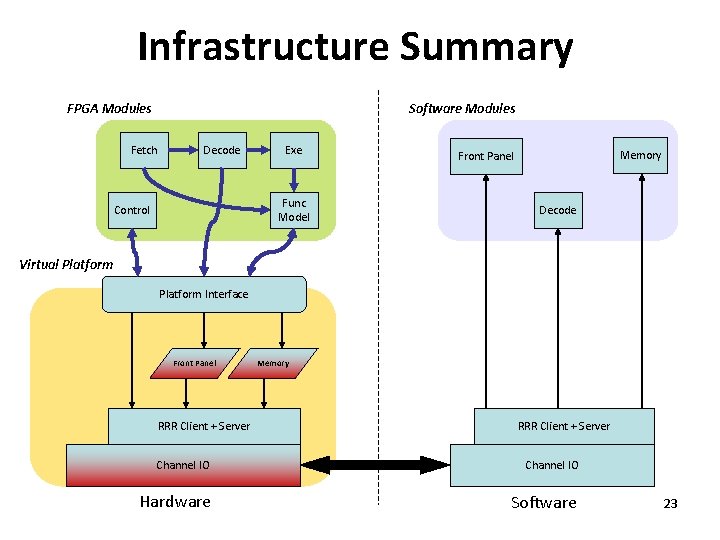

Infrastructure Summary FPGA Modules Software Modules Fetch Decode Exe Func Model Control Memory Front Panel Decode Virtual Platform Interface Front Panel RRR Client + Server Memory RRR Client + Server Channel IO Hardware Software 23

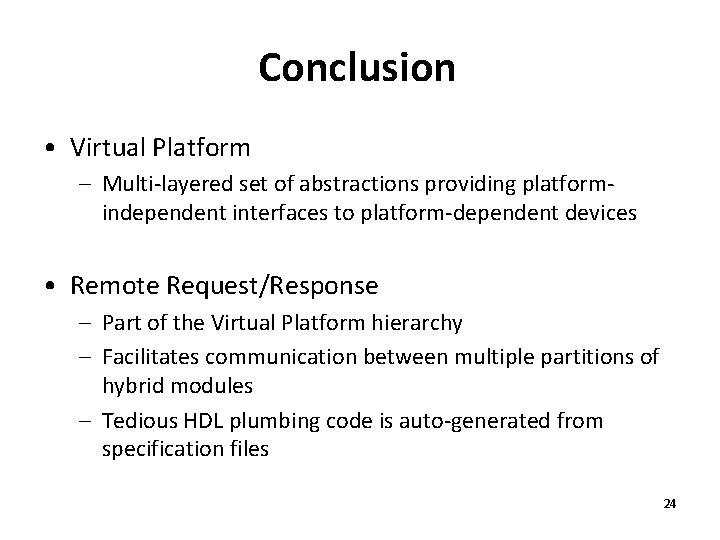

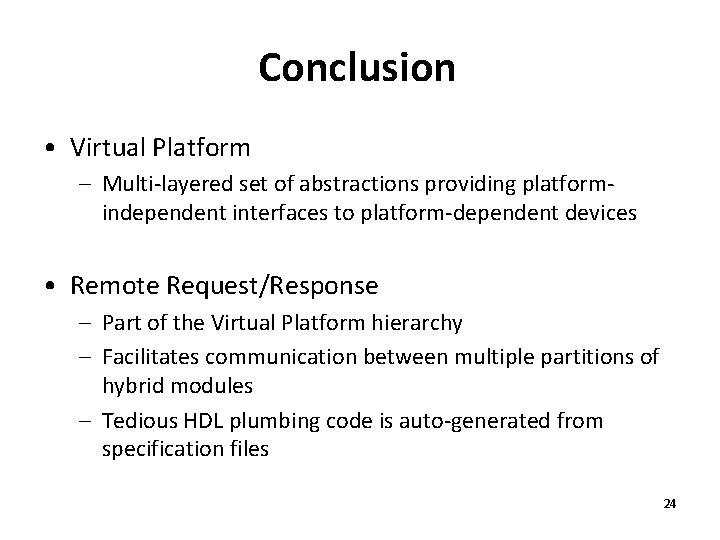

Conclusion • Virtual Platform – Multi-layered set of abstractions providing platformindependent interfaces to platform-dependent devices • Remote Request/Response – Part of the Virtual Platform hierarchy – Facilitates communication between multiple partitions of hybrid modules – Tedious HDL plumbing code is auto-generated from specification files 24

Backup Slides

Sample RRR Service Stub 26

Outline • History and Motivation • Virtual Platforms • Hybrid Modules and RRR • Conclusion and Demo 27

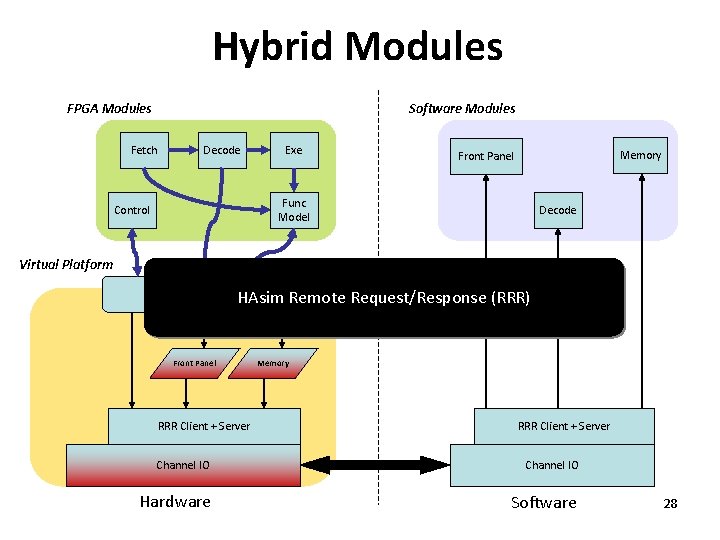

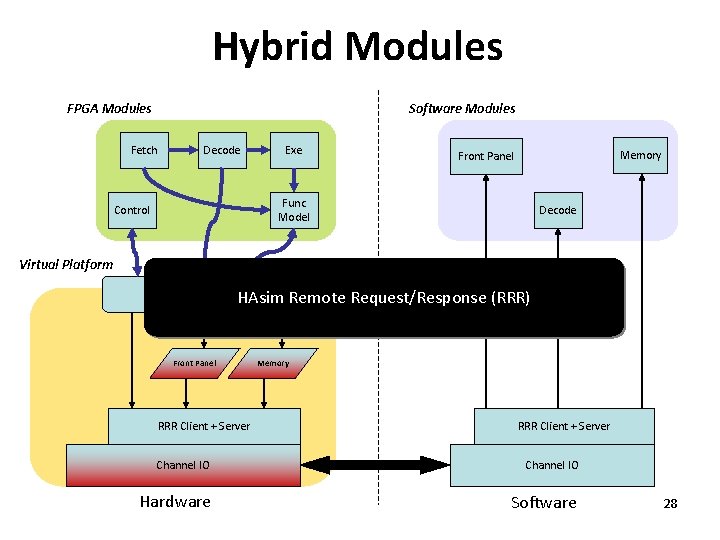

Hybrid Modules FPGA Modules Software Modules Fetch Decode Exe Memory Front Panel Func Model Control Decode Virtual Platform Interface HAsim Front Panel RRR Client + Server Remote Request/Response (RRR) Memory RRR Client + Server Channel IO Hardware Software 28

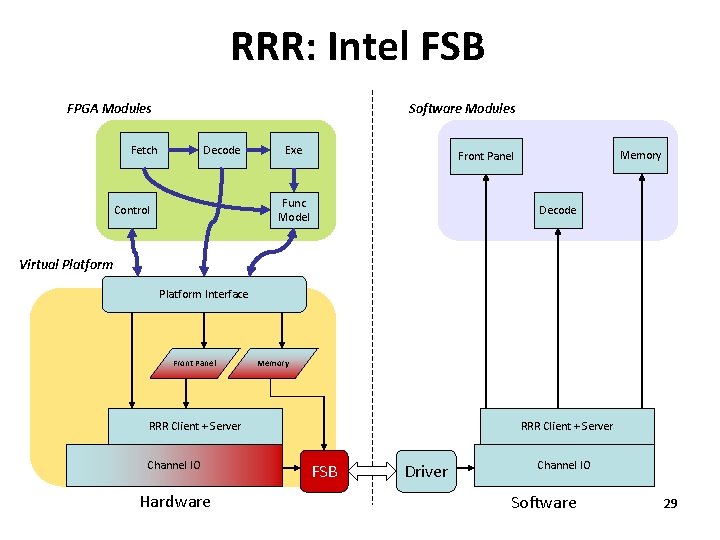

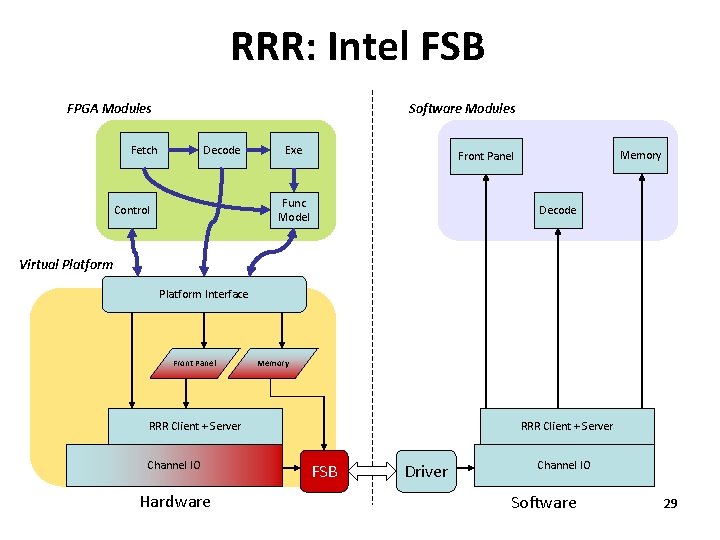

RRR: Intel FSB FPGA Modules Software Modules Fetch Decode Exe Func Model Control Memory Front Panel Decode Virtual Platform Interface Front Panel Memory RRR Client + Server Channel IO Hardware RRR Client + Server FSB Driver Channel IO Software 29

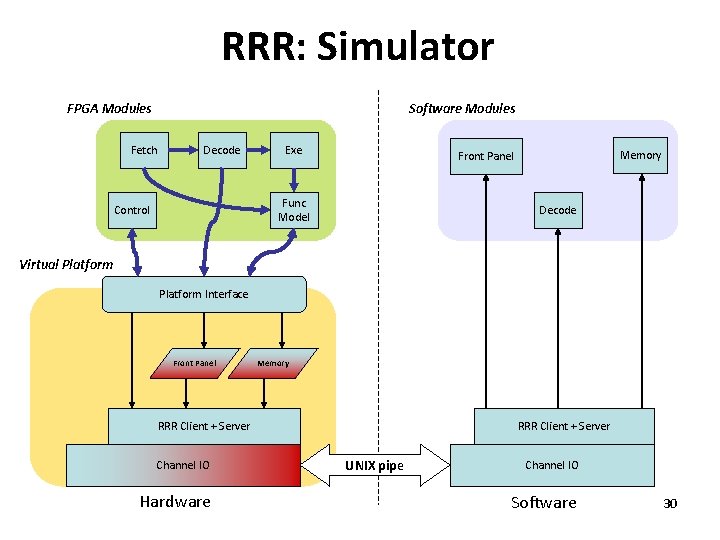

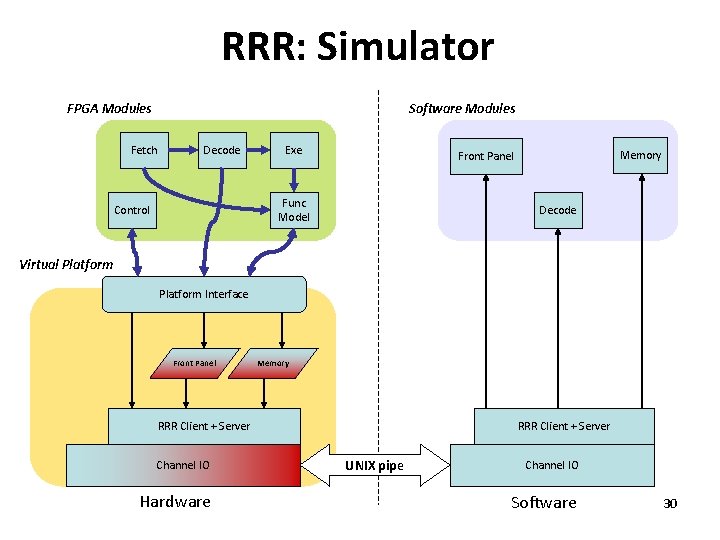

RRR: Simulator FPGA Modules Software Modules Fetch Decode Exe Func Model Control Memory Front Panel Decode Virtual Platform Interface Front Panel Memory RRR Client + Server Channel IO Hardware RRR Client + Server UNIX pipe Channel IO Software 30

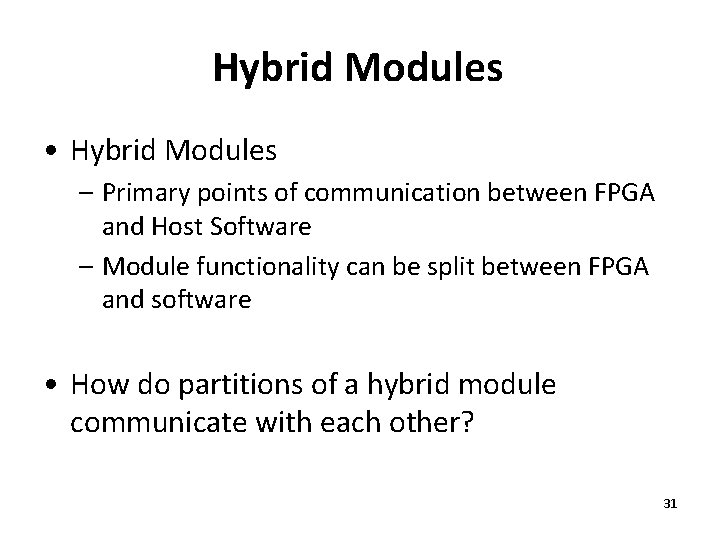

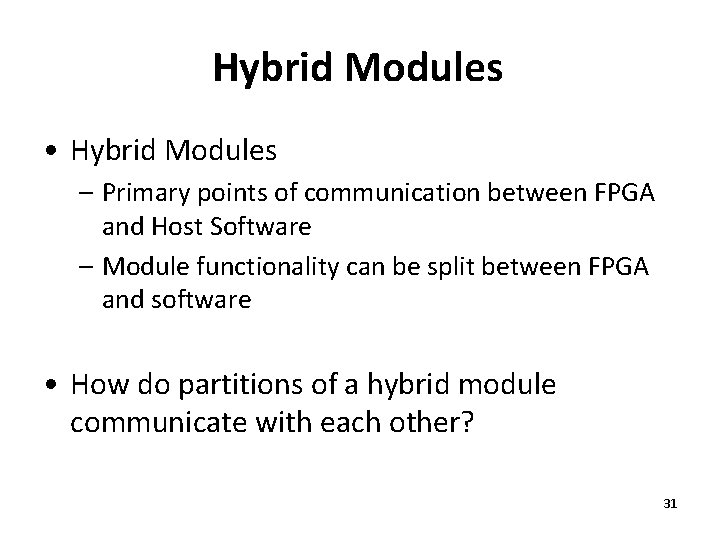

Hybrid Modules • Hybrid Modules – Primary points of communication between FPGA and Host Software – Module functionality can be split between FPGA and software • How do partitions of a hybrid module communicate with each other? 31

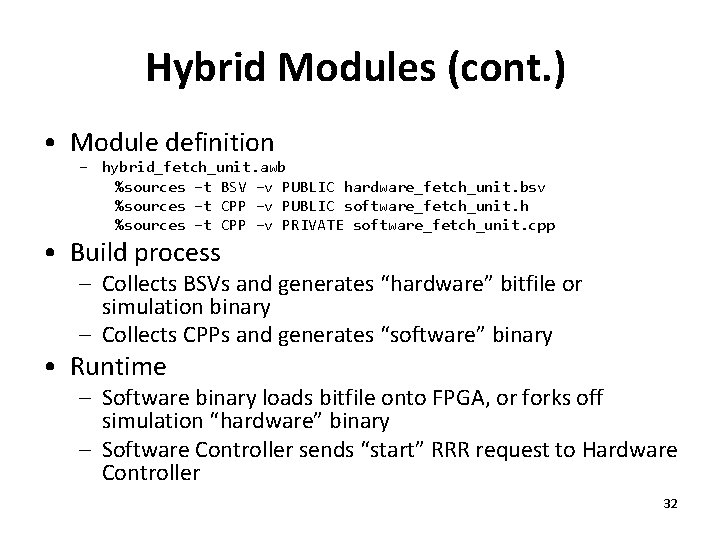

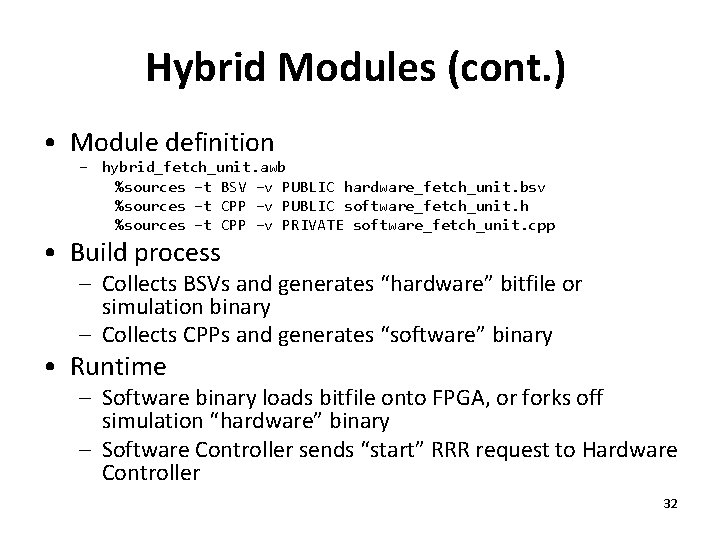

Hybrid Modules (cont. ) • Module definition – hybrid_fetch_unit. awb %sources –t BSV –v PUBLIC hardware_fetch_unit. bsv %sources –t CPP –v PUBLIC software_fetch_unit. h %sources –t CPP –v PRIVATE software_fetch_unit. cpp • Build process – Collects BSVs and generates “hardware” bitfile or simulation binary – Collects CPPs and generates “software” binary • Runtime – Software binary loads bitfile onto FPGA, or forks off simulation “hardware” binary – Software Controller sends “start” RRR request to Hardware Controller 32