Radisys 7010 NPU Routing for Shared Metarouter Cards

- Slides: 7

Radisys 7010 NPU Routing for Shared Metarouter Cards David M. Zar dzar@wustl. edu http: //www. arl. wustl. edu/arl

Radisys 7010 Shared Metarouter Card n Physical Problem: We wish to route packets coming into a metarouter (MR) card to the NPU where the MR lives. n Logical Problem: In the general case, where packets are arriving over the fabric switch on a 10 Gb/s link to the FIC, we cannot inspect packet data to route packets based on VLAN (or anything else). 2 - David M. Zar - 9/15/2021

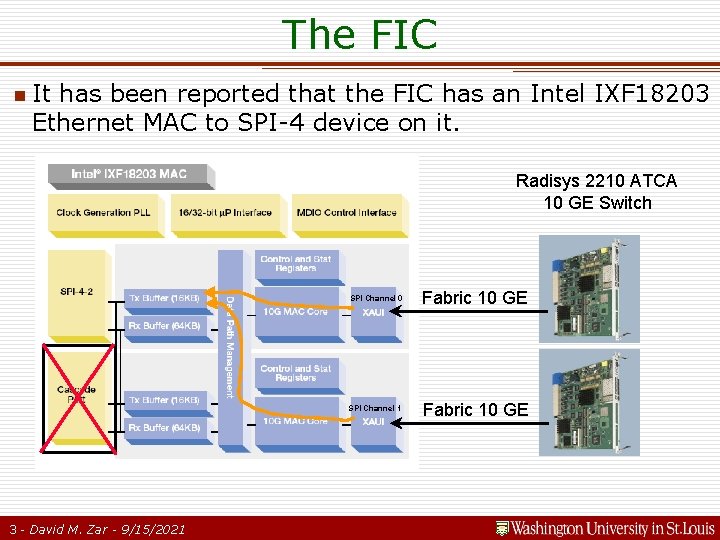

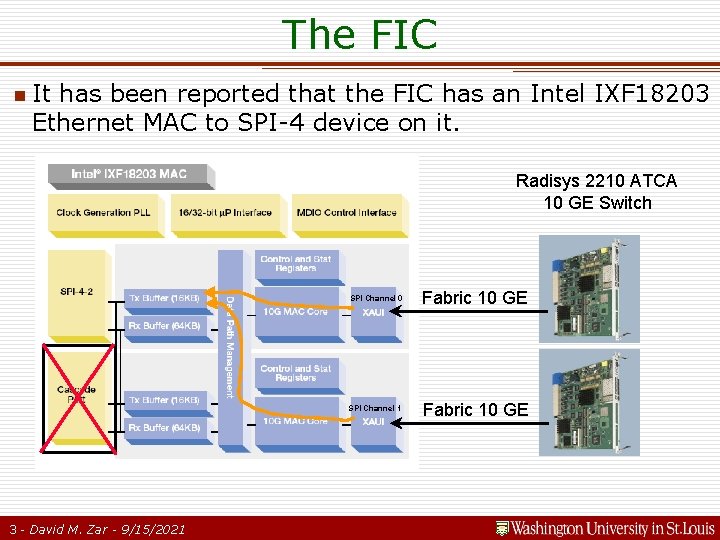

The FIC n It has been reported that the FIC has an Intel IXF 18203 Ethernet MAC to SPI-4 device on it. Radisys 2210 ATCA 10 GE Switch 3 - David M. Zar - 9/15/2021 SPI Channel 0 Fabric 10 GE SPI Channel 1 Fabric 10 GE

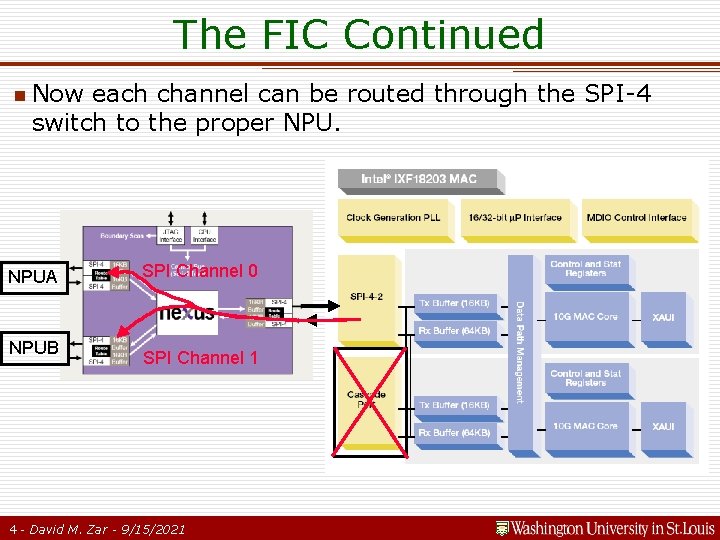

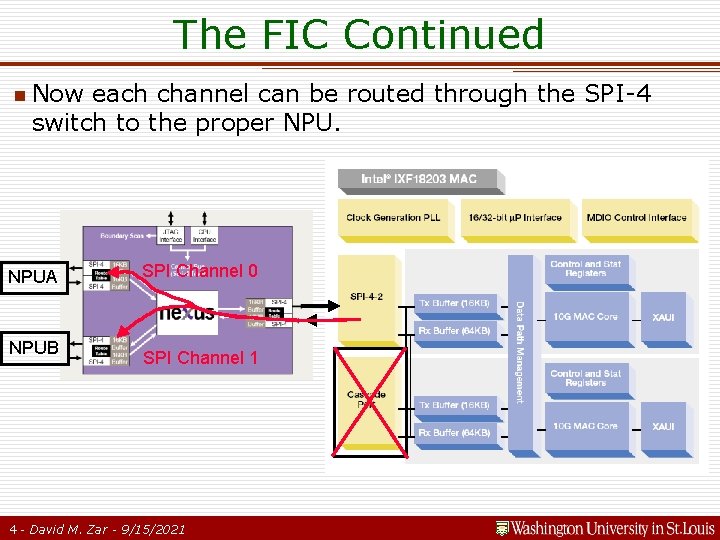

The FIC Continued n Now each channel can be routed through the SPI-4 switch to the proper NPUA NPUB SPI Channel 0 SPI Channel 1 4 - David M. Zar - 9/15/2021

Addressing MR/NPUs n To take advantage of this scheme: » each MR board must be connected to both switches in order to use both NPUs. » There is no failover for if one switch goes down, there is no way to get packets to the NPU accessed by that switch » The MAC address of one of the IXF 18203 MAC devices is the logical MAC address of the NPU. 5 - David M. Zar - 9/15/2021

Lookup Scheme n Packets arriving at the LC need to know where to go: » When a lookup is done to determine which MR is the destination, the logical MAC address of that MR needs to be inserted into the Enet header (no different than before except there are two MAC addresses per –shared- MR card), and » The SPI-4 channel number that is associated with that MAC address is sent to the TX block so that it can send the packet to the correct switch that can “see” this MAC address. n The “reverse” path works the same way: » When a lookup is done to send data from a MR to somewhere else, if that somewhere is another MR, it needs to know the logical MAC address of that MR and insert that into the Enet header. » At the same lookup, the SPI-4 channel number to send out on is also extracted and passed to the transmit block so it is transmitted on the correct channel to reach a switch that can “see” the specified MAC address. » If the destination is an LC, we could use either channel number as its SPI-4 switch would be configured to send all traffic to one NPU (the ingress NPU). If we keep the same channel as the incoming packet, however, then we know it will go out through the same switch that sent the packet to the MR. 6 - David M. Zar - 9/15/2021

Future Scheme n Radisys has mentioned that the next version of the dual NPU blade will have the FIC on the board in the form of an FPGA that we will be able to reprogram. » We could then inspect the packets for VLAN tag to determine which SPI-4 channel to use. » We could have full failover, again, as all traffic could go to either switch and still be routed to the correct NPU through the FPGA lookup. n The timing of this new board is “sometime in 2007. ” 7 - David M. Zar - 9/15/2021