Radiation Tolerance of an SRAM based FPGA Used

Radiation Tolerance of an SRAM based FPGA Used in a Large Tracking Detector Ketil Røed 1, 2, 3 Johan Alme 2, Dominik Fehlker 2, H. Helstrup 1, Matthias Richter 2, Kjetil Ullaland 2, Dieter Röhrich 2 1. Bergen University College 2. University of Bergen 3. CERN www. hib. no RD 09 Firenze

Outline • Main focus: reconfiguration solution applied to reduced the probability of functional failures due to SEUs. • Introduction & background • System description • Testing & Results www. hib. no RD 09 Firenze

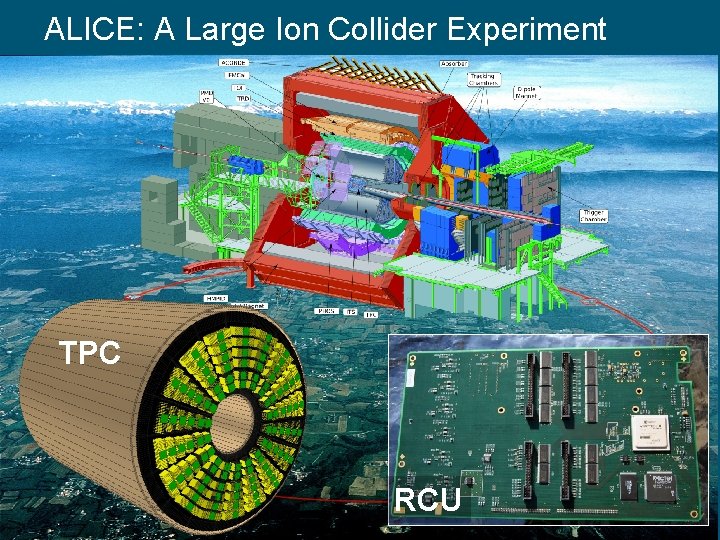

ALICE: A Large Ion Collider Experiment TPC RCU www. hib. no RD 09 Firenze

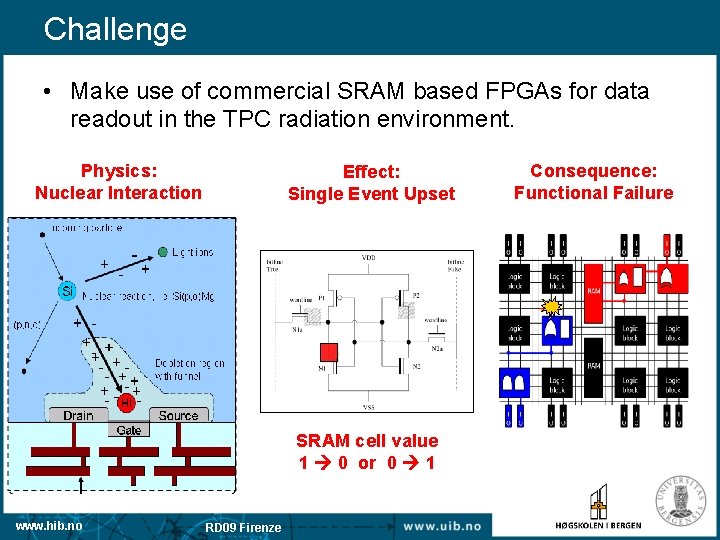

Challenge • Make use of commercial SRAM based FPGAs for data readout in the TPC radiation environment. Physics: Nuclear Interaction Effect: Single Event Upset SRAM cell value 1 0 or 0 1 www. hib. no RD 09 Firenze Consequence: Functional Failure

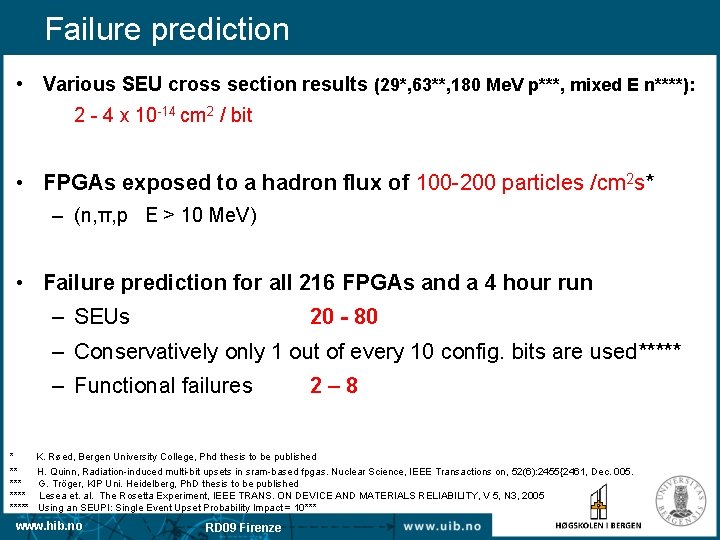

Failure prediction • Various SEU cross section results (29*, 63**, 180 Me. V p***, mixed E n****): 2 - 4 x 10 -14 cm 2 / bit • FPGAs exposed to a hadron flux of 100 -200 particles /cm 2 s* – (n, π, p E > 10 Me. V) • Failure prediction for all 216 FPGAs and a 4 hour run – SEUs 20 - 80 – Conservatively only 1 out of every 10 config. bits are used***** – Functional failures * ** ***** 2– 8 K. Røed, Bergen University College, Phd thesis to be published H. Quinn, Radiation-induced multi-bit upsets in sram-based fpgas. Nuclear Science, IEEE Transactions on, 52(6): 2455{2461, Dec. 005. G. Tröger, KIP Uni. Heidelberg, Ph. D thesis to be published Lesea et. al. The Rosetta Experiment, IEEE TRANS. ON DEVICE AND MATERIALS RELIABILITY, V 5, N 3, 2005 Using an SEUPI: Single Event Upset Probability Impact = 10*** www. hib. no RD 09 Firenze

Repeated Outline • A systen solution is developed to both reduced the probability of failure and to offer additional testing functionality • Introduction & background • System description • Testing & Results www. hib. no RD 09 Firenze

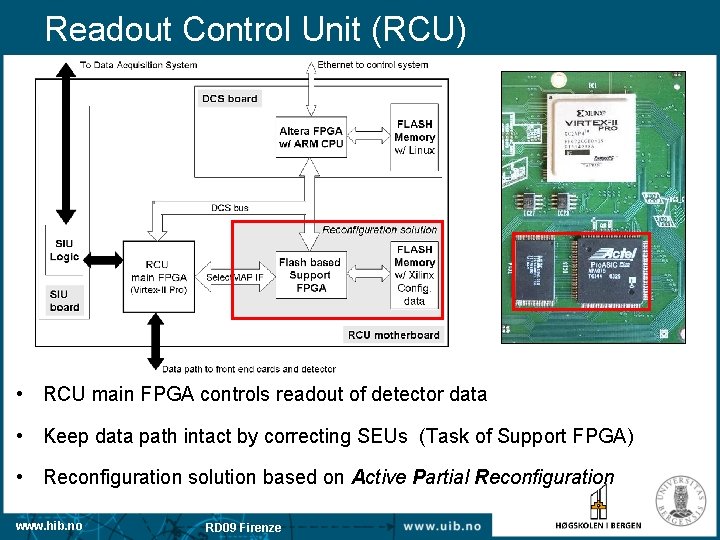

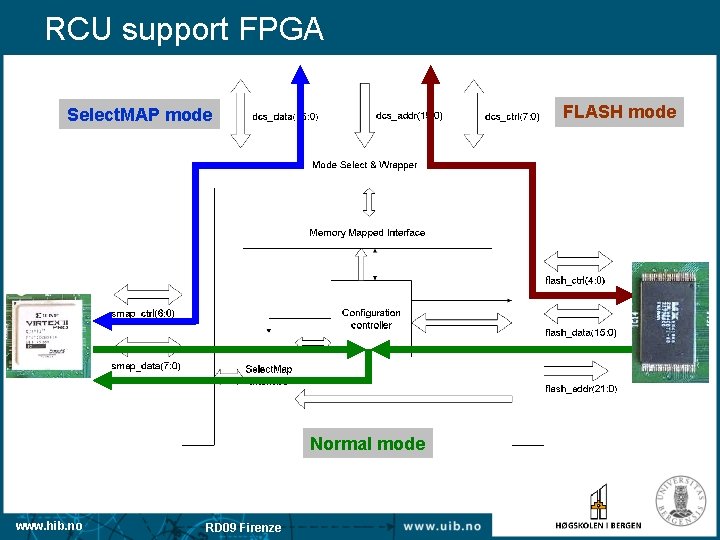

Readout Control Unit (RCU) • RCU main FPGA controls readout of detector data • Keep data path intact by correcting SEUs (Task of Support FPGA) • Reconfiguration solution based on Active Partial Reconfiguration www. hib. no RD 09 Firenze

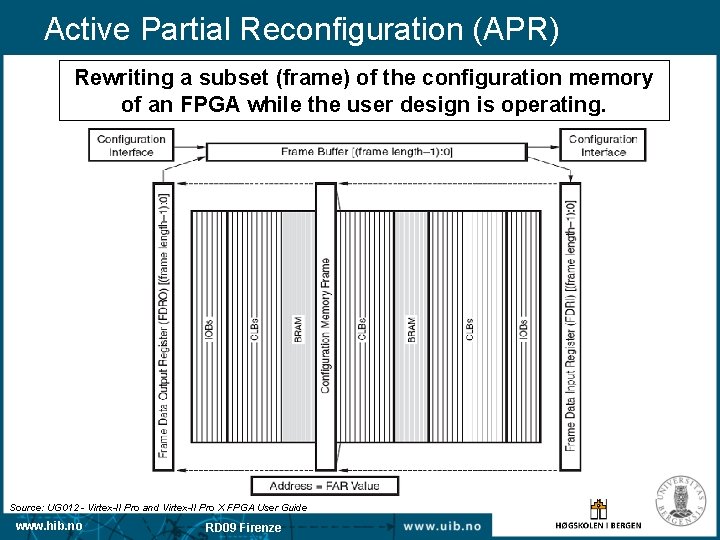

Active Partial Reconfiguration (APR) Rewriting a subset (frame) of the configuration memory of an FPGA while the user design is operating. Source: UG 012 - Virtex-II Pro and Virtex-II Pro X FPGA User Guide www. hib. no RD 09 Firenze

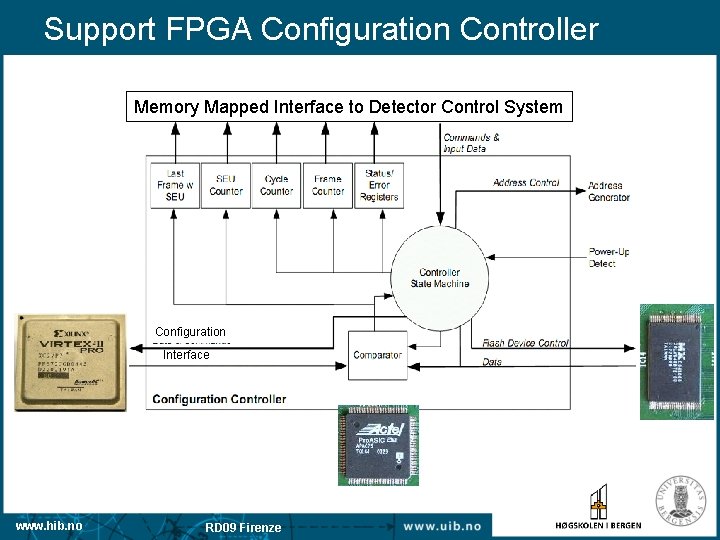

Support FPGA Configuration Controller Memory Mapped Interface to Detector Control System Configuration Interface www. hib. no RD 09 Firenze

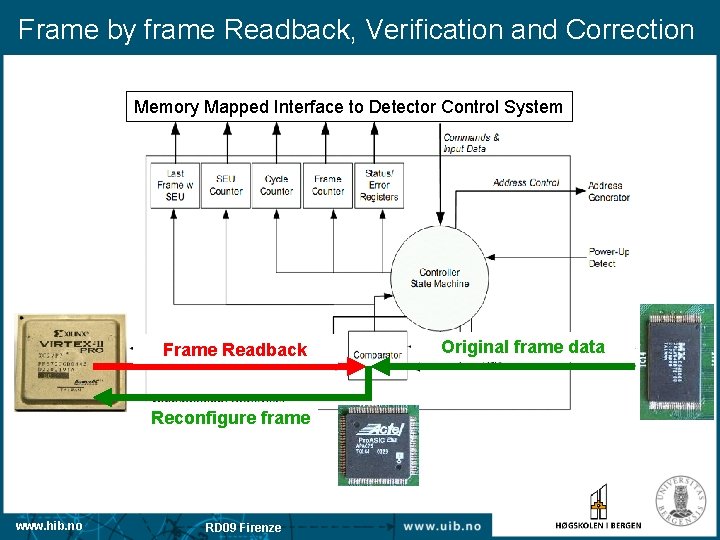

Frame by frame Readback, Verification and Correction Memory Mapped Interface to Detector Control System Frame Readback Reconfigure frame www. hib. no RD 09 Firenze Original frame data

Repeated Outline • Introduction & background • System description • Testing & Results www. hib. no RD 09 Firenze

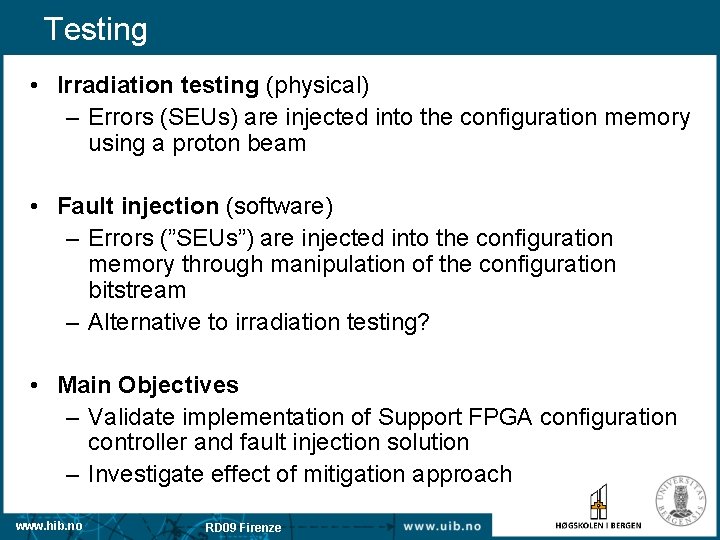

Testing • Irradiation testing (physical) – Errors (SEUs) are injected into the configuration memory using a proton beam • Fault injection (software) – Errors (”SEUs”) are injected into the configuration memory through manipulation of the configuration bitstream – Alternative to irradiation testing? • Main Objectives – Validate implementation of Support FPGA configuration controller and fault injection solution – Investigate effect of mitigation approach www. hib. no RD 09 Firenze

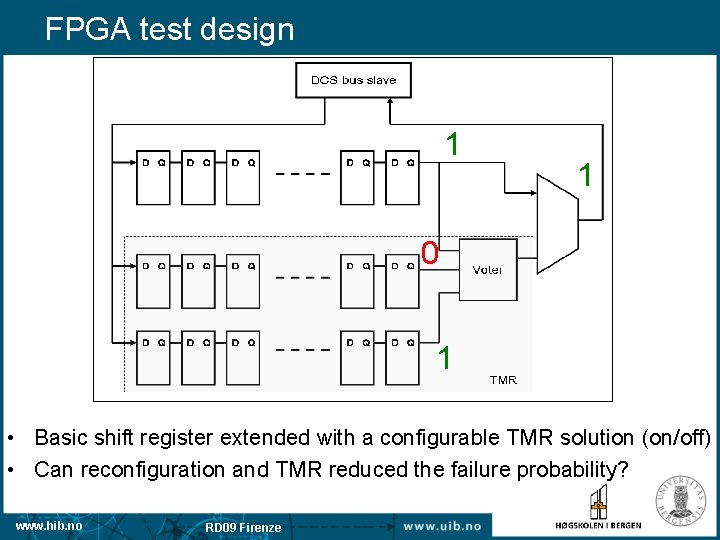

FPGA test design 1 1 0 1 • Basic shift register extended with a configurable TMR solution (on/off) • Can reconfiguration and TMR reduced the failure probability? www. hib. no RD 09 Firenze

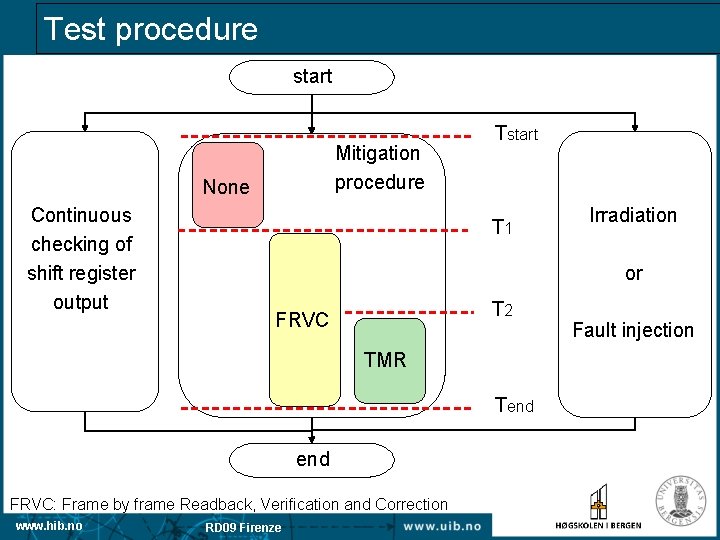

Test procedure start Mitigation procedure None Continuous checking of shift register output Tstart T 1 or T 2 FRVC TMR Tend FRVC: Frame by frame Readback, Verification and Correction www. hib. no Irradiation RD 09 Firenze Fault injection

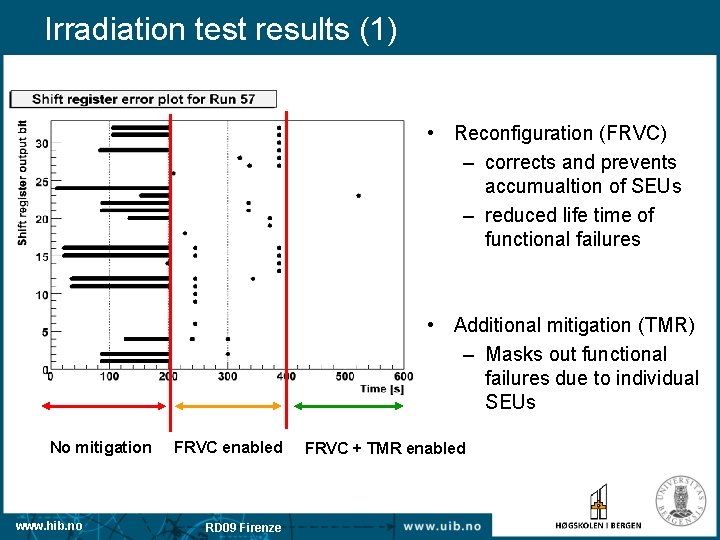

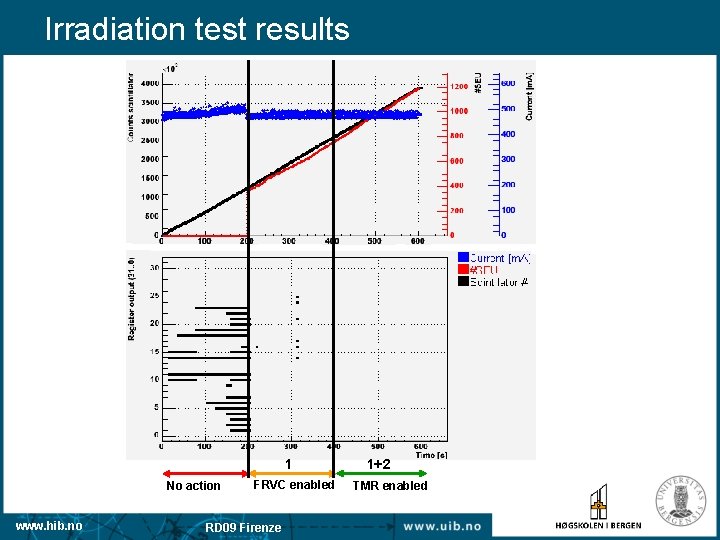

Irradiation test results (1) • Reconfiguration (FRVC) – corrects and prevents accumualtion of SEUs – reduced life time of functional failures • Additional mitigation (TMR) – Masks out functional failures due to individual SEUs No mitigation www. hib. no FRVC enabled RD 09 Firenze FRVC + TMR enabled

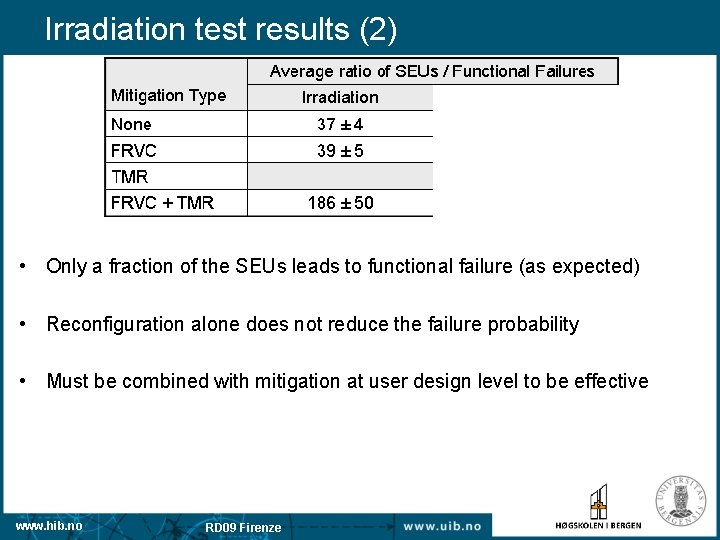

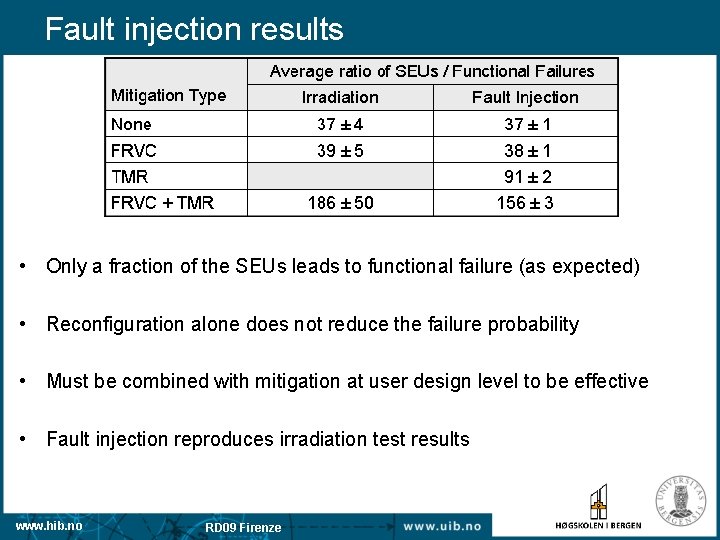

Irradiation test results (2) • Only a fraction of the SEUs leads to functional failure (as expected) • Reconfiguration alone does not reduce the failure probability • Must be combined with mitigation at user design level to be effective • Fault injection reproduces irradiation test results www. hib. no RD 09 Firenze

Fault injection results • Only a fraction of the SEUs leads to functional failure (as expected) • Reconfiguration alone does not reduce the failure probability • Must be combined with mitigation at user design level to be effective • Fault injection reproduces irradiation test results www. hib. no RD 09 Firenze

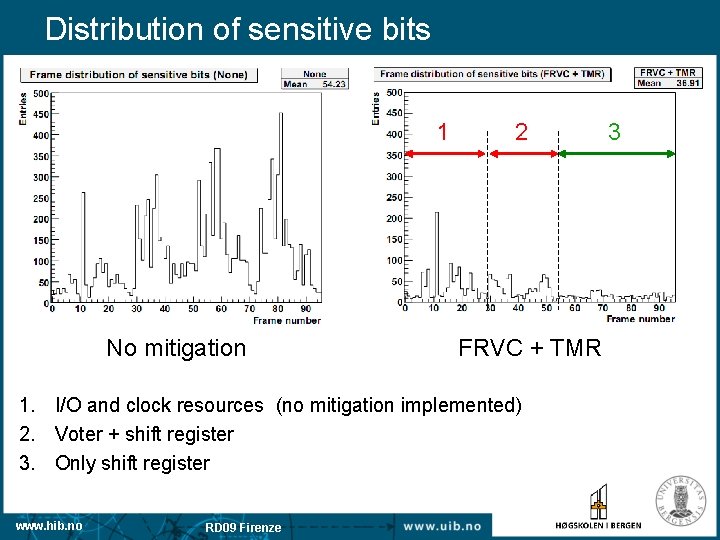

Distribution of sensitive bits 1 No mitigation 2 FRVC + TMR 1. I/O and clock resources (no mitigation implemented) 2. Voter + shift register 3. Only shift register www. hib. no RD 09 Firenze 3

Summary • Successful implementation of reconfiguration network – Allows us to use COTS SRAM FPGAs in radiation environments. – Prevents accumulation of SEUs by continuous reconfiguration, but – mitigation at the level of user design is needed. – Combination will significantly reduce the probability of functional failures during operation. – System allows to monitor SEUs during operation • Fault injection implemented as alternative test method – Locate sensitive bits optimize mitigation approach – To do: Predict the failure probability of the final design www. hib. no RD 09 Firenze

Acknowledgements • Gerd Tröger, University of Heidelberg • Luciano Musa, Blahoslav Pastircák, CERN • Austin Lesea, Xilinx • Alexander Prokofiev, TSL University of Uppsala • Jon Wikne, Eivind Olsen, OCL University of Oslo www. hib. no RD 09 Firenze

Backup www. hib. no RD 09 Firenze

Irradiation test results 1 2 1 No action www. hib. no FRVC enabled RD 09 Firenze 1+2 TMR enabled 3

RCU support FPGA FLASH mode Select. MAP mode Normal mode www. hib. no RD 09 Firenze

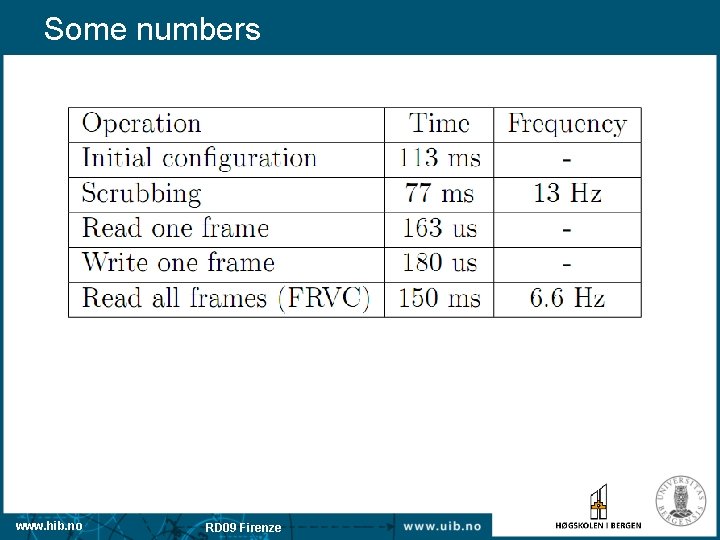

Some numbers www. hib. no RD 09 Firenze

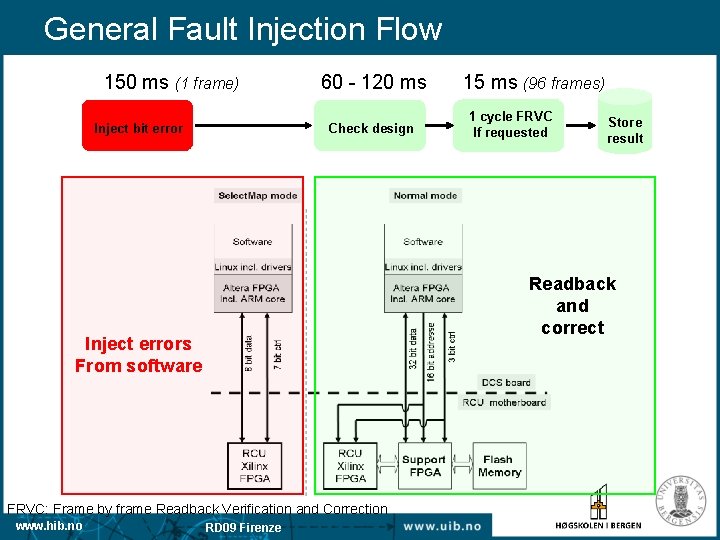

General Fault Injection Flow 150 ms (1 frame) Inject bit error 60 - 120 ms Check design 1 cycle FRVC If requested Store result Readback and correct Inject errors From software FRVC: Frame by frame Readback Verification and Correction www. hib. no 15 ms (96 frames) RD 09 Firenze

- Slides: 25