Radiation Performance of Embedded Core ABC Controller on

Radiation Performance of Embedded Core. ABC Controller on RT-Pro. ASIC 3 Sana Rezgui, Durwyn D'Silva, JJ Wang Partially Supported by AFRL 24 October 2020

Outline 1. 2. 3. 4. 5. RT 3 P vs. A 3 P Design Under Test: Core. ABC Soft IP Radiation Test Results (w/o SEU Mitigation) Error-Rate Prediction Summary Rezgui, MAPLD 2009 Session C 2

Motivation 1. SEE Characterization of an Embedded Processor on a Reprogrammable Non-Volatile FPGA 1. 2. Device Under Test: A 3 P Design Under Test: Core. ABC RT 3 P vs. A 3 P 1. 2. 3. 4. Hermetically-Sealed Ceramic packages (CG or LG) Qualification, Inspection and Assembly in accordance with MILSTD-883 Class B SEU Mitigation [TMR of FFs automated by Synplicity Software Tool] SET mitigation with Actel FAE support Rezgui, MAPLD 2009 Session C 3

Device Under Test (A 3 P) Non-Volatile => By Definition: Should be Very Suitable for FPGA Core Space Applications Rezgui, MAPLD 2009 Session C 4

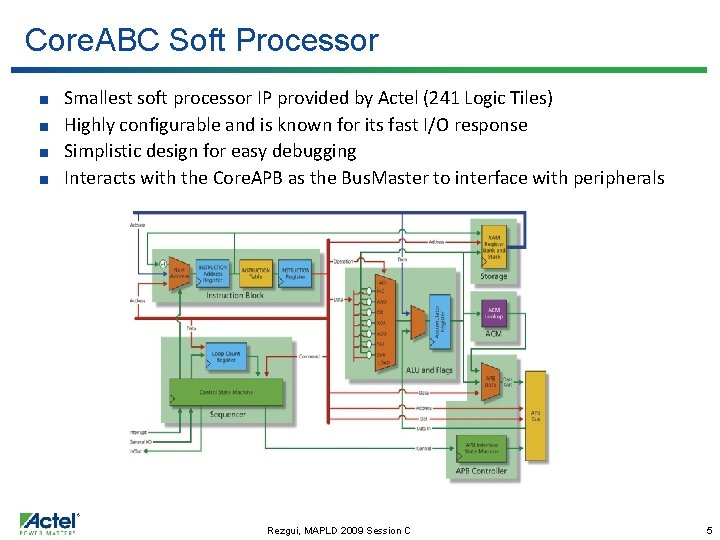

Core. ABC Soft Processor Smallest soft processor IP provided by Actel (241 Logic Tiles) Highly configurable and is known for its fast I/O response Simplistic design for easy debugging Interacts with the Core. APB as the Bus. Master to interface with peripherals Rezgui, MAPLD 2009 Session C 5

Hardware Test Setup Core. ABC Rezgui, MAPLD 2009 Session C 6

Test Design: Core. ABC Rezgui, MAPLD 2009 Session C 7

Test Software: Matrix Multiplication (C = A * B) Cycle 1 Cycle 2 Cycle 3 Rezgui, MAPLD 2009 Session C 8

DUT Algorithm & Master Algorithm DUT MASTER 2 or 39 MHz (Hand-Shaking @ 39 MHz) 1. Initialization & Synchronization 2. Matrix Calculation 3. Report of Errors Rezgui, MAPLD 2009 Session C 9

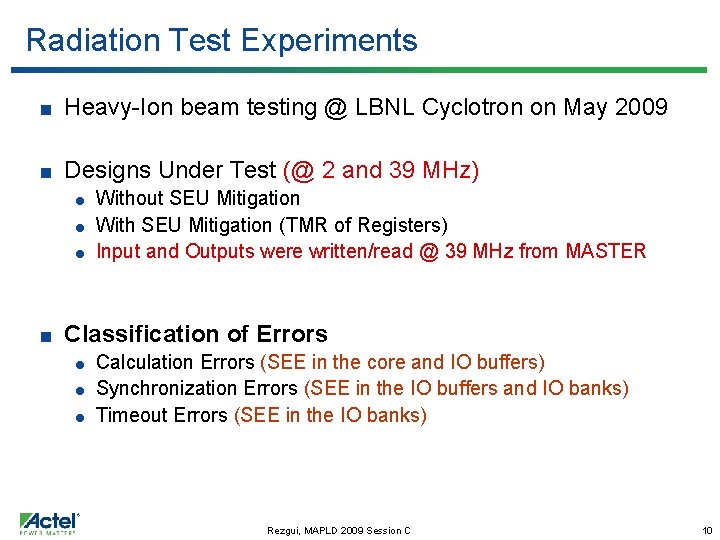

Radiation Test Experiments Heavy-Ion beam testing @ LBNL Cyclotron on May 2009 Designs Under Test (@ 2 and 39 MHz) Without SEU Mitigation With SEU Mitigation (TMR of Registers) Input and Outputs were written/read @ 39 MHz from MASTER Classification of Errors Calculation Errors (SEE in the core and IO buffers) Synchronization Errors (SEE in the IO buffers and IO banks) Timeout Errors (SEE in the IO banks) Rezgui, MAPLD 2009 Session C 10

Radiation Test Designs (w/o SEU Mitigation) DFF Voter DFF Tested DFF SET Filter Non-Mitigated (NM) Design [A 3 P] SEU-Mitigated Design [RT 3 P] SEE-Mitigated Design (SEU & SET) Rezgui, MAPLD 2009 Session C DFF DFF 11

Test Designs (Area, Frequency & Power) Core. ABC IOs Glb. Clock Sq. Cb. SE LVDS Non. Mitigated 58 1013 135 28 SEUMitigated 174 17. 43% 1071 20. 26% 3 SRAM Blk. 3 (Data TMR’d) 89% 82% 16. 7% 37. 5% // // 16% Power Core, IOs MHz m. W @ 39 MHz 45 14. 4 270 39 16. 5 270 // Area Delta Penalty Max. Freq. Timing None Power [SEU Immune FPGA] < 0. 3 W Rezgui, MAPLD 2009 Session C 14% Power 14% N @ 40 MHz 12

![Error-Rate Predictions (Worst-Case) For A 3 P [No SEE Mitigation] For RT 3 P Error-Rate Predictions (Worst-Case) For A 3 P [No SEE Mitigation] For RT 3 P](http://slidetodoc.com/presentation_image/0014ad1372844a249802d992a0707b69/image-13.jpg)

Error-Rate Predictions (Worst-Case) For A 3 P [No SEE Mitigation] For RT 3 P [With SEU Mitigation] Rezgui et al. TNS 2007 Rezgui, MAPLD 2009 Session C 13

Radiation Test Results (Worst-Case) Pred. SEU-Mit Rezgui, MAPLD 2009 Session C Pred. NM 14

![Error-Rate Predictions (Freq. Dependence) For A 3 P [No SEE Mitigation] Refinement: Frequency Dependence Error-Rate Predictions (Freq. Dependence) For A 3 P [No SEE Mitigation] Refinement: Frequency Dependence](http://slidetodoc.com/presentation_image/0014ad1372844a249802d992a0707b69/image-15.jpg)

Error-Rate Predictions (Freq. Dependence) For A 3 P [No SEE Mitigation] Refinement: Frequency Dependence For RT 3 P [With SEU Mitigation] Refinement: Frequency Dependence Rezgui, MAPLD 2009 Session C 15

Radiation Test Results (Freq. Dependence) Pred. SEU-Mit Pred. NM NM SEU-Mit. Rezgui, MAPLD 2009 Session C 16

![Error-Rate Predictions (Synch. /Asynch. ) For A 3 P [No SEE Mitigation] Refinement: Frequency Error-Rate Predictions (Synch. /Asynch. ) For A 3 P [No SEE Mitigation] Refinement: Frequency](http://slidetodoc.com/presentation_image/0014ad1372844a249802d992a0707b69/image-17.jpg)

Error-Rate Predictions (Synch. /Asynch. ) For A 3 P [No SEE Mitigation] Refinement: Frequency Dependence & Synchronicity (IOs) For RT 3 P [With SEU Mitigation] Refinement: Frequency Dependence & Synchronicity (IOs) Rezgui, MAPLD 2009 Session C 17

Radiation Test Results (Synch. /Asynch. ) NM SEU-Mit. Rezgui, MAPLD 2009 Session C 18

Radiation Summary Observations At Frequencies < 40 MHz, SETs on FPGA core have minor contributions to the overall SEE cross-sections If the IOs were clocked at the DUT frequency, a clear dependency with the frequency for the NM Design should have been observed. SET on IO buffers & IO banks are dominant for Small Designs Orbital Error-Rate Prediction [Error/Design/10, 000 years] GEO, Solar Min. , 100 mil, no Funneling, 1 um Collection Depth Design Non-Mitigated SEU-Mitigated @ 39 MHz 25. 8 3 @ 2 MHz 25. 8 1. 9 VERY LOW ERROR-RATES for RT 3 P Rezgui, MAPLD 2009 Session C 19

Error-Rate Prediction: Cortex M 1 Any Other IP should have Sequential & Combinational Gates. Error-Rate Predictions should apply in the same way. It is a MUST to validate this formula on other Designs For RT 3 P Rezgui, MAPLD 2009 Session C 20

- Slides: 20