Radiation Belt Storm Probes RBSP Instrument Data Processing

Radiation Belt Storm Probes RBSP Instrument Data Processing Unit (IDPU) Sept 30 – Oct 1 2009 Critical Design Review Michael Ludlam Space Sciences Laboratory UC Berkeley RBSP EFW ICDR 1

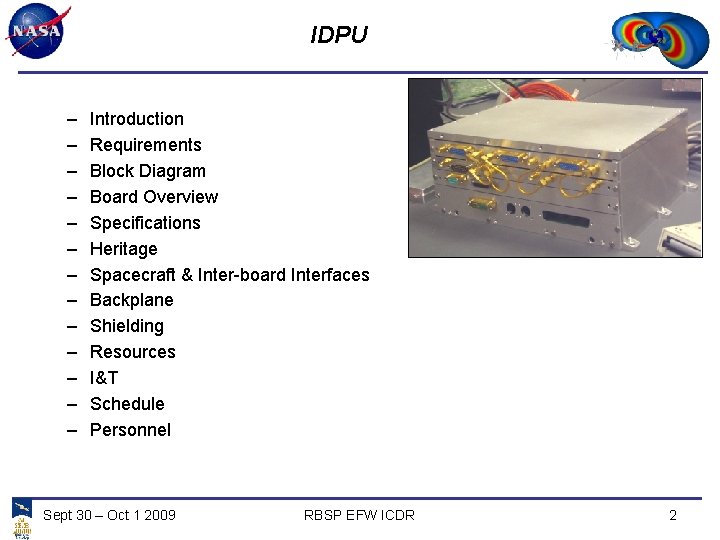

IDPU – – – – Introduction Requirements Block Diagram Board Overview Specifications Heritage Spacecraft & Inter-board Interfaces Backplane Shielding Resources I&T Schedule Personnel Sept 30 – Oct 1 2009 RBSP EFW ICDR 2

IDPU Introduction – Scope of Presentation • Gives overview of Instrument Data Processing Unit (IDPU). • Areas that are handled at the IDPU top level are discussed in detail here. • Individual board details, requirements and designs are discussed during those board presentations. – Synopsis: IDPU houses most of the instrument electronics, providing the electrical interface between the spacecraft and the sensor / boom units. It contains four circuit boards: • • Low Voltage Power Supply (LVPS) and Power Control Board Circuit (PCB) Digital Control Board (DCB) Digital Fields Board (DFB) Boom Electronics Board (BEB) Sept 30 – Oct 1 2009 RBSP EFW ICDR 3

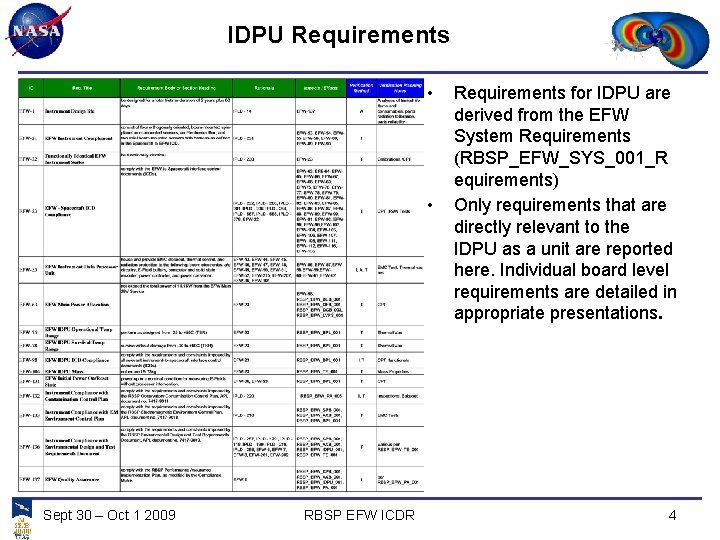

IDPU Requirements • • Sept 30 – Oct 1 2009 RBSP EFW ICDR Requirements for IDPU are derived from the EFW System Requirements (RBSP_EFW_SYS_001_R equirements) Only requirements that are directly relevant to the IDPU as a unit are reported here. Individual board level requirements are detailed in appropriate presentations. 4

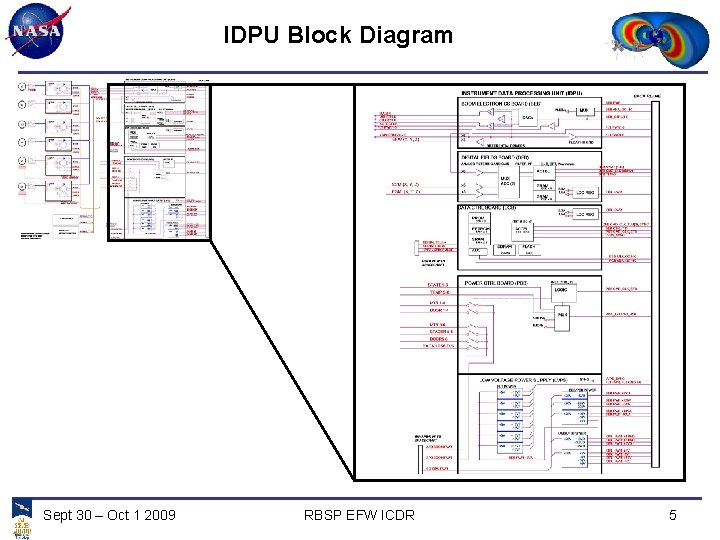

IDPU Block Diagram Sept 30 – Oct 1 2009 RBSP EFW ICDR 5

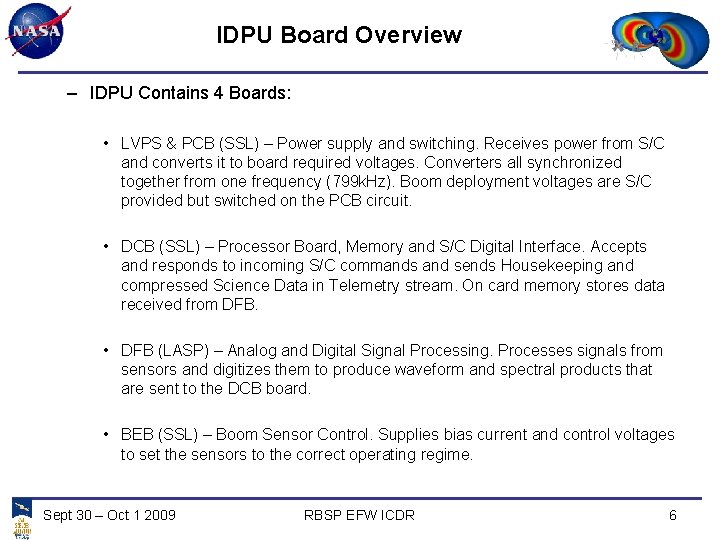

IDPU Board Overview – IDPU Contains 4 Boards: • LVPS & PCB (SSL) – Power supply and switching. Receives power from S/C and converts it to board required voltages. Converters all synchronized together from one frequency (799 k. Hz). Boom deployment voltages are S/C provided but switched on the PCB circuit. • DCB (SSL) – Processor Board, Memory and S/C Digital Interface. Accepts and responds to incoming S/C commands and sends Housekeeping and compressed Science Data in Telemetry stream. On card memory stores data received from DFB. • DFB (LASP) – Analog and Digital Signal Processing. Processes signals from sensors and digitizes them to produce waveform and spectral products that are sent to the DCB board. • BEB (SSL) – Boom Sensor Control. Supplies bias current and control voltages to set the sensors to the correct operating regime. Sept 30 – Oct 1 2009 RBSP EFW ICDR 6

IDPU Electrical Specifications – Board Specification Documents: • • • RBSP_EFW_LVPS_001 J_Specification RBSP_EFW_DCB_003 E_Specification RBSP_EFW_DFB_001 D_SPECrev. D_07_29_09. pdf RBSP_EFW_BEB_001 G_Specification RBSP_EFW_BPL_001 M_Specification Sept 30 – Oct 1 2009 RBSP EFW ICDR 7

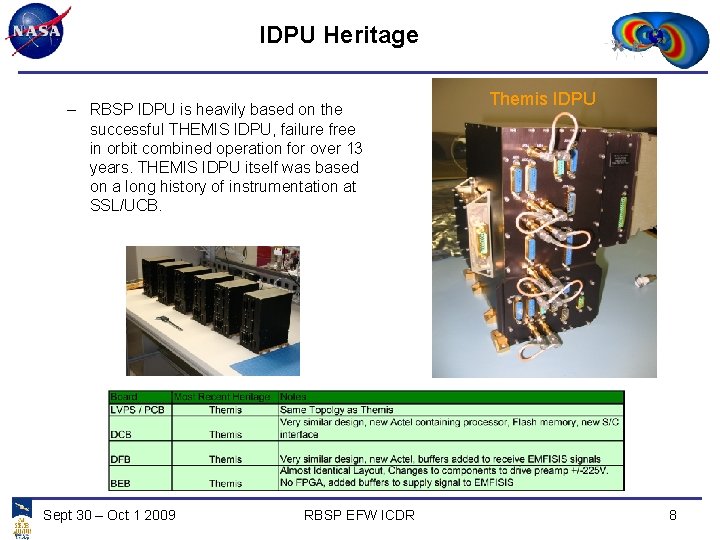

IDPU Heritage – RBSP IDPU is heavily based on the successful THEMIS IDPU, failure free in orbit combined operation for over 13 years. THEMIS IDPU itself was based on a long history of instrumentation at SSL/UCB. Sept 30 – Oct 1 2009 RBSP EFW ICDR Themis IDPU 8

IDPU External Electrical Interfaces • IDPU provides interface to S/C via: – 1 x 15 M DSub Connector on the LVPS (Instrument and Boom Deploy Power). – 1 x 9 F DSub Connector on the DCB (Instrument Commands, 1 PPS/SP, Instrument Telemetry). – Interfaces are defined in the APL Controlled EFW ICD (7417 -9083) – currently Rev. A. – LVDS has been verified by APL provided GSE. ETU IDPU Test planned at APL. – S/C Model power switch circuit from EMECP has been built up for testing with the LVPS. • IDPU provides interface to boom units via: – 3 x 26 F HDSub Connectors on the BEB board (Defined in BEB Specification – RBSP_EFW_BEB_001). – 1 x 62 F HDSub Connector on the LVPS/PCB board (Defined in LVPS/PCB Specification – RBSP_EFW_LVPS_001). – Verified during instrument I&T safe to mate. • IDPU provides interface to EMFISIS via: – pins on 3 x 26 F HDSub Connectors on BEB Board (EFW out). – 1 x 26 M HDSub Connector on DFB (MAG, MSC in). – Interfaces are defined in the APL Controlled EFW to EMFISIS ICD (7417 -9089) – currently Rev. A. – Verified by EFW – EMFISIS interface test on ETU (August 09). Sept 30 – Oct 1 2009 RBSP EFW ICDR 9

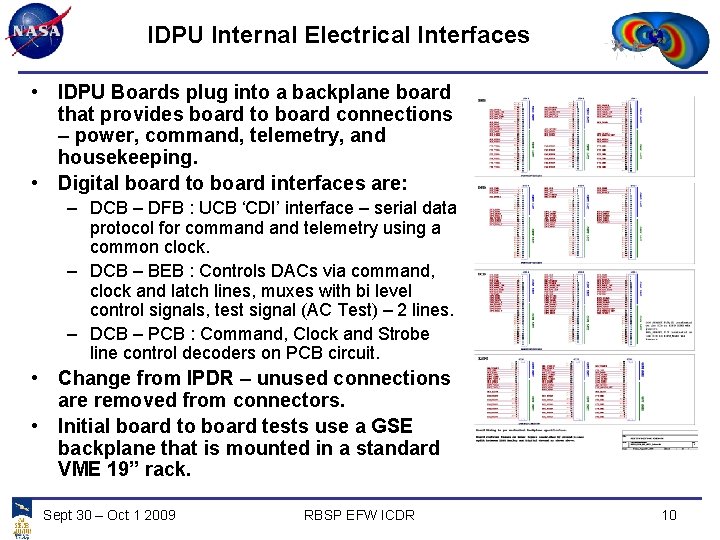

IDPU Internal Electrical Interfaces • IDPU Boards plug into a backplane board that provides board to board connections – power, command, telemetry, and housekeeping. • Digital board to board interfaces are: – DCB – DFB : UCB ‘CDI’ interface – serial data protocol for command telemetry using a common clock. – DCB – BEB : Controls DACs via command, clock and latch lines, muxes with bi level control signals, test signal (AC Test) – 2 lines. – DCB – PCB : Command, Clock and Strobe line control decoders on PCB circuit. • Change from IPDR – unused connections are removed from connectors. • Initial board to board tests use a GSE backplane that is mounted in a standard VME 19” rack. Sept 30 – Oct 1 2009 RBSP EFW ICDR 10

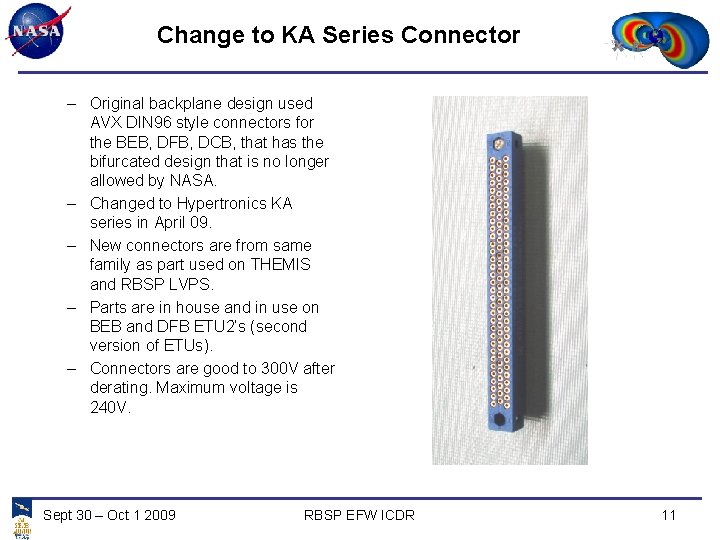

Change to KA Series Connector – Original backplane design used AVX DIN 96 style connectors for the BEB, DFB, DCB, that has the bifurcated design that is no longer allowed by NASA. – Changed to Hypertronics KA series in April 09. – New connectors are from same family as part used on THEMIS and RBSP LVPS. – Parts are in house and in use on BEB and DFB ETU 2’s (second version of ETUs). – Connectors are good to 300 V after derating. Maximum voltage is 240 V. Sept 30 – Oct 1 2009 RBSP EFW ICDR 11

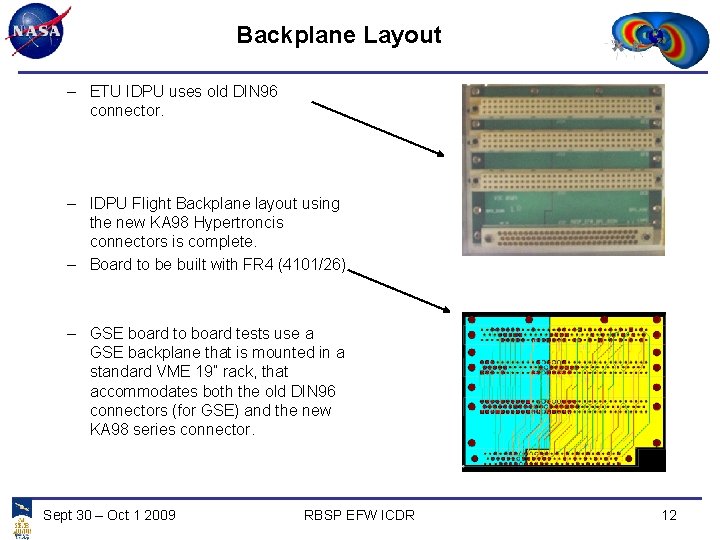

Backplane Layout – ETU IDPU uses old DIN 96 connector. – IDPU Flight Backplane layout using the new KA 98 Hypertroncis connectors is complete. – Board to be built with FR 4 (4101/26) – GSE board to board tests use a GSE backplane that is mounted in a standard VME 19” rack, that accommodates both the old DIN 96 connectors (for GSE) and the new KA 98 series connector. Sept 30 – Oct 1 2009 RBSP EFW ICDR 12

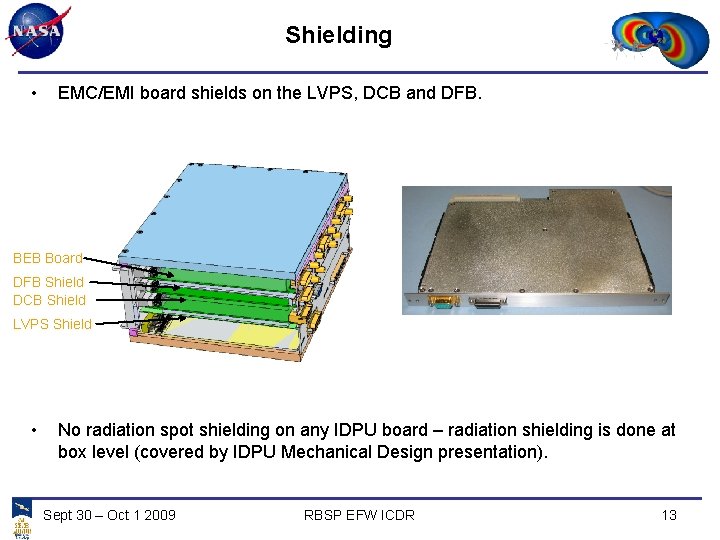

Shielding • EMC/EMI board shields on the LVPS, DCB and DFB. BEB Board DFB Shield DCB Shield LVPS Shield • No radiation spot shielding on any IDPU board – radiation shielding is done at box level (covered by IDPU Mechanical Design presentation). Sept 30 – Oct 1 2009 RBSP EFW ICDR 13

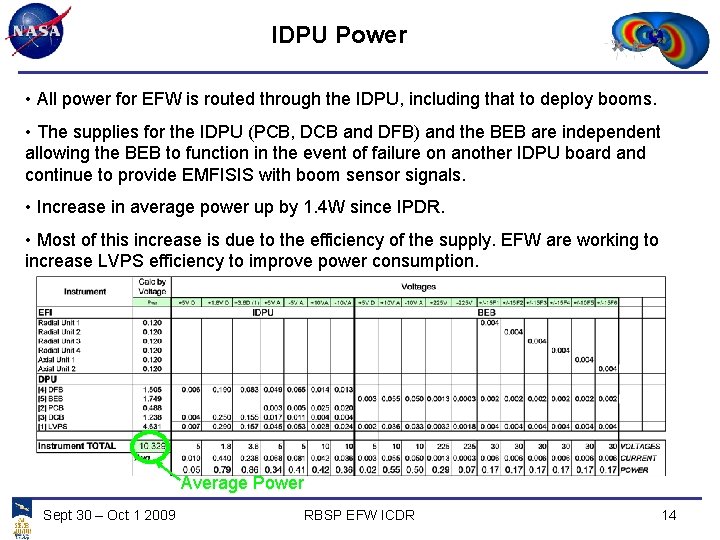

IDPU Power • All power for EFW is routed through the IDPU, including that to deploy booms. • The supplies for the IDPU (PCB, DCB and DFB) and the BEB are independent allowing the BEB to function in the event of failure on another IDPU board and continue to provide EMFISIS with boom sensor signals. • Increase in average power up by 1. 4 W since IPDR. • Most of this increase is due to the efficiency of the supply. EFW are working to increase LVPS efficiency to improve power consumption. Average Power Sept 30 – Oct 1 2009 RBSP EFW ICDR 14

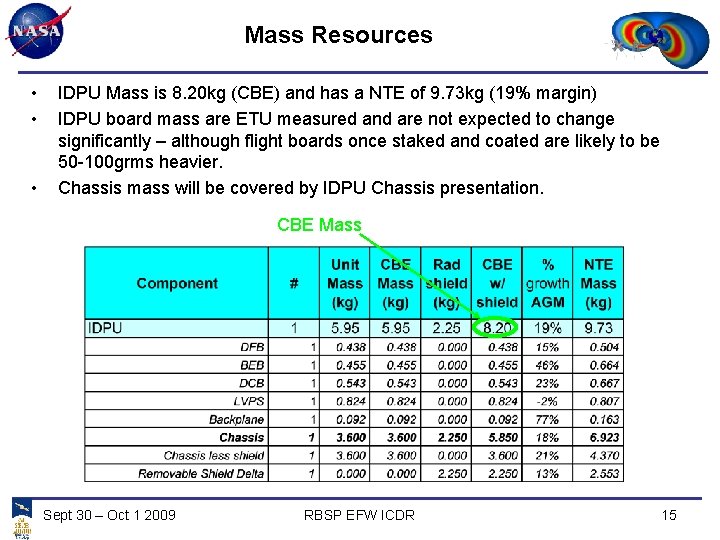

Mass Resources • • • IDPU Mass is 8. 20 kg (CBE) and has a NTE of 9. 73 kg (19% margin) IDPU board mass are ETU measured and are not expected to change significantly – although flight boards once staked and coated are likely to be 50 -100 grms heavier. Chassis mass will be covered by IDPU Chassis presentation. CBE Mass Sept 30 – Oct 1 2009 RBSP EFW ICDR 15

ETU Testing • DFB, DCB and BEB boards were integrated together in April / May. • LVPS integrated into IDPU in early August, in time for interface tests with EMFISIS in mid-August (see I&T presentation). • Interfaces between boards worked well, and there are no modifications to the interface for flight. • Further IDPU testing involving SPB/AXB deployment and LVPS/BEB Thermal testing is due to occur in September/October 09. • EMC Zap Test Q 4 2009. Sept 30 – Oct 1 2009 RBSP EFW ICDR 16

Subsystem Testing • Flight IDPU I&T Flow: – Individual IDPU boards delivered to IDPU for integration once they have met board requirements and completed test procedures. – Board to board interfaces are then verified. – Integration will follow written test procedure. – Unit is assembled in box and functionally tested (CPT). – IDPU then supports SPB/AXB testing (deployments / functionals). – IDPU boards are staked and coated. – IDPU then ready for remaining I&T / environments. – Further I&T descriptions are dealt in I&T presentation. Sept 30 – Oct 1 2009 RBSP EFW ICDR 17

Schedule IDPU Schedule is kept up to date and reported monthly. Key Dates: ETU IDPU delivery to I&T: August 2009 F 1 IDPU delivery to I&T: March 2010 F 1 Instrument I&T: June 2010 F 2 IDPU delivery to I&T: April 2010 F 2 Instrument I&T: July 2010 Sept 30 – Oct 1 2009 RBSP EFW ICDR 18

RBSP Radiation Belt Storm Probes Sept 30 – Oct 1 2009 Data Control Board (DCB) Critical Design Review Michael Ludlam Space Sciences Laboratory UC Berkeley RBSP EFW ICDR 19

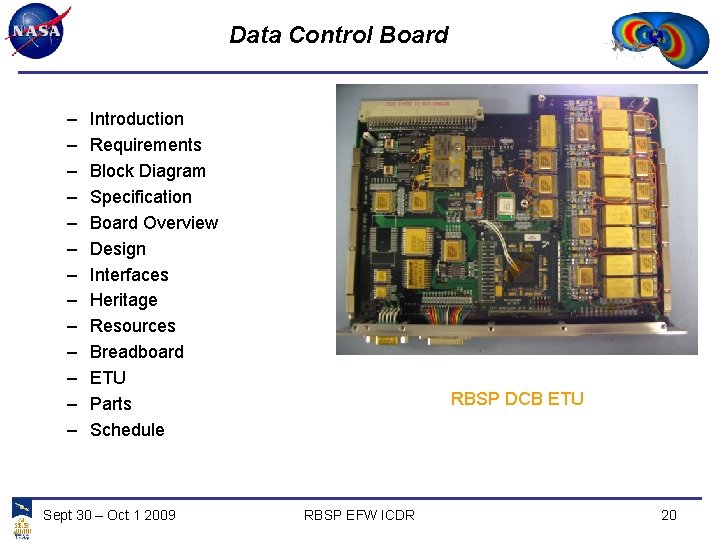

Data Control Board – – – – Introduction Requirements Block Diagram Specification Board Overview Design Interfaces Heritage Resources Breadboard ETU Parts Schedule Sept 30 – Oct 1 2009 RBSP DCB ETU RBSP EFW ICDR 20

DCB Introduction – Scope of Presentation • Gives overview of DCB board. • DCB FPGA Actel presentation follows and is only presented as a component in this presentation. • EFW FSW is detailed in a separate presentation. – Synopsis: The DCB card; • provides the digital interface between the S/C and the rest of the instrument. • receives, packetizes and stores science data before transmitting it to the spacecraft. • receives and transmits housekeeping to the spacecraft. • receives and acts on commands from the spacecraft. Sept 30 – Oct 1 2009 RBSP EFW ICDR 21

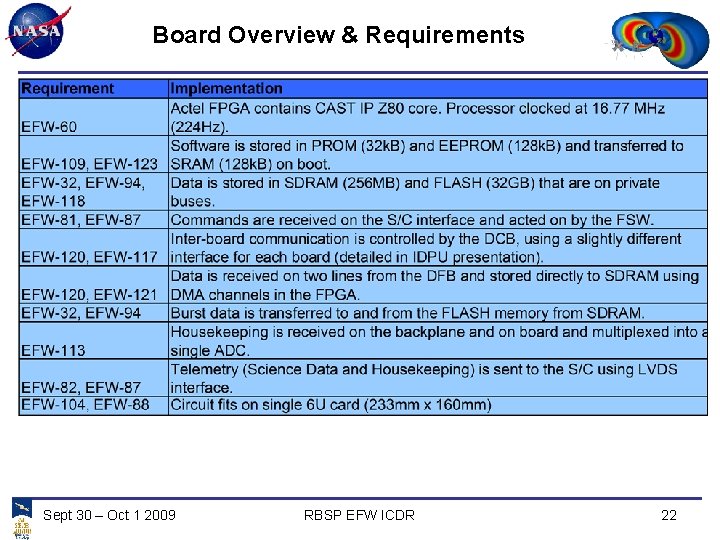

Board Overview & Requirements Sept 30 – Oct 1 2009 RBSP EFW ICDR 22

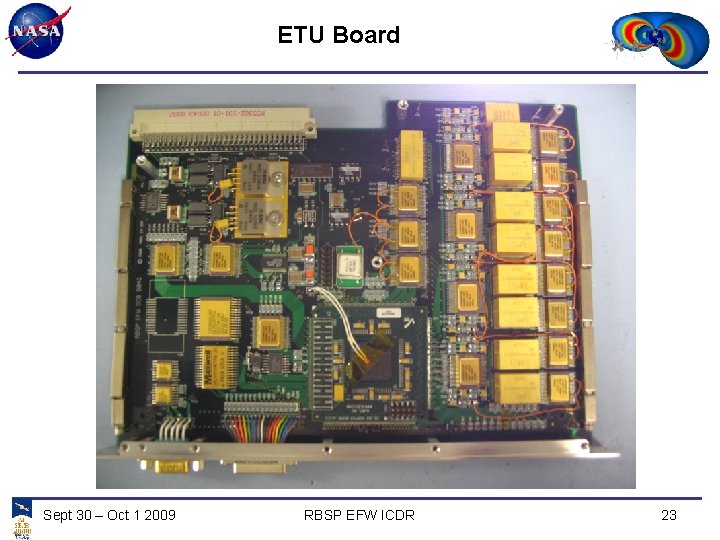

ETU Board Sept 30 – Oct 1 2009 RBSP EFW ICDR 23

FPGA & FSW Requirements • EFW requirements are flowed to subsystems and also used to derive FSW requirements. – RBSP_EFW_FSW_002 D • FSW Requirements specifically control more of the functionality of the DCB board than directly using the EFW requirements themselves. • FPGA requirements are flowed from the DCB board into the DCB FPGA specification. • Both the DCB Board and DCB FPGA specification are reviewed for completeness by the Systems Engineer, the FSW Engineer, the DCB Engineer and the DCB FPGA Engineer. Sept 30 – Oct 1 2009 RBSP EFW ICDR 24

Changes since PDR • • No changes to requirements since PDR for DCB board. No major component changes since PDR. Sept 30 – Oct 1 2009 RBSP EFW ICDR 25

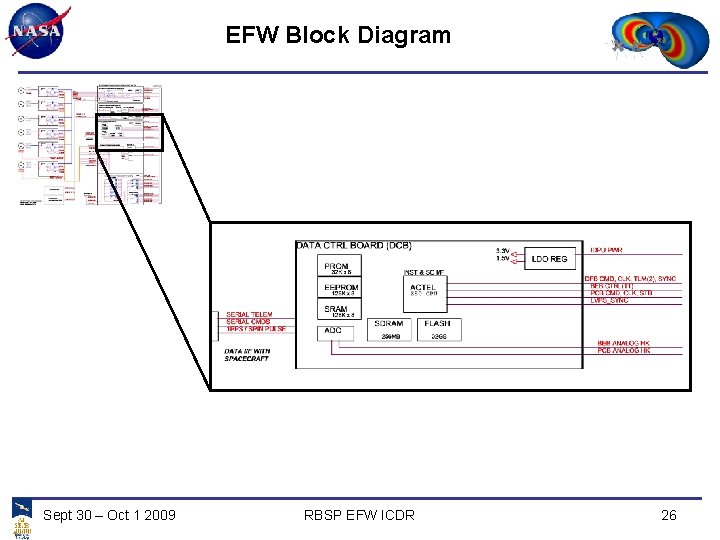

EFW Block Diagram Sept 30 – Oct 1 2009 RBSP EFW ICDR 26

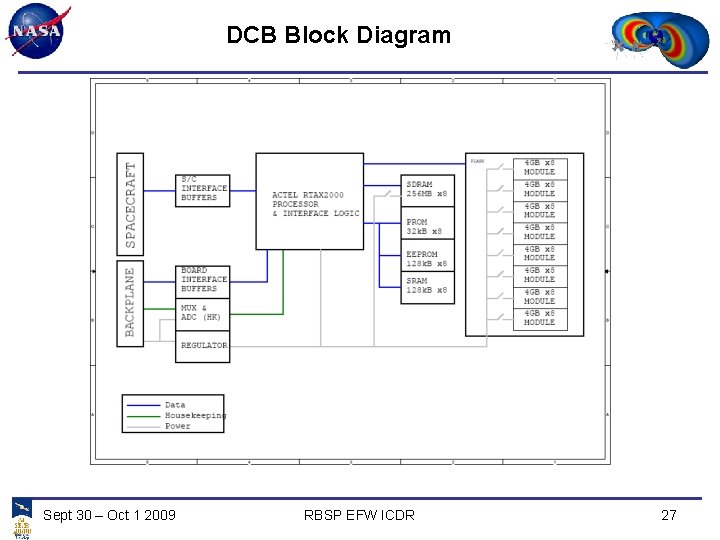

DCB Block Diagram Sept 30 – Oct 1 2009 RBSP EFW ICDR 27

DCB Specifications – DCB Board Specification Document: • RBSP_EFW_DCB_003 E_Specification – DCB FPGA Specification Document: • RBSP_EFW_DCB_001 N – FSW Specification Document: • RBSP_EFW_FSW_003_Specification – Mechanical ICD: • RBSP-IDP-MEC-011 Rev F Sept 30 – Oct 1 2009 RBSP EFW ICDR 28

– DCB also has an external 51 -way connector to debug board. Connector cover will be installed on delivery of FM IDPUs to APL. – Board built for ETU that allows alternative boot PROM / EEPROM and logic analyzer connections. – Will be used on flight board until flight PROM is burned and installed. Backplane – DCB has digital interface to S/C via 9 F DSub Connector (Instrument Commands, 1 PPS/SP, Instrument Telemetry). – Interface is defined in the APL Controlled EFW ICD (7417 -9083) –currently Rev. A. – Signal levels have been verified by APL provided Emulator. – Test planned with ETU IDPU at APL. Debug / Alternative Boot S/C Interfaces – Internal IDPU communications are routed on the 98 pin KA connector that connects to the backplane. – Verified during integration with other IDPU boards. No issues found during ETU testing. Sept 30 – Oct 1 2009 RBSP EFW ICDR 29

Heritage – Heritage • DCB is based on THEMIS equivalent board (also called the DCB). • Although processor is different (RBSP: Z 80, THEMIS: 8085) instruction set is compatible and allows reuse of FSW modules. • SDRAM, ADC and MUX is identical to one flown on THEMIS. • SRAM, EEPROM are 3. 3 V equivalent parts of those flown on THEMIS. – New for RBSP! • • • IP Core – Extensively tested on ETU. Flash – Extensively tested on ETU. LVDS – Extensively tested on ETU, APL recommended parts. MSK Regulator for 1. 5 V and 3. 3 V supplies. Extensively tested on ETU. RTAX FPGA – Not yet tested. Sept 30 – Oct 1 2009 RBSP EFW ICDR 30

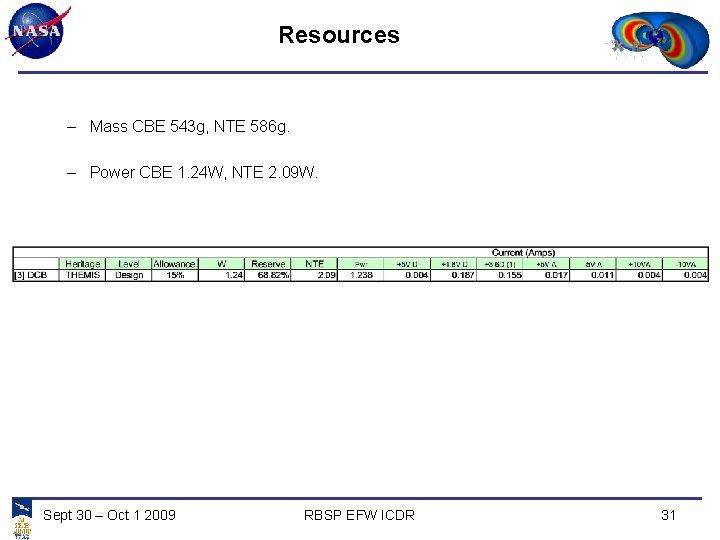

Resources – Mass CBE 543 g, NTE 586 g. – Power CBE 1. 24 W, NTE 2. 09 W. Sept 30 – Oct 1 2009 RBSP EFW ICDR 31

Radiation • All DCB Active parts are rad hard / rad tolerant or have undergone a TID test. (Board designed to TID of 33 k. Rad. ) • All DCB Active parts are SEL immune up to 80 Me. V/cm 2 or have a waiver. • Parts with waiver: – LTC 1604 (ADC) – Flash memory • Parts on S/C interface have been tested by APL for DDD. Sept 30 – Oct 1 2009 RBSP EFW ICDR 32

ETU Testing Results • Board tested to and met requirements. • Board has supported FSW, FPGA and IDPU testing without problems. • No major modifications have been necessary to the board. • One potential issue arose with the MSK regulator parts which require a large (0. 5 Amp) start up current. ETU Testing with the LVPS shows the power supply is able to support this. A more flight like load test is planned in September 09. Sept 30 – Oct 1 2009 RBSP EFW ICDR 33

DCB Flight Layout • • • Flight layout has been started and will be completed in early October. Minor Changes from ETU: – Buffers run as warm spare for the Flash & SDRAM. – Changed DIN 96 connector to the new KA 98 connector. – Removal of filter on regulator supplies (no longer necessary after SEU testing of parts). – Corrected switch to SDRAM and Flash – Minor changes to layout to correct layout errors – Added buffer enable control to the Flash to FPGA – Added Analog Spare nets to connector for spares. Differences between ETU and Flight: – FPGA on ETU board is Aldec adaptor board with A 3 P 1500 part. – Oscillator is commercial part. – Other parts are engineering versions of flight parts. Board will be manufactured from FR 4 (4101/26) Still to be done: – Minor tweaks of signal trace impedances. – Power Control Board (PCB) interface circuitry checkout Sept 30 – Oct 1 2009 RBSP EFW ICDR 34

Test Plan • Test plan was written for ETU testing – RBSP_EFW_DCB_004 – Prior to FPGA installation • Simple Power Up • POR • Oscillator check – After FPGA installation • Verification of signal integrity on board & board timing. • This will be developed into a test procedure for the flight board and run on the ETU first. • Once the board is populated and delivered to UCB, functionality that can be checked at a hardware only level will be verified, before handing over to FPGA verification and FSW verification. • Both flight boards will be assembled together. FPGA will be installed on one board and tested before second board has FPGA installed. Sept 30 – Oct 1 2009 RBSP EFW ICDR 35

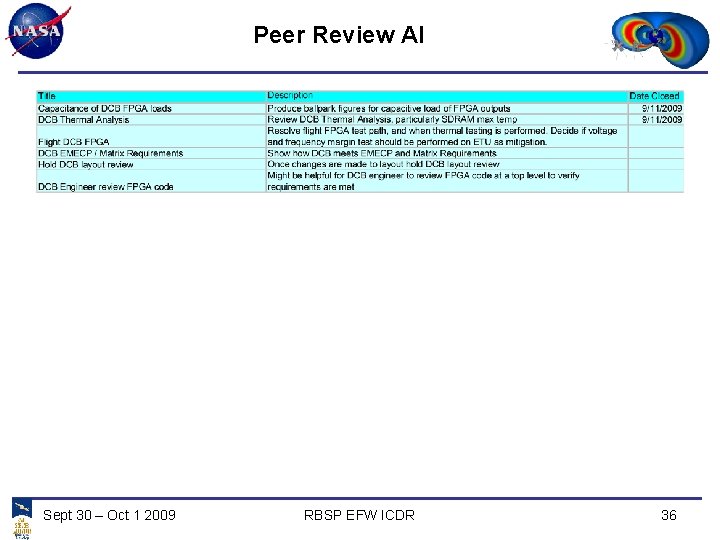

Peer Review AI Sept 30 – Oct 1 2009 RBSP EFW ICDR 36

IC Parts List & Status • All long lead parts are in house or due soon. • All parts meet derating defined in INST-002. • Although team has extensive experience with Actel parts, we have not yet programmed and run a RTAX part. • All other parts have been tested using ETU version or have recent flight history (THEMIS). Sept 30 – Oct 1 2009 RBSP EFW ICDR 37

Handling • • Flight boards will be assembled by approved external contractor (Jackson and Tull). Board handled with gloves / ESD strap at all times during functional checkout / board verification. After functional tests are complete the board will be cleaned before being staked and coated. Board then only unbagged in cleanroom. Sept 30 – Oct 1 2009 RBSP EFW ICDR 38

Schedule Board is ready for flight. Board layout and fabrication due to happen in October 2009 Assembly in November 2009 Test in December 2009 DCB progress is tracked in the IDPU Schedule. Sept 30 – Oct 1 2009 RBSP EFW ICDR 39

- Slides: 39