Quelle www wikipedia org Fachreferat von Mathias Herbst

Quelle: www. wikipedia. org Fachreferat von Mathias Herbst

Gliederung Definition Rahmenbedingungen Aufbau Entwicklungsschritte

Definition: Bei eingebetteten Systemen handelt es sich um Rechenmaschinen die, für den Benutzer weitestgehend unsichtbar, in elektrischen Maschinen „eingebettet“ sind. Diese Rechenmaschinen stimmen im grundsätzlichem Aufbau mit der Funktionsweise eines „normalen“ Desktop Rechners überein, sind jedoch je nach geforderter Funktion unterschiedlich.

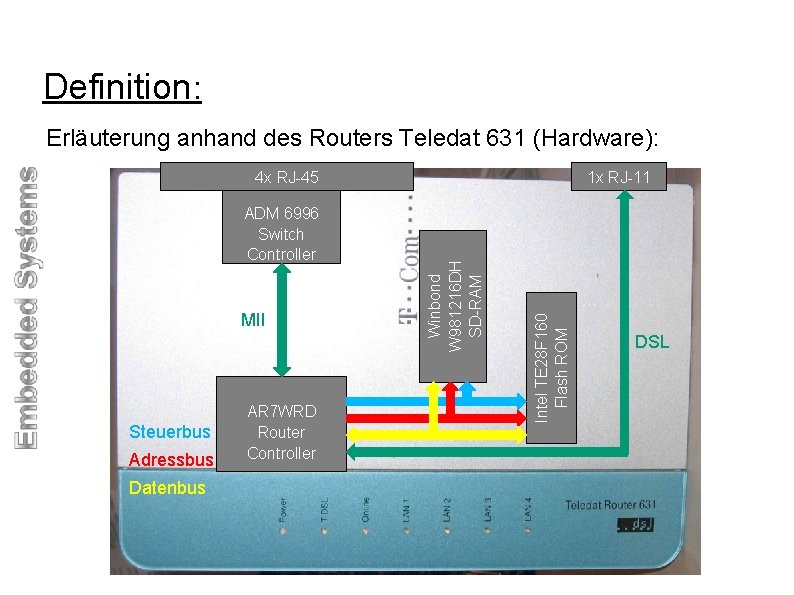

Definition: Erläuterung anhand des Routers Teledat 631 (Hardware): MII Steuerbus Adressbus Datenbus AR 7 WRD Router Controller Intel TE 28 F 160 Flash ROM ADM 6996 Switch Controller 1 x RJ-11 Winbond W 981216 DH SD-RAM 4 x RJ-45 DSL

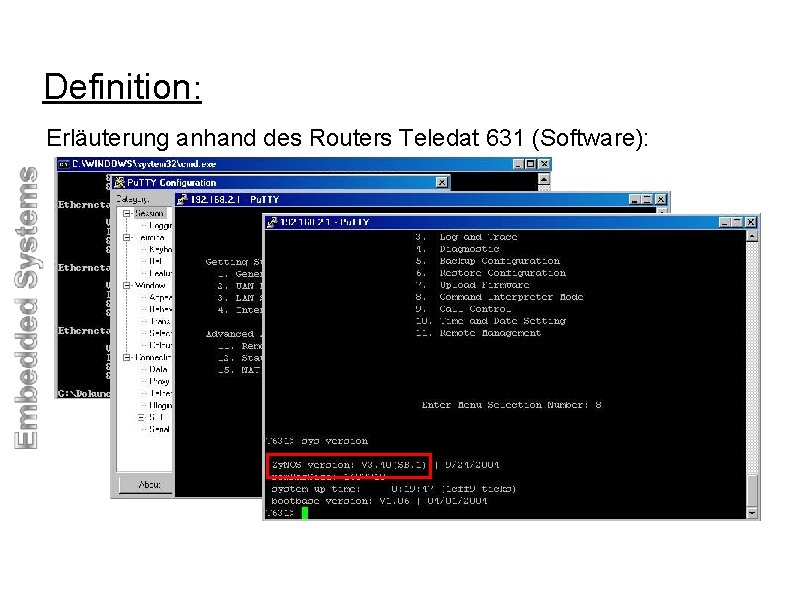

Definition: Erläuterung anhand des Routers Teledat 631 (Software):

Rahmenbedingungen: Embedded Systeme führen eine Funktion wiederholt aus (Routingentscheidungen des Teledat). Embedded Systeme sind an enge Randbedingungen gebunden im Bezug auf Produktionskosten, Größe, . . . (Größe und Kosten z. B. bei einem MP 3 Spieler). Embedded Systeme reagieren in Echtzeit auf Ihre Umwelt. (ABS bei einem Auto). Man unterscheidet hier zwischen harter und weicher Echtzeit.

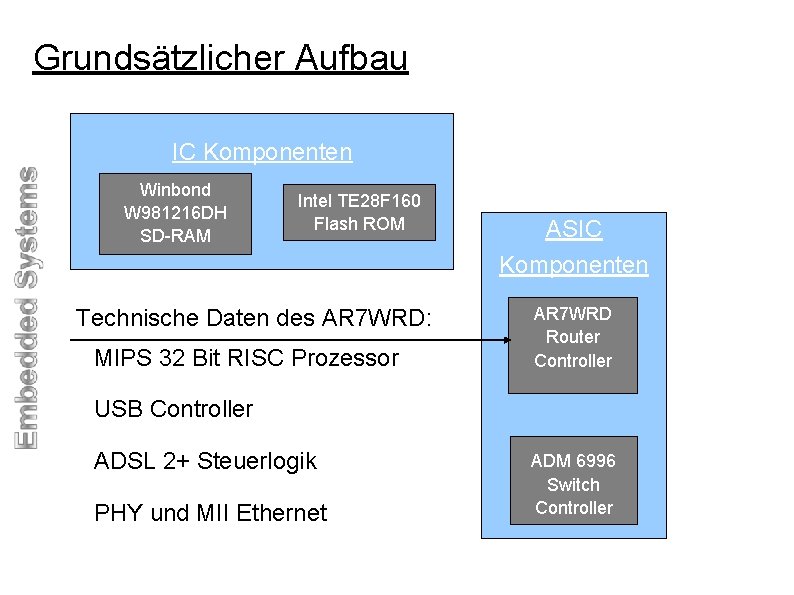

Grundsätzlicher Aufbau IC Komponenten Winbond W 981216 DH SD-RAM Intel TE 28 F 160 Flash ROM Technische Daten des AR 7 WRD: MIPS 32 Bit RISC Prozessor ASIC Komponenten AR 7 WRD Router Controller USB Controller ADSL 2+ Steuerlogik PHY und MII Ethernet ADM 6996 Switch Controller

Grundsätzlicher Aufbau ASIC Komponenten Application Specific Integrated Circuit: IC Komponenten ASICs sind ICs, die nur für die Anwendung in einem bestimmten Produkt entwickelt und produziert werden. Integrated Circuit: ICs, stellen im Gegensatz dazu eine Lösung für den Markt dar.

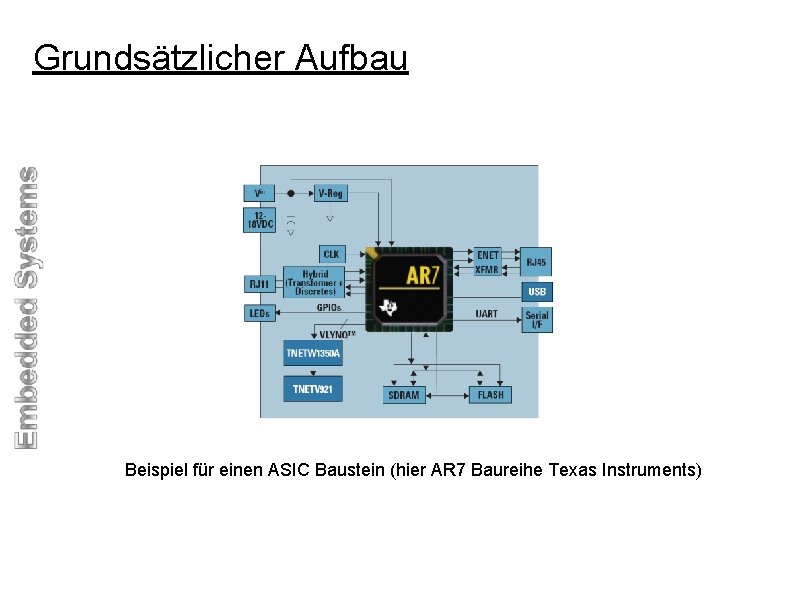

Grundsätzlicher Aufbau ASIC Komponenten Beispiel für einen ASIC Baustein (hier AR 7 Baureihe Texas Instruments)

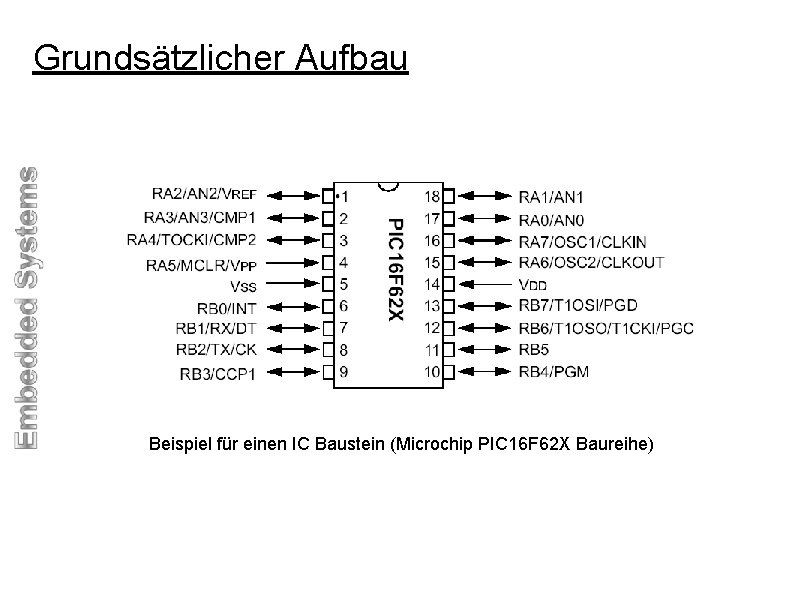

Grundsätzlicher Aufbau ASIC Komponenten Beispiel für einen IC Baustein (Microchip PIC 16 F 62 X Baureihe)

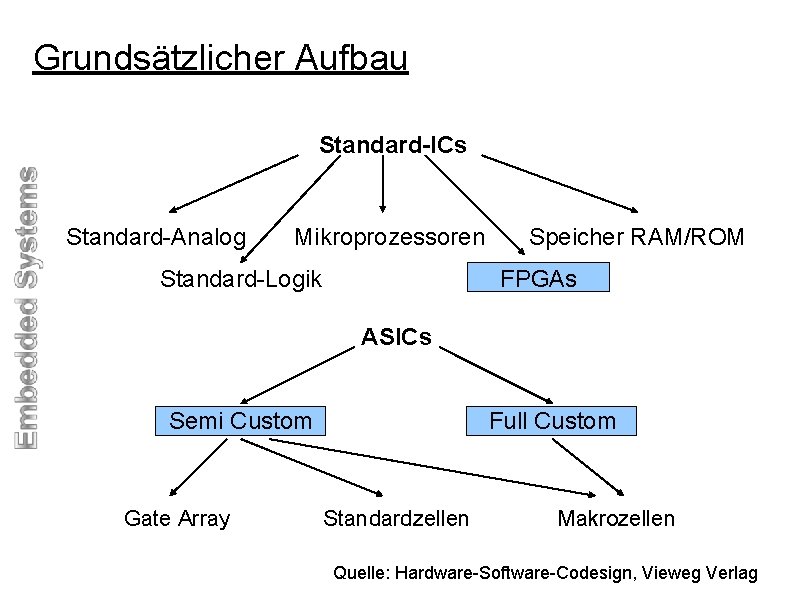

Grundsätzlicher Aufbau Standard-ICs Standard-Analog Mikroprozessoren Standard-Logik Speicher RAM/ROM FPGAs ASICs Semi Custom Gate Array Full Custom Standardzellen Makrozellen Quelle: Hardware-Software-Codesign, Vieweg Verlag

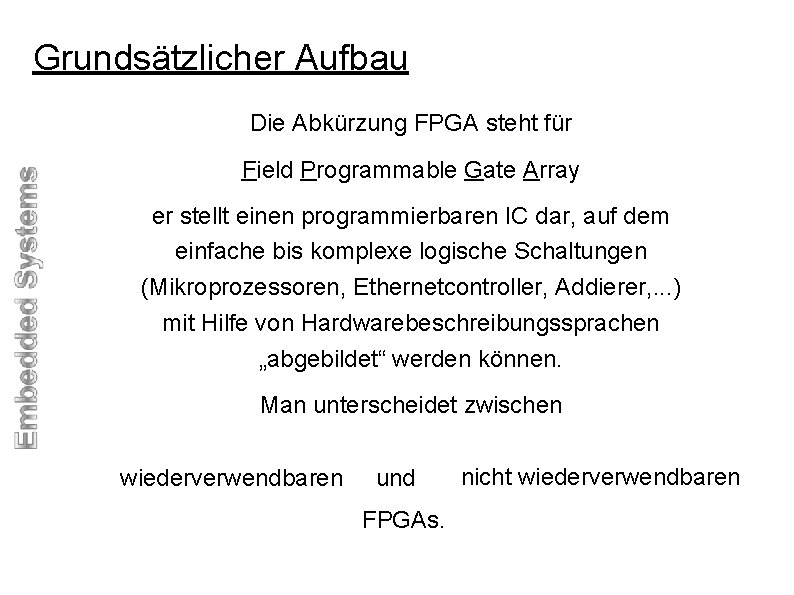

Grundsätzlicher Aufbau Die Abkürzung FPGA steht für Field Programmable Gate Array er stellt einen programmierbaren IC dar, auf dem einfache bis komplexe logische Schaltungen (Mikroprozessoren, Ethernetcontroller, Addierer, . . . ) mit Hilfe von Hardwarebeschreibungssprachen „abgebildet“ werden können. Man unterscheidet zwischen wiederverwendbaren und FPGAs. nicht wiederverwendbaren

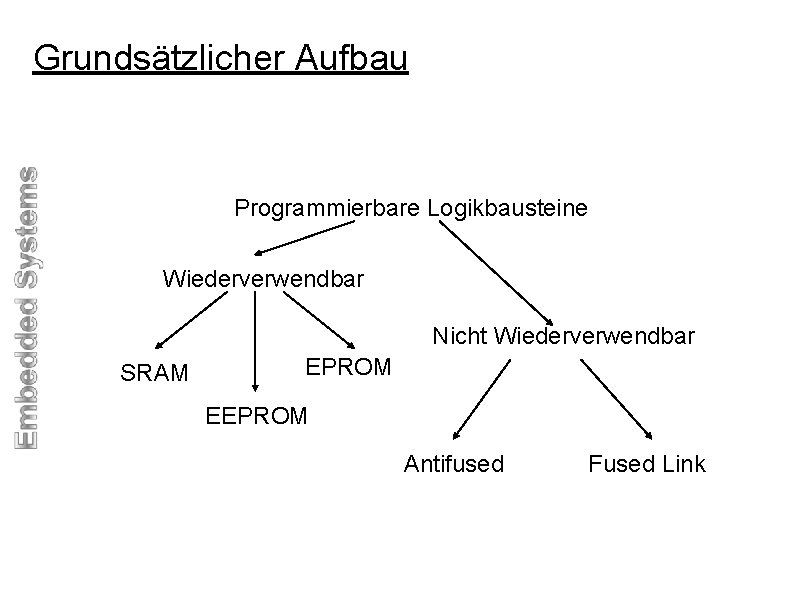

Grundsätzlicher Aufbau Programmierbare Logikbausteine Wiederverwendbar Nicht Wiederverwendbar SRAM EPROM EEPROM Antifused Fused Link

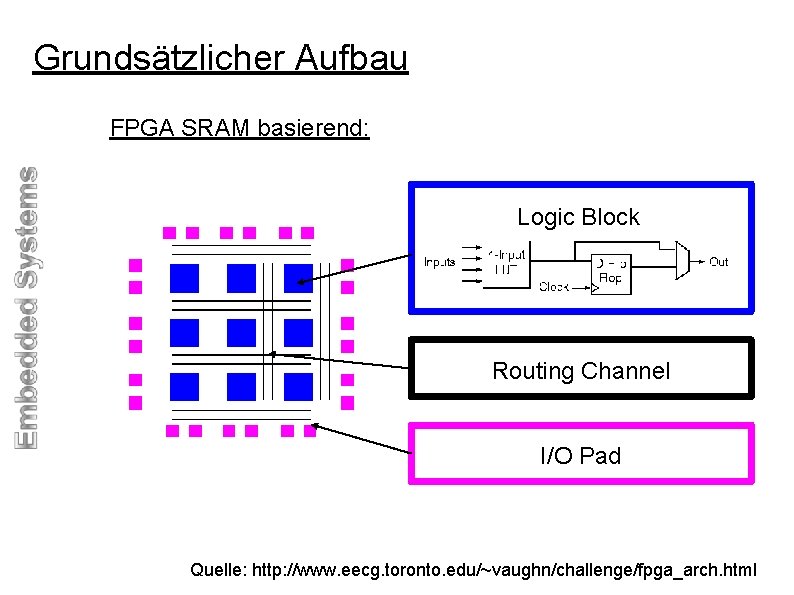

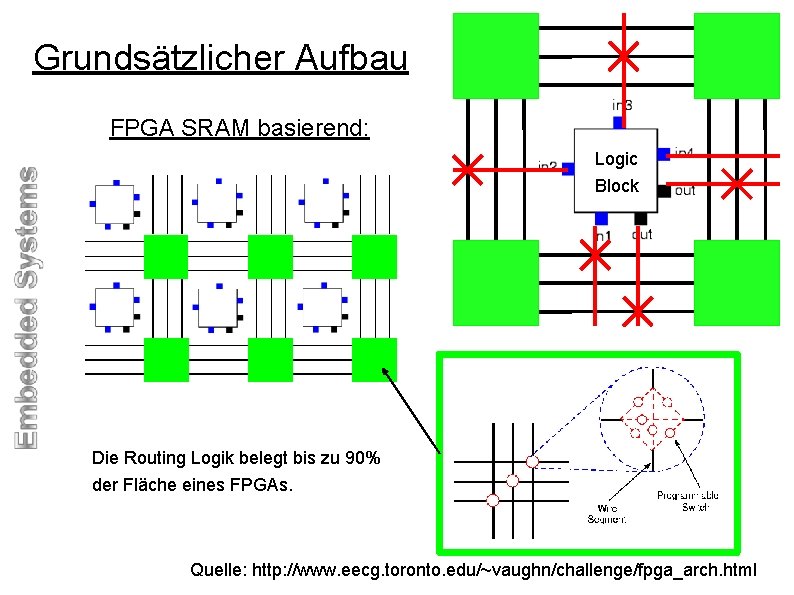

Grundsätzlicher Aufbau FPGA SRAM basierend: Logic Block Routing Channel I/O Pad Quelle: http: //www. eecg. toronto. edu/~vaughn/challenge/fpga_arch. html

Grundsätzlicher Aufbau FPGA SRAM basierend: Logic Block Die Routing Logik belegt bis zu 90% der Fläche eines FPGAs. Quelle: http: //www. eecg. toronto. edu/~vaughn/challenge/fpga_arch. html

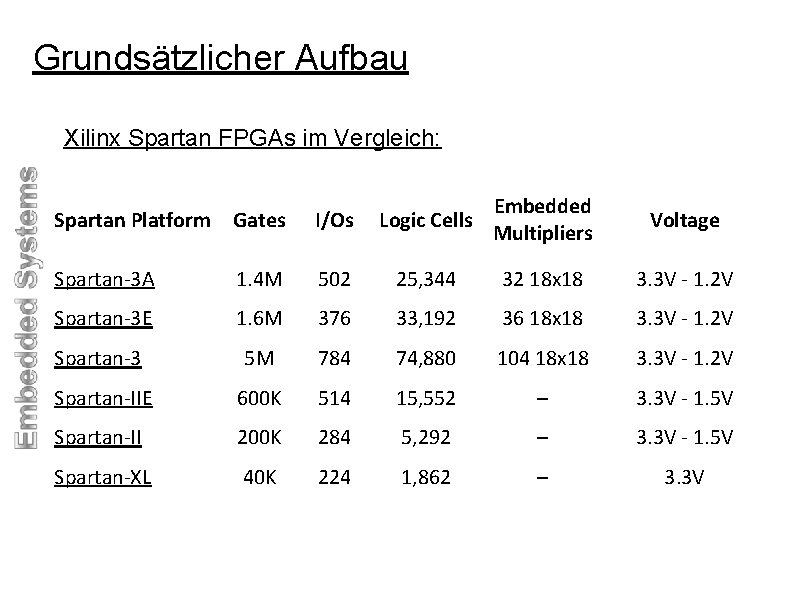

Grundsätzlicher Aufbau Xilinx Spartan FPGAs im Vergleich: Spartan Platform Gates I/Os Logic Cells Embedded Multipliers Voltage Spartan-3 A 1. 4 M 502 25, 344 32 18 x 18 3. 3 V - 1. 2 V Spartan-3 E 1. 6 M 376 33, 192 36 18 x 18 3. 3 V - 1. 2 V Spartan-3 5 M 784 74, 880 104 18 x 18 3. 3 V - 1. 2 V Spartan-IIE 600 K 514 15, 552 – 3. 3 V - 1. 5 V Spartan-II 200 K 284 5, 292 – 3. 3 V - 1. 5 V Spartan-XL 40 K 224 1, 862 – 3. 3 V

Grundsätzlicher Aufbau Anwendung von FPGAs: Im Parallelrechner COPACABANA der Universitäten Bochum und Kiel werden 120 FPGAs eingesetzt um die DES Verschlüsselung zu brechen. Die FPGAs sind vom Typ Spartan 3(1000). Bild: www. wikipedia. de

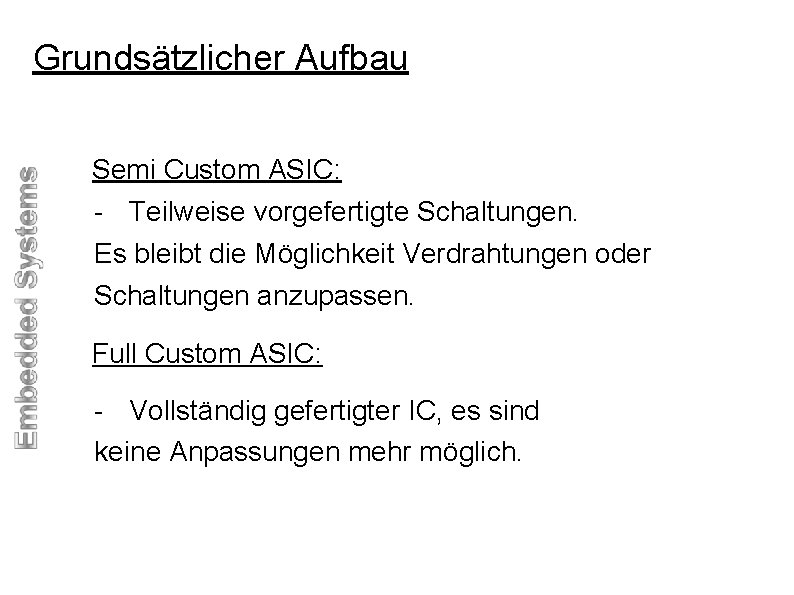

Grundsätzlicher Aufbau Semi Custom ASIC: - Teilweise vorgefertigte Schaltungen. Es bleibt die Möglichkeit Verdrahtungen oder Schaltungen anzupassen. Full Custom ASIC: - Vollständig gefertigter IC, es sind keine Anpassungen mehr möglich.

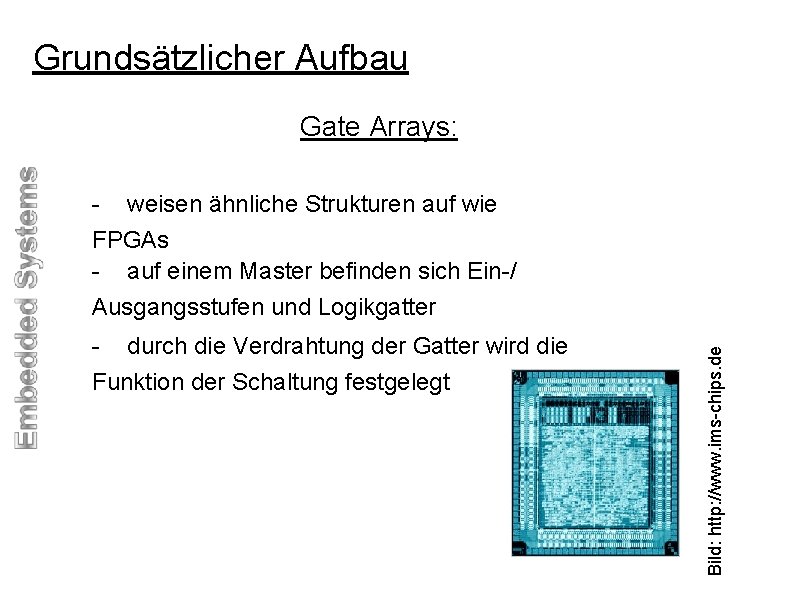

Grundsätzlicher Aufbau Gate Arrays: - durch die Verdrahtung der Gatter wird die Funktion der Schaltung festgelegt Bild: http: //www. ims-chips. de - weisen ähnliche Strukturen auf wie FPGAs - auf einem Master befinden sich Ein-/ Ausgangsstufen und Logikgatter

Grundsätzlicher Aufbau Standardzellen: - weisen keine vorgefertigten Strukturen auf - Grundfunktionen sind in Bibliotheken abgelegt (z. B. Logikgatter) Makrozellen: - vereinen die Vorteile von Gate Arrays und Standardzellen

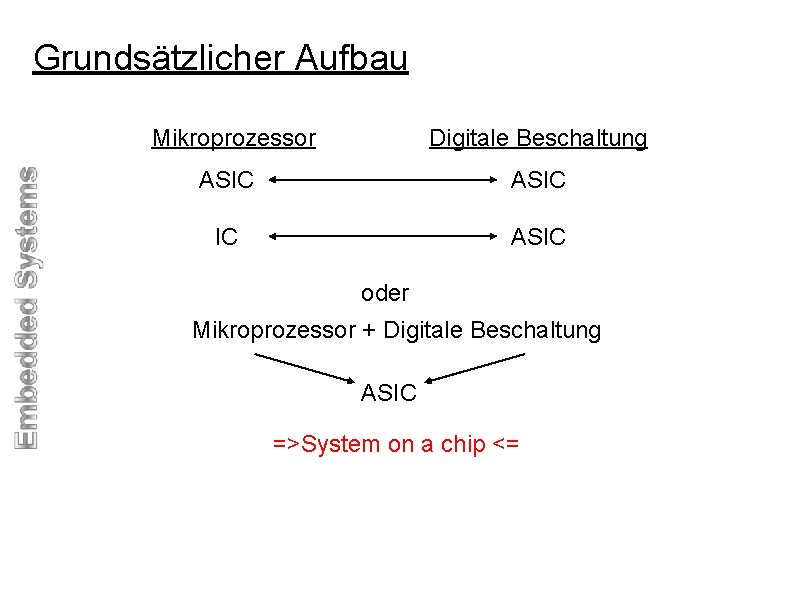

Grundsätzlicher Aufbau Mikroprozessor Digitale Beschaltung ASIC IC ASIC oder Mikroprozessor + Digitale Beschaltung ASIC =>System on a chip <=

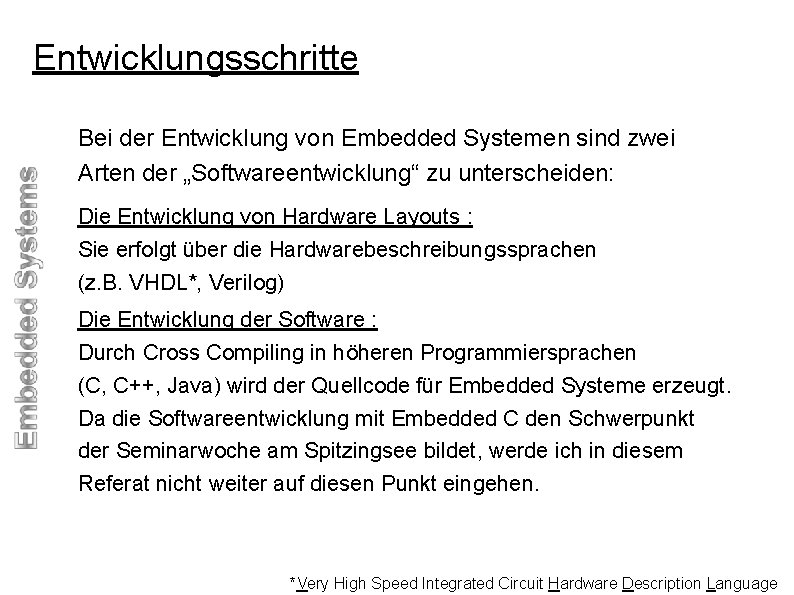

Entwicklungsschritte Bei der Entwicklung von Embedded Systemen sind zwei Arten der „Softwareentwicklung“ zu unterscheiden: Die Entwicklung von Hardware Layouts : Sie erfolgt über die Hardwarebeschreibungssprachen (z. B. VHDL*, Verilog) Die Entwicklung der Software : Durch Cross Compiling in höheren Programmiersprachen (C, C++, Java) wird der Quellcode für Embedded Systeme erzeugt. Da die Softwareentwicklung mit Embedded C den Schwerpunkt der Seminarwoche am Spitzingsee bildet, werde ich in diesem Referat nicht weiter auf diesen Punkt eingehen. *Very High Speed Integrated Circuit Hardware Description Language

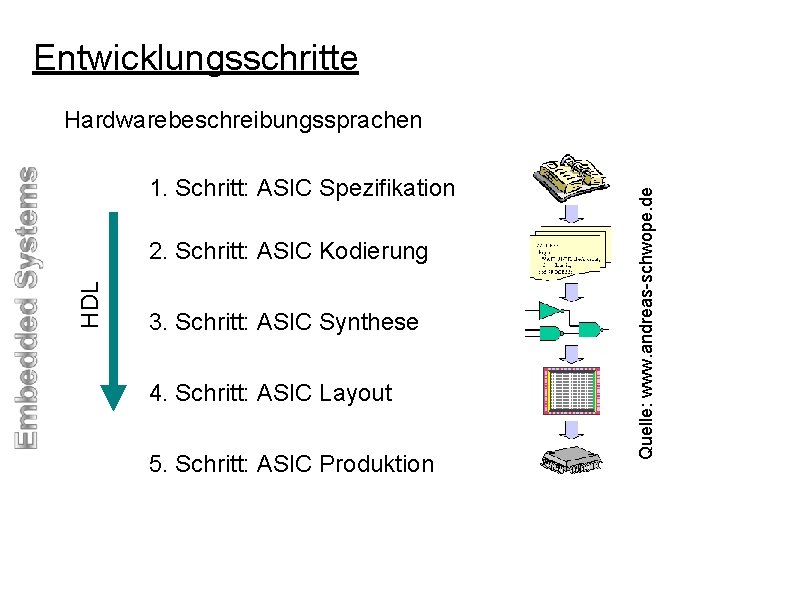

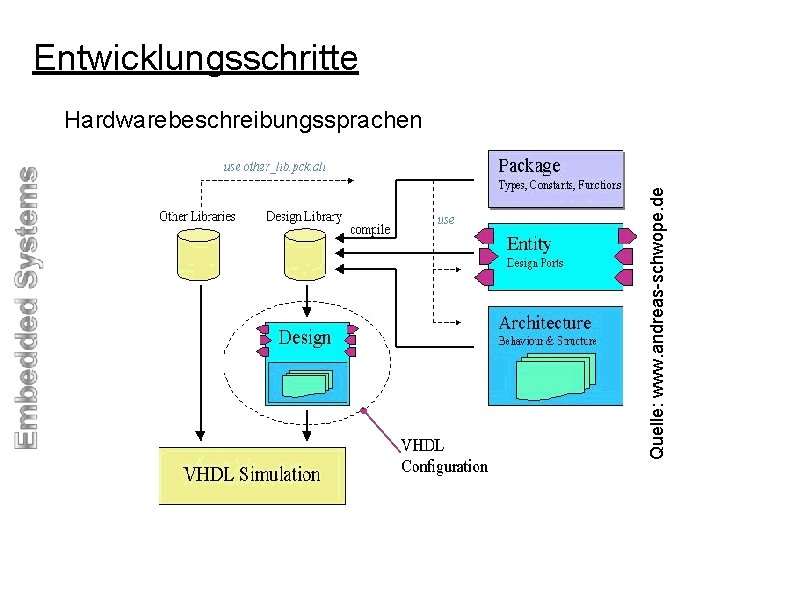

Entwicklungsschritte 1. Schritt: ASIC Spezifikation HDL 2. Schritt: ASIC Kodierung 3. Schritt: ASIC Synthese 4. Schritt: ASIC Layout 5. Schritt: ASIC Produktion Quelle: www. andreas-schwope. de Hardwarebeschreibungssprachen

Entwicklungsschritte Quelle: www. andreas-schwope. de Hardwarebeschreibungssprachen

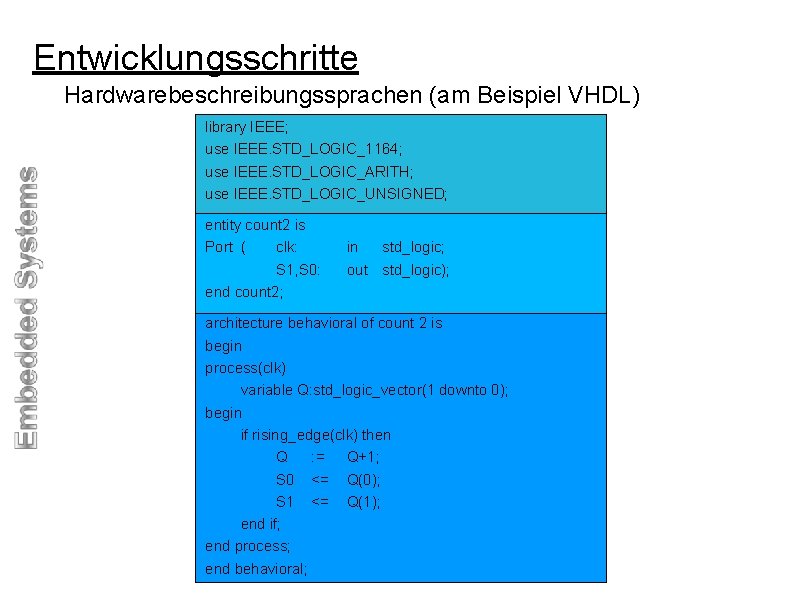

Entwicklungsschritte Hardwarebeschreibungssprachen (am Beispiel VHDL) library IEEE; use IEEE. STD_LOGIC_1164; use IEEE. STD_LOGIC_ARITH; use IEEE. STD_LOGIC_UNSIGNED; entity count 2 is Port ( clk: S 1, S 0: end count 2; in std_logic; out std_logic); architecture behavioral of count 2 is begin process(clk) variable Q: std_logic_vector(1 downto 0); begin if rising_edge(clk) then Q : = Q+1; S 0 <= Q(0); S 1 <= Q(1); end if; end process; end behavioral;

Entwicklungsschritte Hardwarebeschreibungssprachen Durch HDL erzeugte Schaltungen werden als Intellectual Property bezeichnet. Diese IP Cores können in Form von Softcores und Hardcores beim FPGA bzw. ASIC Entwurf genutzt werden.

FRAGEN? Quellen: www. andreas-schwope. de www. xilinx. com www. eecg. toronto. edu www. wikipedia. de www. wikipedia. org Hardware-Software-Codesign, Vieweg Verlag, ISBN 978 -3 -8348 -0048 -0

- Slides: 27