Quartus ROM ROM table 1 File New Memory

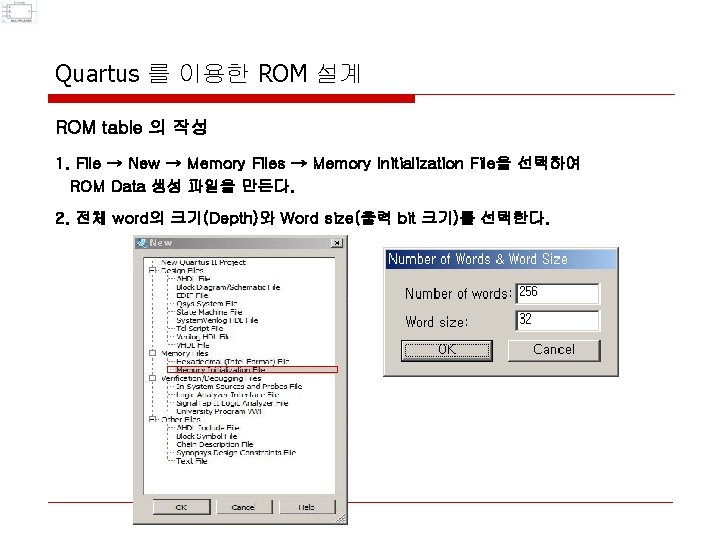

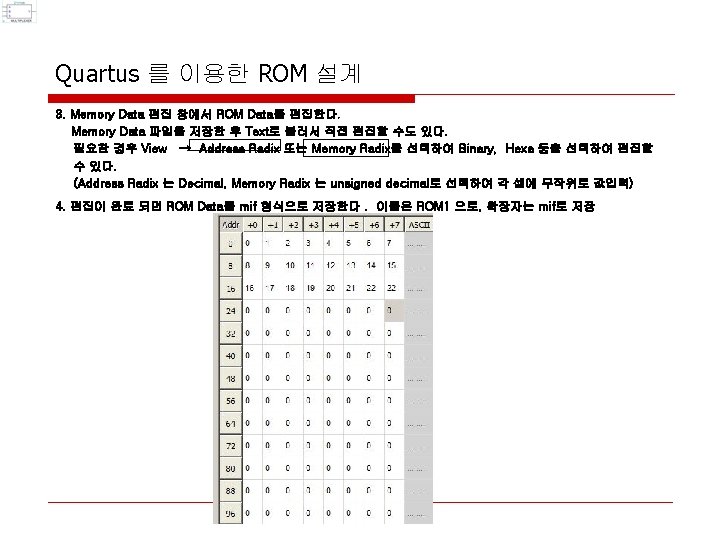

Quartus 를 이용한 ROM 설계 ROM table 의 작성 1. File → New → Memory Files → Memory Initialization File을 선택하여 ROM Data 생성 파일을 만든다. 2. 전체 word의 크기(Depth)와 Word size(출력 bit 크기)를 선택한다.

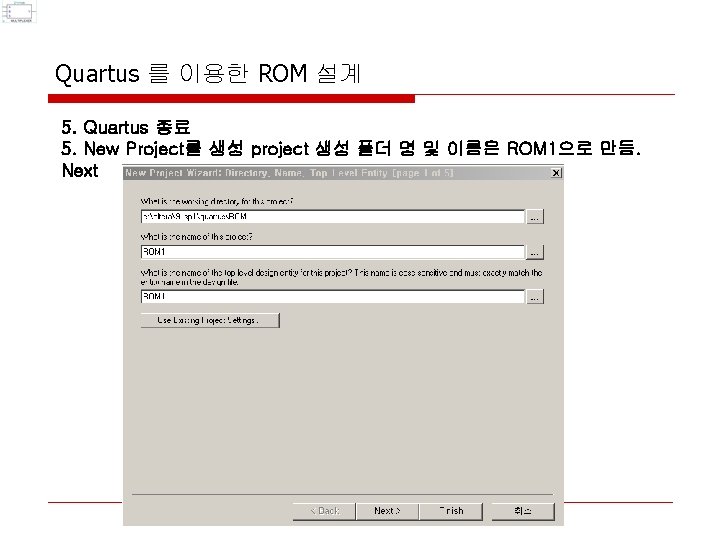

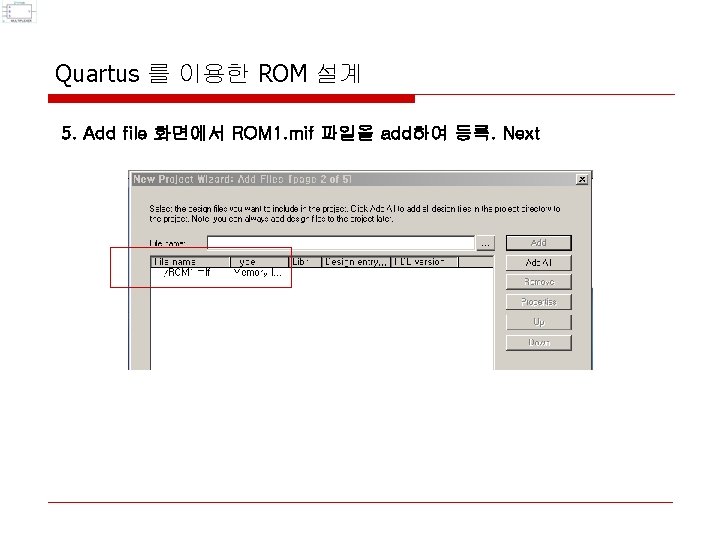

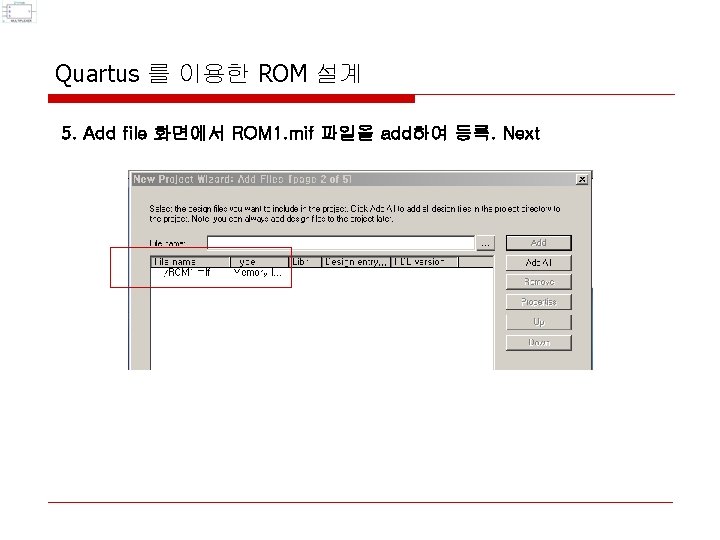

Quartus 를 이용한 ROM 설계 5. Add file 화면에서 ROM 1. mif 파일을 add하여 등록. Next

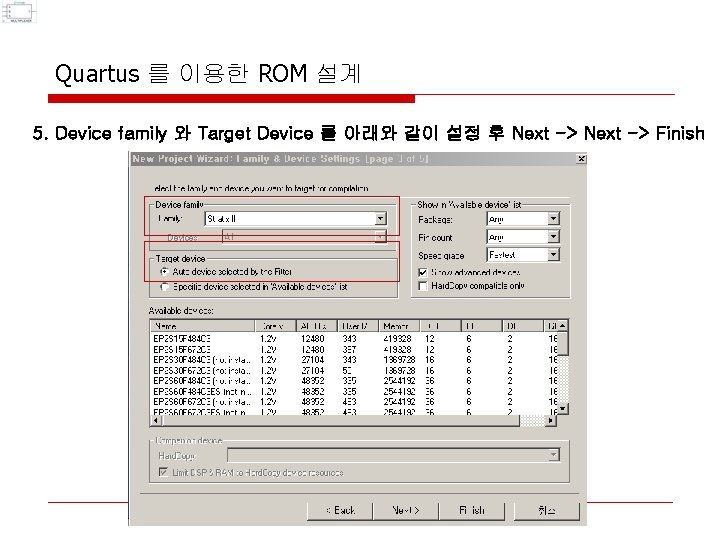

Quartus 를 이용한 ROM 설계 5. Device family 와 Target Device 를 아래와 같이 설정 후 Next -> Finish

Quartus 를 이용한 ROM 설계 5. Add file 화면에서 ROM 1. mif 파일을 add하여 등록. Next

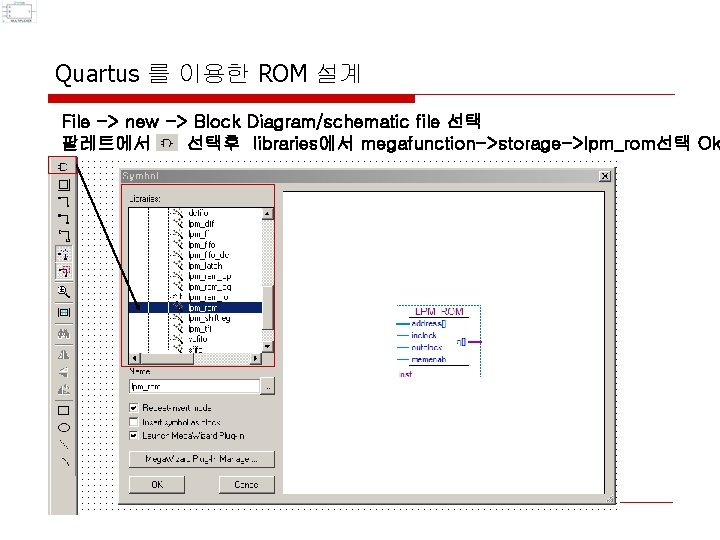

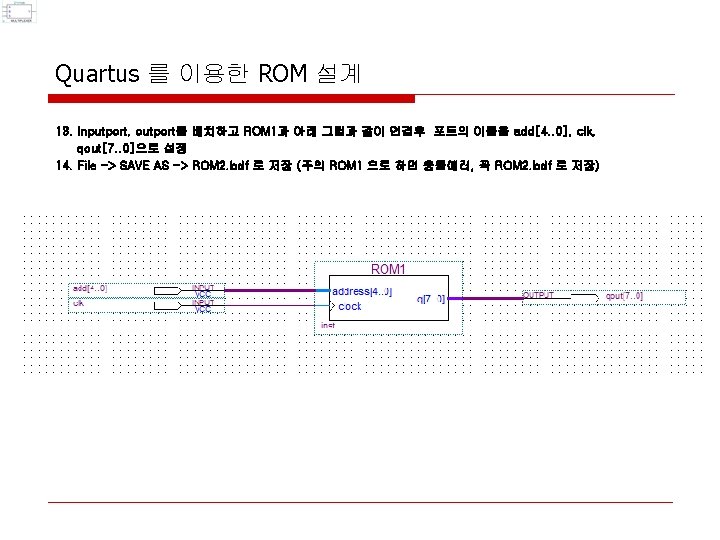

Quartus 를 이용한 ROM 설계 File -> new -> Block Diagram/schematic file 선택 팔레트에서 선택후 libraries에서 megafunction->storage->lpm_rom선택 Ok

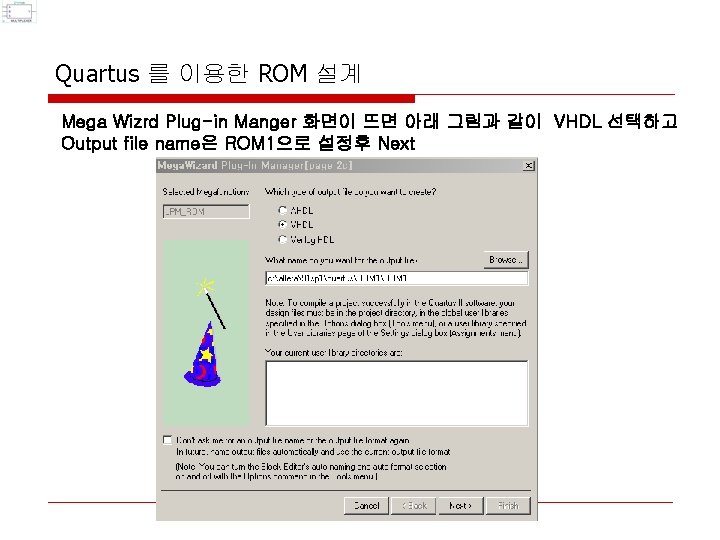

Quartus 를 이용한 ROM 설계 Mega Wizrd Plug-in Manger 화면이 뜨면 아래 그림과 같이 VHDL 선택하고 Output file name은 ROM 1으로 설정후 Next

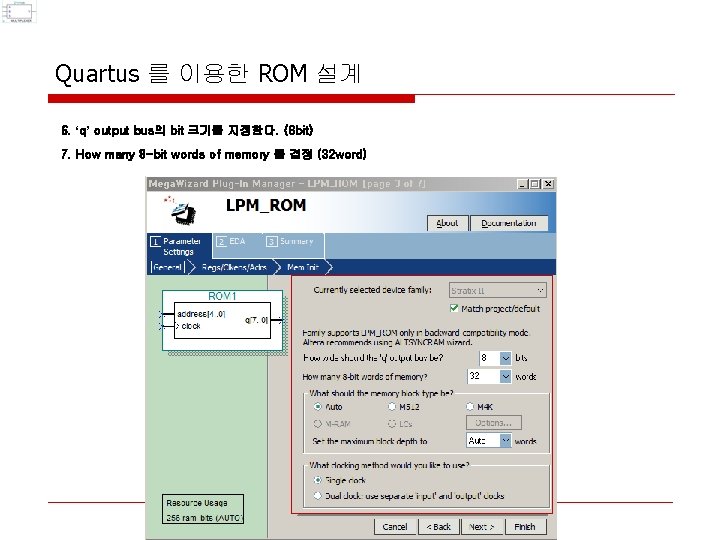

Quartus 를 이용한 ROM 설계 6. ‘q’ output bus의 bit 크기를 지정한다. (8 bit) 7. How many 8 -bit words of memory 를 결정 (32 word)

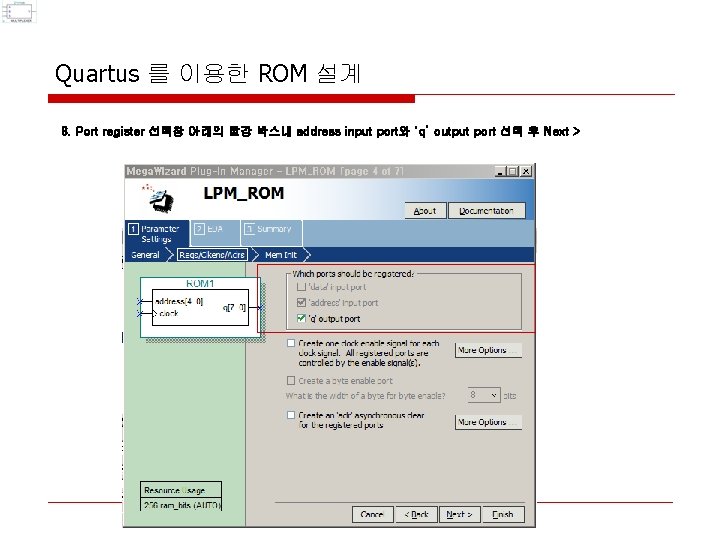

Quartus 를 이용한 ROM 설계 8. Port register 선택창 아래의 빨강 박스내 address input port와 ‘q’ output port 선택 후 Next >

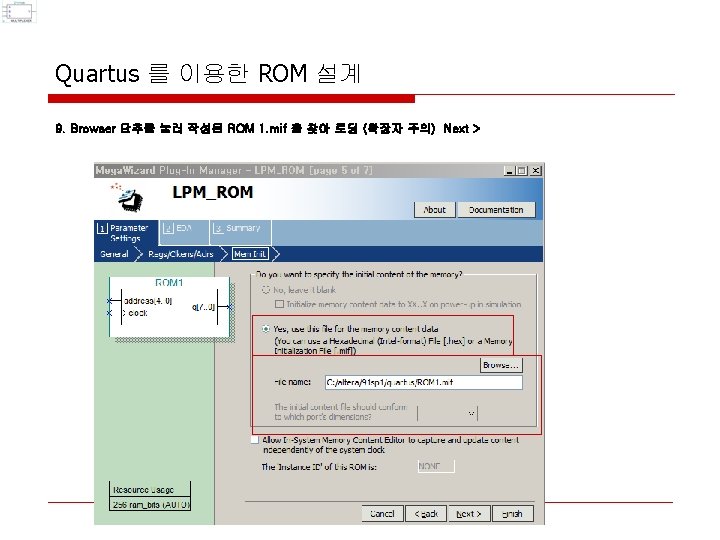

Quartus 를 이용한 ROM 설계 10. 화면 아래쪽의 Generate netlist 체크 하고 NEXT

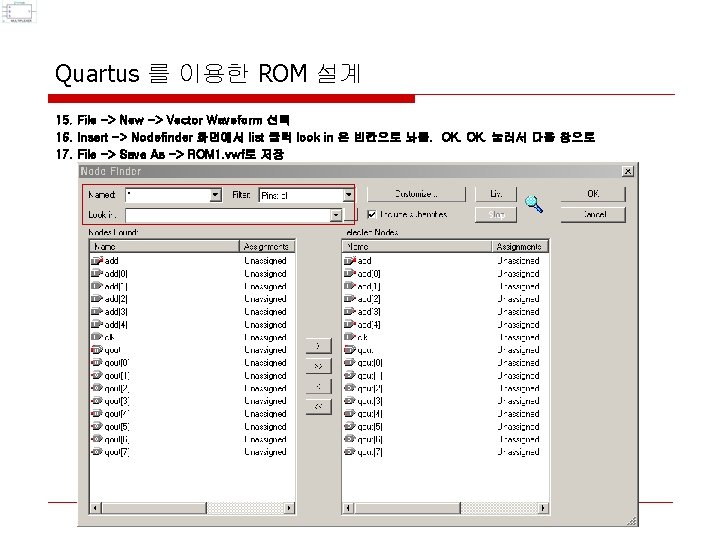

Quartus 를 이용한 ROM 설계 15. File -> New -> Vector Waveform 선택 16. Insert -> Nodefinder 화면에서 list 클릭 look in 은 빈칸으로 놔둠. OK. 눌러서 다음 창으로 17. File -> Save As -> ROM 1. vwf로 저장

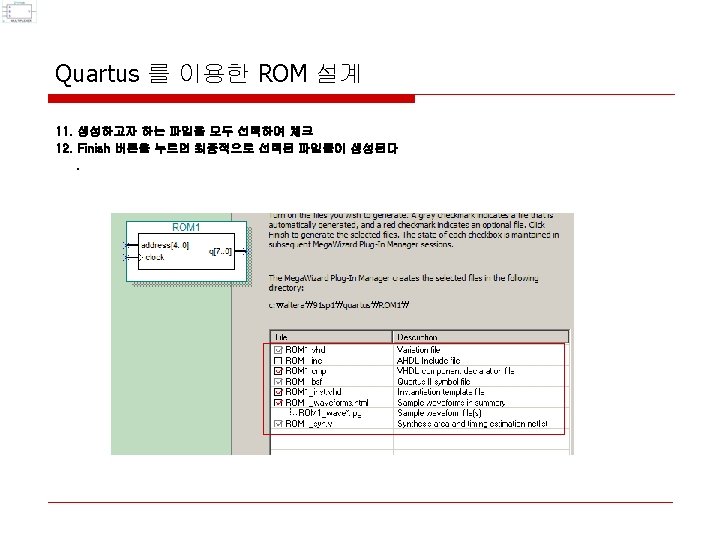

![Quartus 를 이용한 ROM 설계 18. Vector Waveform 화면에 서 를 이용하여 add[0] 는 Quartus 를 이용한 ROM 설계 18. Vector Waveform 화면에 서 를 이용하여 add[0] 는](http://slidetodoc.com/presentation_image_h/2879bf0a5ba801b8364a904334f4bad6/image-16.jpg)

Quartus 를 이용한 ROM 설계 18. Vector Waveform 화면에 서 를 이용하여 add[0] 는 주기를 10 ns, add[1]은 20 ns, add[2]는 30 ns, add[3]는 40 ns, add[4]는 50 ns로 설정 19. Clk 는 5 ns로 설정 20. 설정후 ROM 1. vwf 파일 재 저장 21. Processing -> Generte functional simulation netlist 클릭 22. Processing -> Simulator tool 클릭 -> simulation mode를 timing 에서 functional 로 교체 (다음 ppt)

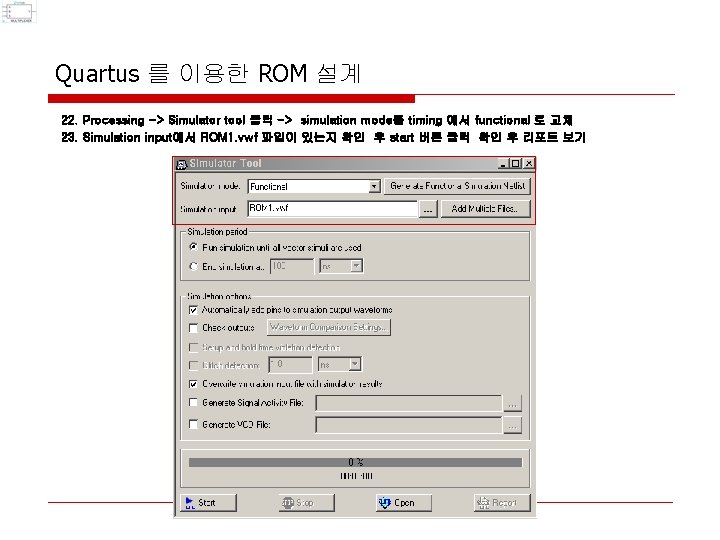

Quartus 를 이용한 ROM 설계 22. Processing -> Simulator tool 클릭 -> simulation mode를 timing 에서 functional 로 교체 23. Simulation input에서 ROM 1. vwf 파일이 있는지 확인 후 start 버튼 클릭 확인 후 리포트 보기

- Slides: 17