q file identifier filetype open fileopenkindexpression is stringexpression

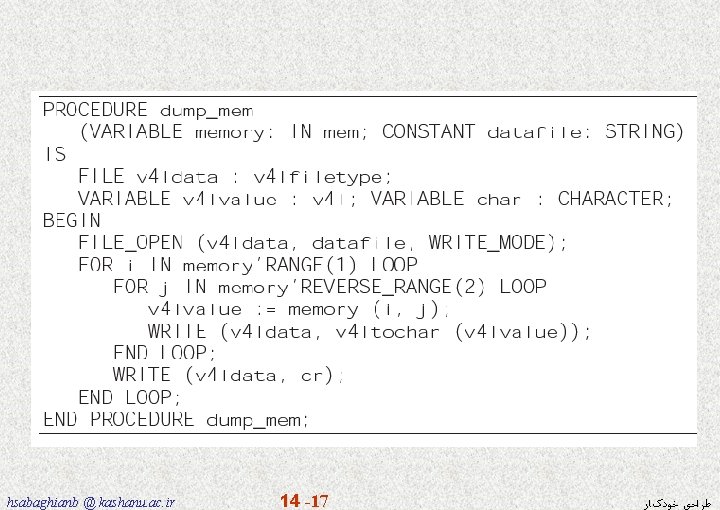

- Slides: 14

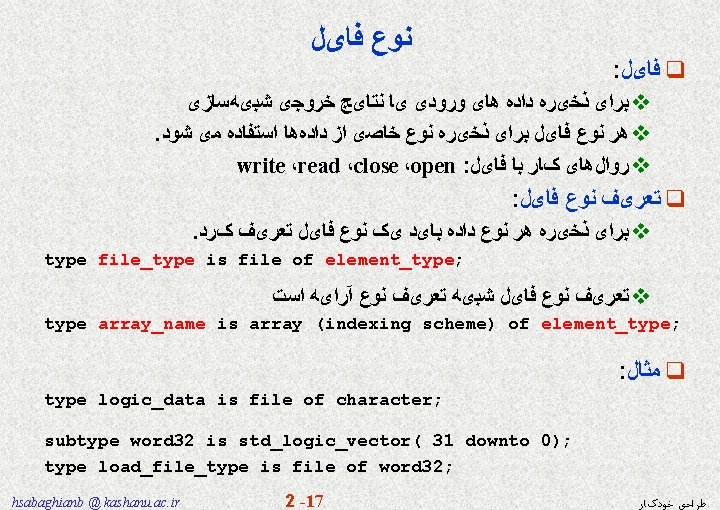

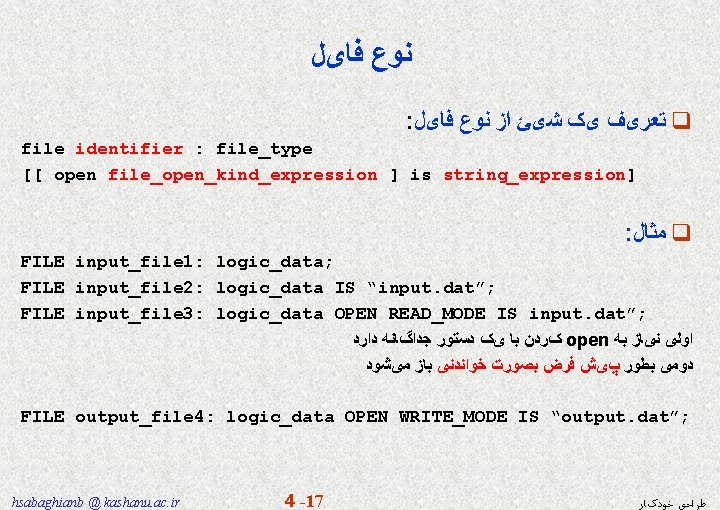

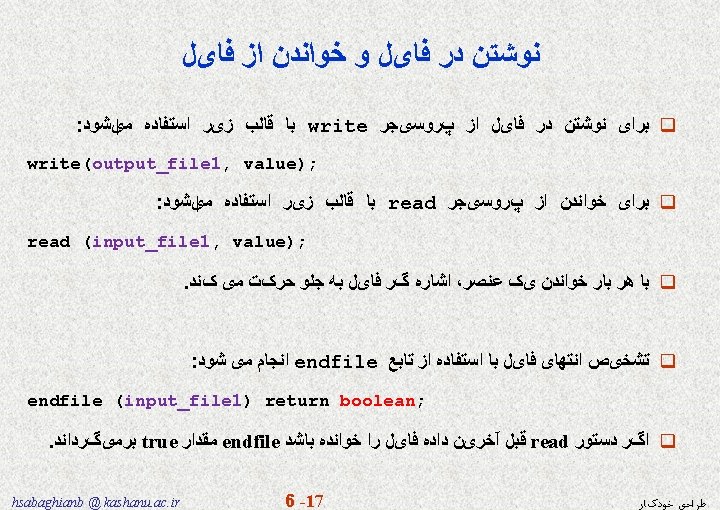

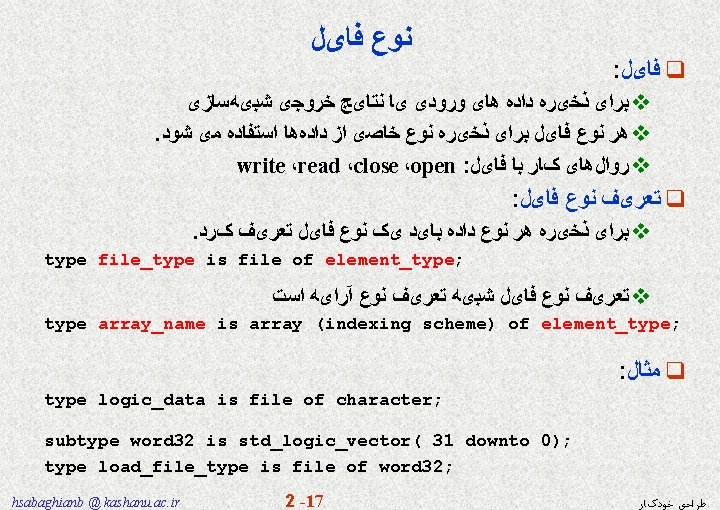

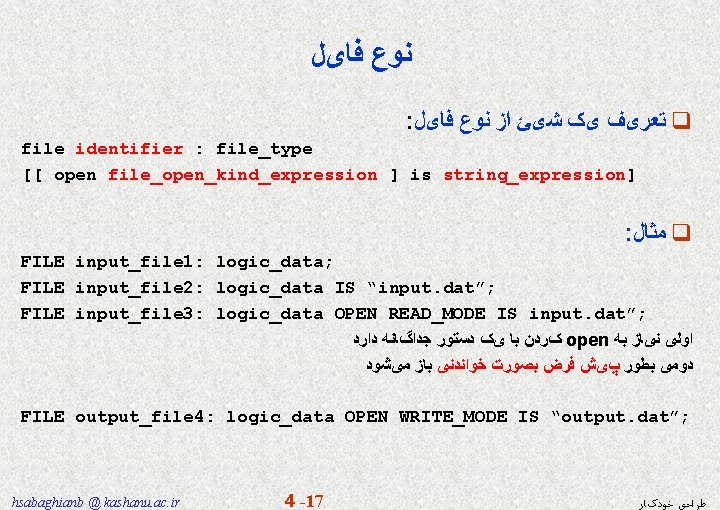

ﻧﻮﻉ ﻓﺎیﻞ : ﺗﻌﺮیﻒ یک ﺷیﺊ ﺍﺯ ﻧﻮﻉ ﻓﺎیﻞ q file identifier : file_type [[ open file_open_kind_expression ] is string_expression] : ﻣﺜﺎﻝ q FILE input_file 1: logic_data; FILE input_file 2: logic_data IS “input. dat”; FILE input_file 3: logic_data OPEN READ_MODE IS input. dat”; کﺮﺩﻥ ﺑﺎ یک ﺩﺳﺘﻮﺭ ﺟﺪﺍگﺎﻧﻪ ﺩﺍﺭﺩ open ﺍﻭﻟی ﻧیﺎﺯ ﺑﻪ ﺩﻭﻣی ﺑﻄﻮﺭ پیﺶ ﻓﺮﺽ ﺑﺼﻮﺭﺕ ﺧﻮﺍﻧﺪﻧی ﺑﺎﺯ ﻣیﺷﻮﺩ FILE output_file 4: logic_data OPEN WRITE_MODE IS “output. dat”; hsabaghianb @ kashanu. ac. ir 4 -17 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

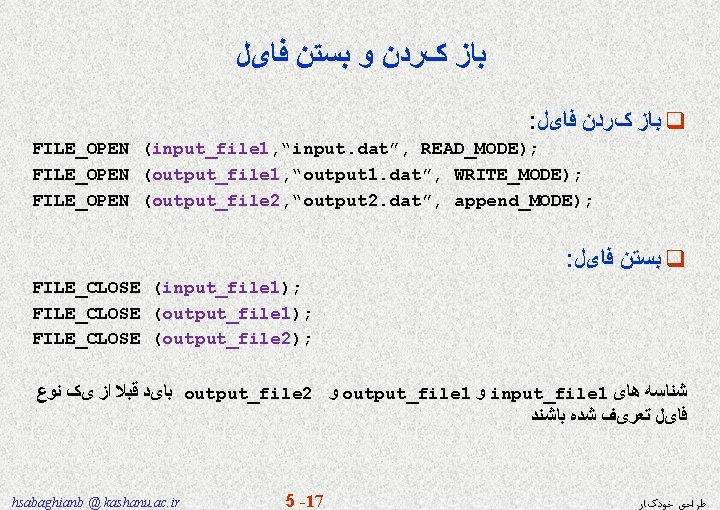

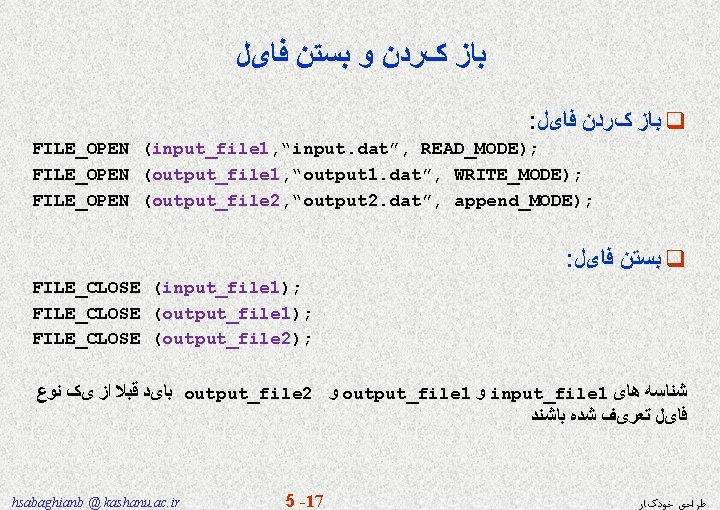

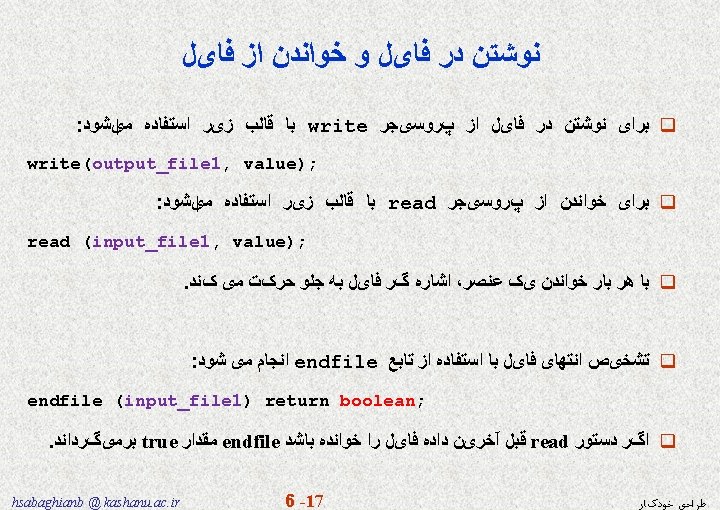

ﺑﺎﺯ کﺮﺩﻥ ﻭ ﺑﺴﺘﻦ ﻓﺎیﻞ : ﺑﺎﺯ کﺮﺩﻥ ﻓﺎیﻞ q FILE_OPEN (input_file 1, “input. dat”, READ_MODE); FILE_OPEN (output_file 1, “output 1. dat”, WRITE_MODE); FILE_OPEN (output_file 2, “output 2. dat”, append_MODE); : ﺑﺴﺘﻦ ﻓﺎیﻞ q FILE_CLOSE (input_file 1); FILE_CLOSE (output_file 2); ﺑﺎیﺪ ﻗﺒﻼ ﺍﺯ یک ﻧﻮﻉ output_file 2 ﻭ output_file 1 ﻭ input_file 1 ﺷﻨﺎﺳﻪ ﻫﺎی ﻓﺎیﻞ ﺗﻌﺮیﻒ ﺷﺪﻩ ﺑﺎﺷﻨﺪ hsabaghianb @ kashanu. ac. ir 5 -17 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

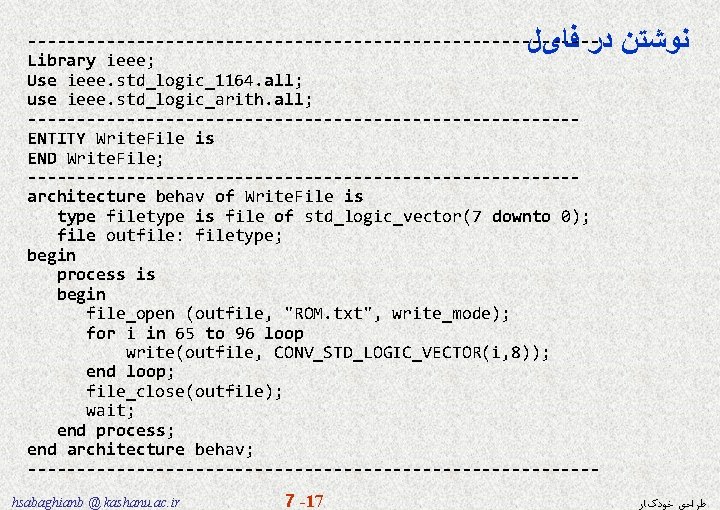

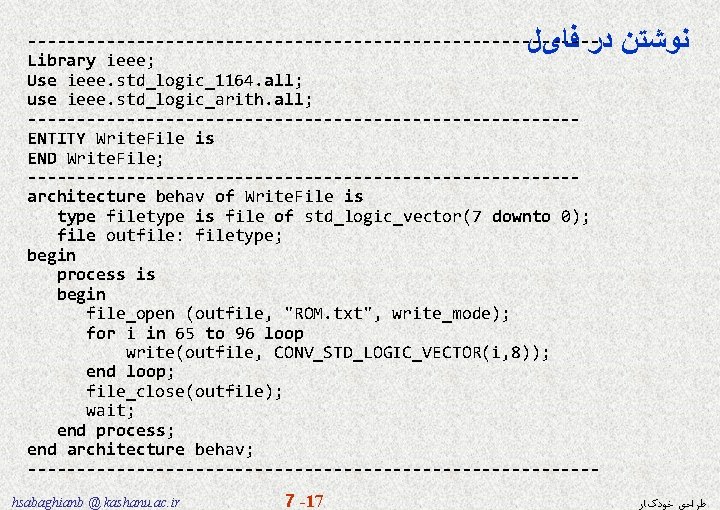

ﻧﻮﺷﺘﻦ ﺩﺭ ﻓﺎیﻞ -----------------------------Library ieee; Use ieee. std_logic_1164. all; use ieee. std_logic_arith. all; ----------------------------ENTITY Write. File is END Write. File; ----------------------------architecture behav of Write. File is type filetype is file of std_logic_vector(7 downto 0); file outfile: filetype; begin process is begin file_open (outfile, "ROM. txt", write_mode); for i in 65 to 96 loop write(outfile, CONV_STD_LOGIC_VECTOR(i, 8)); end loop; file_close(outfile); wait; end process; end architecture behav; -----------------------------hsabaghianb @ kashanu. ac. ir 7 -17 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

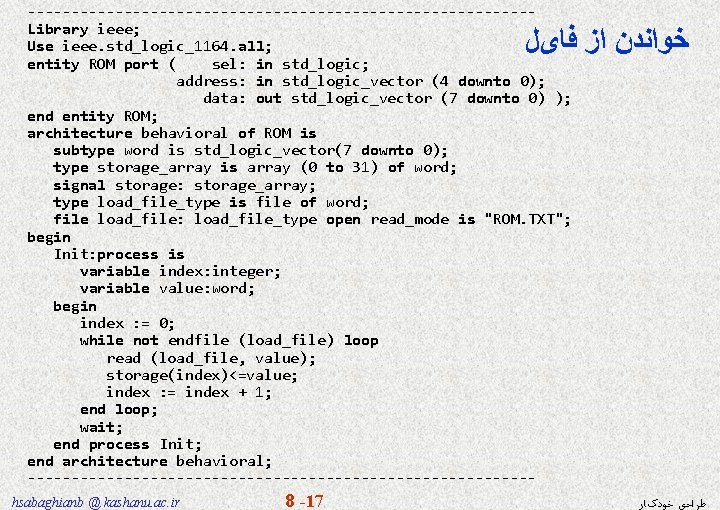

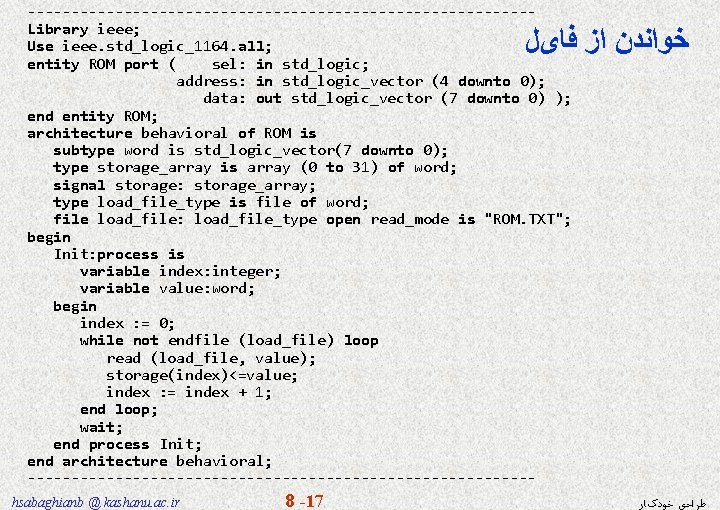

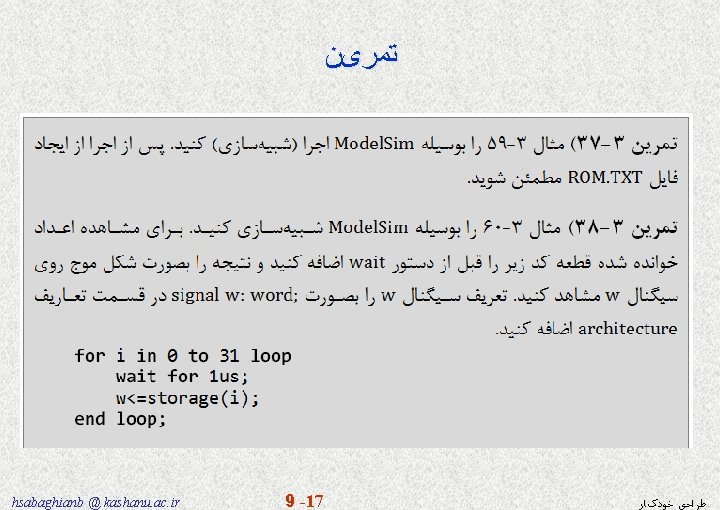

-----------------------------Library ieee; Use ieee. std_logic_1164. all; entity ROM port ( sel: in std_logic; address: in std_logic_vector (4 downto 0); data: out std_logic_vector (7 downto 0) ); end entity ROM; architecture behavioral of ROM is subtype word is std_logic_vector(7 downto 0); type storage_array is array (0 to 31) of word; signal storage: storage_array; type load_file_type is file of word; file load_file: load_file_type open read_mode is "ROM. TXT"; begin Init: process is variable index: integer; variable value: word; begin index : = 0; while not endfile (load_file) loop read (load_file, value); storage(index)<=value; index : = index + 1; end loop; wait; end process Init; end architecture behavioral; ----------------------------- ﺧﻮﺍﻧﺪﻥ ﺍﺯ ﻓﺎیﻞ hsabaghianb @ kashanu. ac. ir 8 -17 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

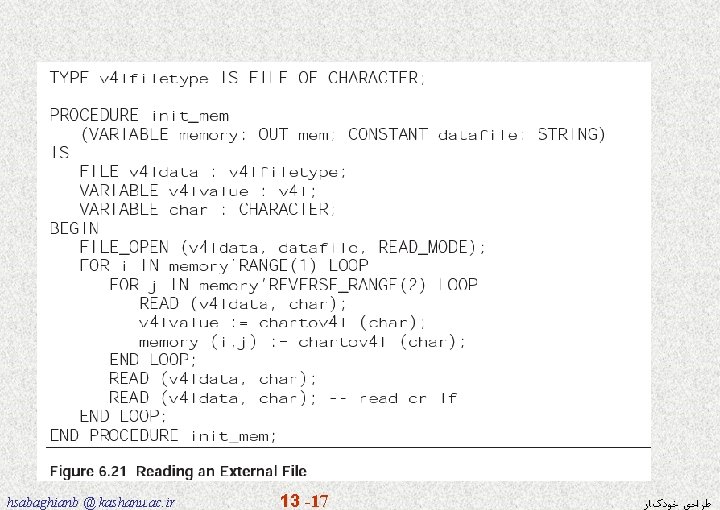

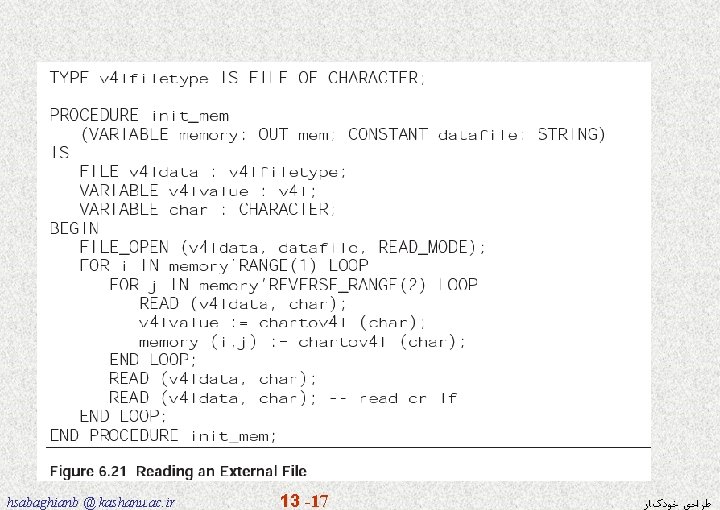

hsabaghianb @ kashanu. ac. ir 13 -17 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ

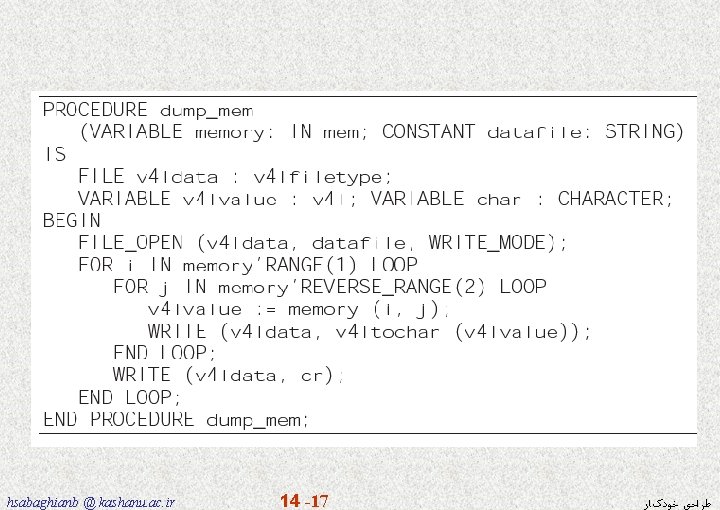

hsabaghianb @ kashanu. ac. ir 14 -17 ﻃﺮﺍﺣی ﺧﻮﺩکﺎﺭ