Putting Formal Description of Software Architecture in Practice

![STATIC DESCRIPTION WITH DARWIN Graphic Description of the SAXC component SAXC cxc[0] cxc[1] bxc[0] STATIC DESCRIPTION WITH DARWIN Graphic Description of the SAXC component SAXC cxc[0] cxc[1] bxc[0]](https://slidetodoc.com/presentation_image_h2/525f5a1da3755902cb27d6dfc8124c49/image-19.jpg)

- Slides: 30

Putting Formal Description of Software Architecture in Practice: Good News, Bad News. Paola Inverardi UNIVERSITA’ DEGLI STUDI DELL’AQUILA Area Informatica, Facolta’ di SSMMNN

Brief history of our work in SA • Formal description of SA via CHAM • Behavioral Analysis of the SA • algebraic analysis and finite state modeling • validation and quantitative analysis based on FSTM

Our experience • Modelling SA for three telecommunication companies • UML as ADL • Poor dynamics descriptions

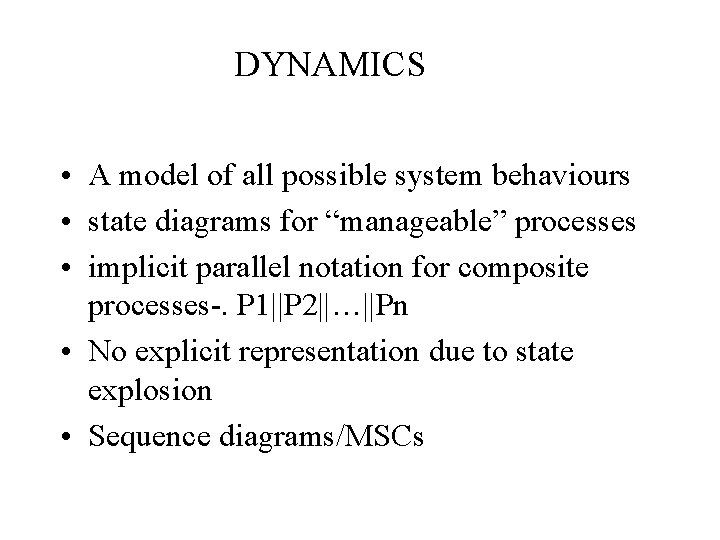

DYNAMICS • A model of all possible system behaviours • state diagrams for “manageable” processes • implicit parallel notation for composite processes-. P 1||P 2||…||Pn • No explicit representation due to state explosion • Sequence diagrams/MSCs

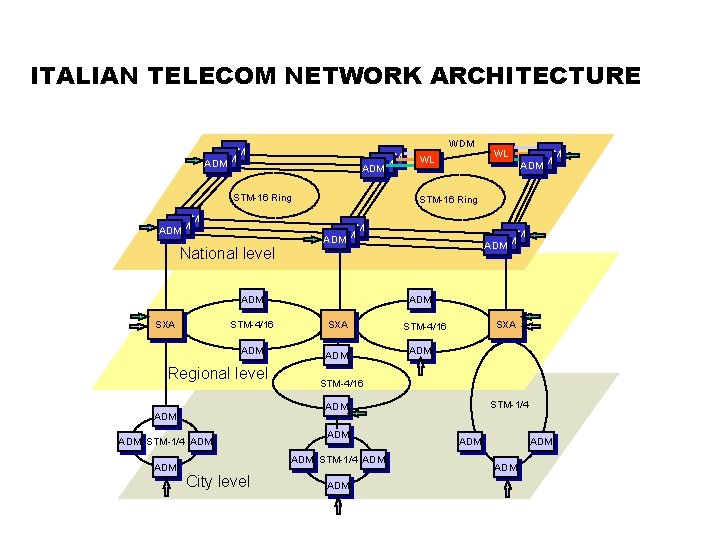

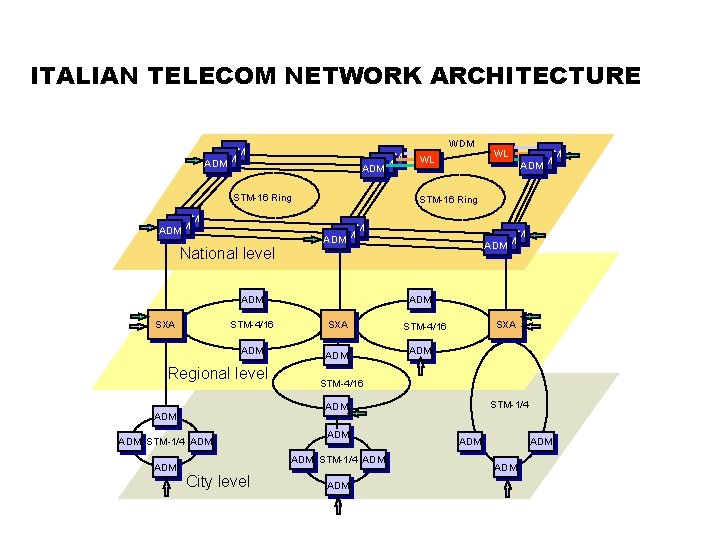

ITALIAN TELECOM NETWORK ARCHITECTURE WDM ADM ADM ADM STM-16 Ring ADM ADM National level STM-4/16 ADM Regional level ADM ADM STM-1/4 ADM ADM SXC SXA 4/1 ADM SXA STM-4/16 ADM ADM STM-1/4 ADM City level ADM ADM ADM STM-1/4 ADM WL STM-16 Ring ADM SXA WL ADM ADM

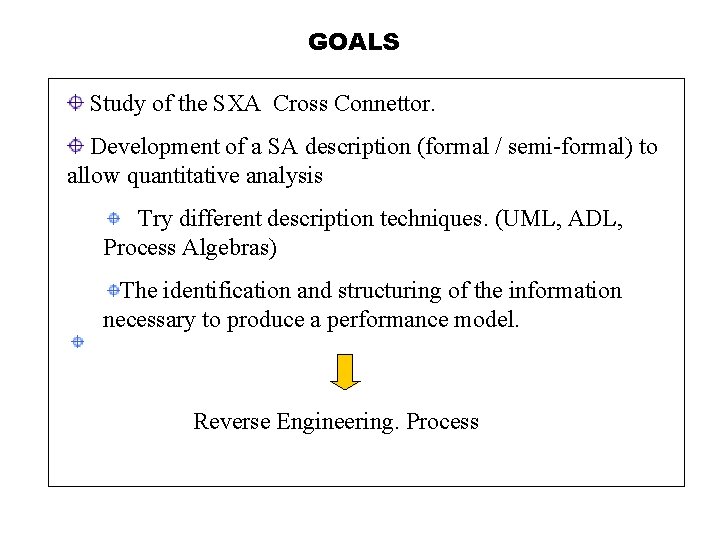

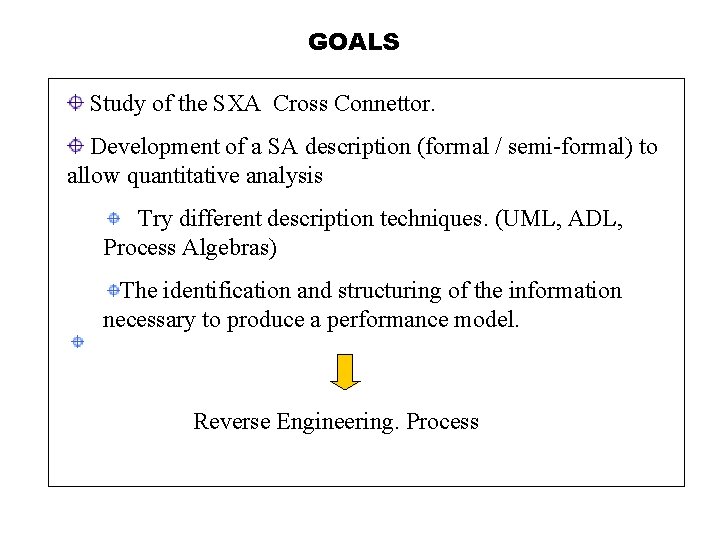

GOALS Study of the SXA Cross Connettor. Development of a SA description (formal / semi-formal) to allow quantitative analysis Try different description techniques. (UML, ADL, Process Algebras) The identification and structuring of the information necessary to produce a performance model. Reverse Engineering. Process

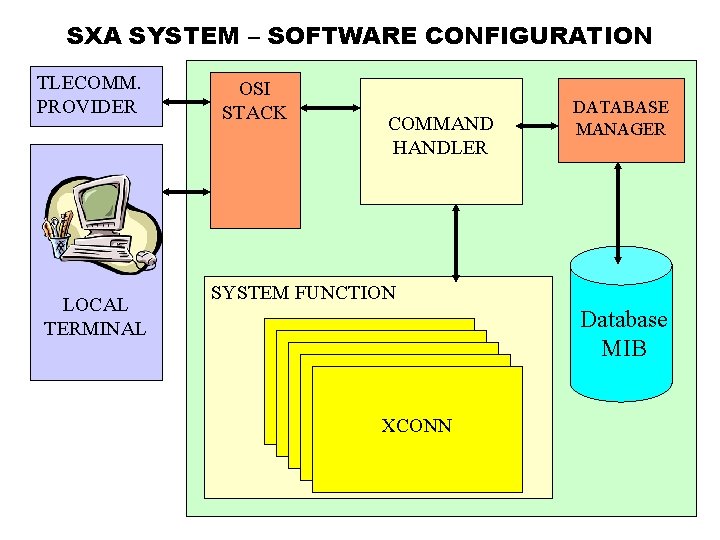

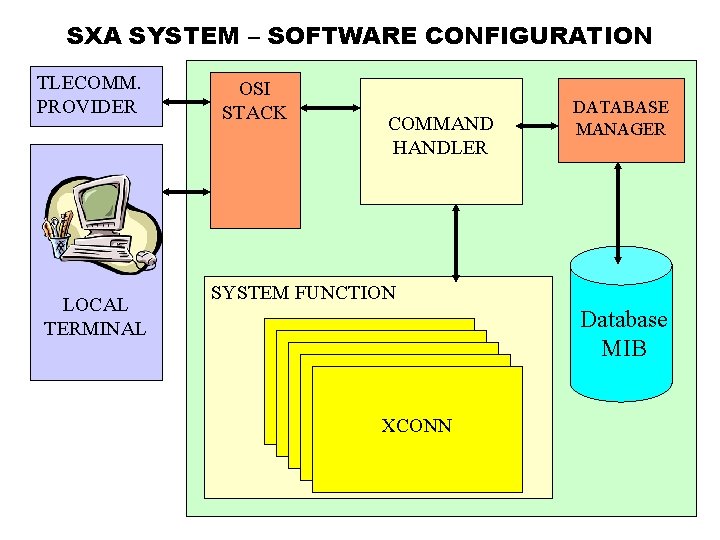

SXA SYSTEM – SOFTWARE CONFIGURATION TLECOMM. PROVIDER LOCAL TERMINAL OSI STACK COMMAND HANDLER DATABASE MANAGER SYSTEM FUNCTION Database MIB XCONN

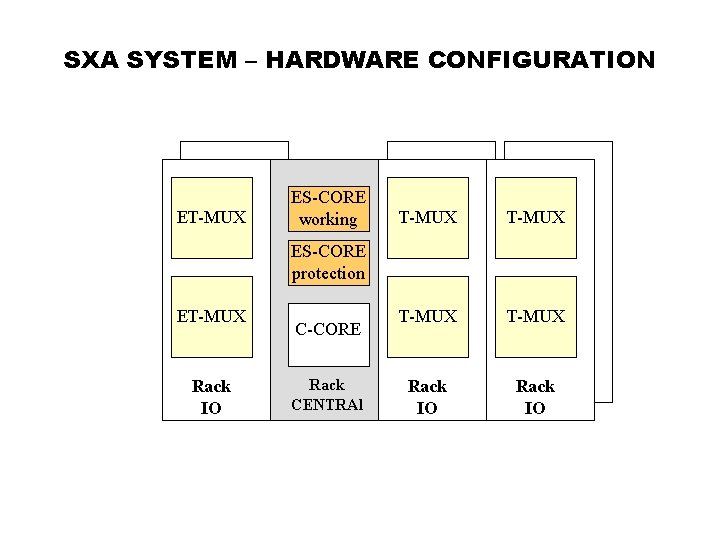

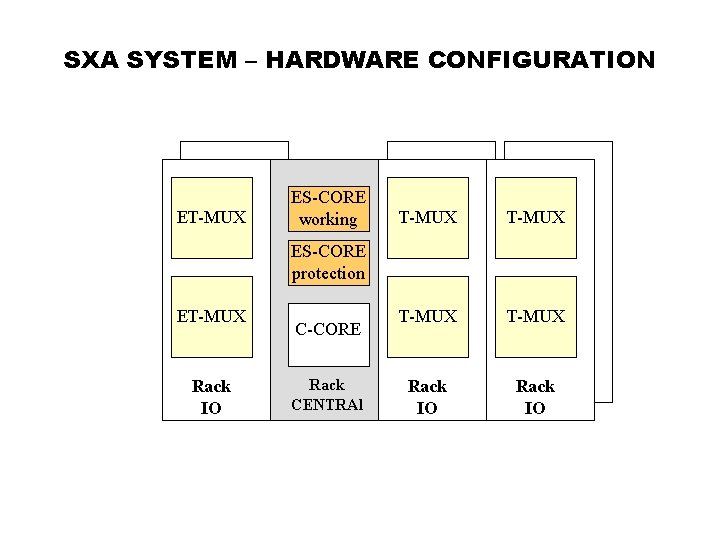

SXA SYSTEM – HARDWARE CONFIGURATION ET-MUX ES-CORE working T-MUX Rack IO ES-CORE protection ET-MUX Rack IO C-CORE Rack CENTRAl

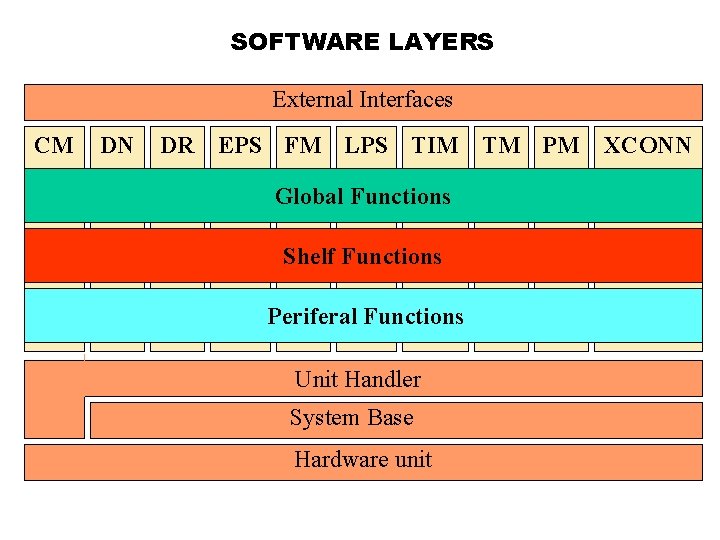

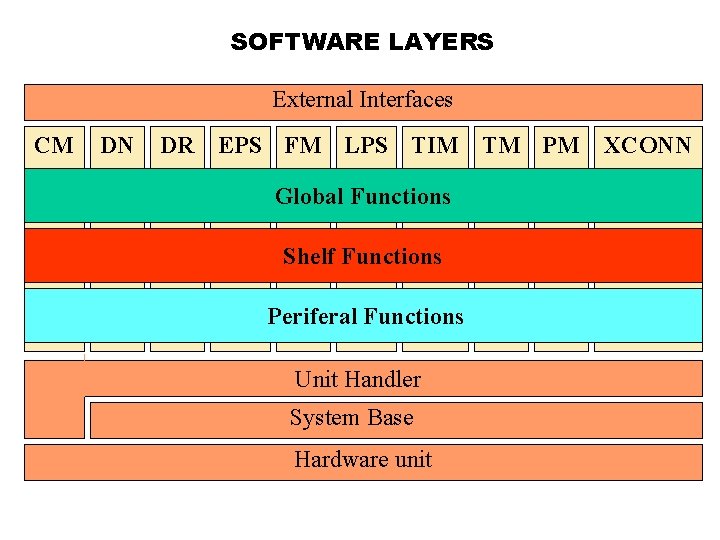

SOFTWARE LAYERS External Interfaces CM DN DR EPS FM LPS TIM TM PM Global Functions Shelf Functions Periferal Functions Unit Handler System Base Hardware unit XCONN

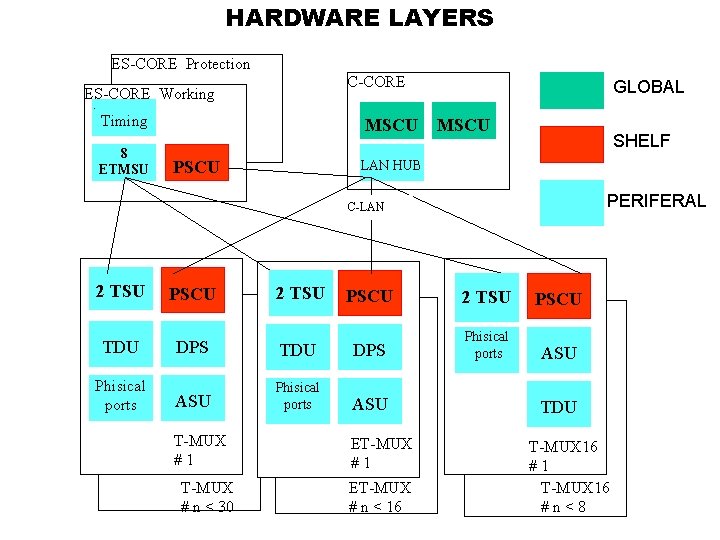

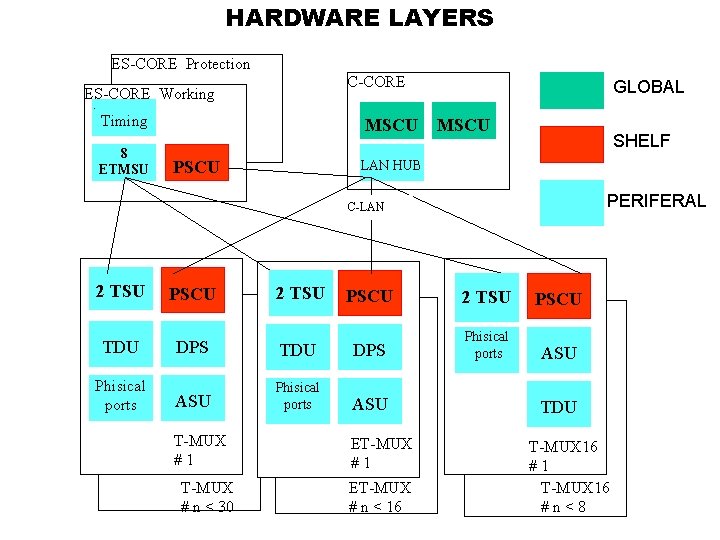

HARDWARE LAYERS ES-CORE Protection C-CORE ES-CORE Working GLOBAL . Timing 8 ETMSU MSCU SHELF LAN HUB PSCU PERIFERAL C-LAN 2 TSU PSCU TDU DPS Phisical ports ASU T-MUX #1 T-MUX # n < 30 2 TSU PSCU TDU DPS Phisical ports ASU ET-MUX #1 ET-MUX # n < 16 TDU T-MUX 16 #1 T-MUX 16 #n<8

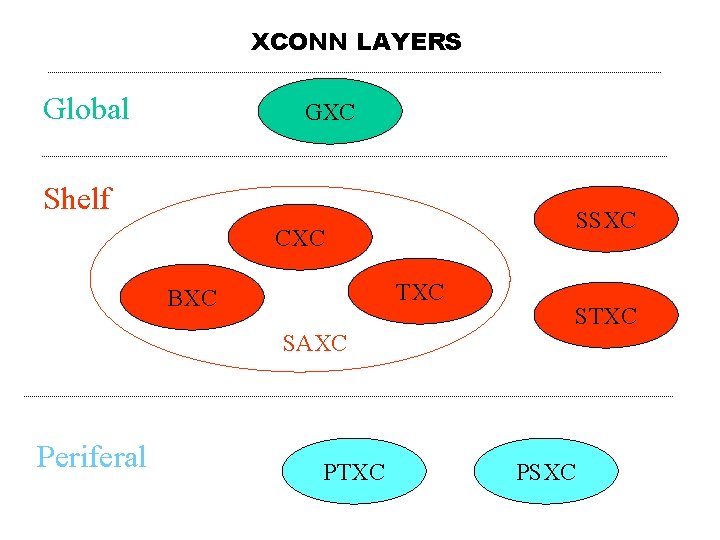

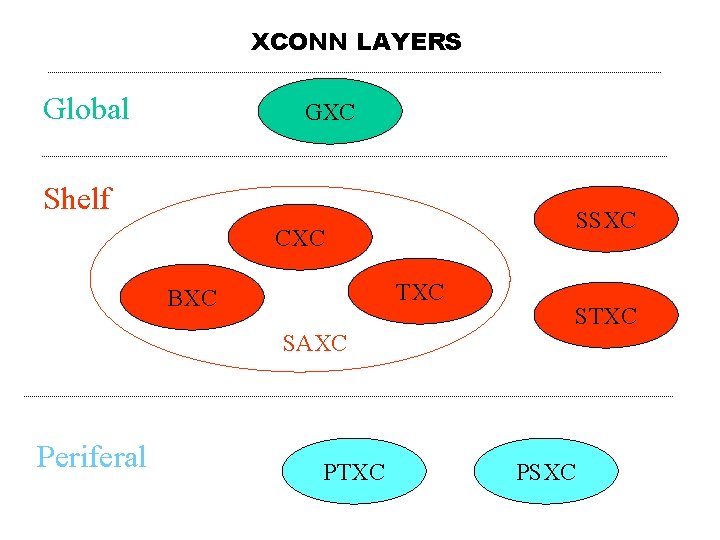

XCONN LAYERS Global GXC Shelf SSXC CXC TXC BXC STXC SAXC Periferal PTXC PSXC

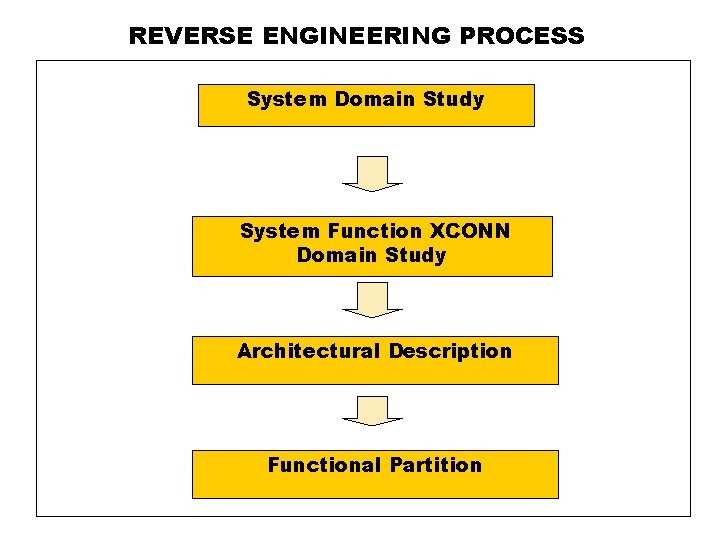

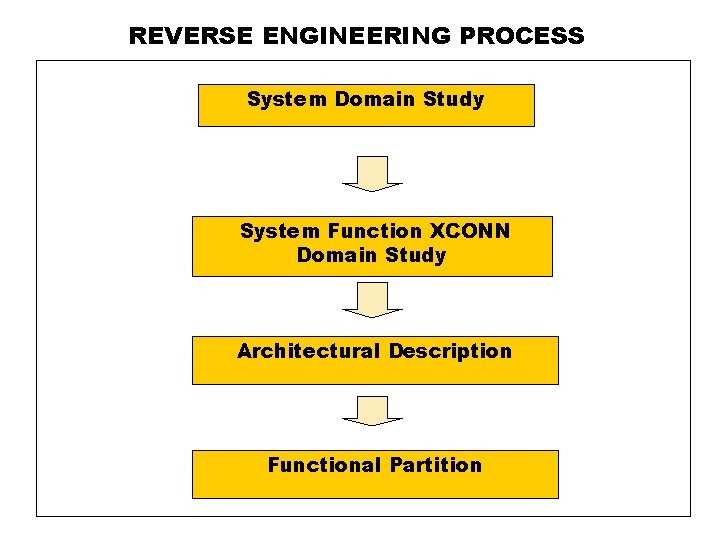

REVERSE ENGINEERING PROCESS System Domain Study System Function XCONN Domain Study Architectural Description Functional Partition

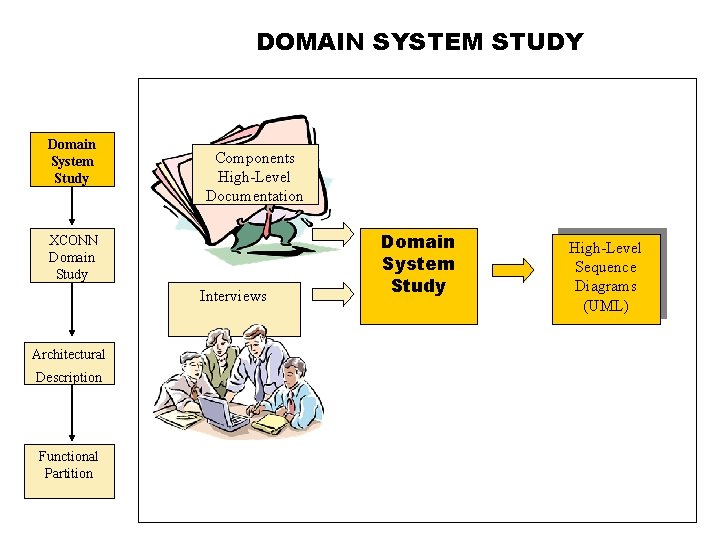

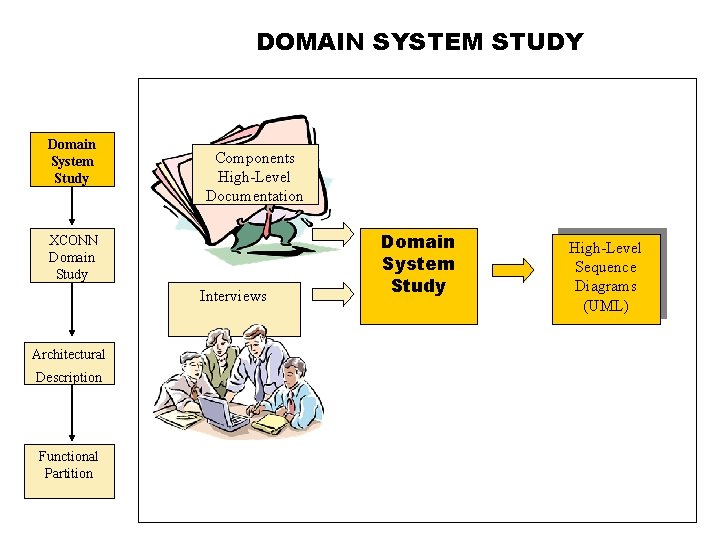

DOMAIN SYSTEM STUDY Domain System Study Components High-Level Documentation XCONN Domain Study Interviews Architectural Description Functional Partition Domain System Study High-Level Sequence Diagrams (UML)

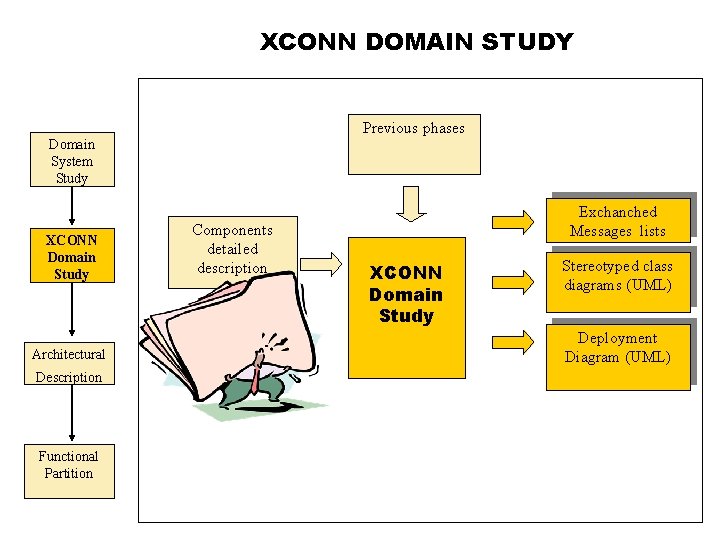

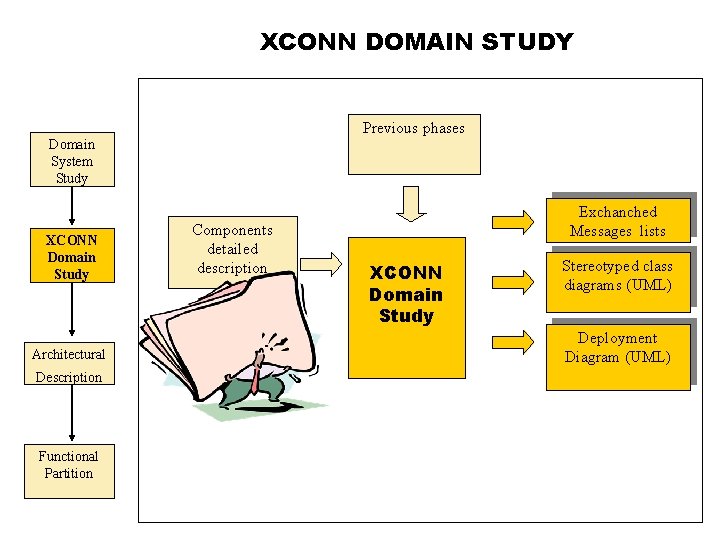

XCONN DOMAIN STUDY Previous phases Domain System Study XCONN Domain Study Architectural Description Functional Partition Components detailed description Exchanched Messages lists XCONN Domain Study Stereotyped class diagrams (UML) Deployment Diagram (UML)

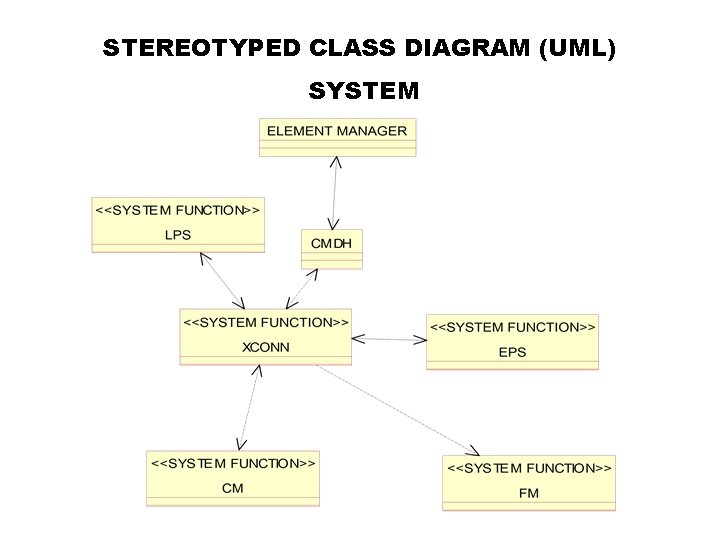

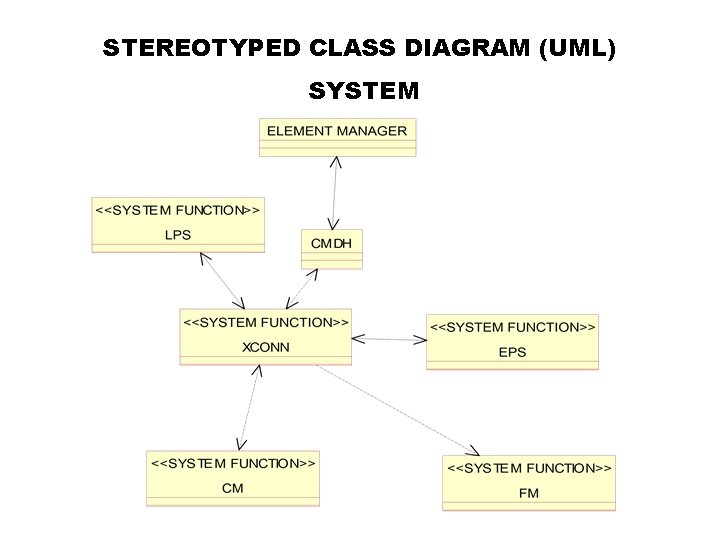

STEREOTYPED CLASS DIAGRAM (UML) SYSTEM

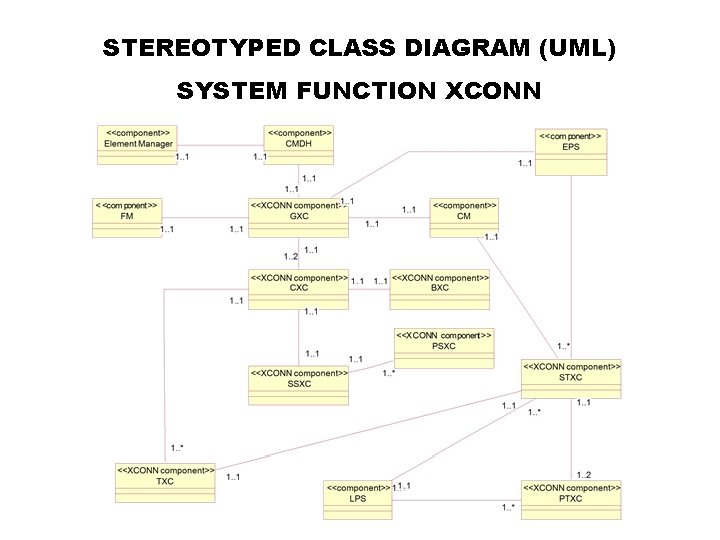

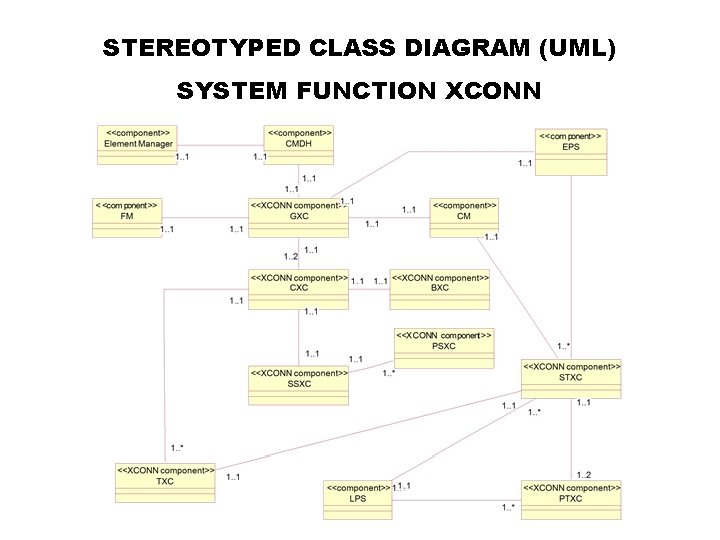

STEREOTYPED CLASS DIAGRAM (UML) SYSTEM FUNCTION XCONN

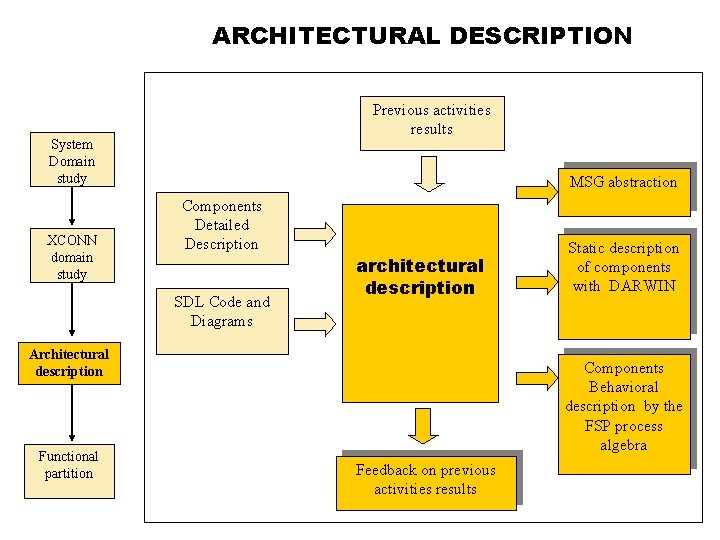

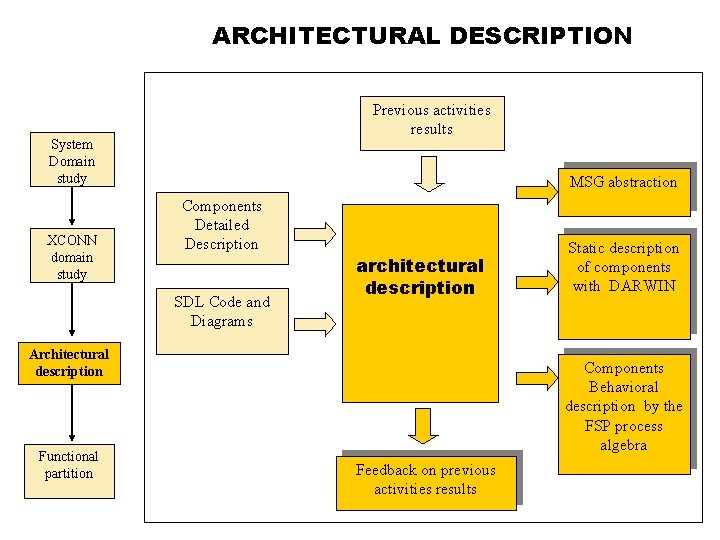

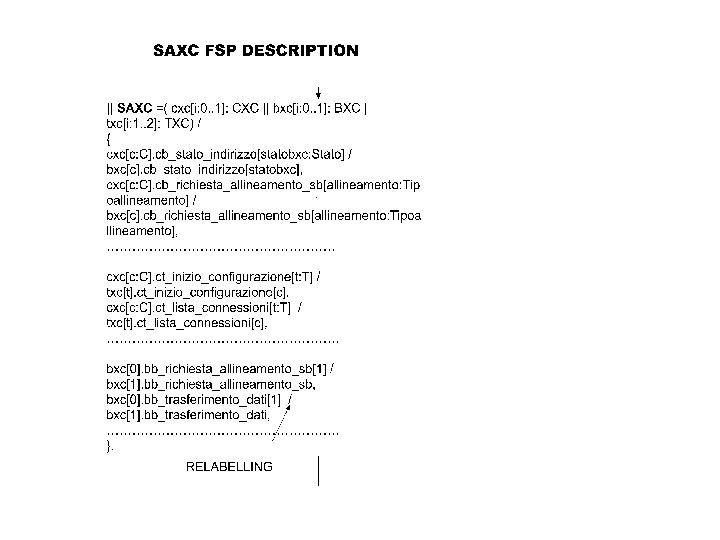

ARCHITECTURAL DESCRIPTION Previous activities results System Domain study XCONN domain study MSG abstraction Components Detailed Description SDL Code and Diagrams architectural description Architectural description Functional partition Static description of components with DARWIN Components Behavioral description by the FSP process algebra Feedback on previous activities results

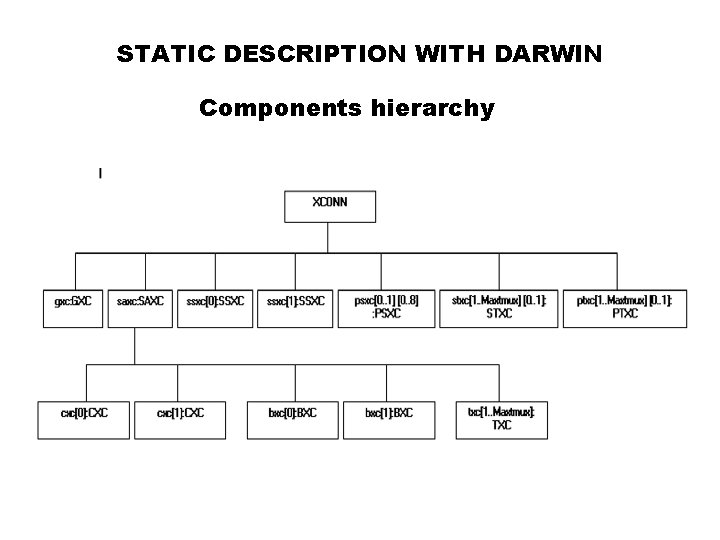

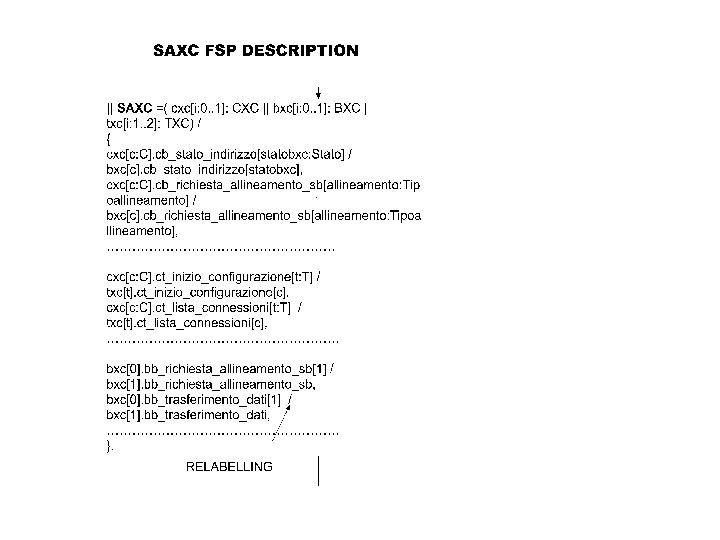

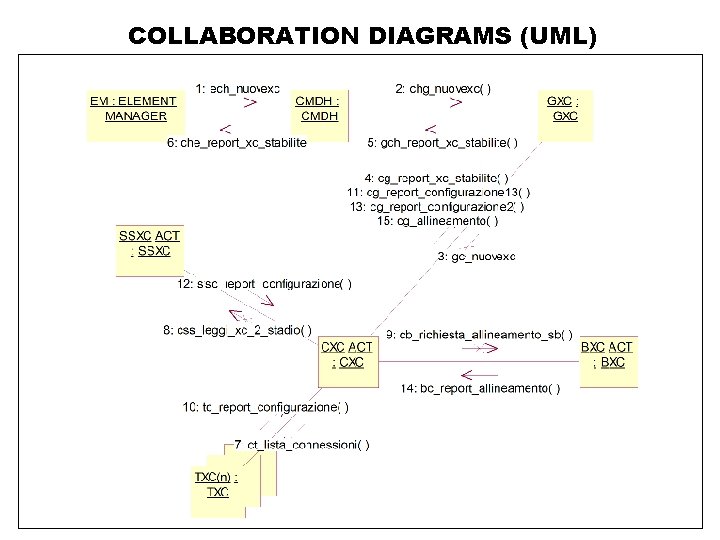

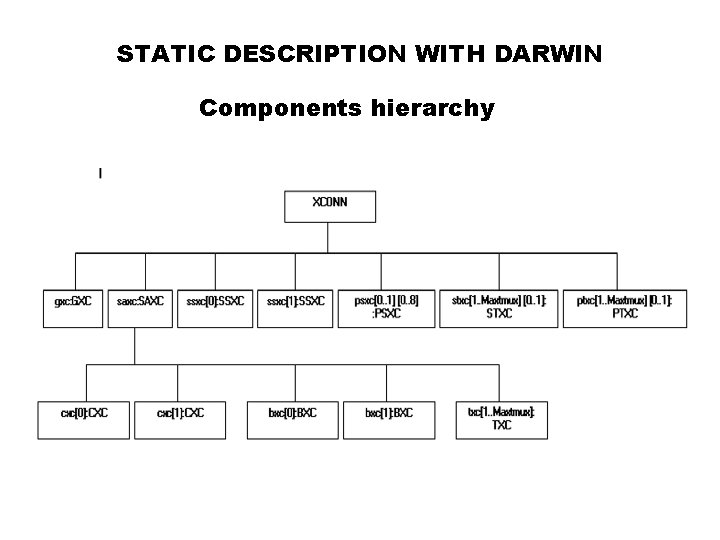

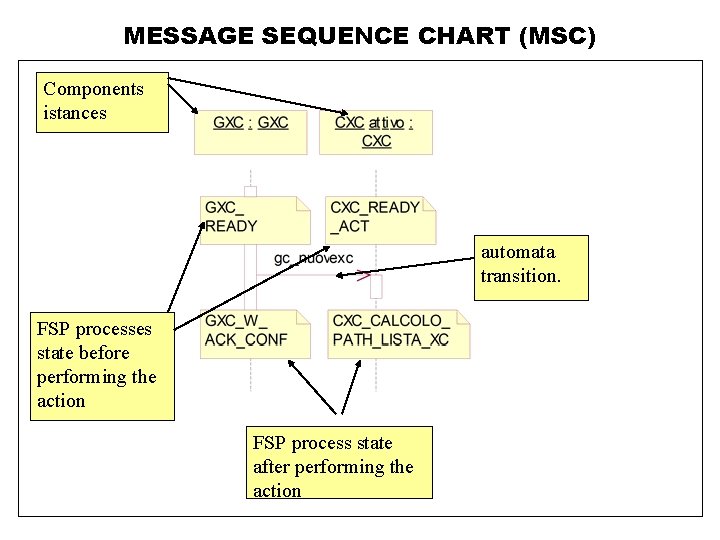

STATIC DESCRIPTION WITH DARWIN Components hierarchy

![STATIC DESCRIPTION WITH DARWIN Graphic Description of the SAXC component SAXC cxc0 cxc1 bxc0 STATIC DESCRIPTION WITH DARWIN Graphic Description of the SAXC component SAXC cxc[0] cxc[1] bxc[0]](https://slidetodoc.com/presentation_image_h2/525f5a1da3755902cb27d6dfc8124c49/image-19.jpg)

STATIC DESCRIPTION WITH DARWIN Graphic Description of the SAXC component SAXC cxc[0] cxc[1] bxc[0] txc[1] txc[2] bxc[1] txc[n]

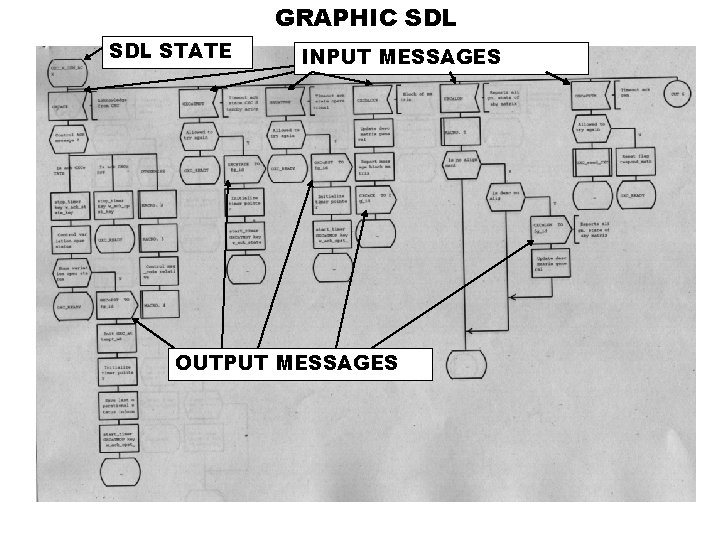

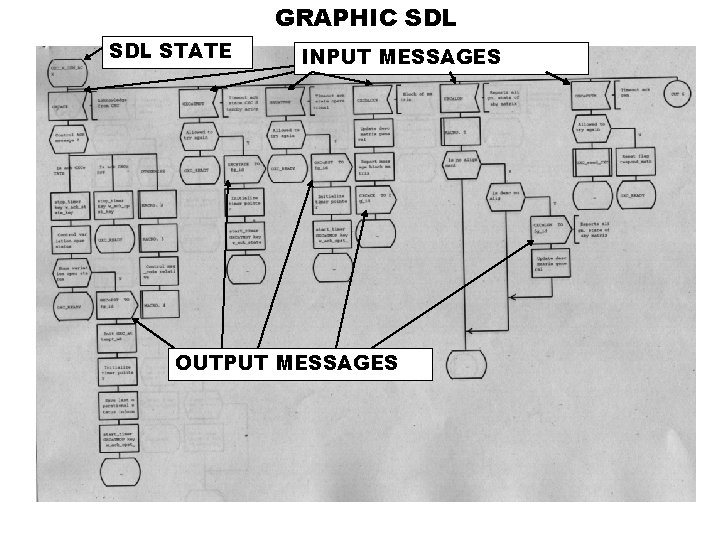

GRAPHIC SDL STATE INPUT MESSAGES OUTPUT MESSAGES

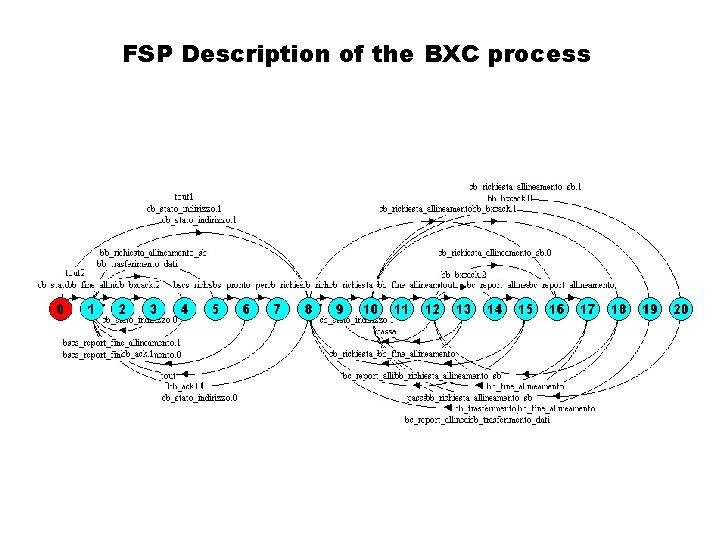

Sub-structure of the BXC process

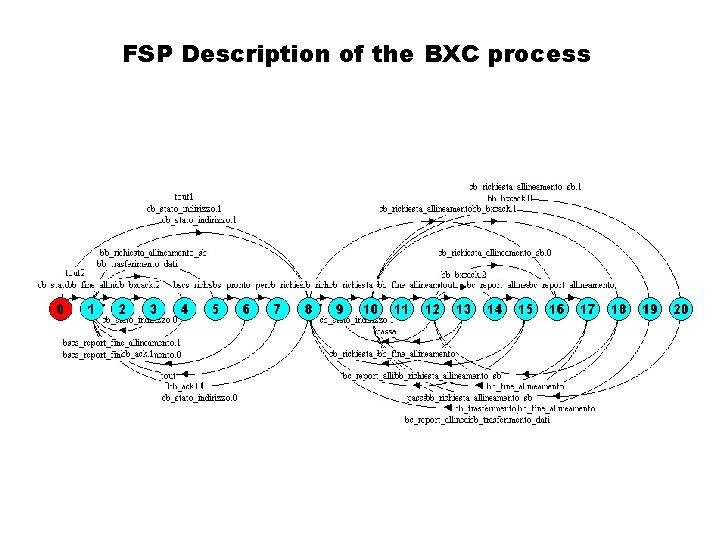

FSP Description of the BXC process

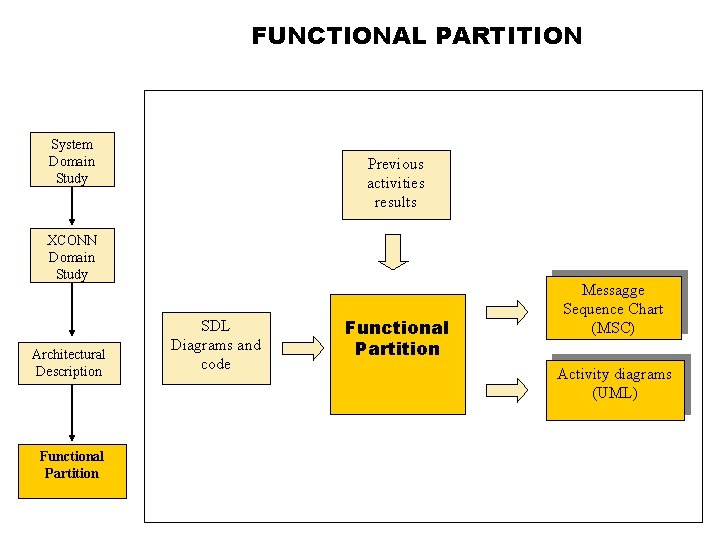

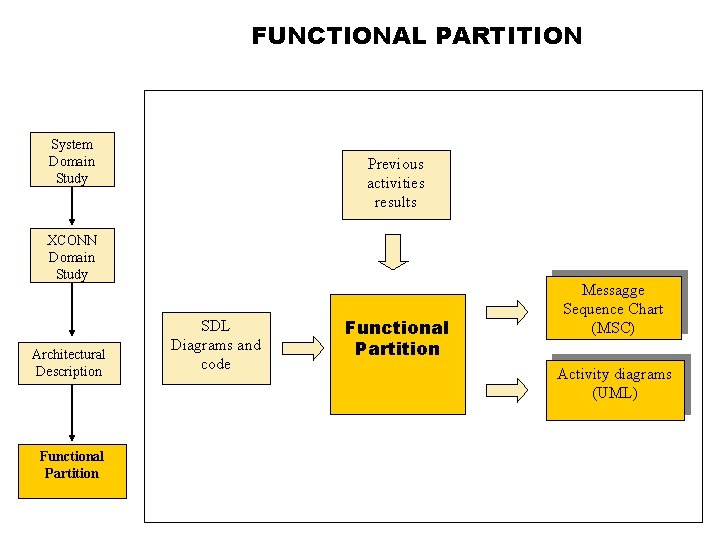

FUNCTIONAL PARTITION System Domain Study Previous activities results XCONN Domain Study Architectural Description Functional Partition SDL Diagrams and code Functional Partition Messagge Sequence Chart (MSC) Activity diagrams (UML)

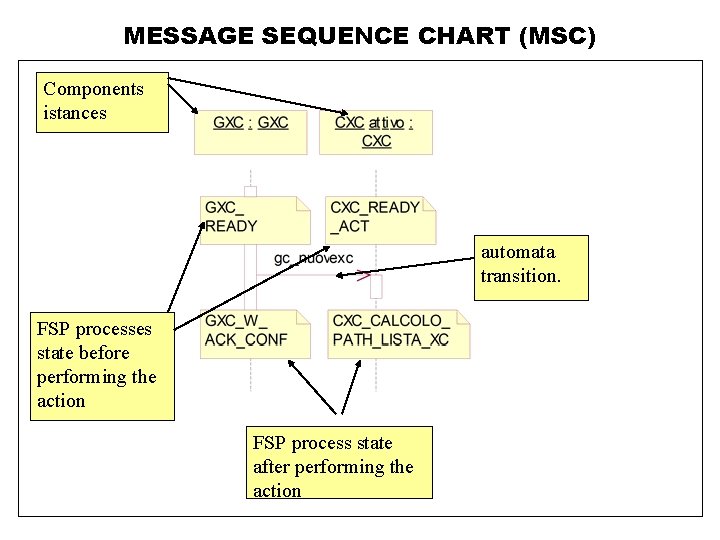

MESSAGE SEQUENCE CHART (MSC) Components istances automata transition. FSP processes state before performing the action FSP process state after performing the action

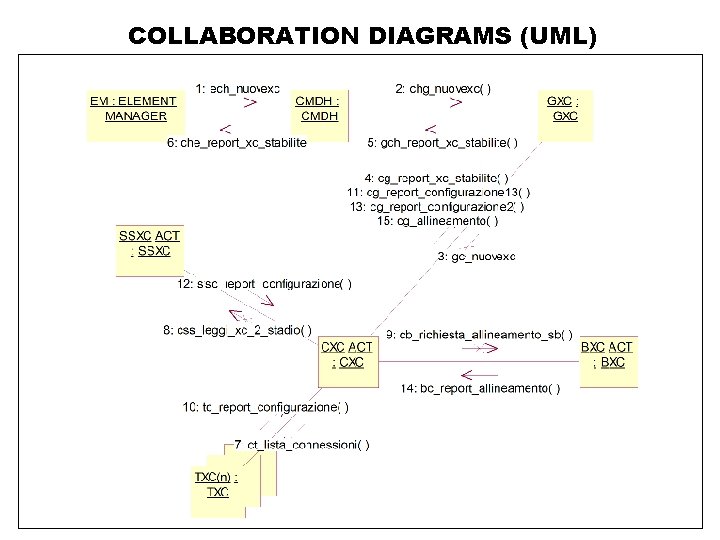

COLLABORATION DIAGRAMS (UML)

Summarizing • Issue of complexity: Have clear in mind what the SA has to be for • Domain specific ADL, complementing standard notations with ad hoc notations, e. g. FSP • Predictive analysis and evaluation of the architectural choices