PSuper BSVT Attivita e finanze 2010 Attivita e

P-Super. B-SVT • Attivita’ e finanze 2010 • Attivita’ e richieste 2011 Frascati 9 Luglio 2010 Giuliana Rizzo Universita’ & INFN Pisa G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 1

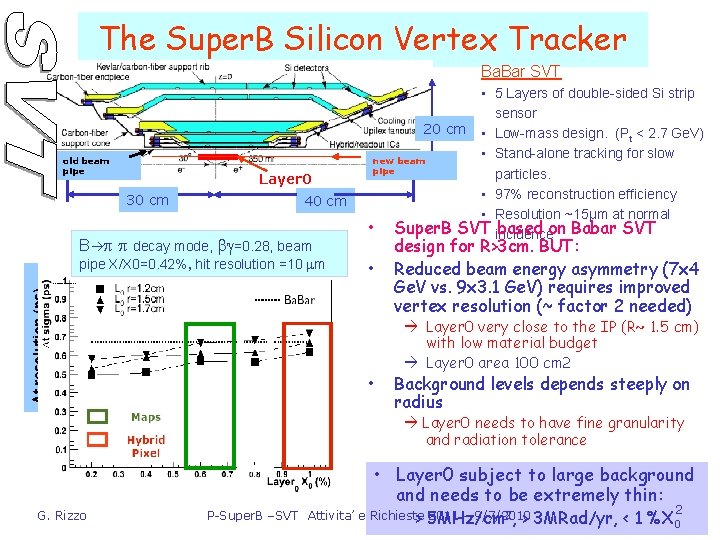

The Super. B Silicon Vertex Tracker Ba. Bar SVT old beam pipe Layer 0 30 cm 40 cm B p p decay mode, bg=0. 28, beam Dt resolution (ps) pipe X/X 0=0. 42%, hit resolution =10 mm • 5 Layers of double-sided Si strip sensor 20 cm • Low-mass design. (P < 2. 7 Ge. V) t • Stand-alone tracking for slow new beam pipe particles. • 97% reconstruction efficiency • Resolution ~15μm at normal • Super. B SVT incidence based on Babar SVT • • design for R>3 cm. BUT: Reduced beam energy asymmetry (7 x 4 Ge. V vs. 9 x 3. 1 Ge. V) requires improved vertex resolution (~ factor 2 needed) Layer 0 very close to the IP (R~ 1. 5 cm) with low material budget Layer 0 area 100 cm 2 Background levels depends steeply on radius Layer 0 needs to have fine granularity and radiation tolerance • Layer 0 subject to large background and needs to be extremely thin: G. Rizzo 2, > 3 MRad/yr, P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 > 5 MHz/cm 2 < 1 %X 0

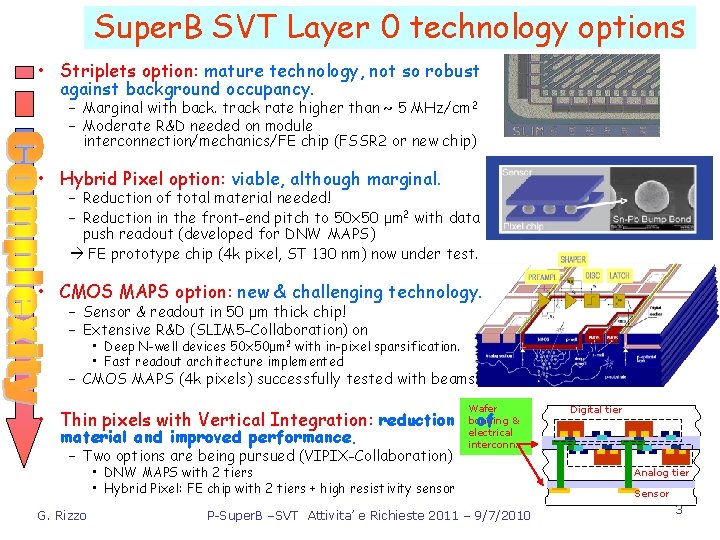

Super. B SVT Layer 0 technology options • Striplets option: mature technology, not so robust against background occupancy. – Marginal with back. track rate higher than ~ 5 MHz/cm 2 – Moderate R&D needed on module interconnection/mechanics/FE chip (FSSR 2 or new chip) • Hybrid Pixel option: viable, although marginal. – Reduction of total material needed! – Reduction in the front-end pitch to 50 x 50 μm 2 with data push readout (developed for DNW MAPS) FE prototype chip (4 k pixel, ST 130 nm) now under test. • CMOS MAPS option: new & challenging technology. – Sensor & readout in 50 μm thick chip! – Extensive R&D (SLIM 5 -Collaboration) on • Deep N-well devices 50 x 50μm 2 with in-pixel sparsification. • Fast readout architecture implemented – CMOS MAPS (4 k pixels) successfully tested with beams. • Thin pixels with Vertical Integration: reduction material and improved performance. – Two options are being pursued (VIPIX-Collaboration) Wafer bonding & electrical interconn. of • DNW MAPS with 2 tiers • Hybrid Pixel: FE chip with 2 tiers + high resistivity sensor G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 Digital tier Analog tier Sensor 3

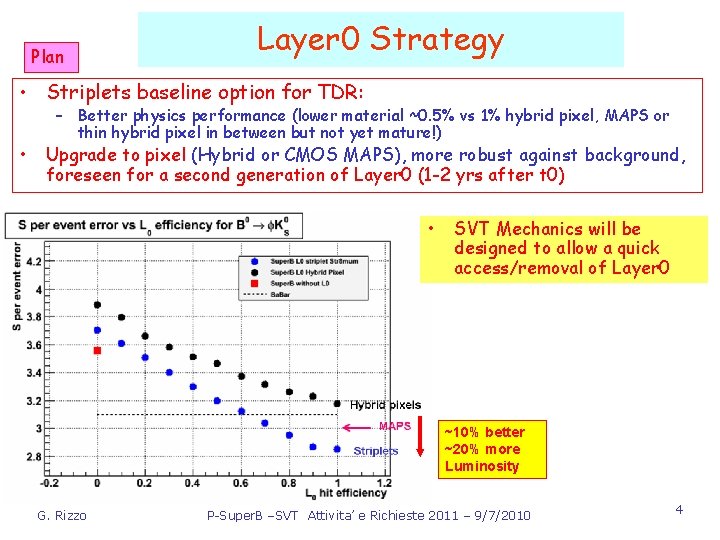

Plan Layer 0 Strategy • Striplets baseline option for TDR: • – Better physics performance (lower material ~0. 5% vs 1% hybrid pixel, MAPS or thin hybrid pixel in between but not yet mature!) Upgrade to pixel (Hybrid or CMOS MAPS), more robust against background, foreseen for a second generation of Layer 0 (1 -2 yrs after t 0) • SVT Mechanics will be designed to allow a quick access/removal of Layer 0 ~10% better ~20% more Luminosity G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 4

Attivita’ SVT per TDR Layer 0 • Striplets (per baseline): Sezioni: Bologna, Milano, Pavia, Pisa, Roma III, Torino, Trieste – indagine sul chip di lettura • FSRR 2 (PV+TS), utilizzo altri chip esistenti o sviluppo nuovo chip (PV) – Prototipo modulo a striplets: • Sensori (TS), Fanout multistrato (MI+TS), HDI (MI+TS), support & assembly (PI) • Pixel (per upgrade) (tutte le sezioni coinvolte): – Hybrid Pixels: sviluppo chip di FE pitch 50 x 50 um connesso con matrice di pixel su alta resistivita’. – Realizzazione e test di prototipo modulo pixel multichip con specs Super. B – Continua R&D su pixel sottili (CMOS MAPS e thin hybrid pixels con integrazione verticale) in VIPIX-CSN 5 Layer 1 -5 a strip : – Design componenti moduli: sensori (TS)+fanout(MI+TS), valutazione chip lettura (PV+TS), “ibrido” (MI+TS) Meccanica: – Light support/cooling for Layer 0 modules & cooled beam-pipe design (PI), – Layer 0 support & quick removal procedure for Layer 0 (PI+SLAC), – External layers Module design + SVT Mech. Support (PI+TO) Off Detector electronics (MI) and DAQ Development (BO) Simulazione: Background (Full. Sim) (PI) – Det. Optimization (Fast. Sim) (PI+TS) G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 5

Dove siamo arrivati nel 2010 G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 6

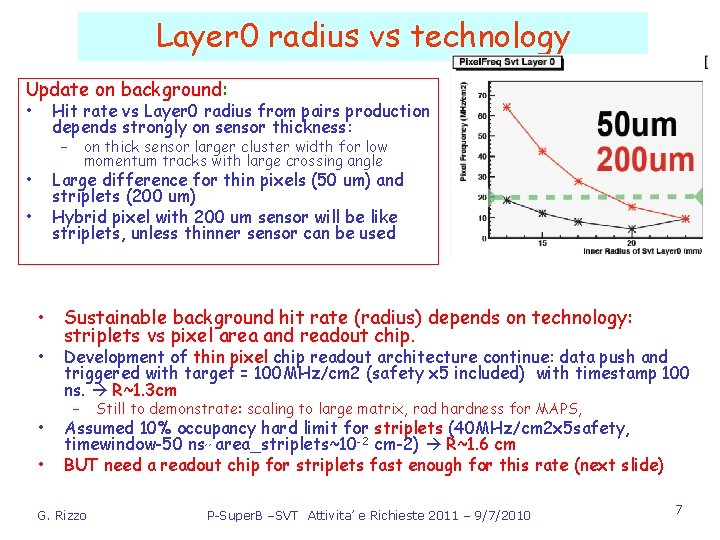

Layer 0 radius vs technology Update on background: • Hit rate vs Layer 0 radius from pairs production depends strongly on sensor thickness: – • on thick sensor larger cluster width for low momentum tracks with large crossing angle Large difference for thin pixels (50 um) and striplets (200 um) Hybrid pixel with 200 um sensor will be like striplets, unless thinner sensor can be used • • Sustainable background hit rate (radius) depends on technology: striplets vs pixel area and readout chip. • • • Development of thin pixel chip readout architecture continue: data push and triggered with target = 100 MHz/cm 2 (safety x 5 included) with timestamp 100 ns. R~1. 3 cm – Still to demonstrate: scaling to large matrix, rad hardness for MAPS, Assumed 10% occupancy hard limit for striplets (40 MHz/cm 2 x 5 safety, timewindow-50 ns, , area_striplets~10 -2 cm-2) R~1. 6 cm BUT need a readout chip for striplets fast enough for this rate (next slide) G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 7

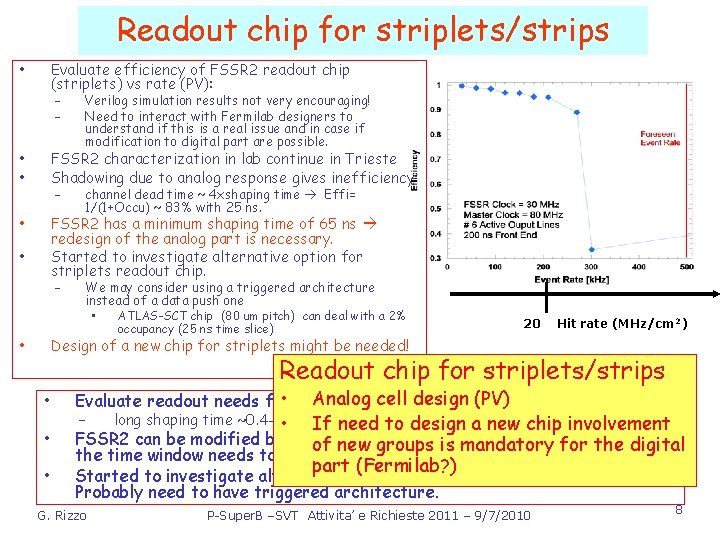

Readout chip for striplets/strips • Evaluate efficiency of FSSR 2 readout chip (striplets) vs rate (PV): – – Verilog simulation results not very encouraging! Need to interact with Fermilab designers to understand if this is a real issue and in case if modification to digital part are possible. • • FSSR 2 characterization in lab continue in Trieste Shadowing due to analog response gives inefficiency: • FSSR 2 has a minimum shaping time of 65 ns redesign of the analog part is necessary. Started to investigate alternative option for striplets readout chip. – • – channel dead time ~ 4 xshaping time Effi= 1/(1+Occu) ~ 83% with 25 ns. We may consider using a triggered architecture instead of a data push one • ATLAS-SCT chip (80 um pitch) can deal with a 2% occupancy (25 ns time slice) • 20 Hit rate (MHz/cm 2) Design of a new chip for striplets might be needed! Readout chip for striplets/strips • • the Analog celllayers: design (PV) Evaluate readout needs for external • FSSR 2 can be modified but with pushisarchitecture of the newdata groups mandatory implemented for the digital the time window needs to be > 1 us (problems with background tracks) part (Fermilab? ) Started to investigate alternative options for long strip readout chip. Probably need to have triggered architecture. • – G. Rizzo long shaping time ~0. 4 -1 • us needed to get If need to reasonable design a S/N. new (20 -26) chip involvement P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 8

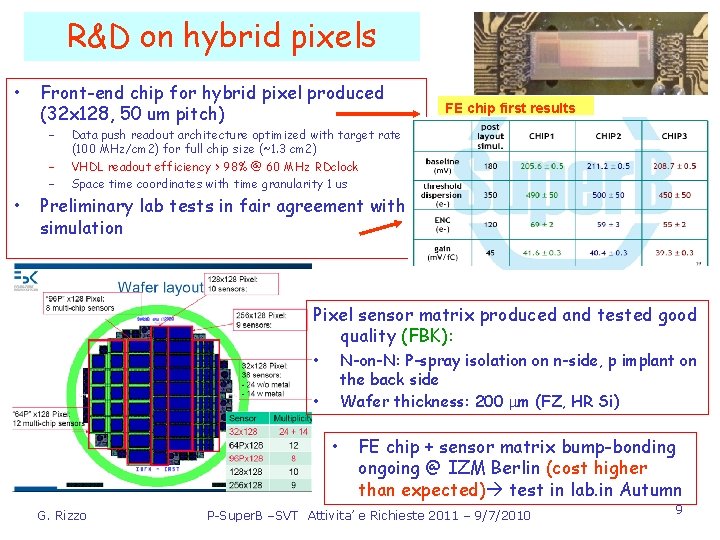

R&D on hybrid pixels • Front-end chip for hybrid pixel produced (32 x 128, 50 um pitch) – – – • FE chip first results Data push readout architecture optimized with target rate (100 MHz/cm 2) for full chip size (~1. 3 cm 2) VHDL readout efficiency > 98% @ 60 MHz RDclock Space time coordinates with time granularity 1 us Preliminary lab tests in fair agreement with simulation Pixel sensor matrix produced and tested good quality (FBK): • N-on-N: P-spray isolation on n-side, p implant on the back side Wafer thickness: 200 mm (FZ, HR Si) • • G. Rizzo FE chip + sensor matrix bump-bonding ongoing @ IZM Berlin (cost higher than expected) test in lab. in Autumn P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 9

1. 0 R&D on thin pixels Development of readout architecture for • Simulation of the new readout 3 D pixels continue (3 D MAPS & 3 D FE Architecture – Data. Pixels Push, Noin Macropixel chip for Hybrid Dec- VIPIX): – – – lettura ordinata temporalmente, rimozione del MP e storing nel pixel del timestamp Data push and triggered mode in the same chip! Triggered option reduces pixel module complexity (lower speed for links & less material for pixel bus) G. Rizzo 0. 8 0. 6 Efficiency • 0. 5 Improvements (collection efficiency & readout performance) with 3 D MAPS: – vertical integration of 2 CMOS layers – First prototypes available in Sept. 100 µm thick 300 µm thick 0. 7 – 4 k pixel matrix with data push readout succesfully tested with beams in 2008 – New cell and irradiated DNW MAPS (10 Mrad) tested with beams in 2009 • 32 x 128 pix - 50 mm pitch 0. 9 CMOS MAPS (SLIM 5 VIPIX): • Single layer DNW MAPS well advanced: DNW MAPS Efficiency vs. threshold 0. 5 MIP 400 450 500 550 600 650 (e-) M 1 - chip 8 not irradiated M 1 chip 24 @ 10 Mrad THR < 4 s Noise Not feasible P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 10 e. Thr.

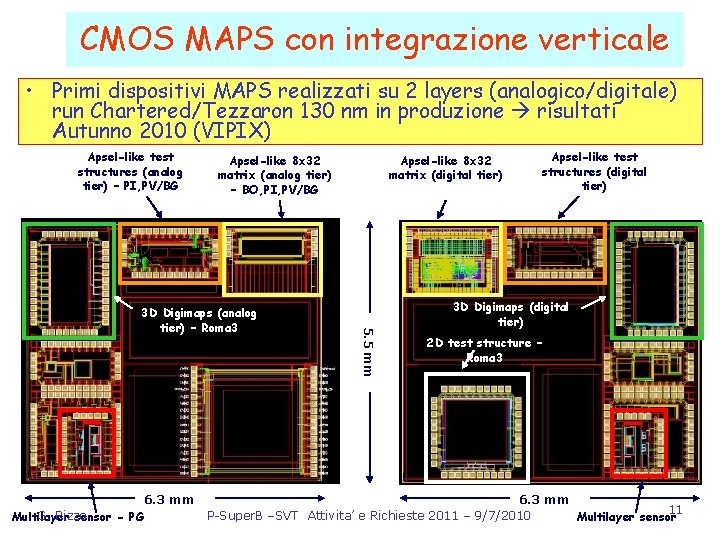

CMOS MAPS con integrazione verticale • Primi dispositivi MAPS realizzati su 2 layers (analogico/digitale) run Chartered/Tezzaron 130 nm in produzione risultati Autunno 2010 (VIPIX) Apsel-like test structures (analog tier) – PI, PV/BG Apsel-like 8 x 32 matrix (analog tier) – BO, PI, PV/BG 6. 3 mm G. Rizzo Multilayer sensor - PG 5. 5 mm 3 D Digimaps (analog tier) – Roma 3 Apsel-like 8 x 32 matrix (digital tier) Apsel-like test structures (digital tier) 3 D Digimaps (digital tier) 2 D test structure – Roma 3 6. 3 mm 11 P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 Multilayer sensor

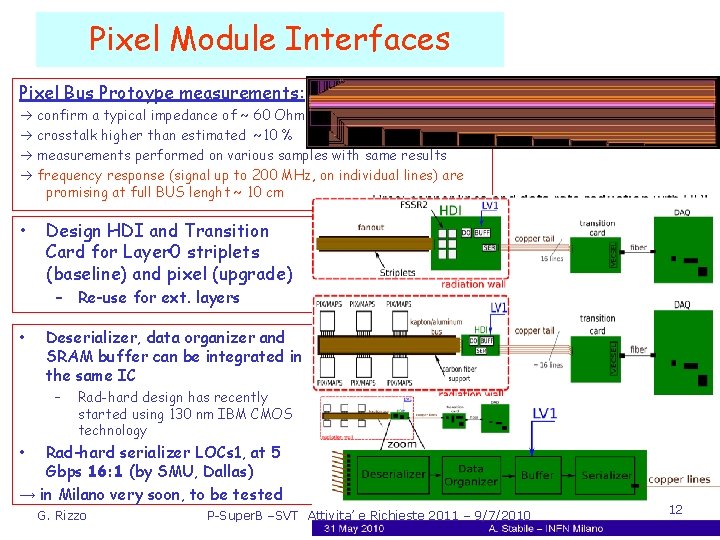

Pixel Module Interfaces Pixel Bus Protoype measurements: confirm a typical impedance of ~ 60 Ohm crosstalk higher than estimated ~10 % measurements performed on various samples with same results frequency response (signal up to 200 MHz, on individual lines) are promising at full BUS lenght ~ 10 cm • Design HDI and Transition Card for Layer 0 striplets (baseline) and pixel (upgrade) – Re-use for ext. layers • Deserializer, data organizer and SRAM buffer can be integrated in the same IC – Rad-hard design has recently started using 130 nm IBM CMOS technology • Rad-hard serializer LOCs 1, at 5 Gbps 16: 1 (by SMU, Dallas) → in Milano very soon, to be tested G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 12

Light pixel module support & cooling • • • Light support with integrated cooling needed for pixel module: P~2 W/cm 2 Carbon Fiber support with microchannel for coolant fluid developed in Pisa: – Total support/cooling thickness = 0. 28 % X 0 full module, 0. 15% X 0 net module Thermo-hydraulic measurements in TFD Lab: results within specs 700 mm Peek 700 mm tube 12. 8 mm Full Module C = 0. 28% C 0 Net Module Carbon Fiber Pultrusion C = 0. 15% C 0 Grande interesse e riscontri molto positivi in tutta la comunita’ per gli sviluppi sul cooling a microcanali! G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 13

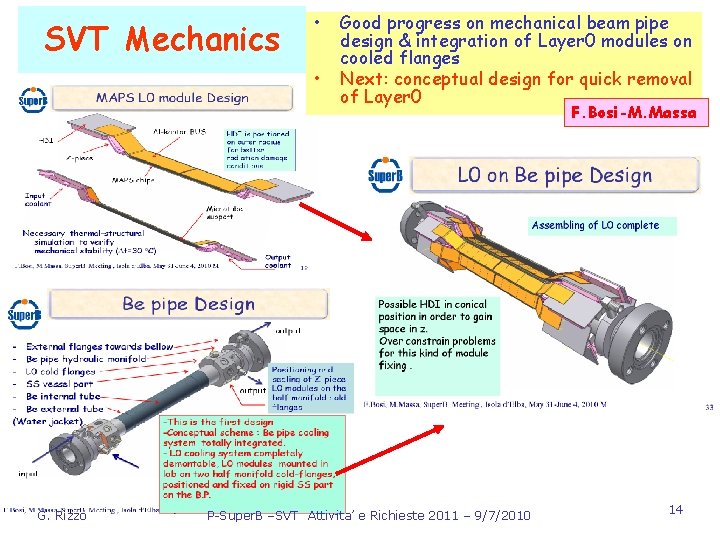

SVT Mechanics • • Good progress on mechanical beam pipe design & integration of Layer 0 modules on cooled flanges Next: conceptual design for quick removal of Layer 0 F. Bosi-M. Massa G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 14

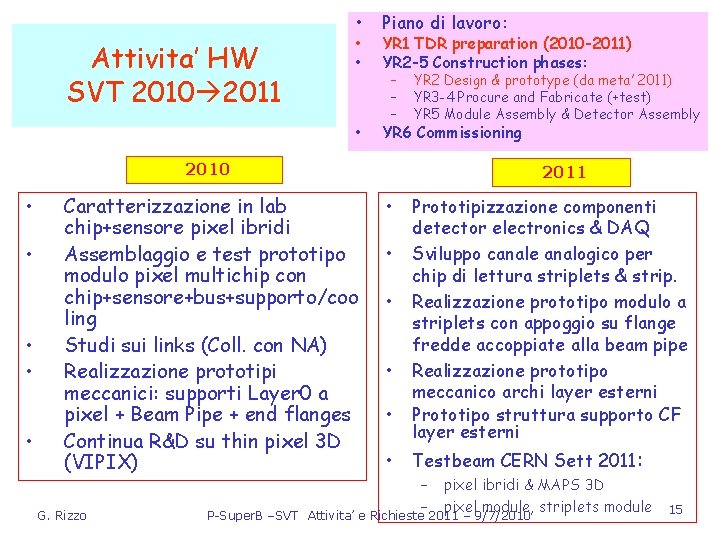

• Attivita’ HW SVT 2010 2011 • • • Piano di lavoro: YR 1 TDR preparation (2010 -2011) YR 2 -5 Construction phases: – – – YR 2 Design & prototype (da meta’ 2011) YR 3 -4 Procure and Fabricate (+test) YR 5 Module Assembly & Detector Assembly YR 6 Commissioning 2010 • • • Caratterizzazione in lab chip+sensore pixel ibridi Assemblaggio e test prototipo modulo pixel multichip con chip+sensore+bus+supporto/coo ling Studi sui links (Coll. con NA) Realizzazione prototipi meccanici: supporti Layer 0 a pixel + Beam Pipe + end flanges Continua R&D su thin pixel 3 D (VIPIX) G. Rizzo 2011 • • • Prototipizzazione componenti detector electronics & DAQ Sviluppo canale analogico per chip di lettura striplets & strip. Realizzazione prototipo modulo a striplets con appoggio su flange fredde accoppiate alla beam pipe Realizzazione prototipo meccanico archi layer esterni Prototipo struttura supporto CF layer esterni Testbeam CERN Sett 2011: – – pixel ibridi & MAPS 3 D pixel module, striplets module P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 15

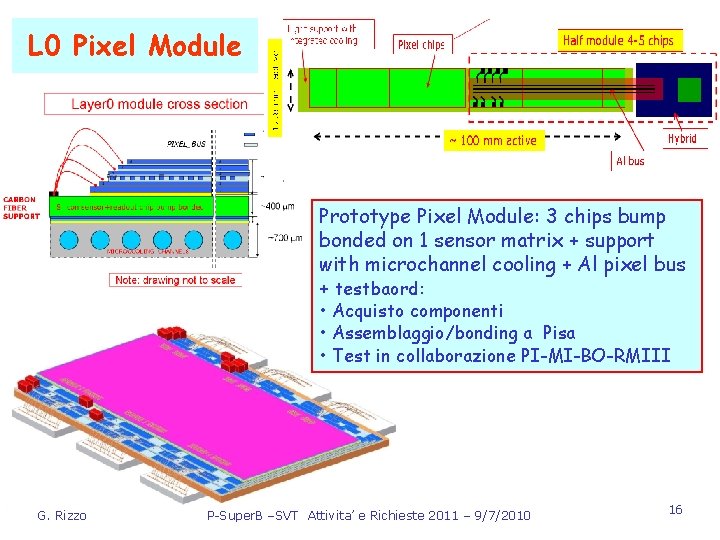

L 0 Pixel Module Prototype Pixel Module: 3 chips bump bonded on 1 sensor matrix + support with microchannel cooling + Al pixel bus + testbaord: • Acquisto componenti • Assemblaggio/bonding a Pisa • Test in collaborazione PI-MI-BO-RMIII G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 16

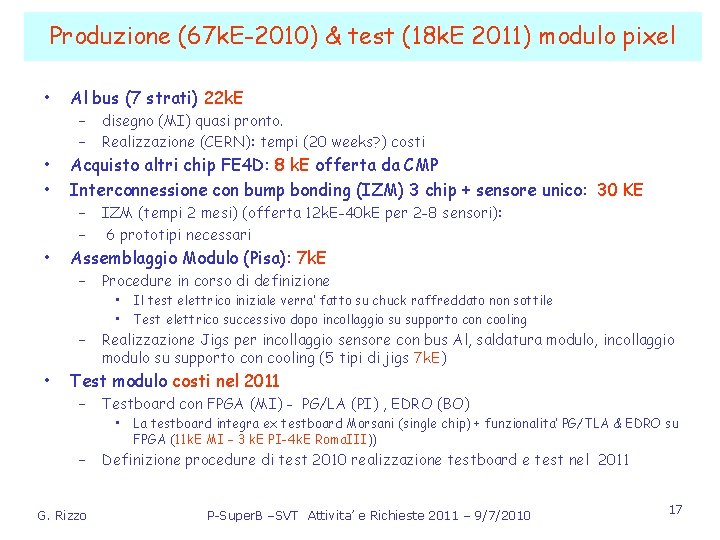

Produzione (67 k. E-2010) & test (18 k. E 2011) modulo pixel • • • Al bus (7 strati) 22 k. E – – disegno (MI) quasi pronto. Realizzazione (CERN): tempi (20 weeks? ) costi Acquisto altri chip FE 4 D: 8 k. E offerta da CMP Interconnessione con bump bonding (IZM) 3 chip + sensore unico: 30 KE – – IZM (tempi 2 mesi) (offerta 12 k. E-40 k. E per 2 -8 sensori): 6 prototipi necessari Assemblaggio Modulo (Pisa): 7 k. E – Procedure in corso di definizione – Realizzazione Jigs per incollaggio sensore con bus Al, saldatura modulo, incollaggio modulo su supporto con cooling (5 tipi di jigs 7 k. E) • Il test elettrico iniziale verra’ fatto su chuck raffreddato non sottile • Test elettrico successivo dopo incollaggio su supporto con cooling Test modulo costi nel 2011 – Testboard con FPGA (MI) - PG/LA (PI) , EDRO (BO) – Definizione procedure di test 2010 realizzazione testboard e test nel 2011 G. Rizzo • La testboard integra ex testboard Morsani (single chip) + funzionalita’ PG/TLA & EDRO su FPGA (11 k. E MI – 3 k. E PI-4 k. E Roma. III)) P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 17

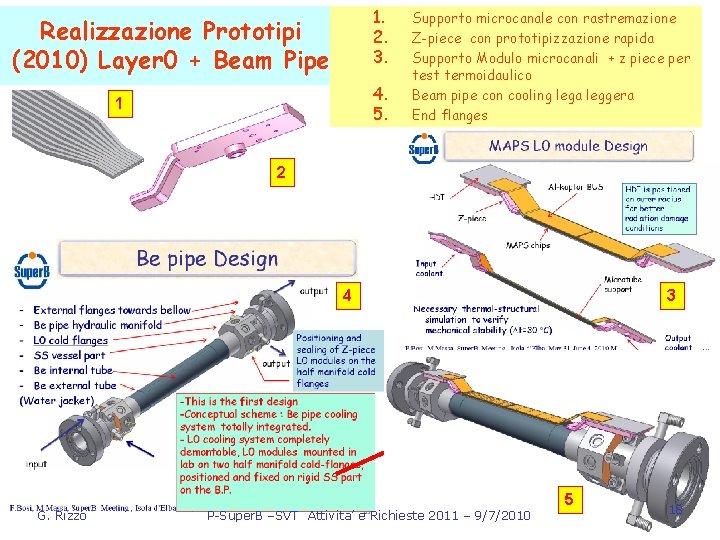

1. 2. 3. Realizzazione Prototipi (2010) Layer 0 + Beam Pipe 4. 5. 1 Supporto microcanale con rastremazione Z-piece con prototipizzazione rapida Supporto Modulo microcanali + z piece per test termoidaulico Beam pipe con cooling lega leggera End flanges 2 4 G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 3 5 18

Costi prototipi meccanici 2010 – 15 k. E 1. 2. 3. 4. 5. - G. Rizzo Supporto microcanale con rastremazione Deformazione elastica (1 k. E) & realizzazione con processo termoplastico (5 k. E) Z-piece con prototipizzazione rapida (1 k. E) Supporto Modulo microcanali + z piece per test termoidaulico (maschere incollaggi 2 k. E) Beam pipe lega leggera 6 k. E Posizionamento di precisione del modulo rispetto alle flange (boccole di alta precisione incollate allo z piece sotto CMM) 0. 5 k. E Realizzazione end flanges 4 k. E gia’ finanziati 2010 P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 19

Integrazione richieste finanziarie SVT 2010 • Per completare attivita’ 2010 SVT necessari 92 k. E consumi – Integrazione costi bump-bonding IZM singoli chip + matrice 5 k. E PV. – Realizzazione pixel module 67 k. E • Al BUS 22 k. E MI • Chips addizionali 8 k. E PI • Bump-bonding 30 k. E PI • Jigs per assemblaggio 7 k. E PI – Prototipi meccanici 15 k. E PI – Test sui links 5 k. E MI • Probe 16 ch 300 MHz per Pattern. Gen. 6 k. E INV (PI) • Missioni nelle diverse sedi G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 20

Dettaglio richieste 2011 G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 21

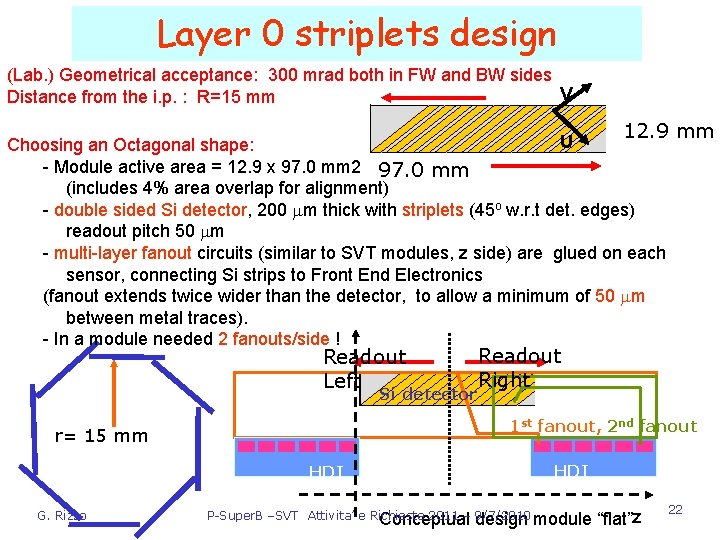

Layer 0 striplets design (Lab. ) Geometrical acceptance: 300 mrad both in FW and BW sides V Distance from the i. p. : R=15 mm 12. 9 mm U Choosing an Octagonal shape: - Module active area = 12. 9 x 97. 0 mm 2 97. 0 mm (includes 4% area overlap for alignment) - double sided Si detector, 200 mm thick with striplets (45 o w. r. t det. edges) readout pitch 50 mm - multi-layer fanout circuits (similar to SVT modules, z side) are glued on each sensor, connecting Si strips to Front End Electronics (fanout extends twice wider than the detector, to allow a minimum of 50 mm between metal traces). - In a module needed 2 fanouts/side ! Readout Left Si detector 1 st fanout, 2 nd fanout r= 15 mm HDI G. Rizzo Readout Right HDI P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 Conceptual design module “flat”z 22

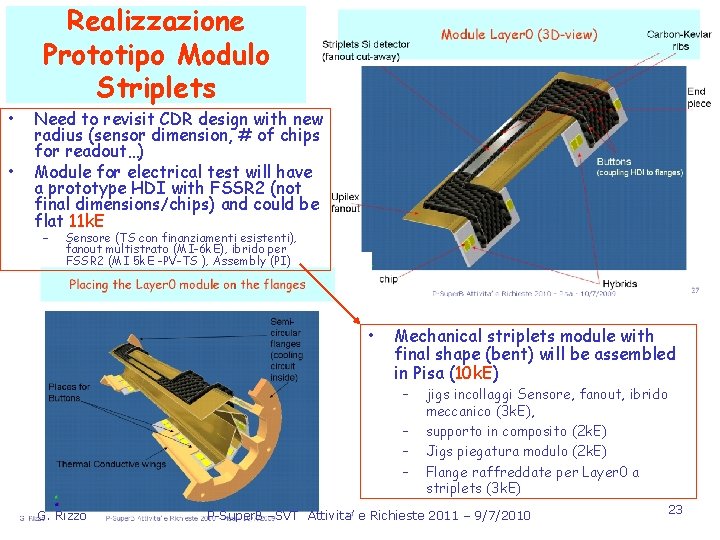

• • Realizzazione Prototipo Modulo Striplets Need to revisit CDR design with new radius (sensor dimension, # of chips for readout…) Module for electrical test will have a prototype HDI with FSSR 2 (not final dimensions/chips) and could be flat 11 k. E – Sensore (TS con finanziamenti esistenti), fanout multistrato (MI-6 k. E), ibrido per FSSR 2 (MI 5 k. E -PV-TS ), Assembly (PI) • Mechanical striplets module with final shape (bent) will be assembled in Pisa (10 k. E) – – G. Rizzo jigs incollaggi Sensore, fanout, ibrido meccanico (3 k. E), supporto in composito (2 k. E) Jigs piegatura modulo (2 k. E) Flange raffreddate per Layer 0 a striplets (3 k. E) P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 23

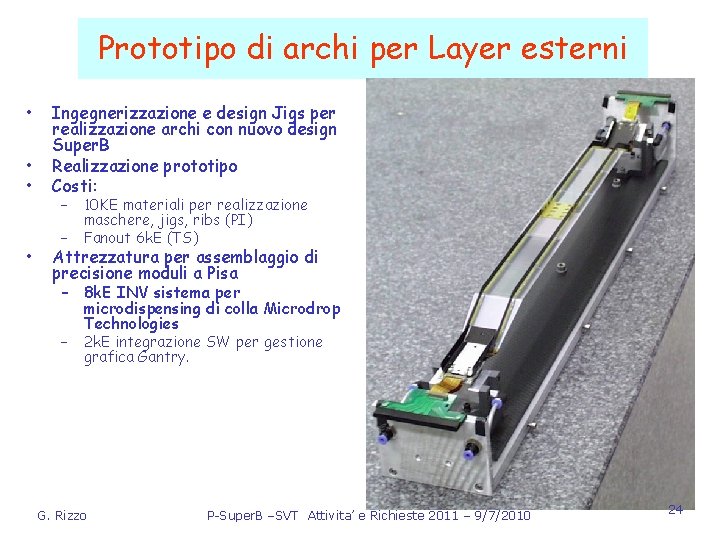

Prototipo di archi per Layer esterni • • Ingegnerizzazione e design Jigs per realizzazione archi con nuovo design Super. B Realizzazione prototipo Costi: – – 10 KE materiali per realizzazione maschere, jigs, ribs (PI) Fanout 6 k. E (TS) Attrezzatura per assemblaggio di precisione moduli a Pisa – 8 k. E INV sistema per – microdispensing di colla Microdrop Technologies 2 k. E integrazione SW per gestione grafica Gantry. G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 24

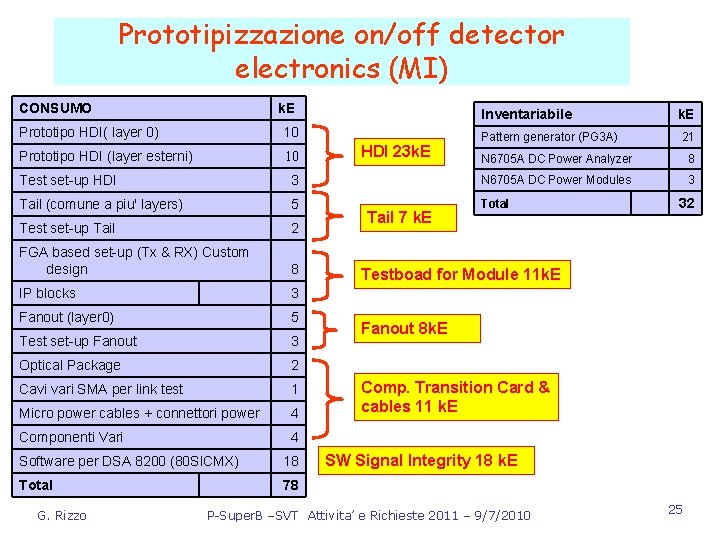

Prototipizzazione on/off detector electronics (MI) CONSUMO k. E Prototipo HDI( layer 0) 10 Prototipo HDI (layer esterni) 10 Test set-up HDI 3 Tail (comune a piu' layers) 5 Test set-up Tail 2 FGA based set-up (Tx & RX) Custom design 8 IP blocks 3 Fanout (layer 0) 5 Test set-up Fanout 3 Optical Package 2 Cavi vari SMA per link test 1 Micro power cables + connettori power 4 Componenti Vari 4 Software per DSA 8200 (80 SICMX) 18 Total 78 G. Rizzo Inventariabile HDI 23 k. E Tail 7 k. E Pattern generator (PG 3 A) k. E 21 N 6705 A DC Power Analyzer 8 N 6705 A DC Power Modules 3 Total 32 Testboad for Module 11 k. E Fanout 8 k. E Comp. Transition Card & cables 11 k. E SW Signal Integrity 18 k. E P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 25

Prototipi DAQ board per Super. B - BO Clear roles of these boards: • • Provide an interface for chip programming Data reading (push/pull modes) Handling of trigger information Chip synchronization SVT-wide Known pieces to implement: • • Clock reception and distribution (details? ) 12 x 1 Gbit/s and 2 x 2. 5 Gbit/s optical links onboard Storage memory (>128 Mbytes) for event handling • Prototipo scala reale FEB board • • Da capire cosa deve ancora essere definito a livello di esperimento (L 1, FTCS, ECS) Soluzioni condivise per i link ottici vs DAQ? “Planning in the large”: adattabilità a diverse esigenze di F. E. (FSSR 2/3, In. MAPS, FE 4 D…) Costo stimato 2 prototipi (12+2 links): 13 k. E G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 26

Attivita’ a Trieste 2011 1) Partecipazione alla realizzazione di un (mezzo) modulo striplets: • • • - Design, procurement, test sensori - Test ibridi con FSSR 2 - Design e test fanout sottili Al su polyimide • Design geometria escelta tecnologia per sensori, fanout Contributo alla valutazione chip di front-end 2) Progetto dei layer esterni (sensori, fanout) per il TDR: • 3) Partecipazione al beam test 2011: • Responsabilità del telescopio di fascio e striplets G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 27

Attivita’ a Torino 2010 • Design dei moduli dei layer ext con la nuova geometria e meccanica di supporto di SVT. – Richieste finanziarie per acquisto CF 8 k. E per prototipi coni di supporto e ribs 5 k. E – Lavorazioni meccaniche per testbeam 5 k. E G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 28

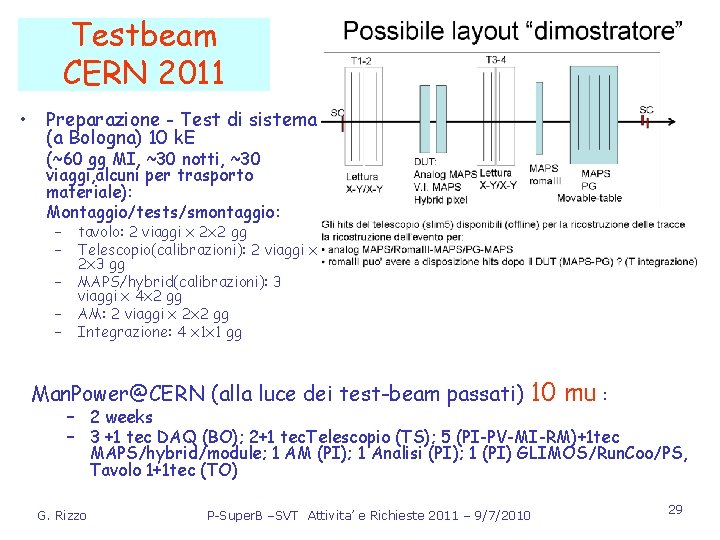

Testbeam CERN 2011 • Preparazione - Test di sistema (a Bologna) 10 k. E (~60 gg MI, ~30 notti, ~30 viaggi, alcuni per trasporto materiale): Montaggio/tests/smontaggio: – – – tavolo: 2 viaggi x 2 x 2 gg Telescopio(calibrazioni): 2 viaggi x 2 x 3 gg MAPS/hybrid(calibrazioni): 3 viaggi x 4 x 2 gg AM: 2 viaggi x 2 x 2 gg Integrazione: 4 x 1 x 1 gg Man. Power@CERN (alla luce dei test-beam passati) 10 mu : – 2 weeks – 3 +1 tec DAQ (BO); 2+1 tec. Telescopio (TS); 5 (PI-PV-MI-RM)+1 tec MAPS/hybrid/module; 1 AM (PI); 1 Analisi (PI); 1 (PI) GLIMOS/Run. Coo/PS, Tavolo 1+1 tec (TO) G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 29

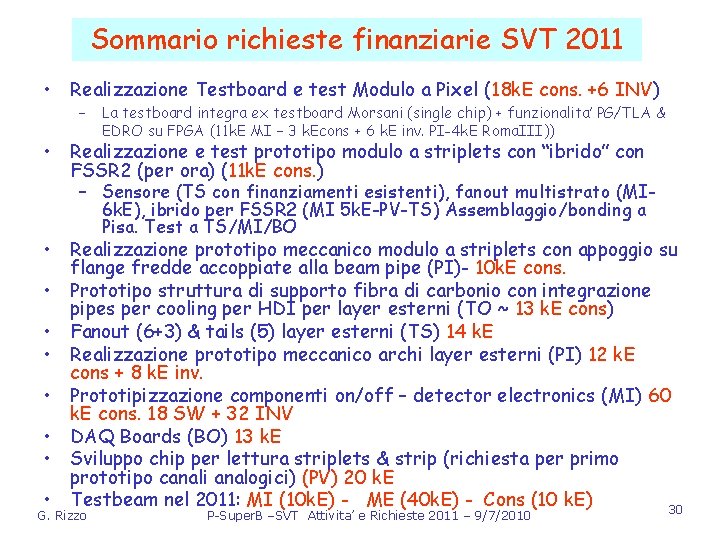

Sommario richieste finanziarie SVT 2011 • Realizzazione Testboard e test Modulo a Pixel (18 k. E cons. +6 INV) – La testboard integra ex testboard Morsani (single chip) + funzionalita’ PG/TLA & EDRO su FPGA (11 k. E MI – 3 k. Econs + 6 k. E inv. PI-4 k. E Roma. III)) • Realizzazione e test prototipo modulo a striplets con “ibrido” con FSSR 2 (per ora) (11 k. E cons. ) • • – Sensore (TS con finanziamenti esistenti), fanout multistrato (MI 6 k. E), ibrido per FSSR 2 (MI 5 k. E-PV-TS) Assemblaggio/bonding a Pisa. Test a TS/MI/BO Realizzazione prototipo meccanico modulo a striplets con appoggio su flange fredde accoppiate alla beam pipe (PI)- 10 k. E cons. Prototipo struttura di supporto fibra di carbonio con integrazione pipes per cooling per HDI per layer esterni (TO ~ 13 k. E cons) Fanout (6+3) & tails (5) layer esterni (TS) 14 k. E Realizzazione prototipo meccanico archi layer esterni (PI) 12 k. E cons + 8 k. E inv. Prototipizzazione componenti on/off – detector electronics (MI) 60 k. E cons. 18 SW + 32 INV DAQ Boards (BO) 13 k. E Sviluppo chip per lettura striplets & strip (richiesta per primo prototipo canali analogici) (PV) 20 k. E Testbeam nel 2011: MI (10 k. E) - ME (40 k. E) - Cons (10 k. E) 30 G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010

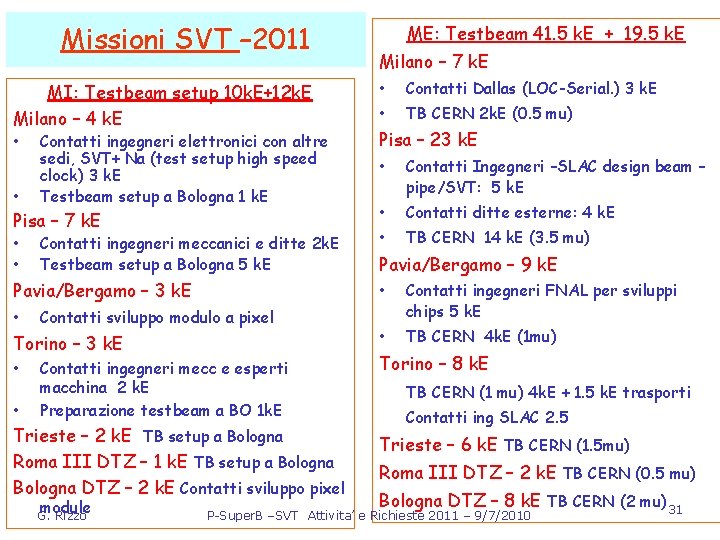

Missioni SVT – 2011 MI: Testbeam setup 10 k. E+12 k. E Milano – 4 k. E • • Contatti ingegneri elettronici con altre sedi, SVT+ Na (test setup high speed clock) 3 k. E Testbeam setup a Bologna 1 k. E Pisa – 7 k. E • • Contatti ingegneri meccanici e ditte 2 k. E Testbeam setup a Bologna 5 k. E Pavia/Bergamo – 3 k. E • Contatti sviluppo modulo a pixel Torino – 3 k. E • • Contatti ingegneri mecc e esperti macchina 2 k. E Preparazione testbeam a BO 1 k. E Trieste – 2 k. E TB setup a Bologna Roma III DTZ – 1 k. E TB setup a Bologna DTZ – 2 k. E Contatti sviluppo pixel module G. Rizzo ME: Testbeam 41. 5 k. E + 19. 5 k. E Milano – 7 k. E • Contatti Dallas (LOC-Serial. ) 3 k. E • TB CERN 2 k. E (0. 5 mu) Pisa – 23 k. E • Contatti Ingegneri –SLAC design beam – pipe/SVT: 5 k. E • Contatti ditte esterne: 4 k. E • TB CERN 14 k. E (3. 5 mu) Pavia/Bergamo – 9 k. E • Contatti ingegneri FNAL per sviluppi chips 5 k. E • TB CERN 4 k. E (1 mu) Torino – 8 k. E TB CERN (1 mu) 4 k. E + 1. 5 k. E trasporti Contatti ing SLAC 2. 5 Trieste – 6 k. E TB CERN (1. 5 mu) Roma III DTZ – 2 k. E TB CERN (0. 5 mu) Bologna DTZ – 8 k. E TB CERN (2 mu)31 P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010

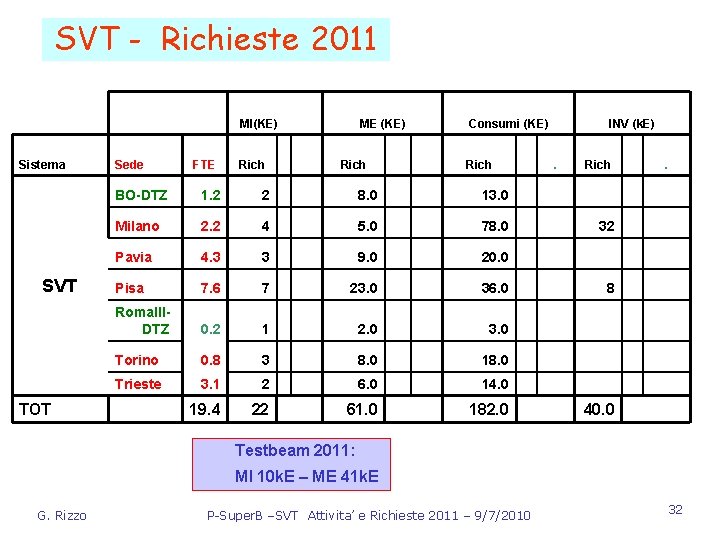

SVT - Richieste 2011 MI(KE) Sistema SVT TOT Sede FTE Rich ME (KE) Rich Consumi (KE) Rich BO-DTZ 1. 2 2 8. 0 13. 0 Milano 2. 2 4 5. 0 78. 0 Pavia 4. 3 3 9. 0 20. 0 Pisa 7. 6 7 23. 0 36. 0 Roma. IIIDTZ 0. 2 1 2. 0 3. 0 Torino 0. 8 3 8. 0 18. 0 Trieste 3. 1 2 6. 0 14. 0 19. 4 22 61. 0 182. 0 INV (k. E). Rich . 32 8 40. 0 Testbeam 2011: MI 10 k. E – ME 41 k. E G. Rizzo P-Super. B –SVT Attivita’ e Richieste 2011 – 9/7/2010 32

- Slides: 32