PSpice Training Guide Version PSD 16 5 2012

- Slides: 163

PSpice Training Guide Version PSD 16. 5 “ 2012 1 ITN ㈜아이티앤

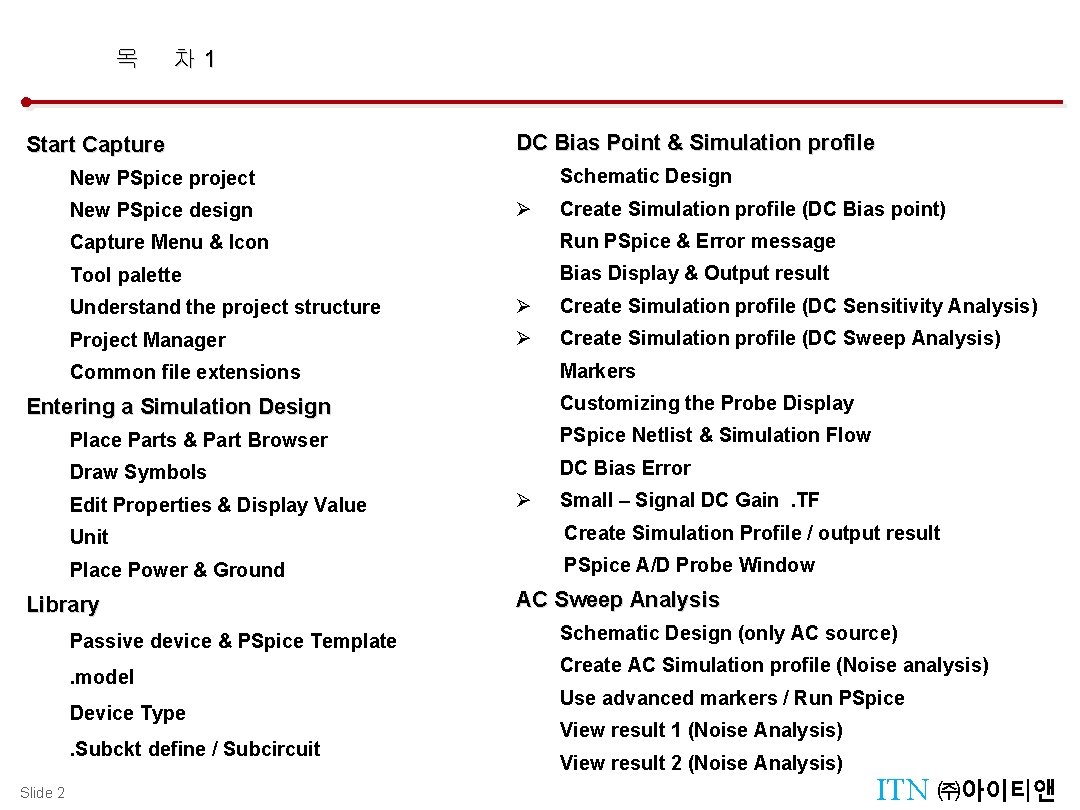

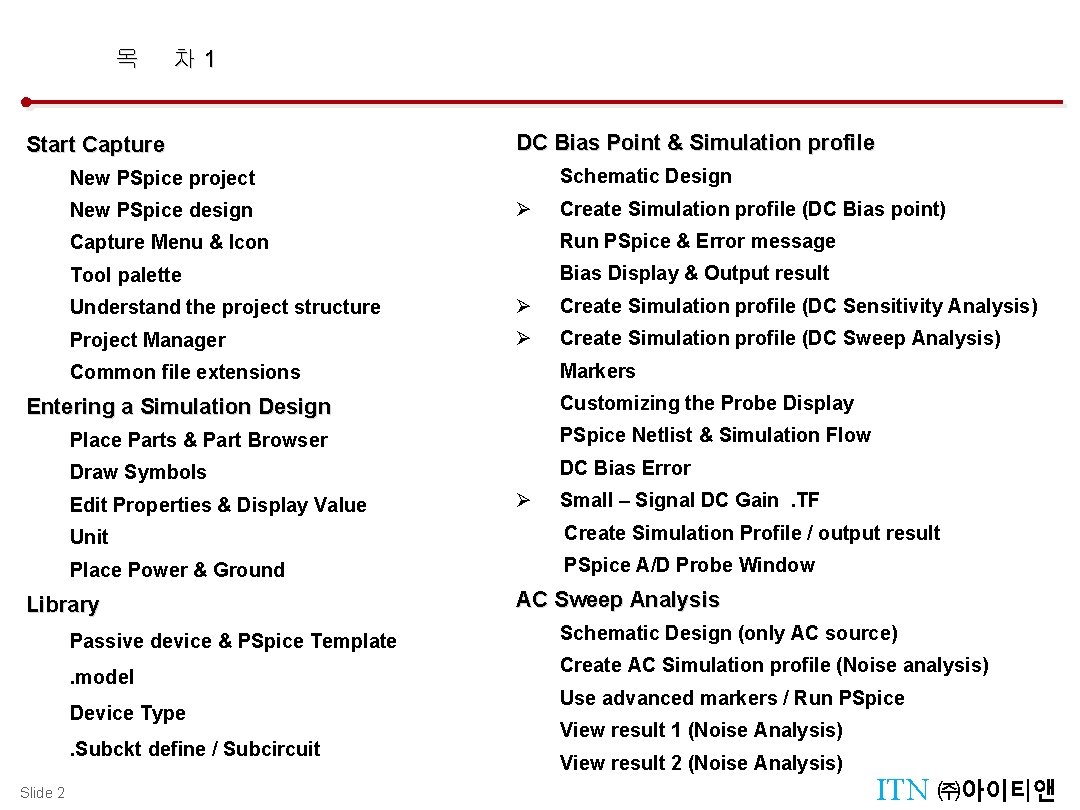

목 차 1 Start Capture DC Bias Point & Simulation profile Schematic Design New PSpice project New PSpice design Ø Capture Menu & Icon Run PSpice & Error message Tool palette Bias Display & Output result Understand the project structure Ø Create Simulation profile (DC Sensitivity Analysis) Project Manager Ø Create Simulation profile (DC Sweep Analysis) Markers Common file extensions Customizing the Probe Display Entering a Simulation Design Place Parts & Part Browser PSpice Netlist & Simulation Flow Draw Symbols DC Bias Error Edit Properties & Display Value Ø Small – Signal DC Gain. TF Unit Create Simulation Profile / output result Place Power & Ground PSpice A/D Probe Window Library Passive device & PSpice Template. model Device Type. Subckt define / Subcircuit Slide 2 Create Simulation profile (DC Bias point) AC Sweep Analysis Schematic Design (only AC source) Create AC Simulation profile (Noise analysis) Use advanced markers / Run PSpice View result 1 (Noise Analysis) View result 2 (Noise Analysis) ITN ㈜아이티앤

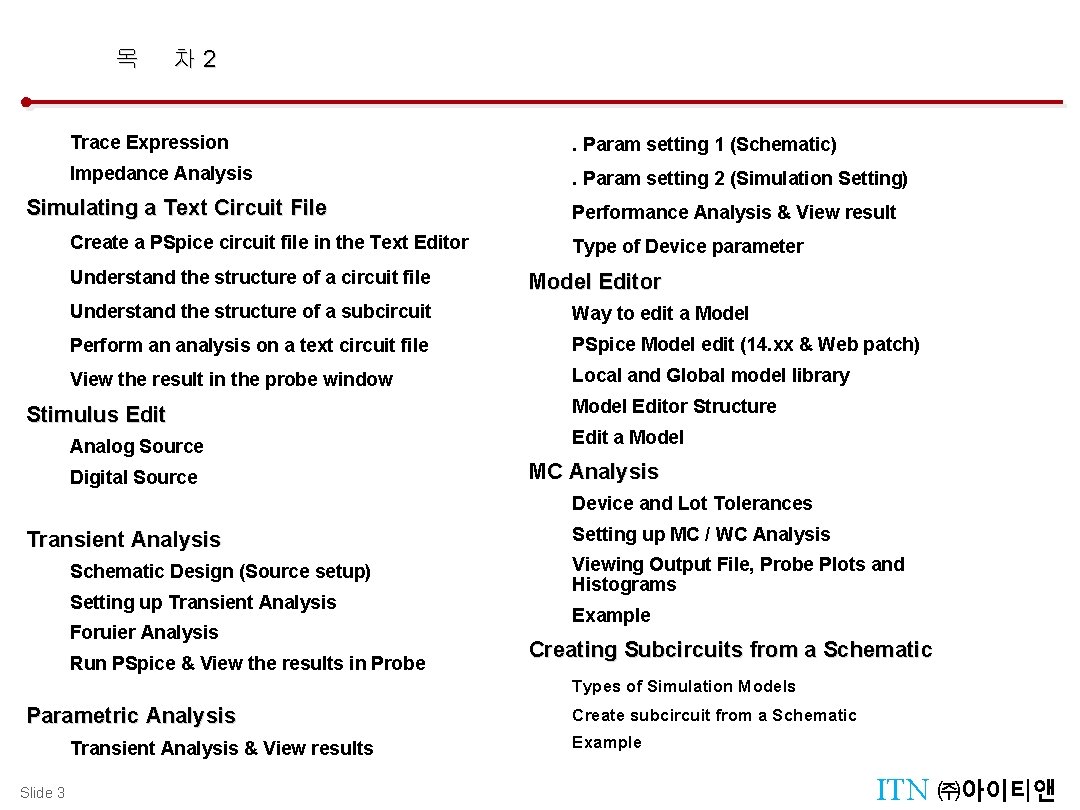

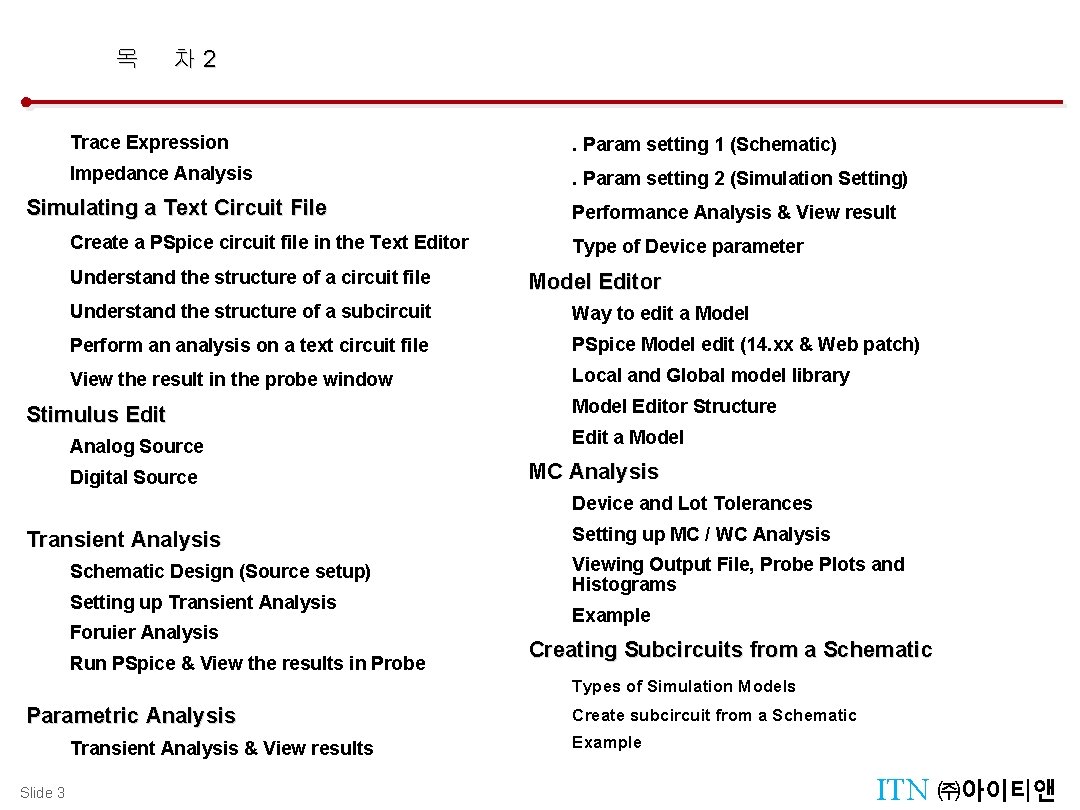

목 차 2 Trace Expression . Param setting 1 (Schematic) Impedance Analysis . Param setting 2 (Simulation Setting) Simulating a Text Circuit File Create a PSpice circuit file in the Text Editor Understand the structure of a circuit file Performance Analysis & View result Type of Device parameter Model Editor Understand the structure of a subcircuit Way to edit a Model Perform an analysis on a text circuit file PSpice Model edit (14. xx & Web patch) View the result in the probe window Local and Global model library Stimulus Edit Analog Source Digital Source Model Editor Structure Edit a Model MC Analysis Device and Lot Tolerances Transient Analysis Schematic Design (Source setup) Setting up Transient Analysis Foruier Analysis Run PSpice & View the results in Probe Setting up MC / WC Analysis Viewing Output File, Probe Plots and Histograms Example Creating Subcircuits from a Schematic Types of Simulation Models Parametric Analysis Transient Analysis & View results Slide 3 Create subcircuit from a Schematic Example ITN ㈜아이티앤

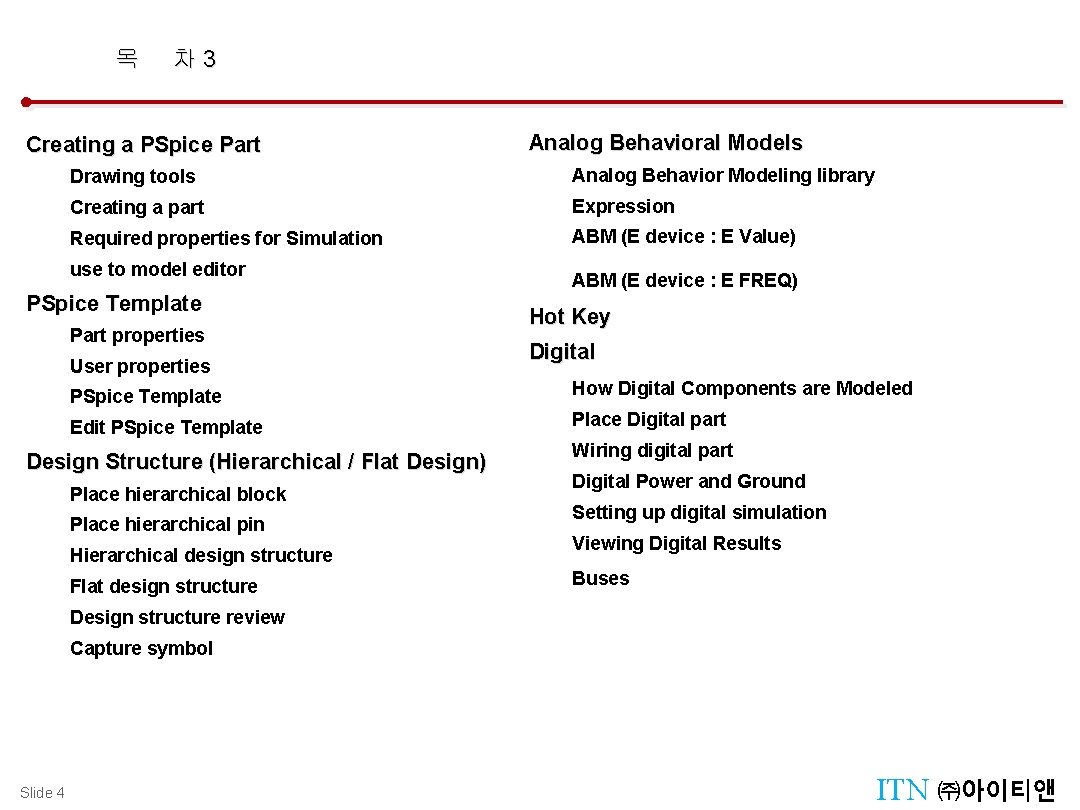

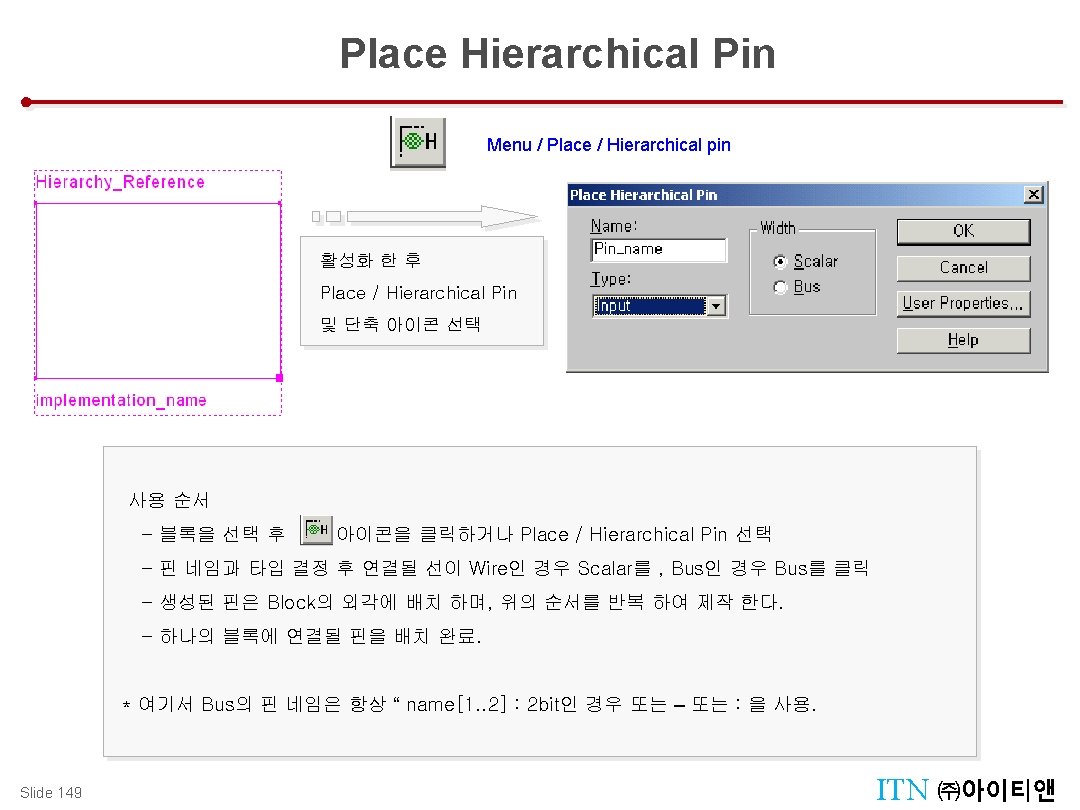

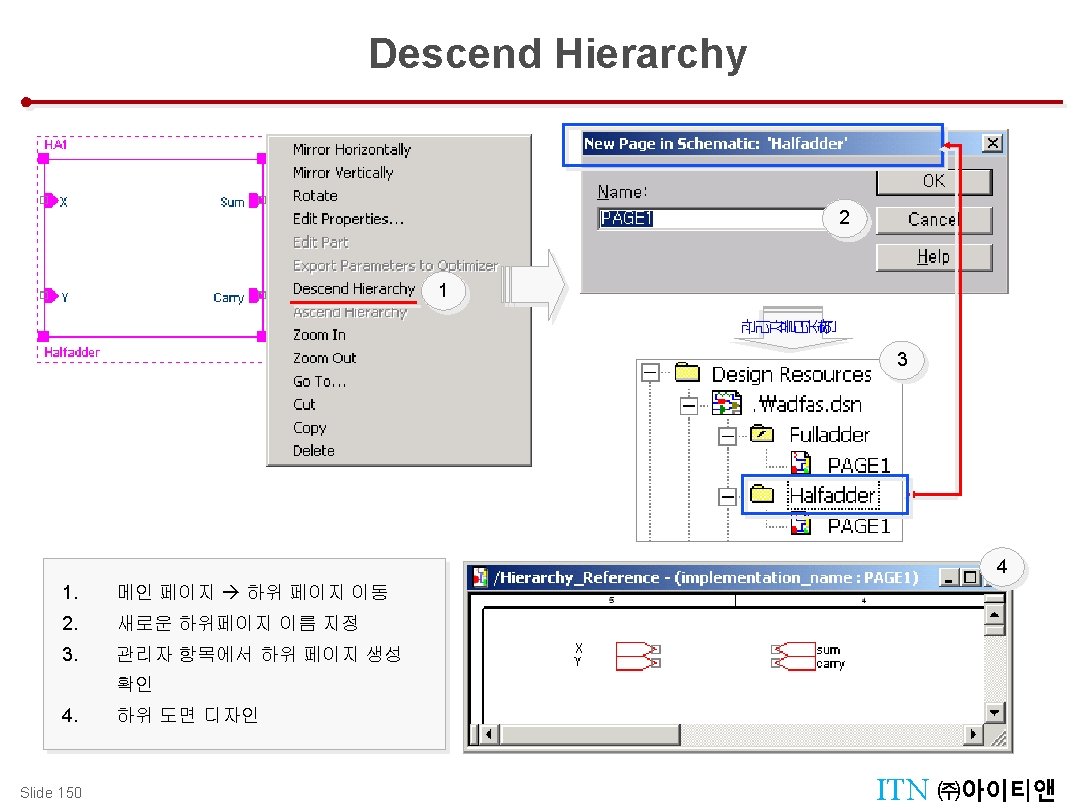

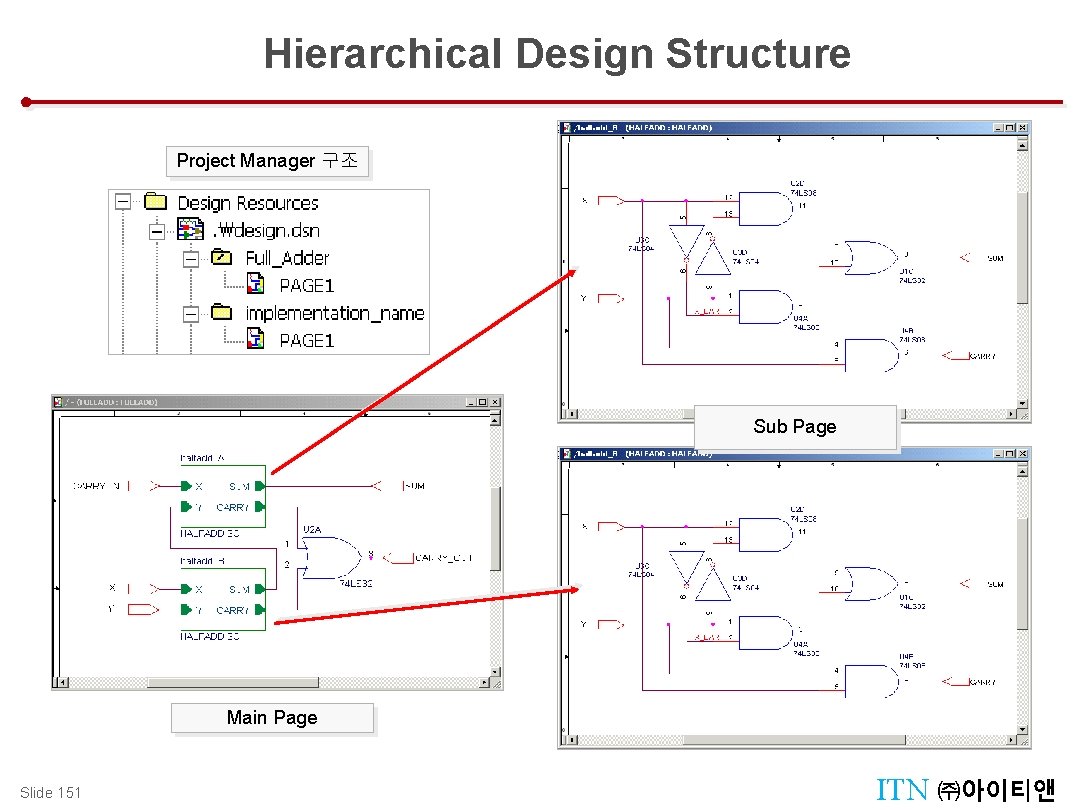

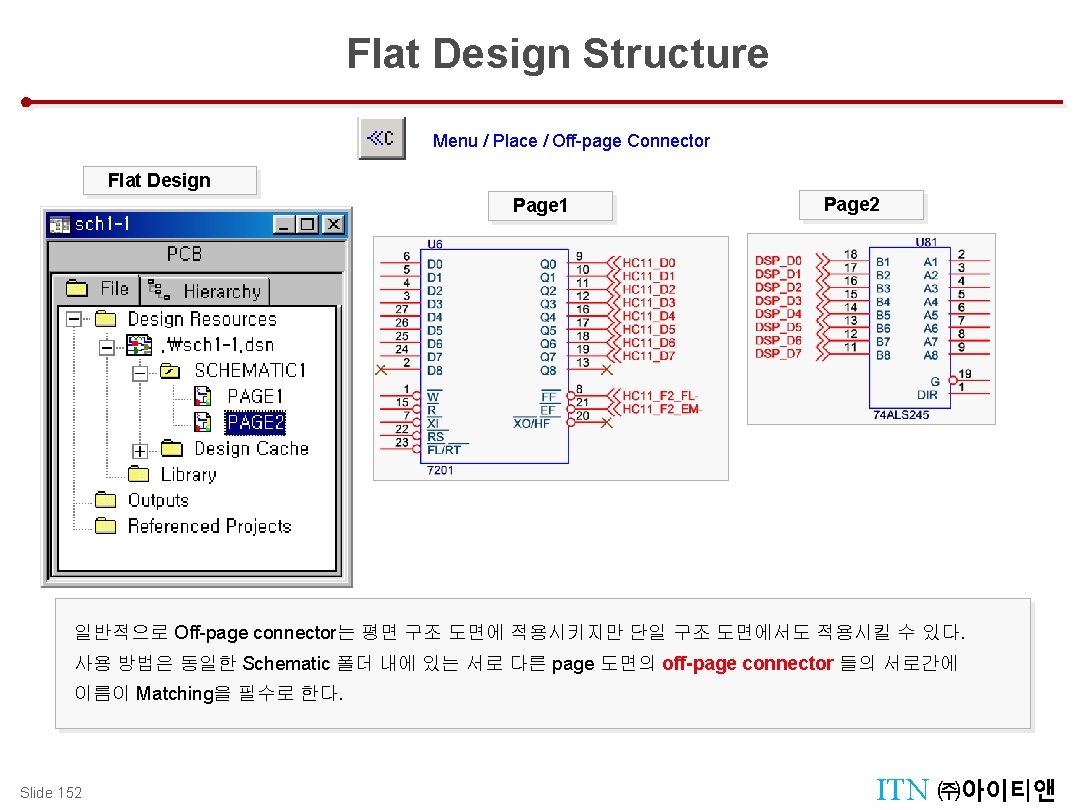

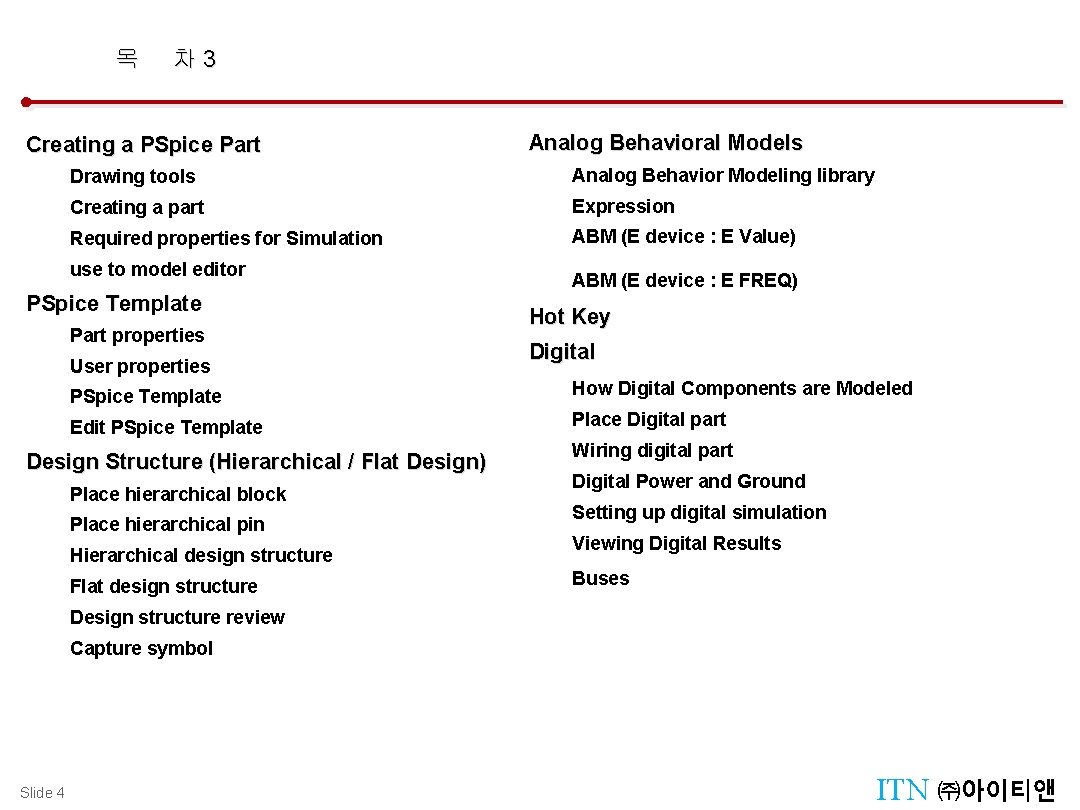

목 차 3 Creating a PSpice Part Analog Behavioral Models Drawing tools Analog Behavior Modeling library Creating a part Expression Required properties for Simulation ABM (E device : E Value) use to model editor PSpice Template Part properties User properties ABM (E device : E FREQ) Hot Key Digital PSpice Template How Digital Components are Modeled Edit PSpice Template Place Digital part Design Structure (Hierarchical / Flat Design) Place hierarchical block Place hierarchical pin Hierarchical design structure Flat design structure Wiring digital part Digital Power and Ground Setting up digital simulation Viewing Digital Results Buses Design structure review Capture symbol Slide 4 ITN ㈜아이티앤

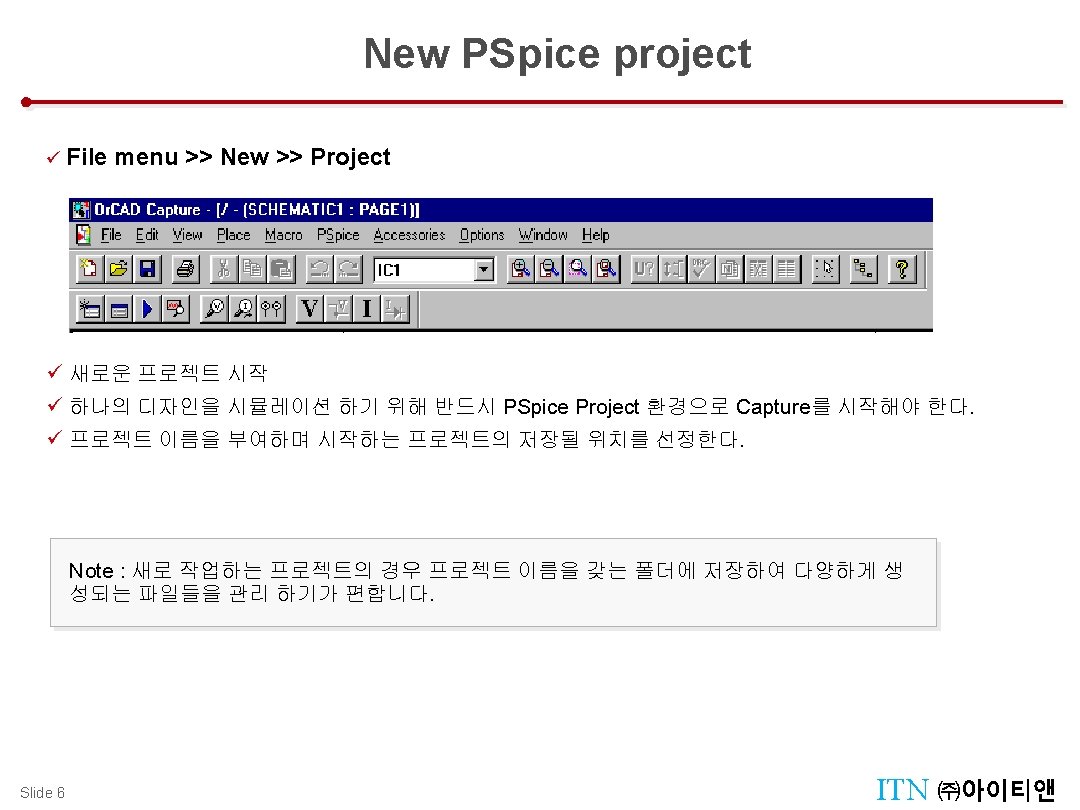

Start Capture New PSpice project New PSpice design Capture Menu & Icon Tool palette Understand the project structure Project Manager Common file extensions Slide 5 ITN ㈜아이티앤

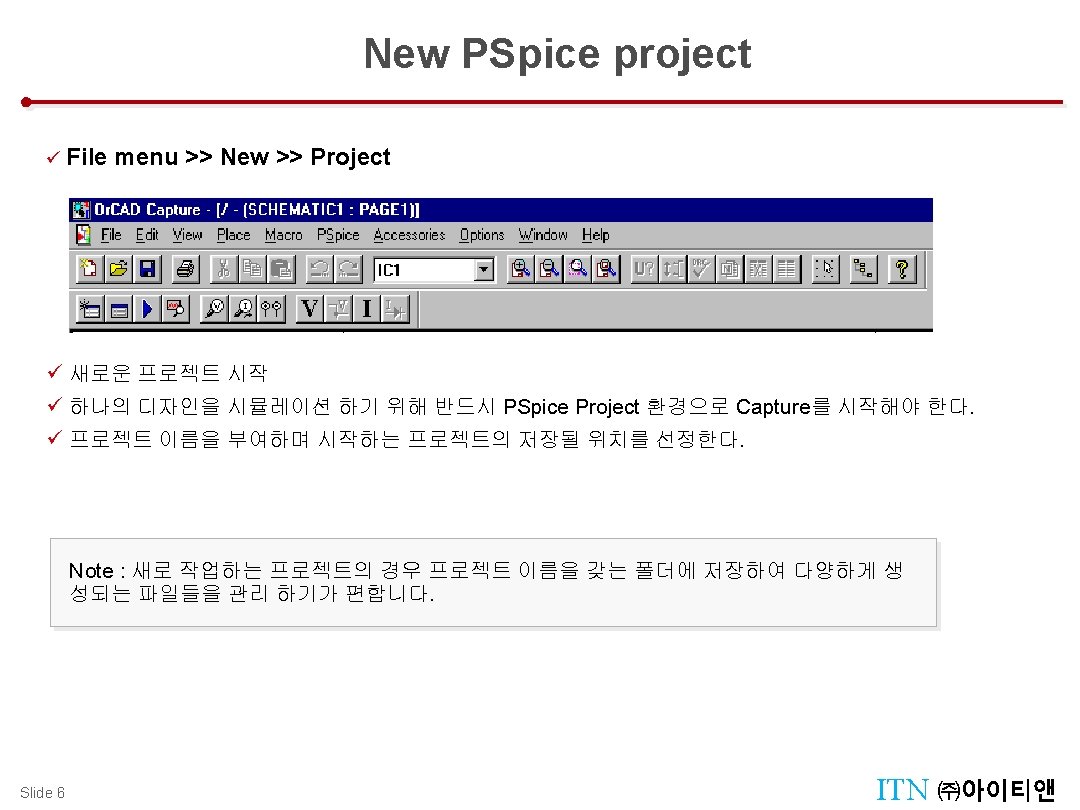

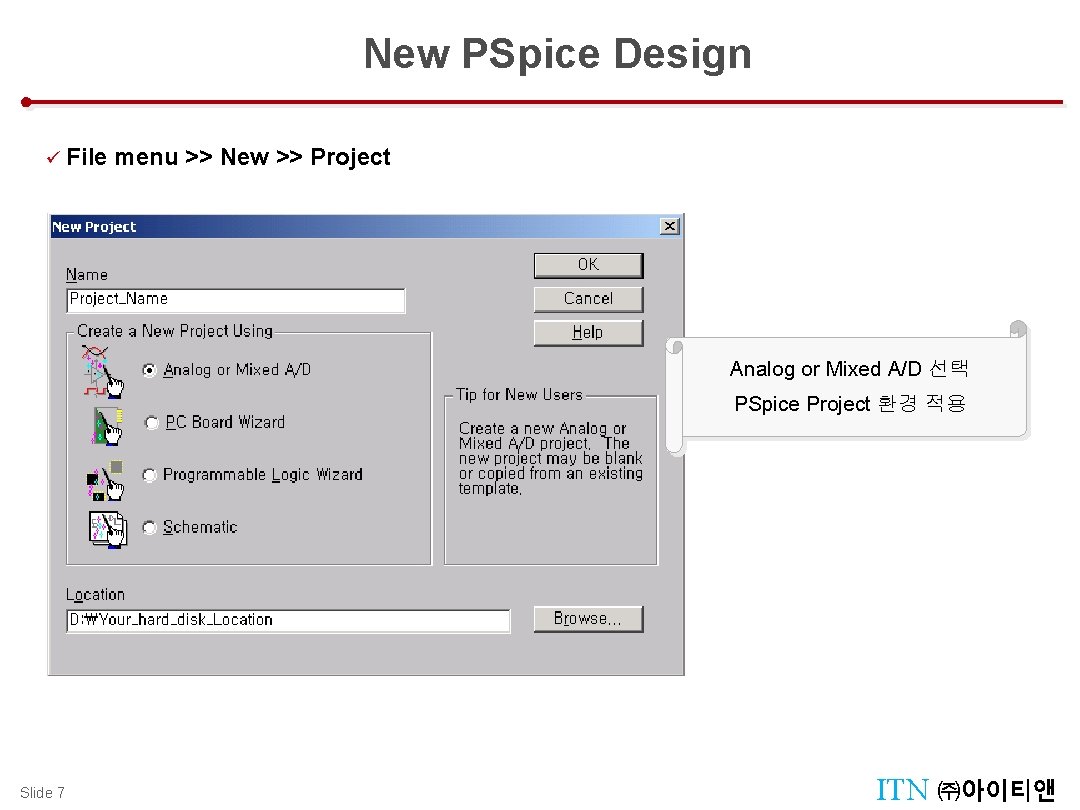

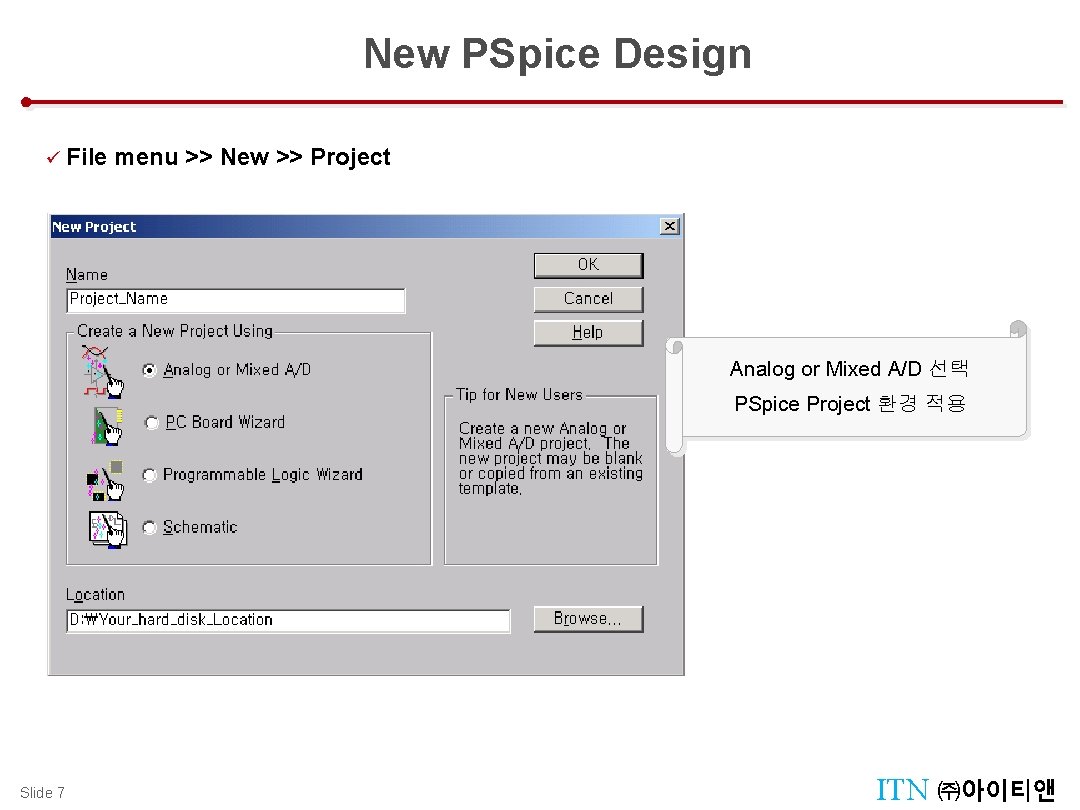

New PSpice Design ü File menu >> New >> Project Analog or Mixed A/D 선택 PSpice Project 환경 적용 Slide 7 ITN ㈜아이티앤

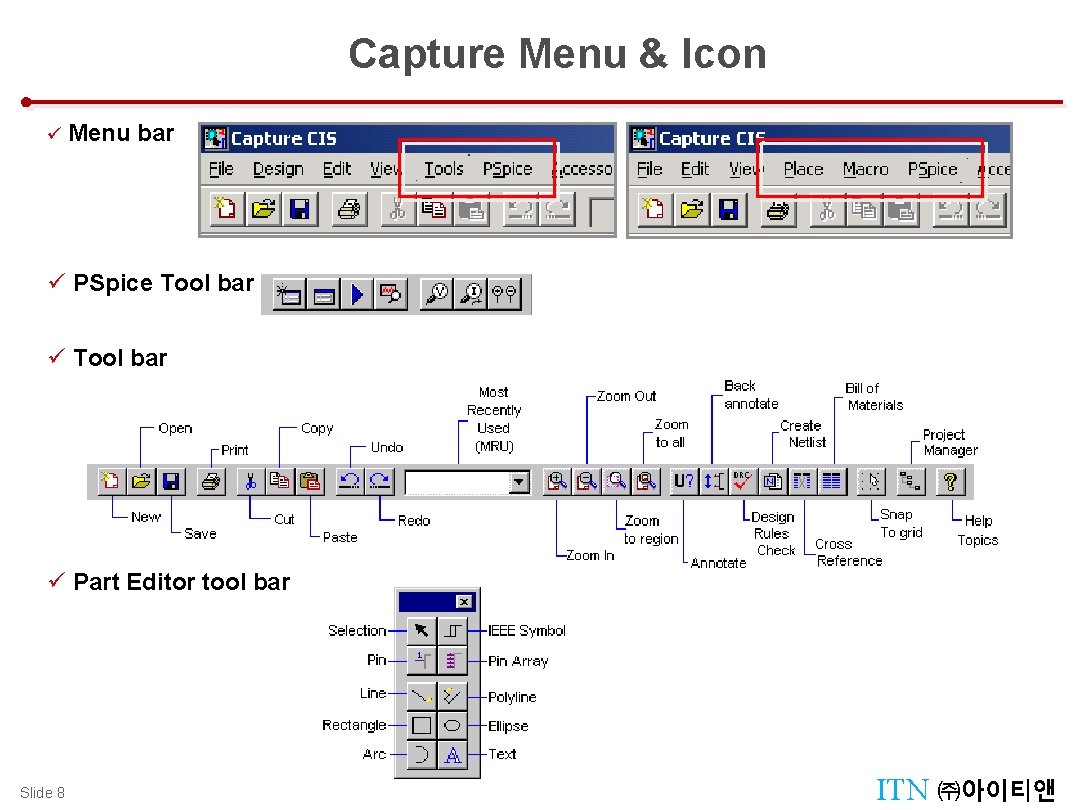

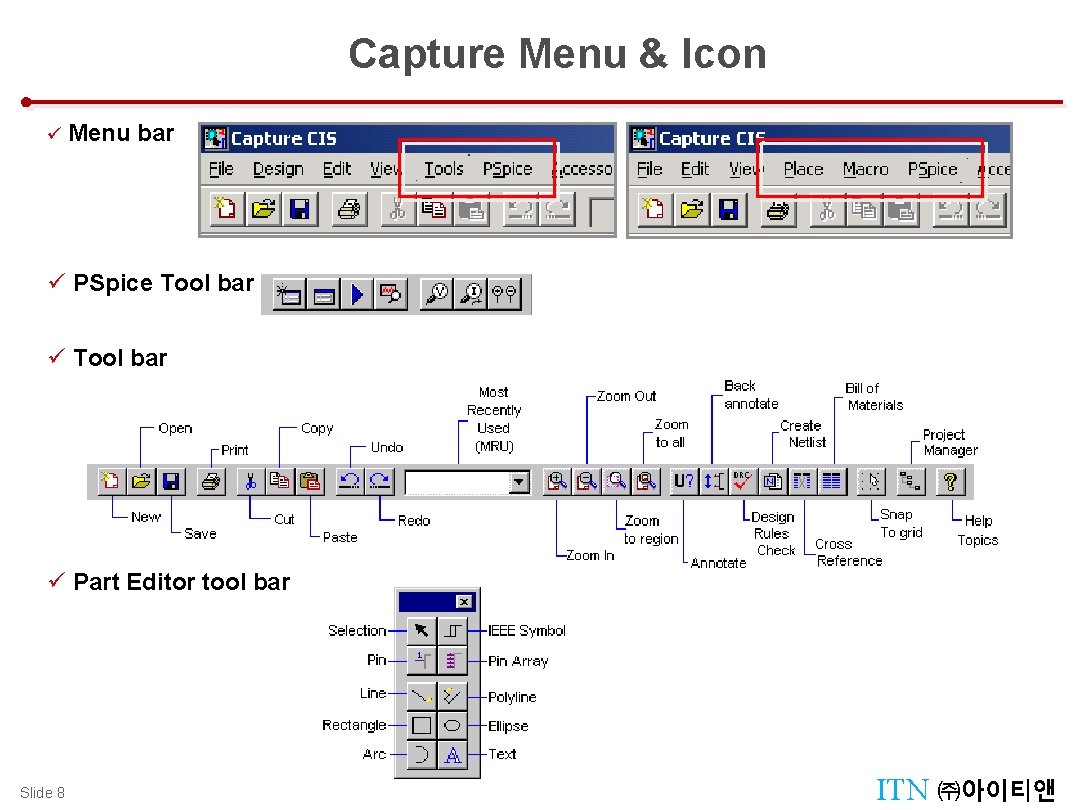

Capture Menu & Icon ü Menu bar ü PSpice Tool bar ü Part Editor tool bar Slide 8 ITN ㈜아이티앤

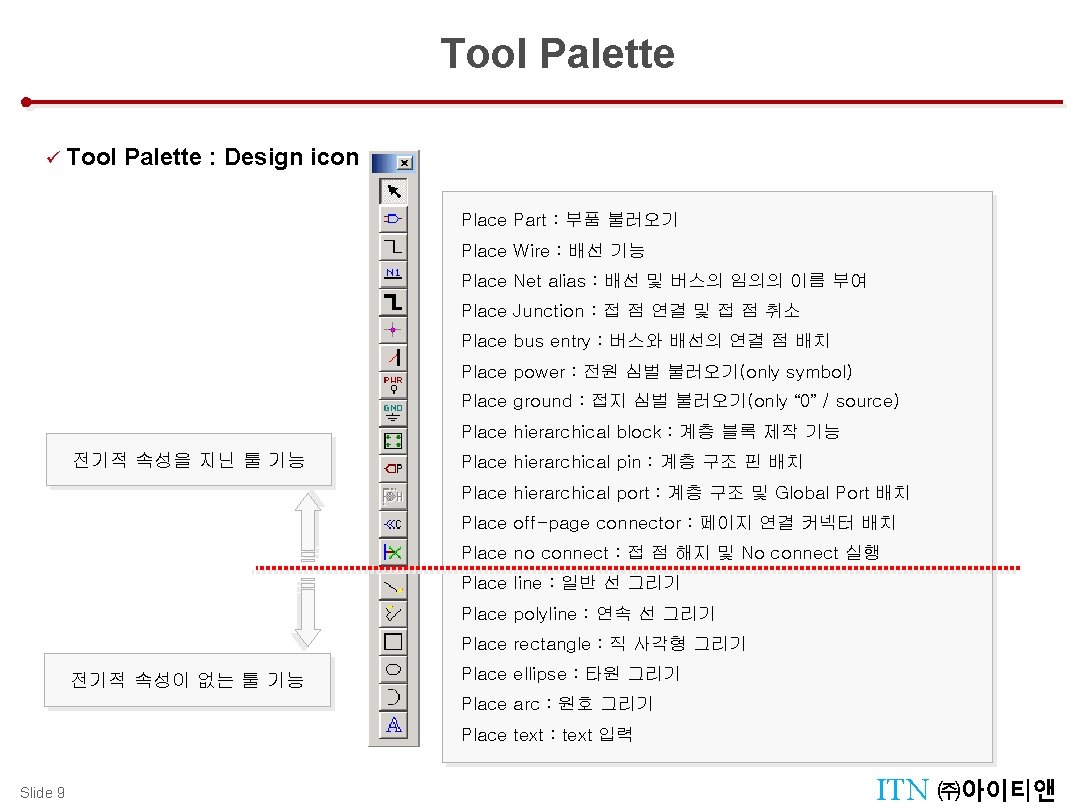

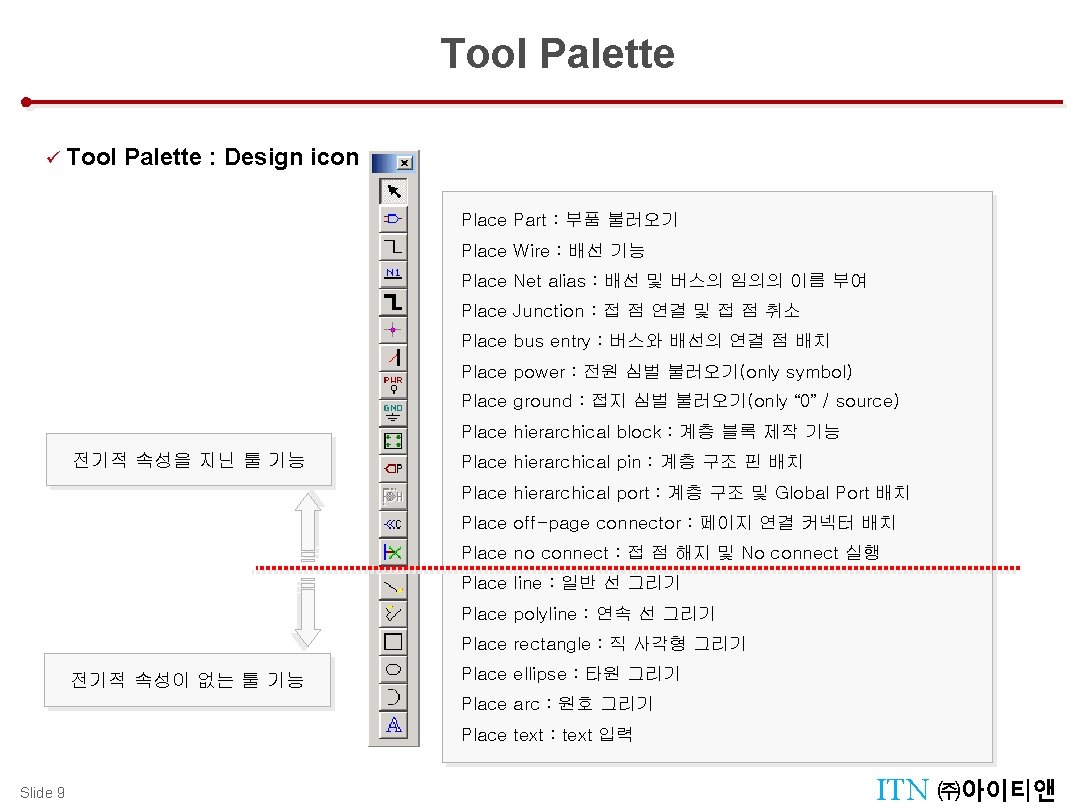

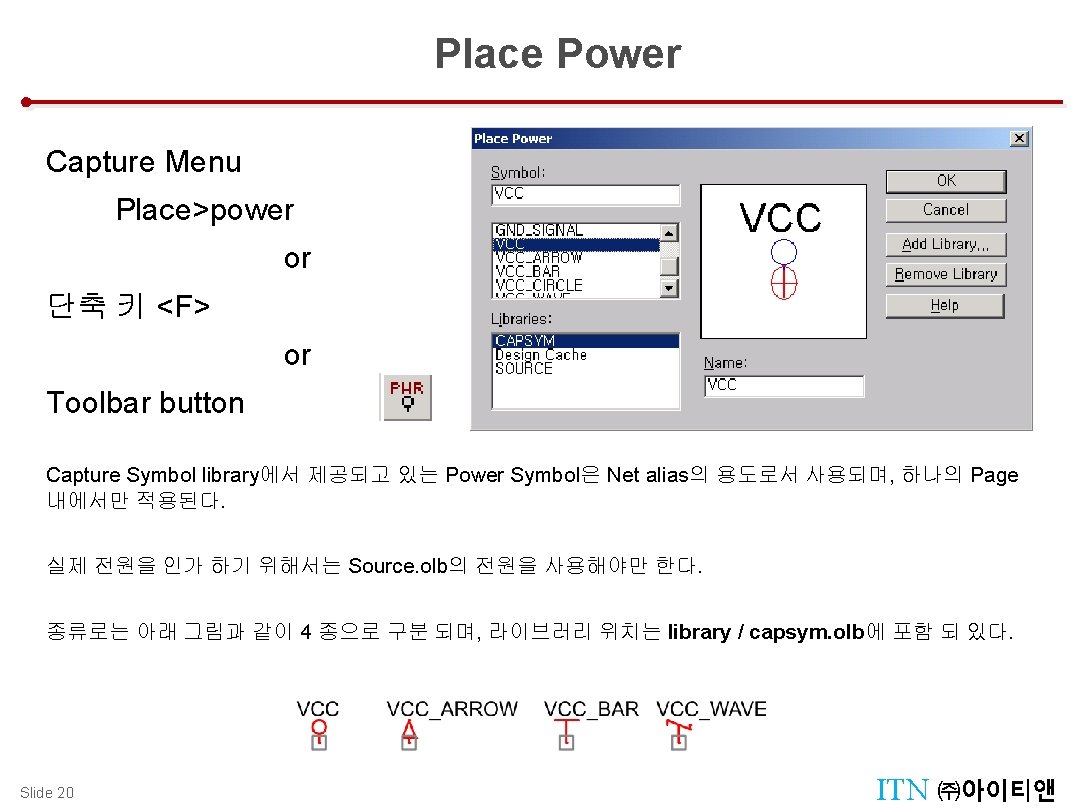

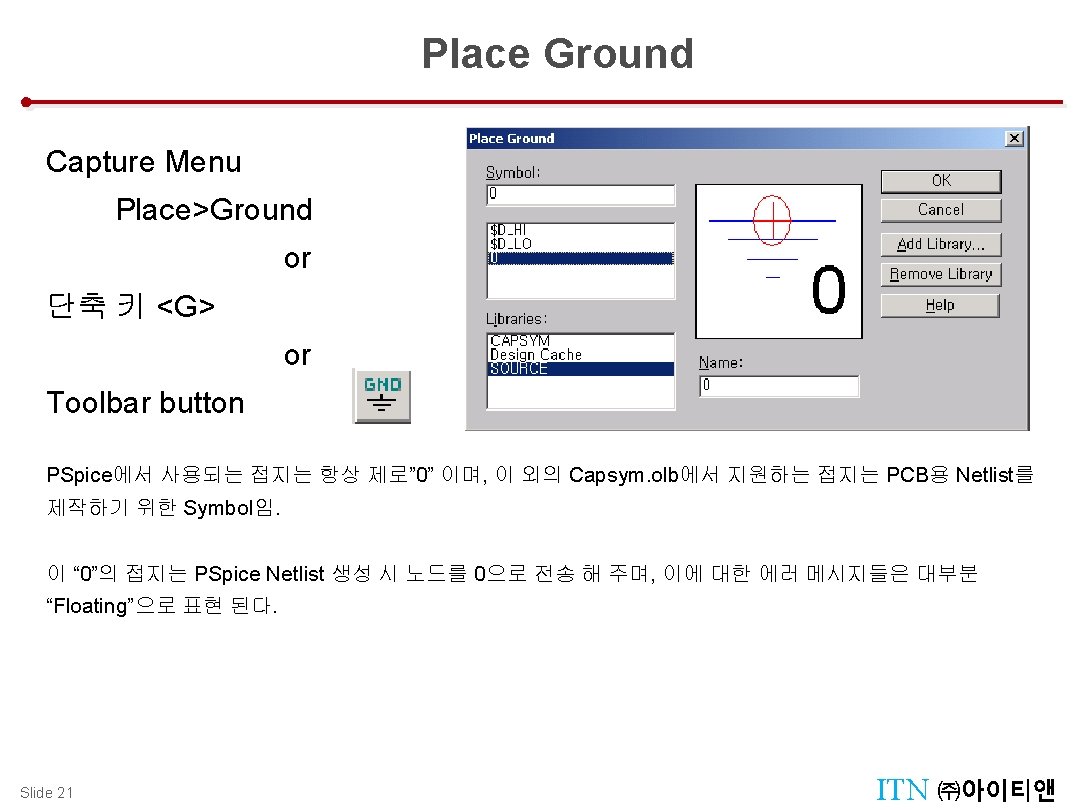

Tool Palette ü Tool Palette : Design icon Place Part : 부품 불러오기 Place Wire : 배선 기능 Place Net alias : 배선 및 버스의 임의의 이름 부여 Place Junction : 접 점 연결 및 접 점 취소 Place bus entry : 버스와 배선의 연결 점 배치 Place power : 전원 심벌 불러오기(only symbol) Place ground : 접지 심벌 불러오기(only “ 0” / source) Place hierarchical block : 계층 블록 제작 기능 전기적 속성을 지닌 툴 기능 Place hierarchical pin : 계층 구조 핀 배치 Place hierarchical port : 계층 구조 및 Global Port 배치 Place off-page connector : 페이지 연결 커넥터 배치 Place no connect : 접 점 해지 및 No connect 실행 Place line : 일반 선 그리기 Place polyline : 연속 선 그리기 Place rectangle : 직 사각형 그리기 전기적 속성이 없는 툴 기능 Place ellipse : 타원 그리기 Place arc : 원호 그리기 Place text : text 입력 Slide 9 ITN ㈜아이티앤

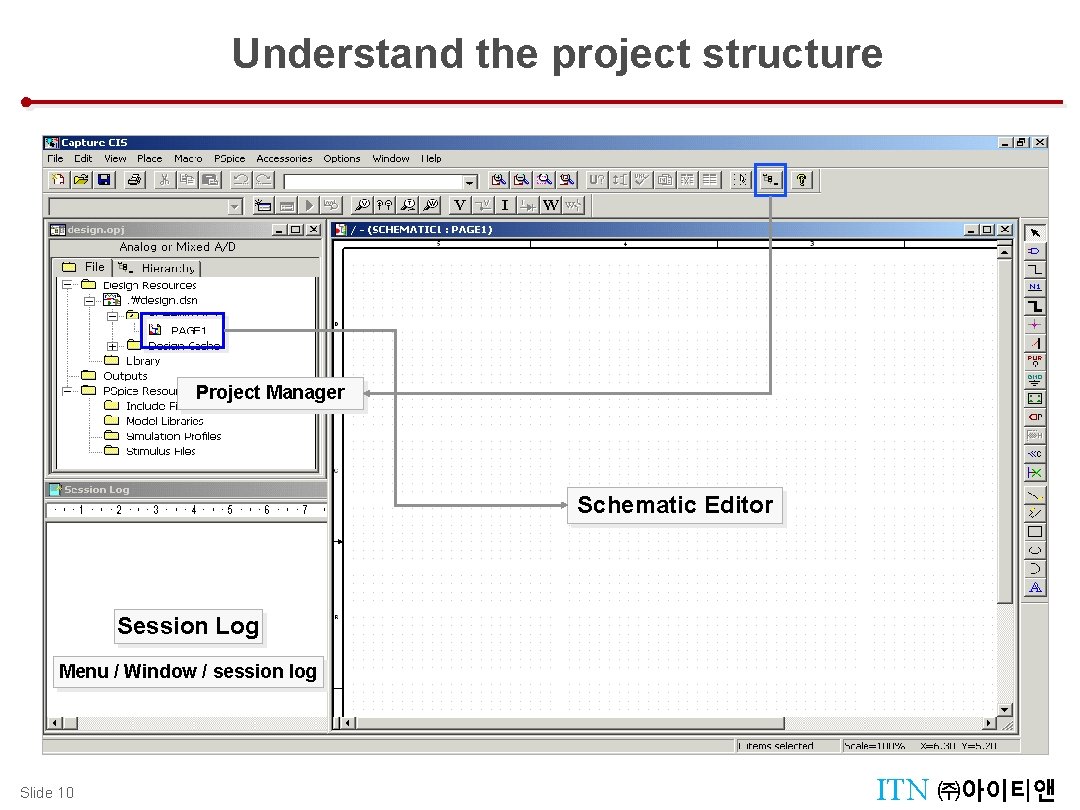

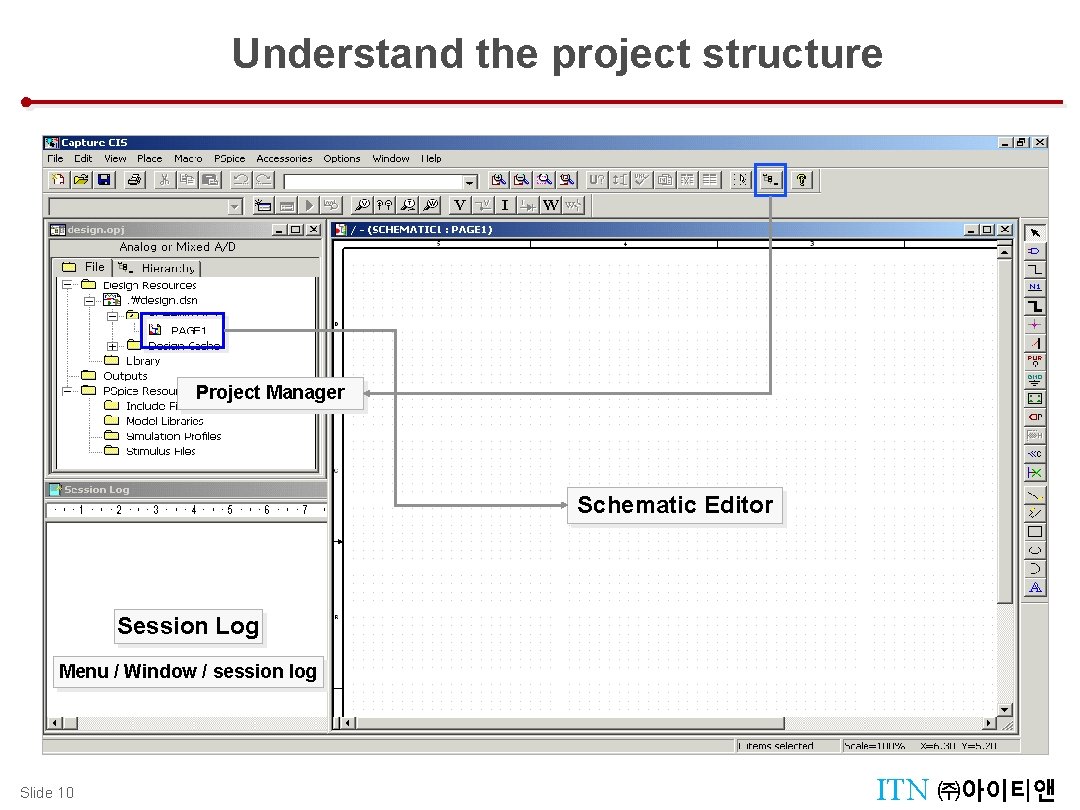

Understand the project structure Project Manager Schematic Editor Session Log Menu / Window / session log Slide 10 ITN ㈜아이티앤

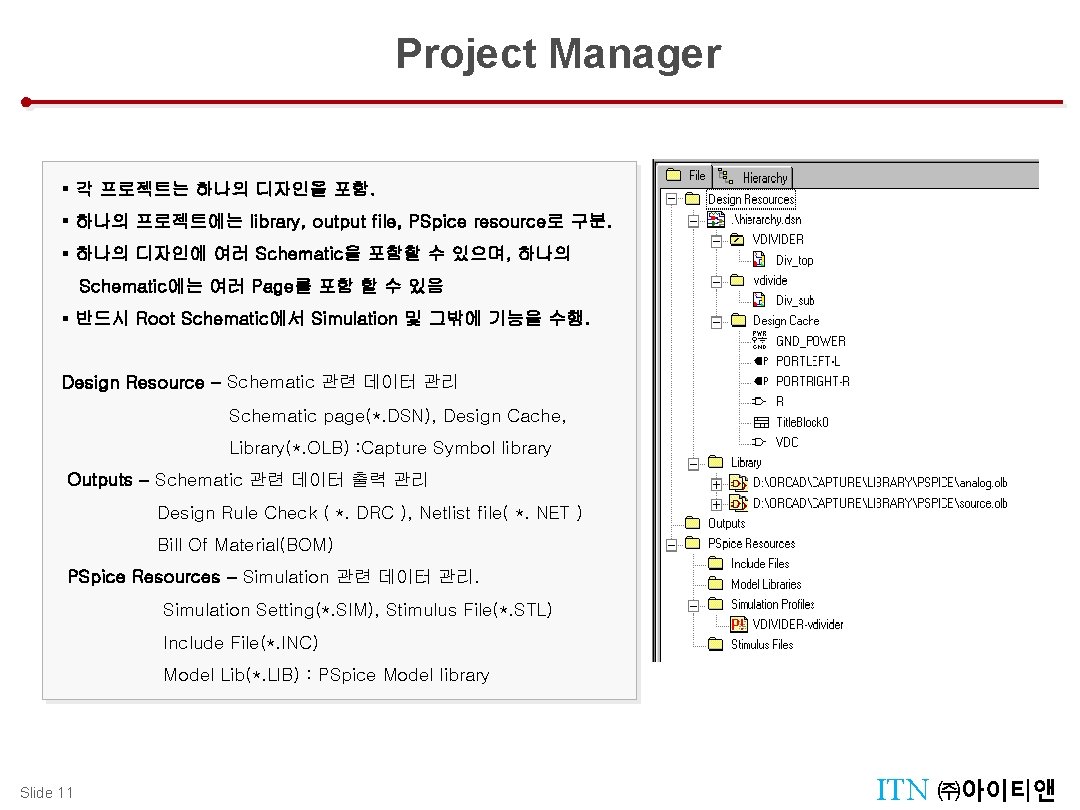

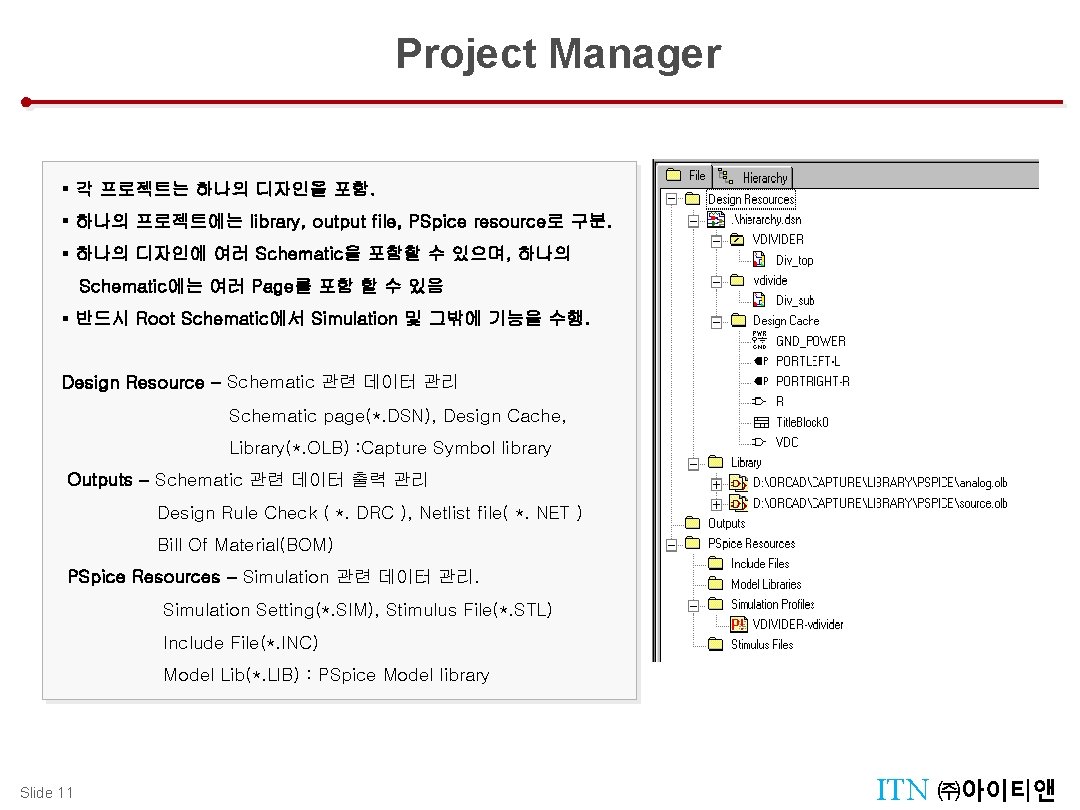

Project Manager § 각 프로젝트는 하나의 디자인을 포함. § 하나의 프로젝트에는 library, output file, PSpice resource로 구분. § 하나의 디자인에 여러 Schematic을 포함할 수 있으며, 하나의 Schematic에는 여러 Page를 포함 할 수 있음 § 반드시 Root Schematic에서 Simulation 및 그밖에 기능을 수행. Design Resource – Schematic 관련 데이터 관리 Schematic page(*. DSN), Design Cache, Library(*. OLB) : Capture Symbol library Outputs – Schematic 관련 데이터 출력 관리 Design Rule Check ( *. DRC ), Netlist file( *. NET ) Bill Of Material(BOM) PSpice Resources – Simulation 관련 데이터 관리. Simulation Setting(*. SIM), Stimulus File(*. STL) Include File(*. INC) Model Lib(*. LIB) : PSpice Model library Slide 11 ITN ㈜아이티앤

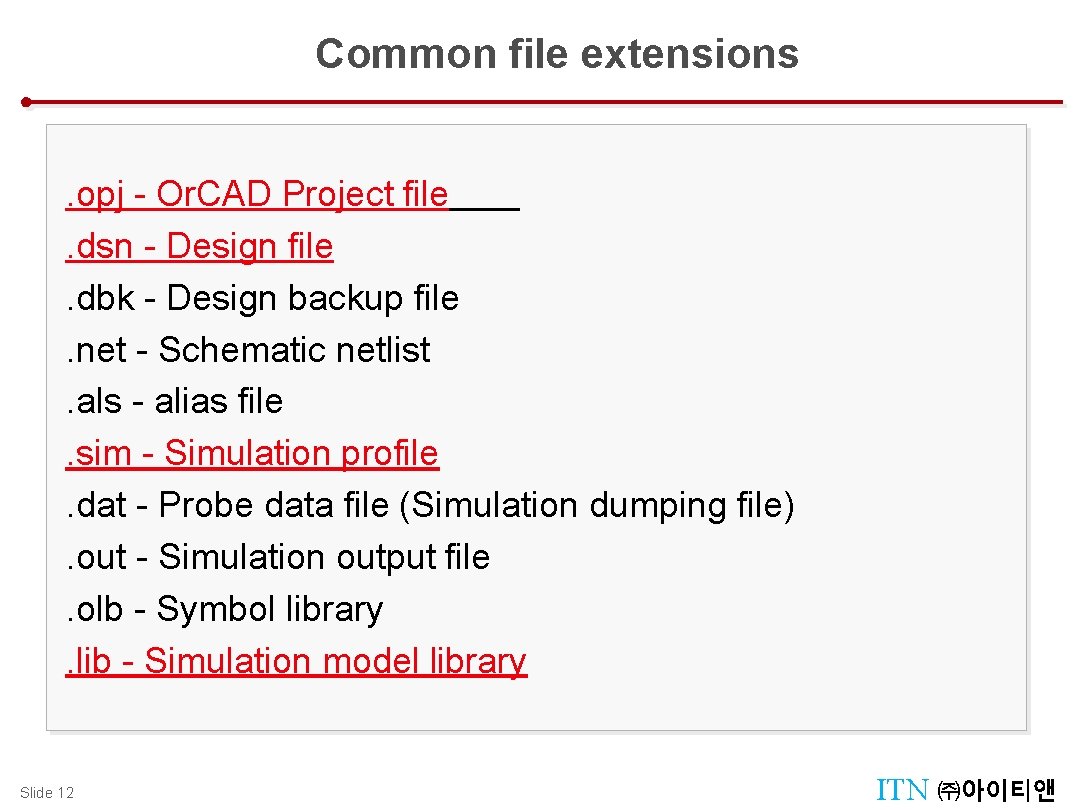

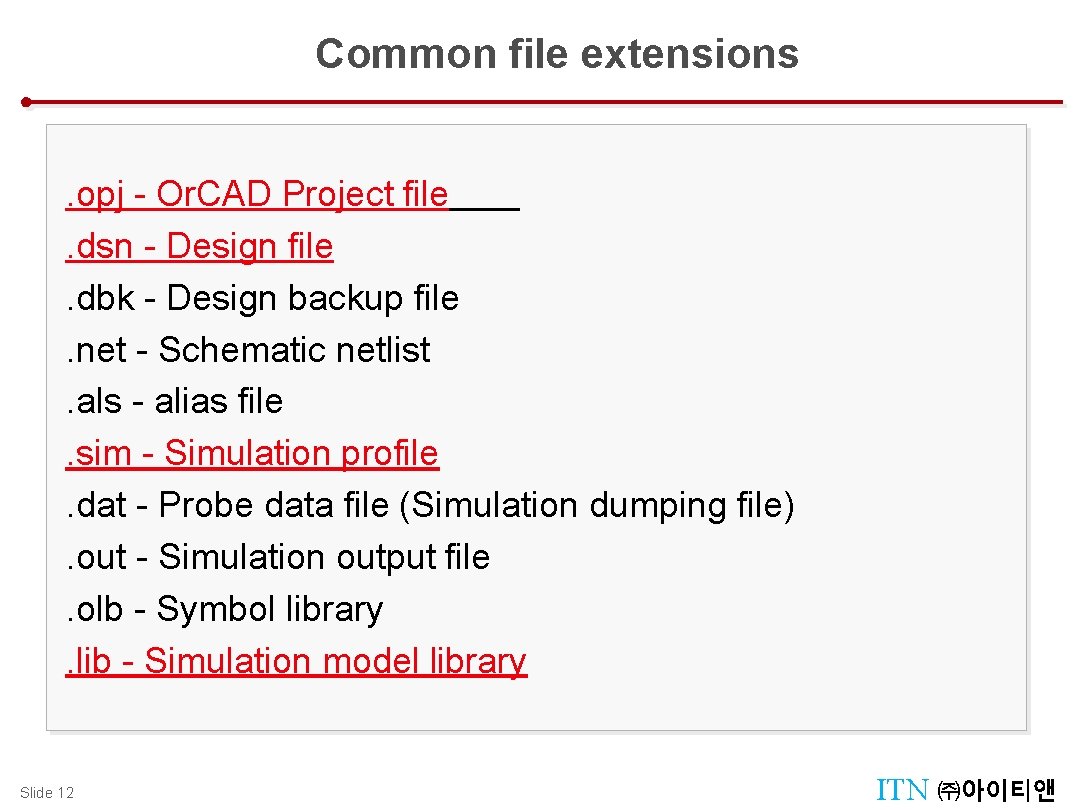

Common file extensions. opj - Or. CAD Project file . dsn - Design file. dbk - Design backup file. net - Schematic netlist. als - alias file. sim - Simulation profile. dat - Probe data file (Simulation dumping file). out - Simulation output file. olb - Symbol library. lib - Simulation model library Slide 12 ITN ㈜아이티앤

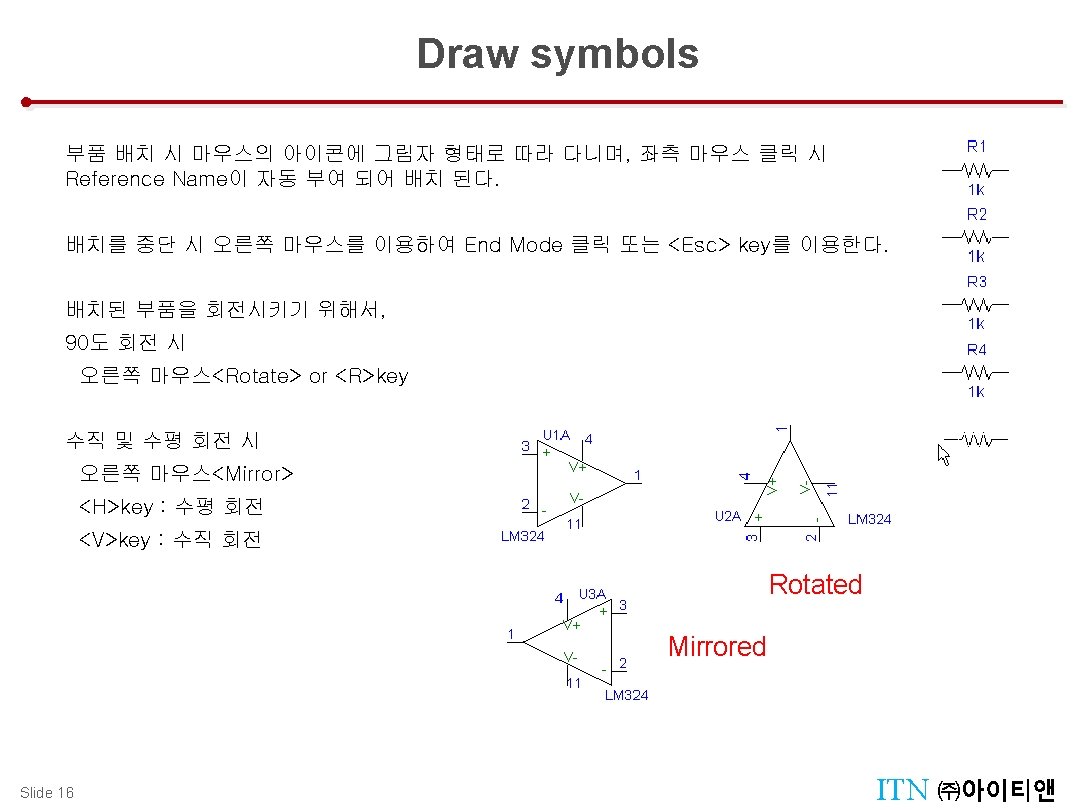

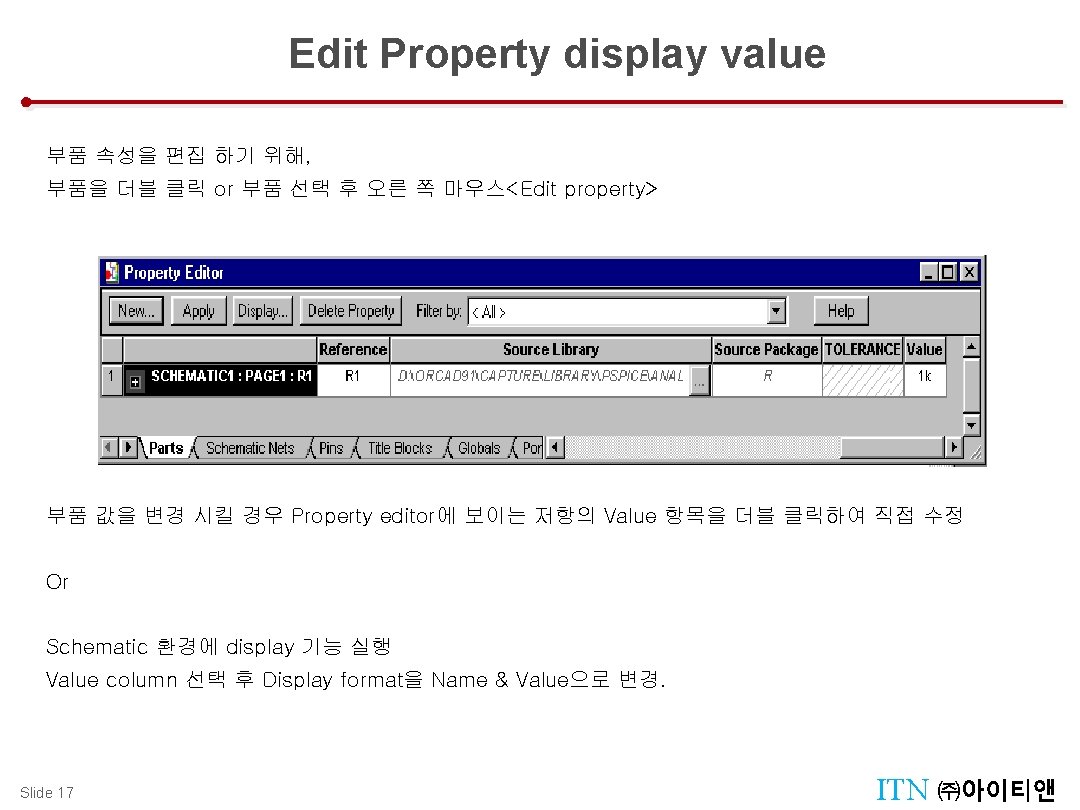

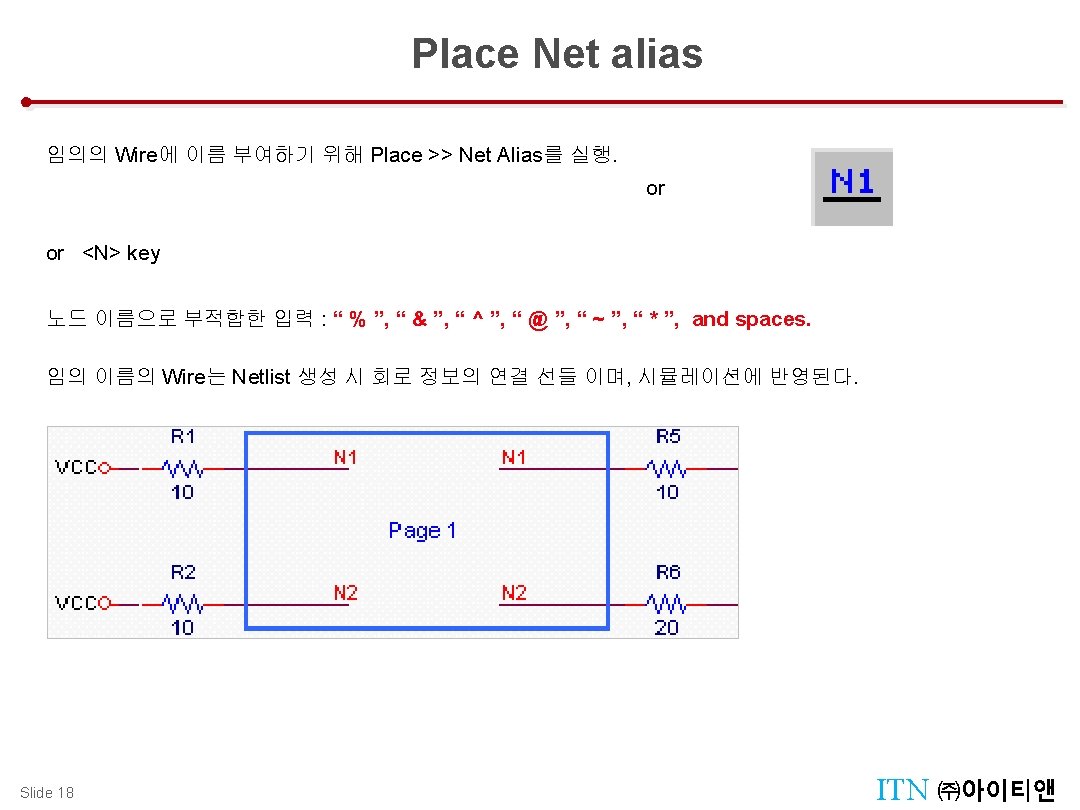

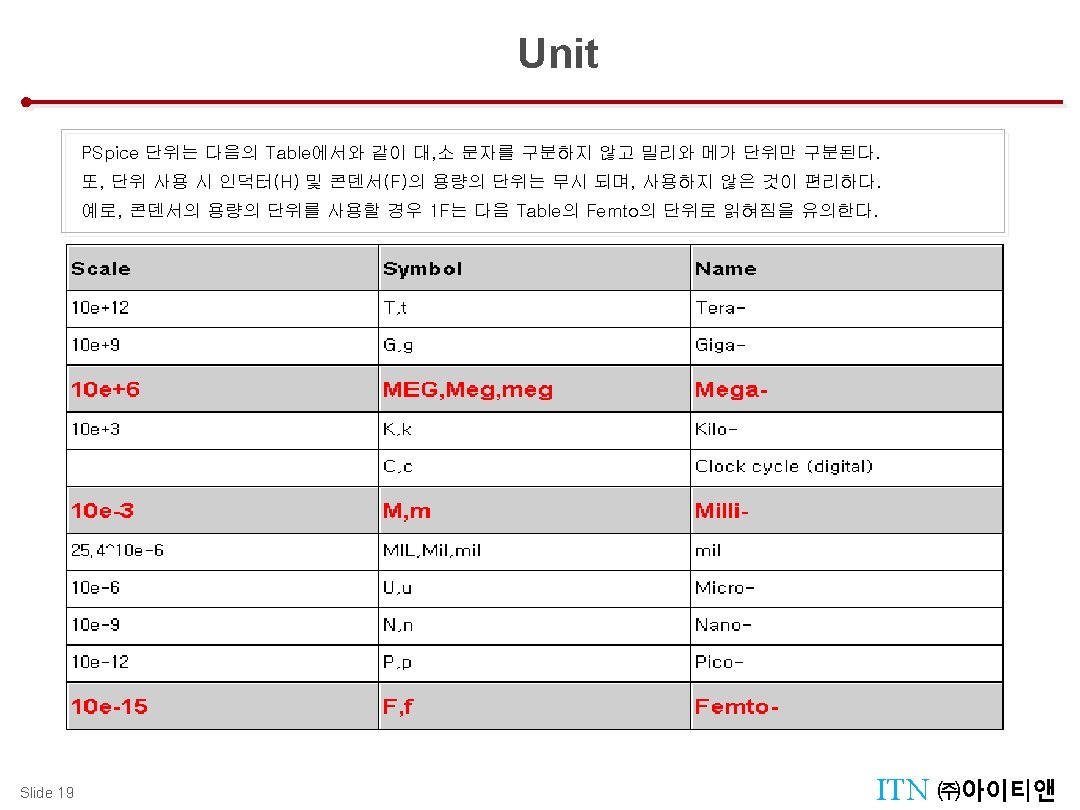

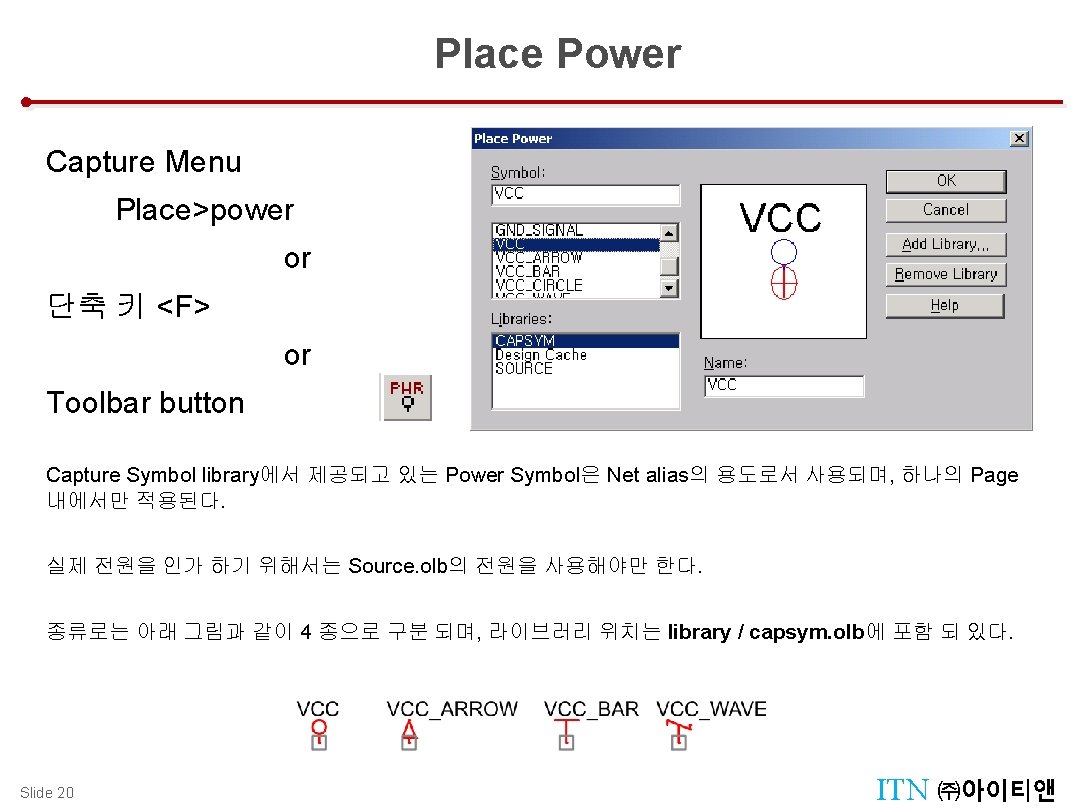

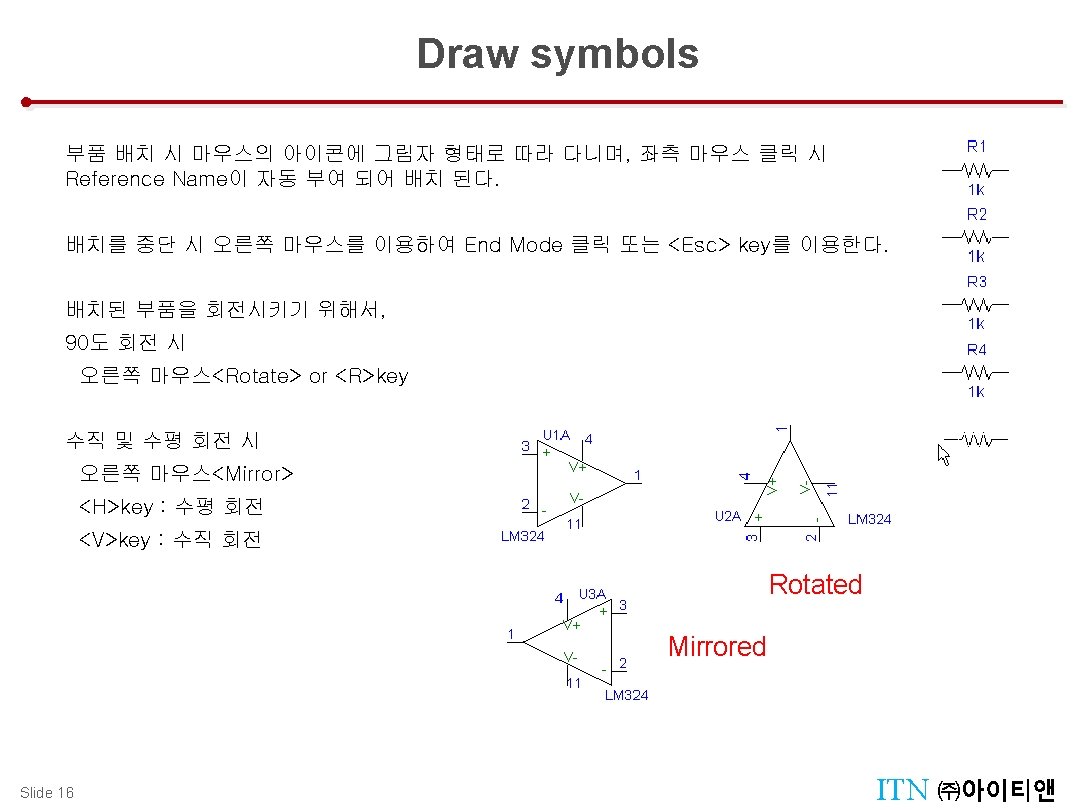

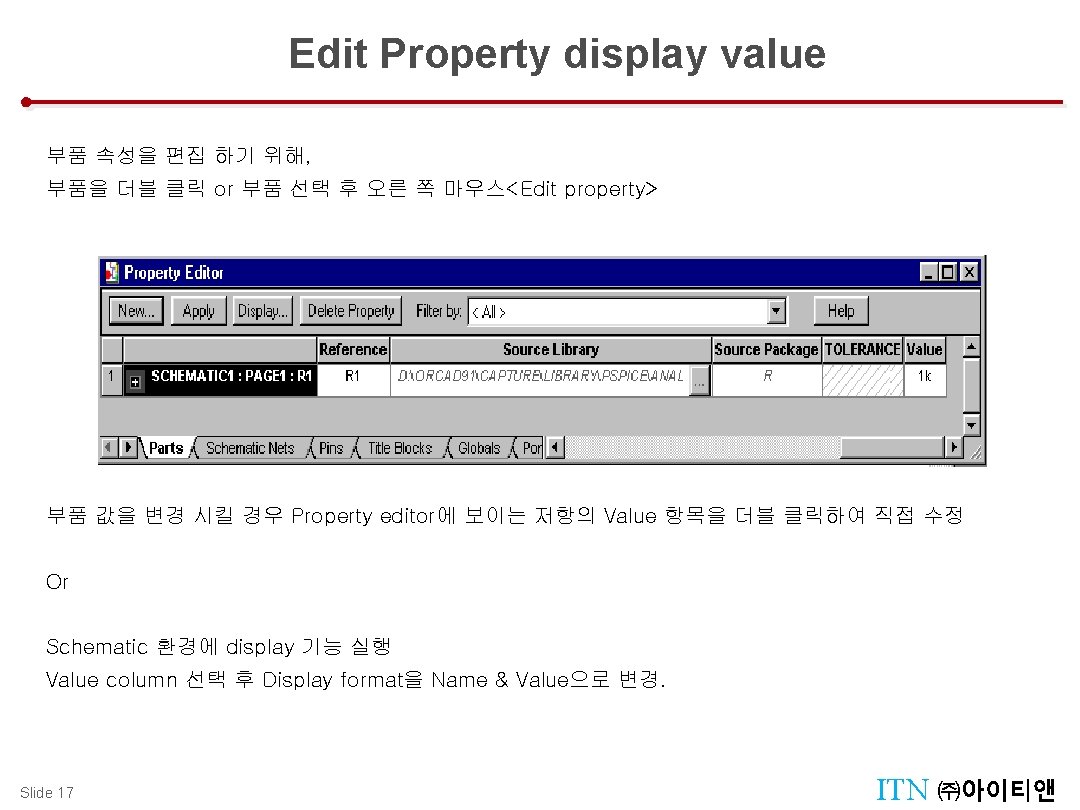

Entering a simulation Design Place Parts Part Browser Draw Symbols Edit Property Display Value Place Net alias Unit Place Power Place Ground Slide 13 ITN ㈜아이티앤

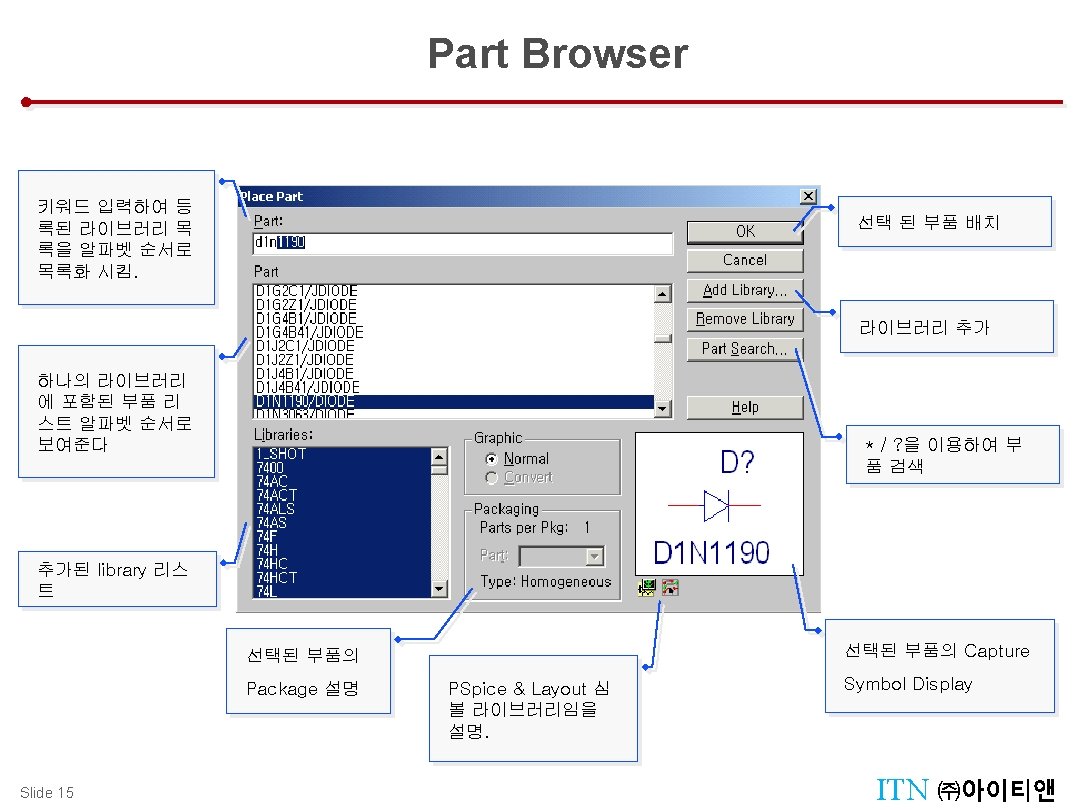

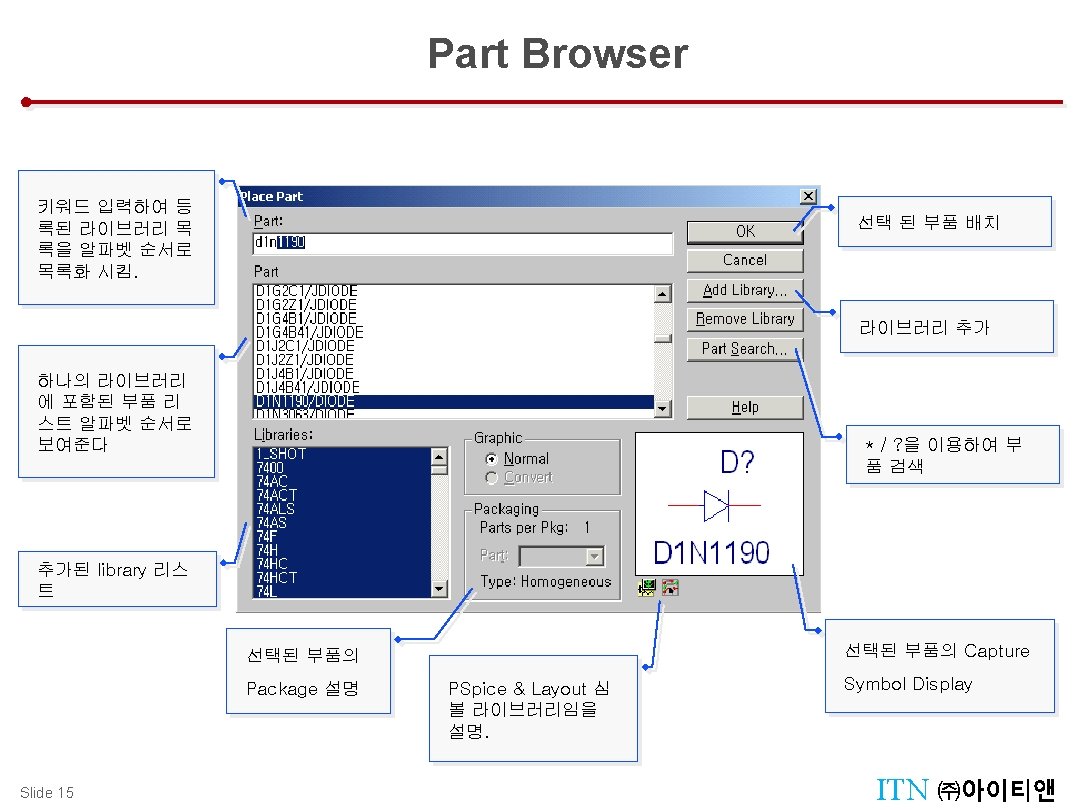

Place Part Capture Menu Place>Part menu 선택 or 단축 키 <P> or Toolbar button Slide 14 ITN ㈜아이티앤

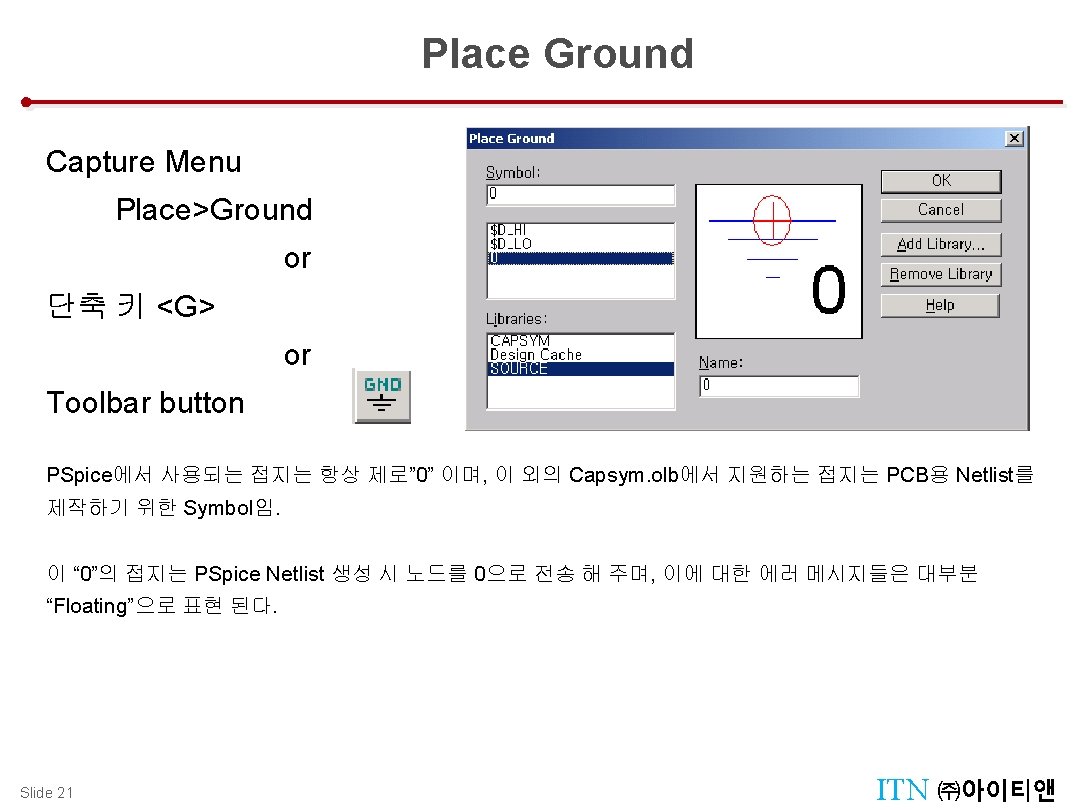

Library Passive device PSpice Template. Model defile. Model Device Type. Subckt define / Subcircuit. Subckt example / subcircuit Slide 22 ITN ㈜아이티앤

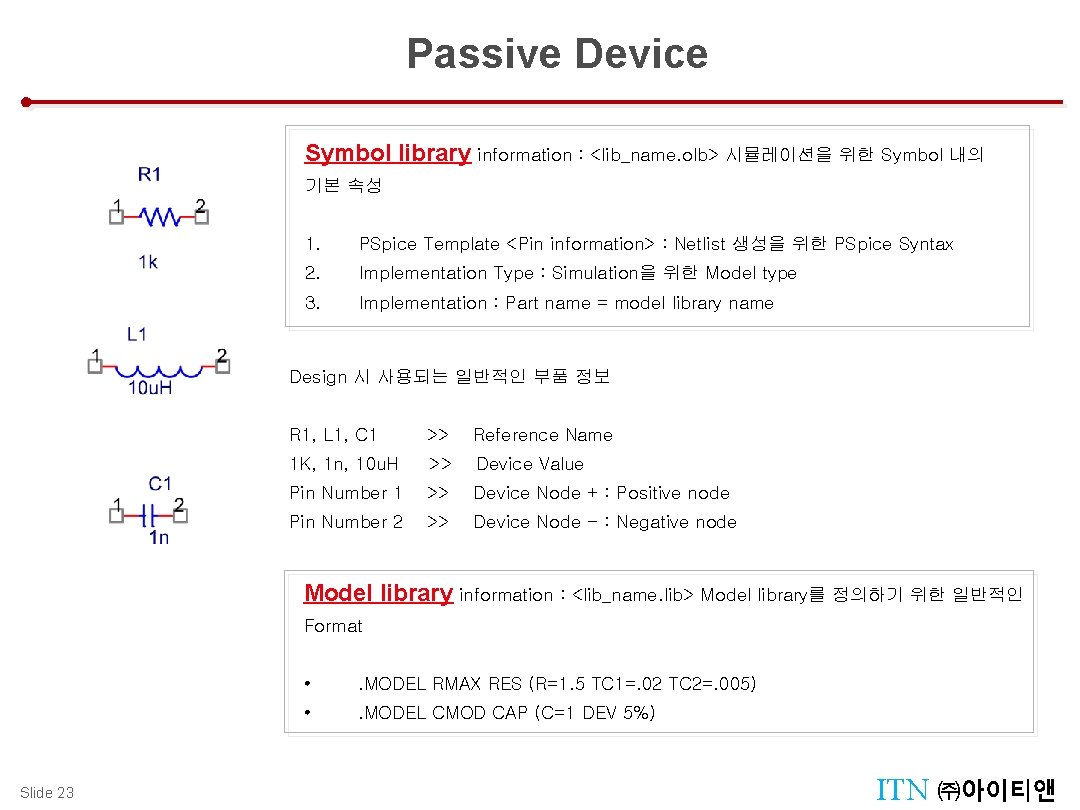

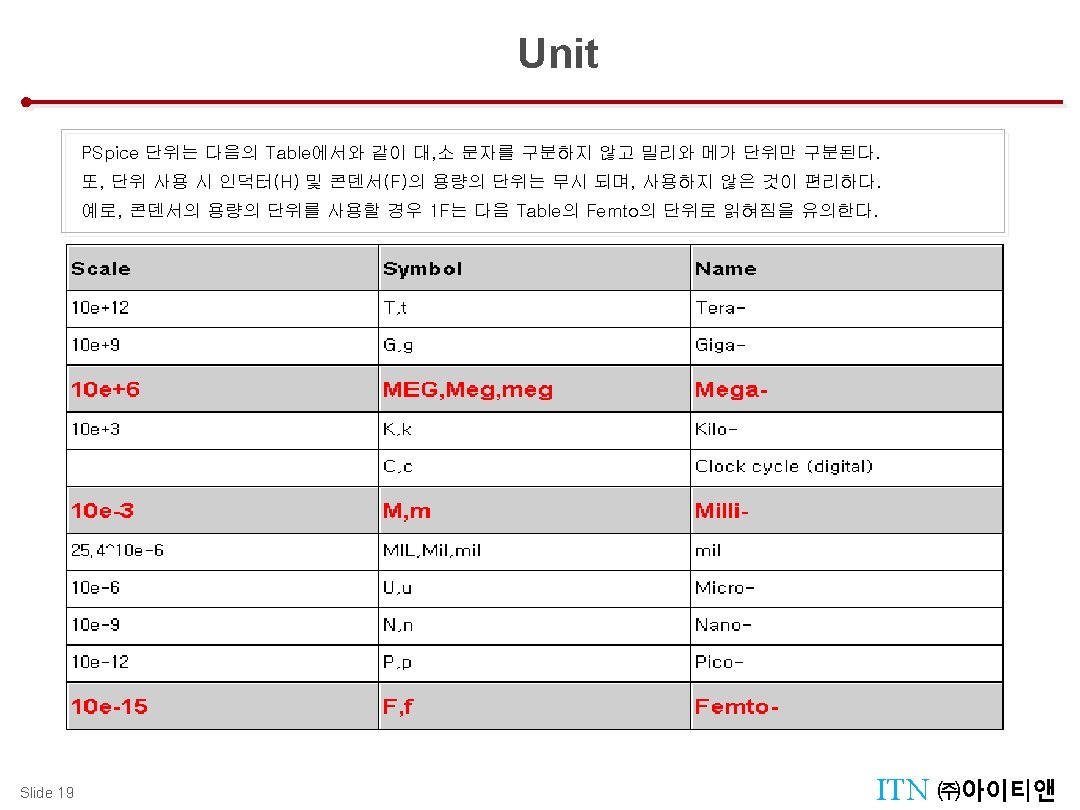

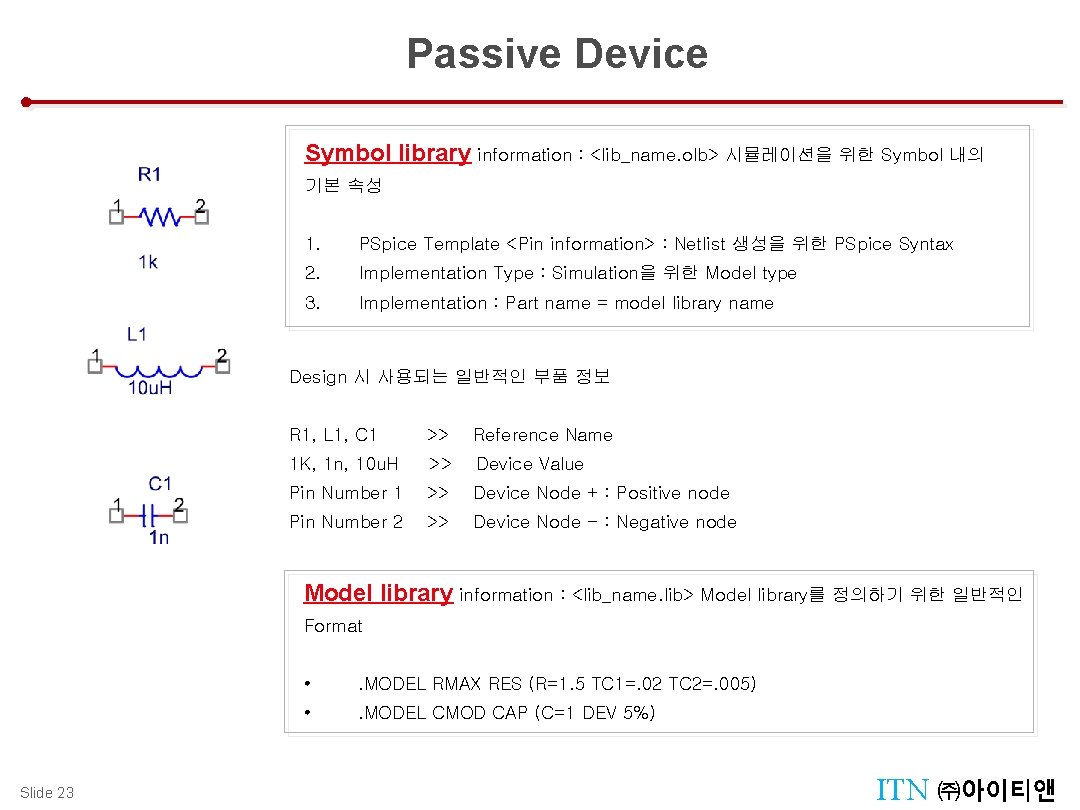

Design Tool Menu : Tool Palettes Passive Device Symbol library information : <lib_name. olb> 시뮬레이션을 위한 Symbol 내의 기본 속성 1. PSpice Template <Pin information> : Netlist 생성을 위한 PSpice Syntax 2. Implementation Type : Simulation을 위한 Model type 3. Implementation : Part name = model library name Design 시 사용되는 일반적인 부품 정보 R 1, L 1, C 1 >> Reference Name 1 K, 1 n, 10 u. H >> Device Value Pin Number 1 >> Device Node + : Positive node Pin Number 2 >> Device Node - : Negative node Model library information : <lib_name. lib> Model library를 정의하기 위한 일반적인 Format Slide 23 • . MODEL RMAX RES (R=1. 5 TC 1=. 02 TC 2=. 005) • . MODEL CMOD CAP (C=1 DEV 5%) ITN ㈜아이티앤

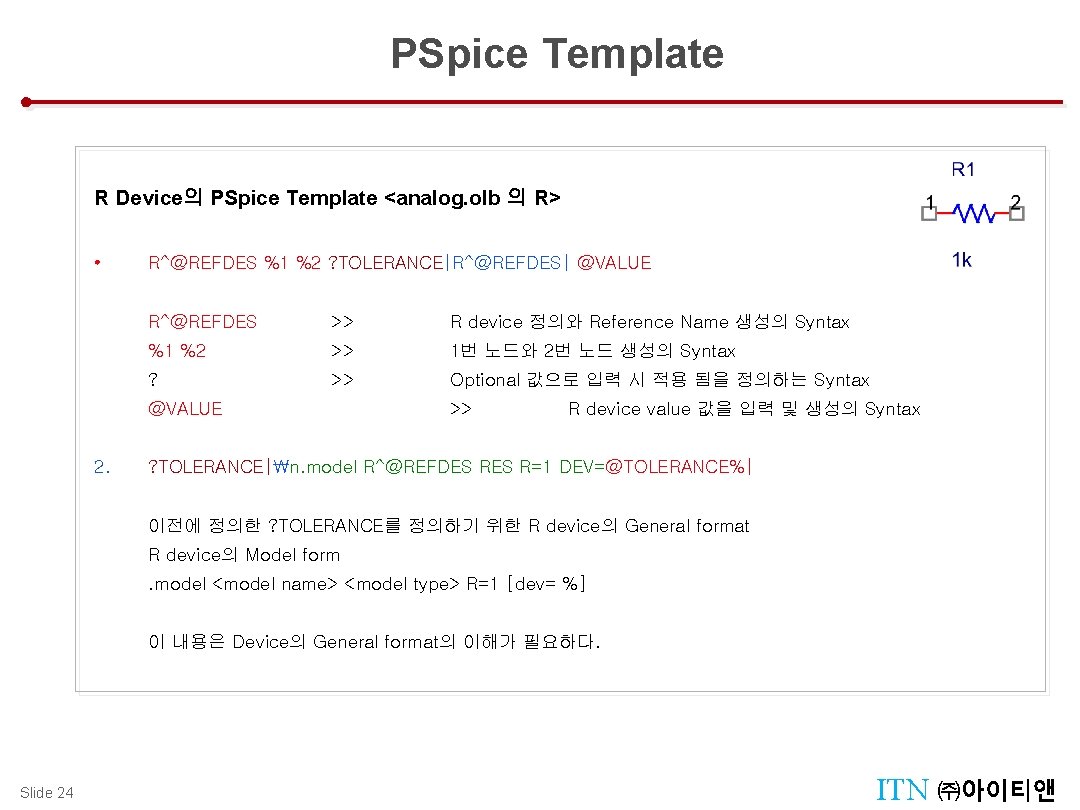

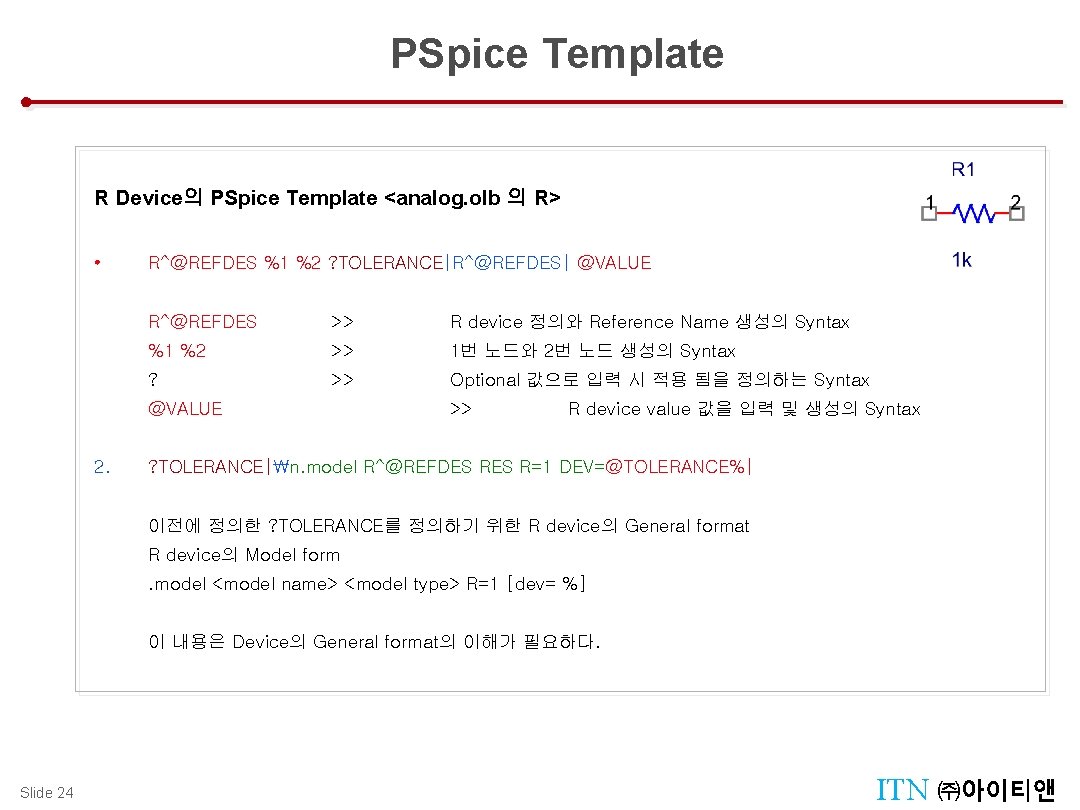

Design Tool Menu : Tool Palettes PSpice Template R Device의 PSpice Template <analog. olb 의 R> • R^@REFDES %1 %2 ? TOLERANCE|R^@REFDES| @VALUE R^@REFDES >> R device 정의와 Reference Name 생성의 Syntax %1 %2 >> 1번 노드와 2번 노드 생성의 Syntax ? >> Optional 값으로 입력 시 적용 됨을 정의하는 Syntax @VALUE 2. >> R device value 값을 입력 및 생성의 Syntax ? TOLERANCE|n. model R^@REFDES R=1 DEV=@TOLERANCE%| 이전에 정의한 ? TOLERANCE를 정의하기 위한 R device의 General format R device의 Model form. model <model name> <model type> R=1 [dev= %] 이 내용은 Device의 General format의 이해가 필요하다. Slide 24 ITN ㈜아이티앤

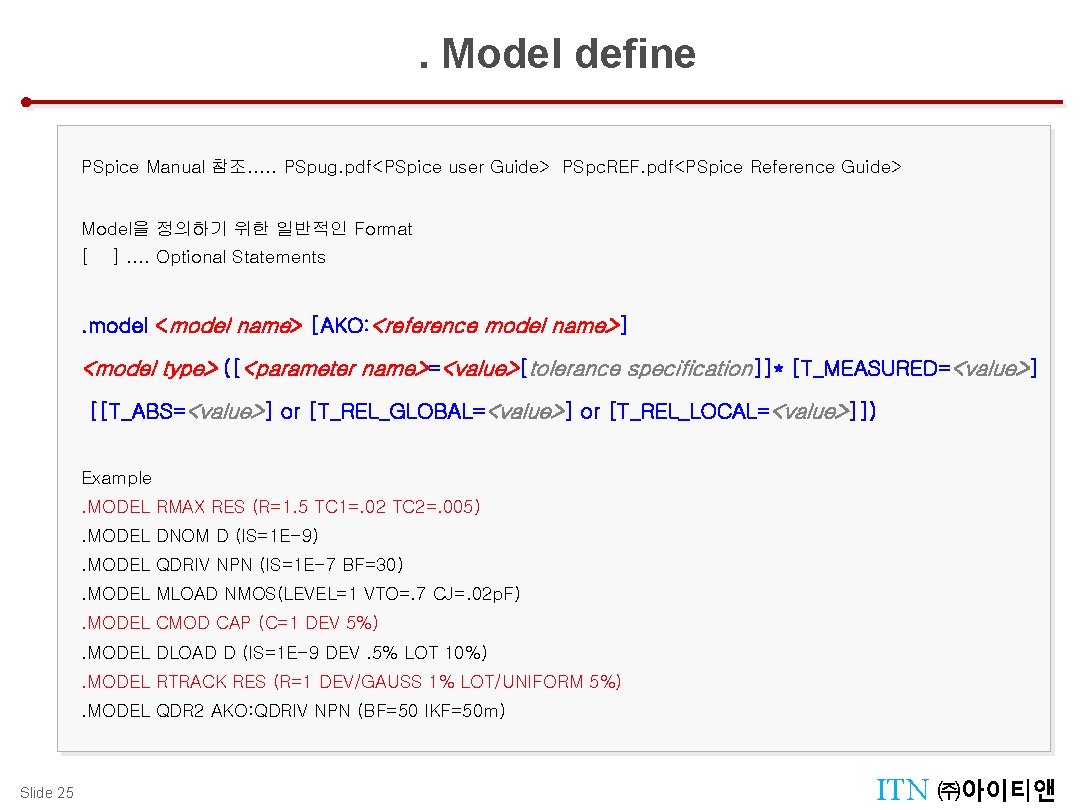

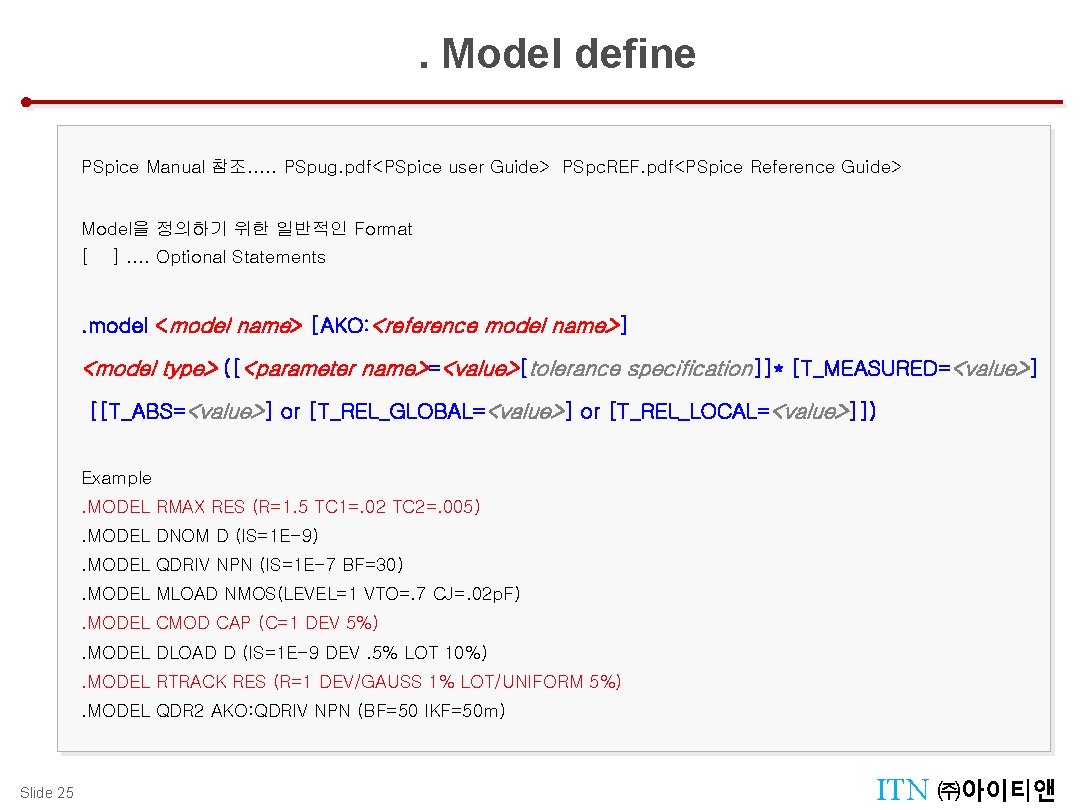

Design Tool Menu : Tool Palettes . Model define PSpice Manual 참조. . . PSpug. pdf<PSpice user Guide> PSpc. REF. pdf<PSpice Reference Guide> Model을 정의하기 위한 일반적인 Format [ ]. . Optional Statements . model <model name> [AKO: <reference model name>] <model type> ([<parameter name>=<value>[tolerance specification]]* [T_MEASURED=<value>] [[T_ABS=<value>] or [T_REL_GLOBAL=<value>] or [T_REL_LOCAL=<value>]]) Example. MODEL RMAX RES (R=1. 5 TC 1=. 02 TC 2=. 005). MODEL DNOM D (IS=1 E-9). MODEL QDRIV NPN (IS=1 E-7 BF=30). MODEL MLOAD NMOS(LEVEL=1 VTO=. 7 CJ=. 02 p. F). MODEL CMOD CAP (C=1 DEV 5%). MODEL DLOAD D (IS=1 E-9 DEV. 5% LOT 10%). MODEL RTRACK RES (R=1 DEV/GAUSS 1% LOT/UNIFORM 5%). MODEL QDR 2 AKO: QDRIV NPN (BF=50 IKF=50 m) Slide 25 ITN ㈜아이티앤

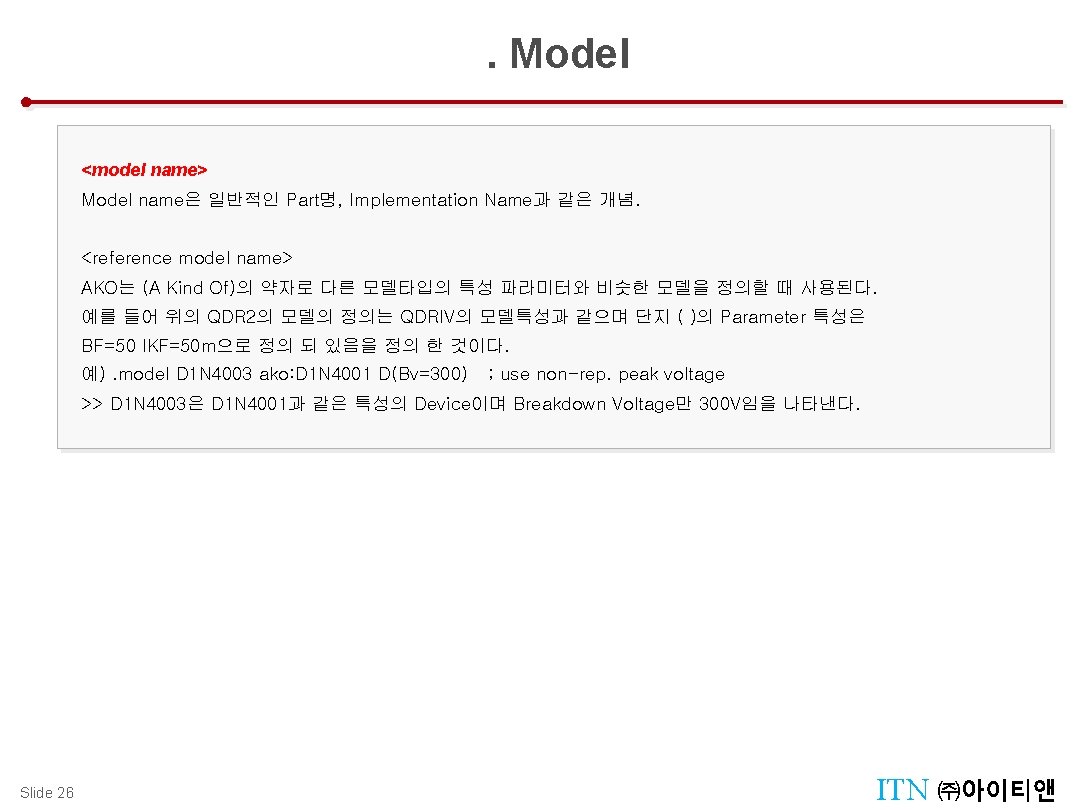

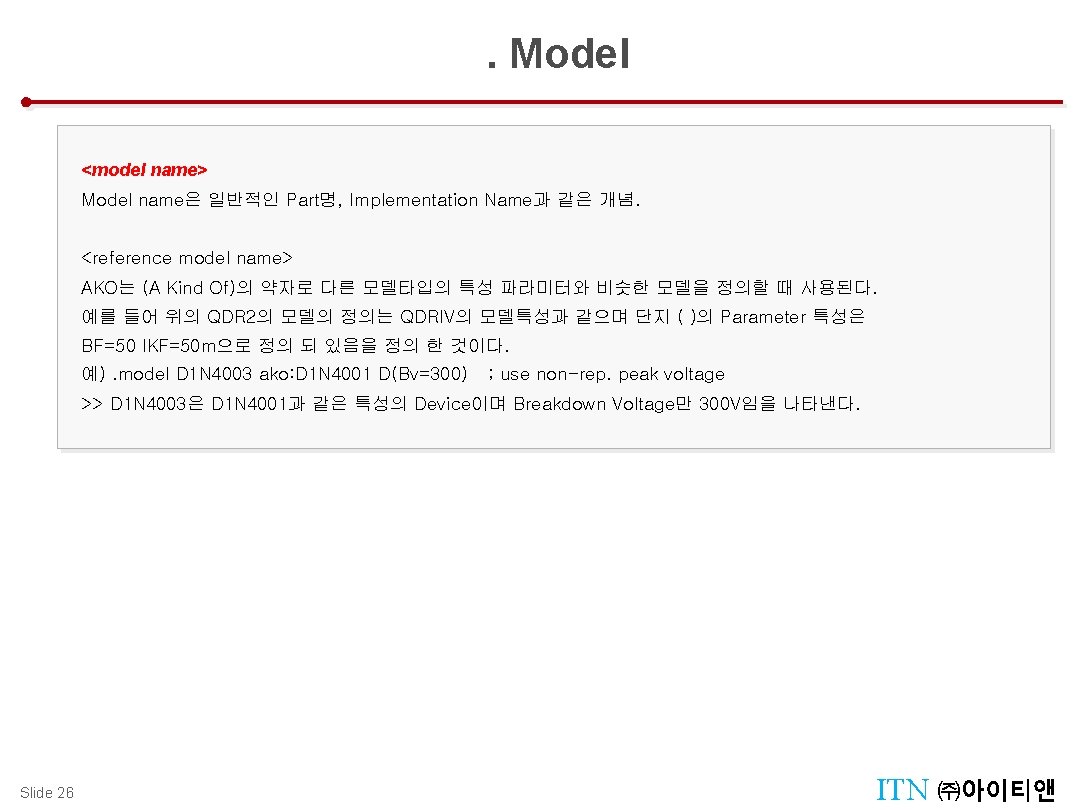

Design Tool Menu : Tool Palettes . Model <model name> Model name은 일반적인 Part명, Implementation Name과 같은 개념. <reference model name> AKO는 (A Kind Of)의 약자로 다른 모델타입의 특성 파라미터와 비슷한 모델을 정의할 때 사용된다. 예를 들어 위의 QDR 2의 모델의 정의는 QDRIV의 모델특성과 같으며 단지 ( )의 Parameter 특성은 BF=50 IKF=50 m으로 정의 되 있음을 정의 한 것이다. 예). model D 1 N 4003 ako: D 1 N 4001 D(Bv=300) ; use non-rep. peak voltage >> D 1 N 4003은 D 1 N 4001과 같은 특성의 Device이며 Breakdown Voltage만 300 V임을 나타낸다. Slide 26 ITN ㈜아이티앤

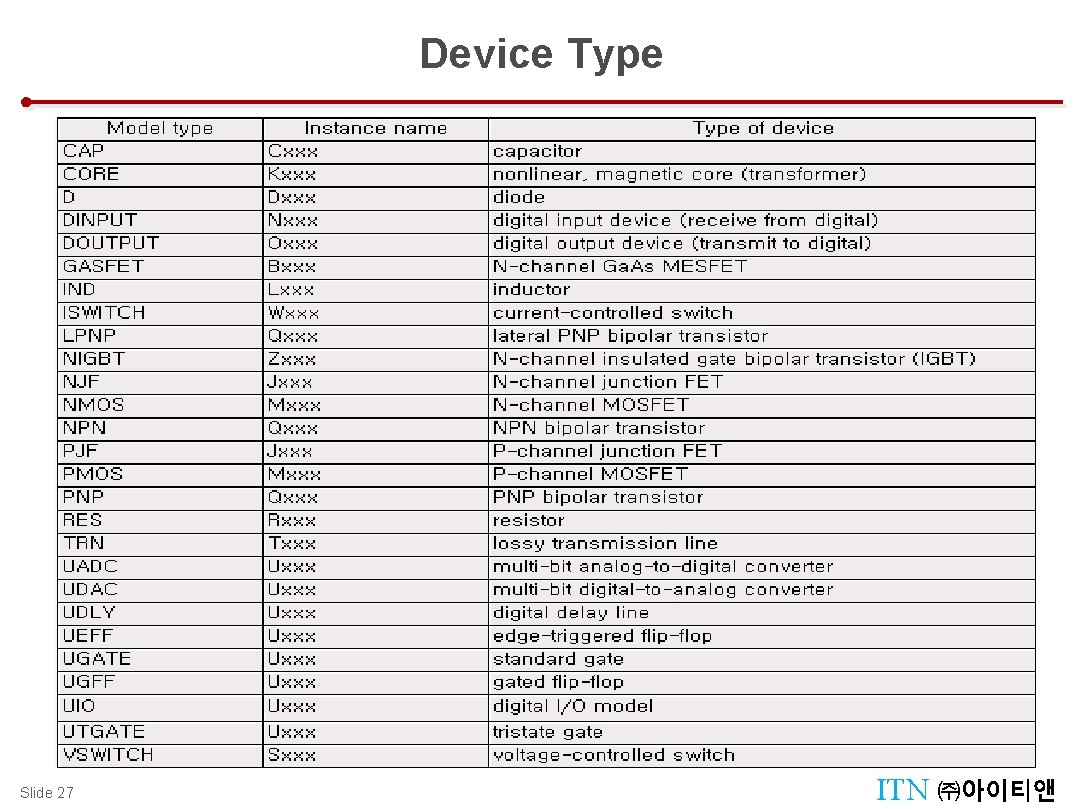

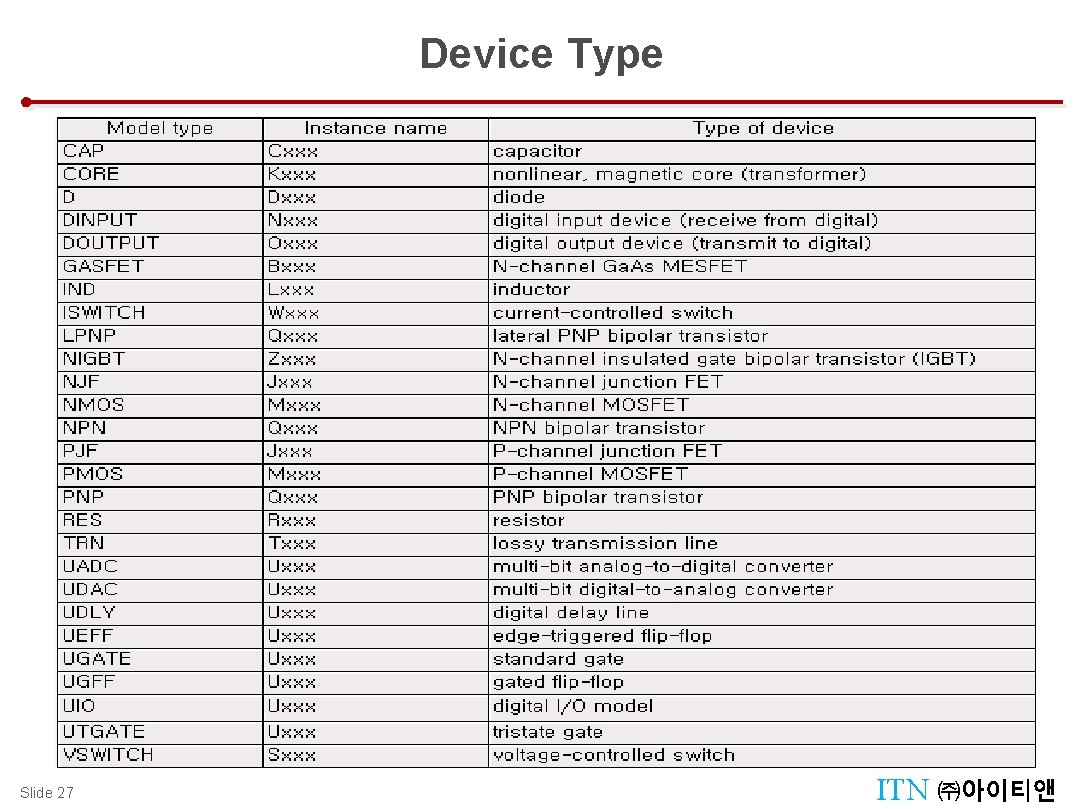

Design Tool Menu : Tool Palettes Slide 27 Device Type ITN ㈜아이티앤

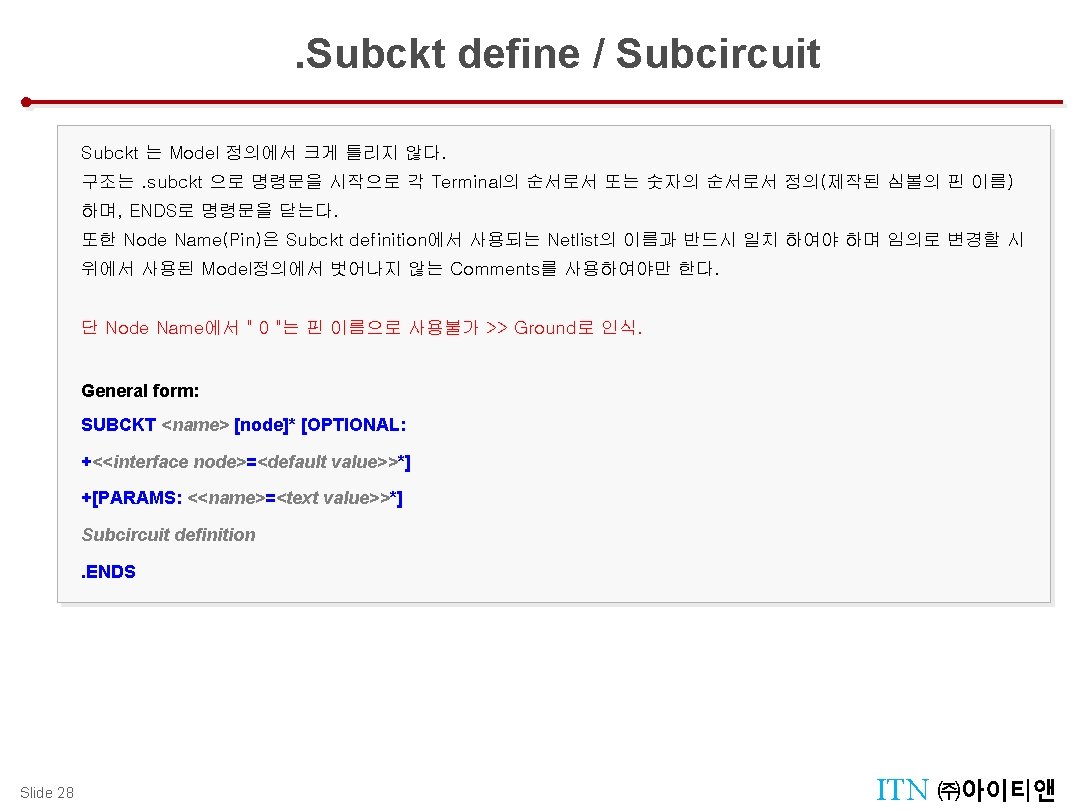

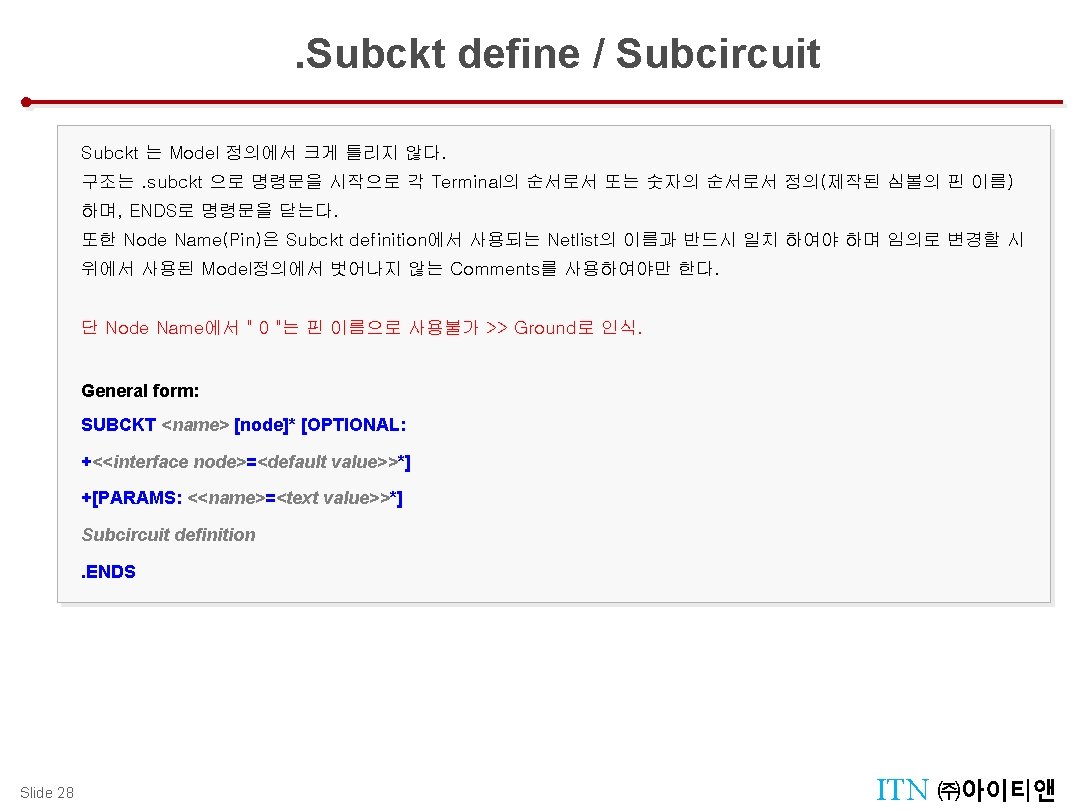

. Subckt define / Subcircuit Design Tool Menu : Tool Palettes Subckt 는 Model 정의에서 크게 틀리지 않다. 구조는. subckt 으로 명령문을 시작으로 각 Terminal의 순서로서 또는 숫자의 순서로서 정의(제작된 심볼의 핀 이름) 하며, ENDS로 명령문을 닫는다. 또한 Node Name(Pin)은 Subckt definition에서 사용되는 Netlist의 이름과 반드시 일치 하여야 하며 임의로 변경할 시 위에서 사용된 Model정의에서 벗어나지 않는 Comments를 사용하여야만 한다. 단 Node Name에서 " 0 "는 핀 이름으로 사용불가 >> Ground로 인식. General form: SUBCKT <name> [node]* [OPTIONAL: +<<interface node>=<default value>>*] +[PARAMS: <<name>=<text value>>*] Subcircuit definition. ENDS Slide 28 ITN ㈜아이티앤

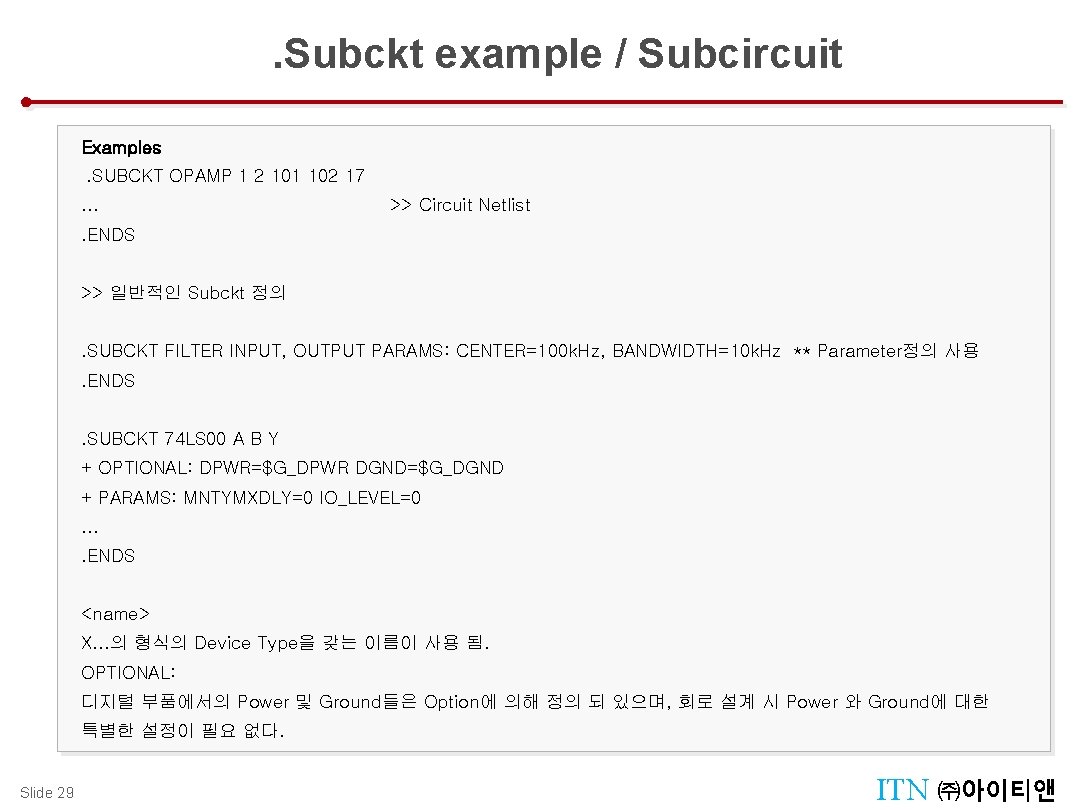

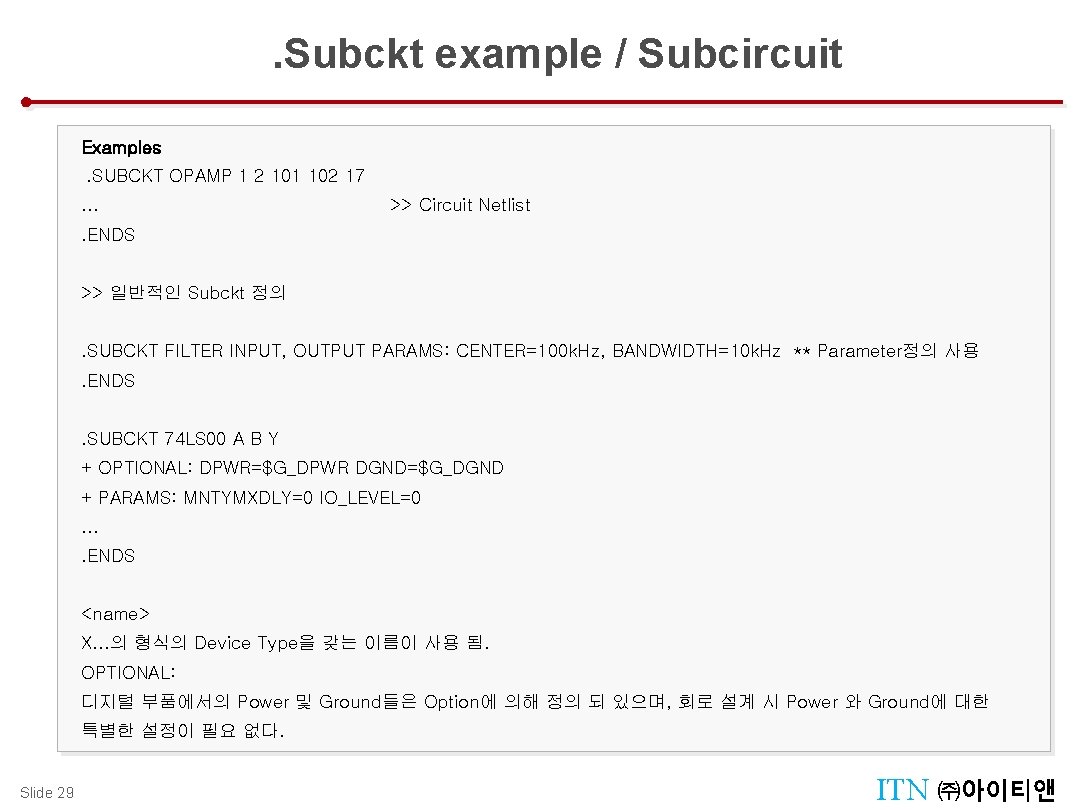

. Subckt example / Subcircuit Design Tool Menu : Tool Palettes Examples . SUBCKT OPAMP 1 2 101 102 17. . . >> Circuit Netlist. ENDS >> 일반적인 Subckt 정의 . SUBCKT FILTER INPUT, OUTPUT PARAMS: CENTER=100 k. Hz, BANDWIDTH=10 k. Hz ** Parameter정의 사용. ENDS . SUBCKT 74 LS 00 A B Y + OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND + PARAMS: MNTYMXDLY=0 IO_LEVEL=0. . ENDS <name> X. . . 의 형식의 Device Type을 갖는 이름이 사용 됨. OPTIONAL: 디지털 부품에서의 Power 및 Ground들은 Option에 의해 정의 되 있으며, 회로 설계 시 Power 와 Ground에 대한 특별한 설정이 필요 없다. Slide 29 ITN ㈜아이티앤

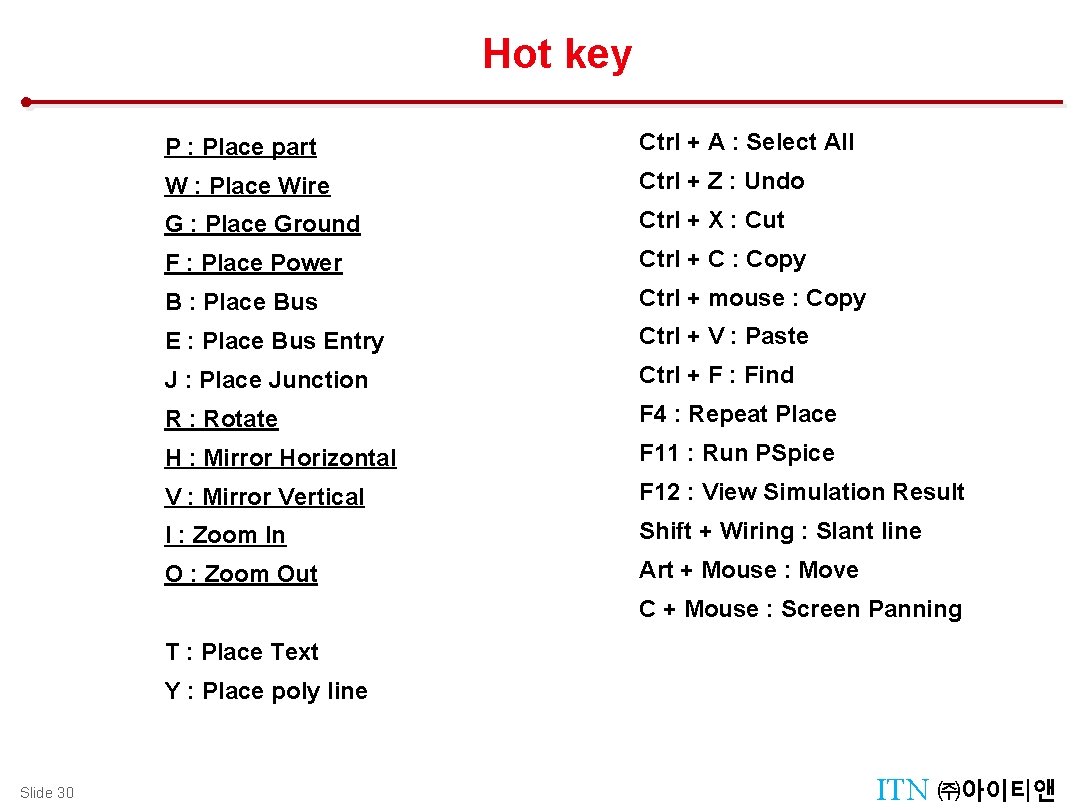

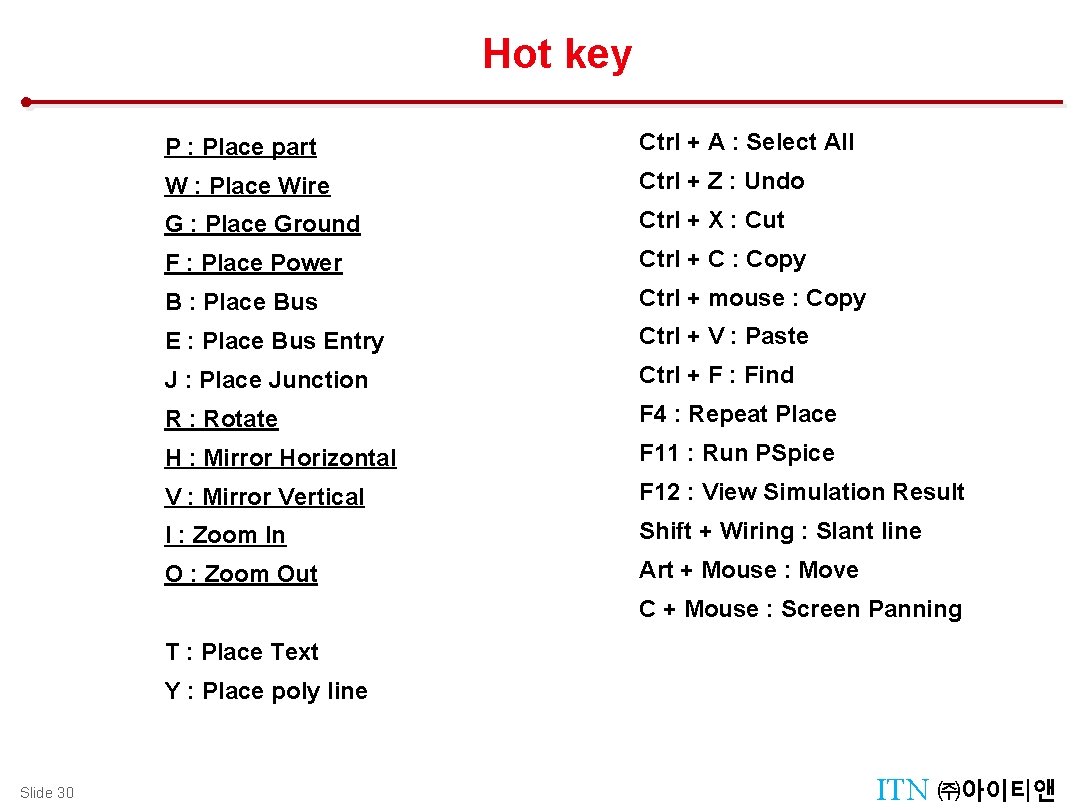

Design Management : Manager Tool Hot key P : Place part Ctrl + A : Select All W : Place Wire Ctrl + Z : Undo G : Place Ground Ctrl + X : Cut F : Place Power Ctrl + C : Copy B : Place Bus Ctrl + mouse : Copy E : Place Bus Entry Ctrl + V : Paste J : Place Junction Ctrl + F : Find R : Rotate F 4 : Repeat Place H : Mirror Horizontal F 11 : Run PSpice V : Mirror Vertical F 12 : View Simulation Result I : Zoom In Shift + Wiring : Slant line O : Zoom Out Art + Mouse : Move C + Mouse : Screen Panning T : Place Text Y : Place poly line Slide 30 ITN ㈜아이티앤

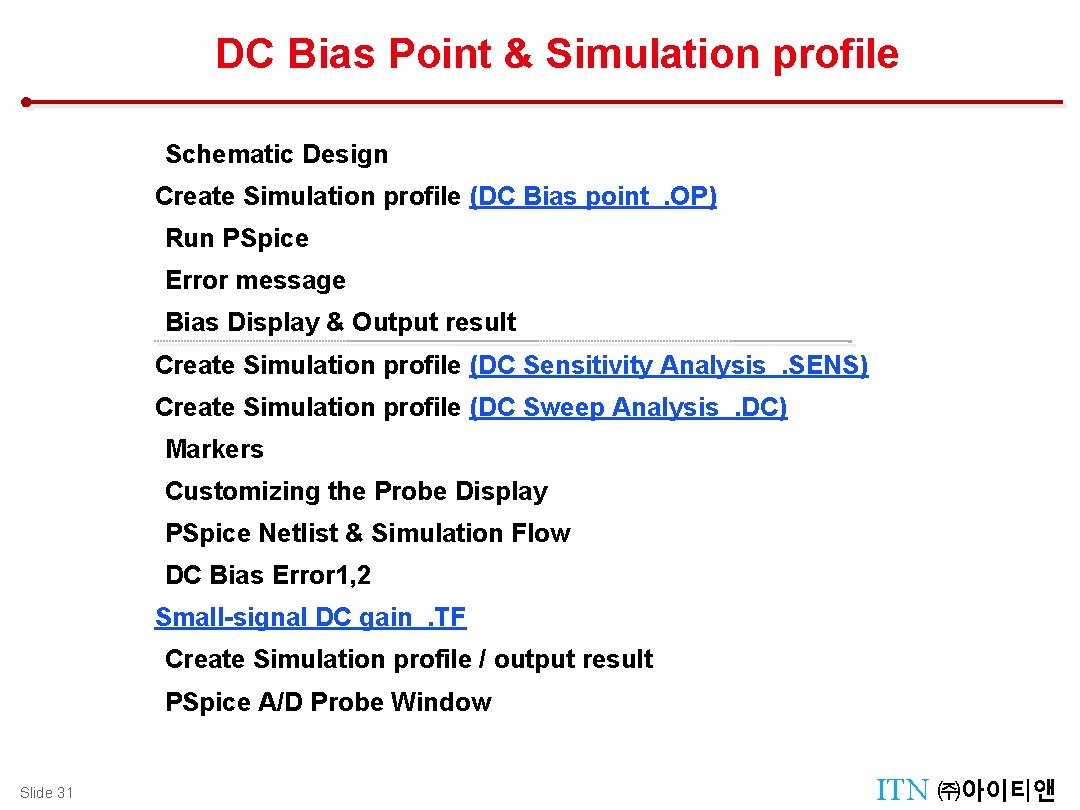

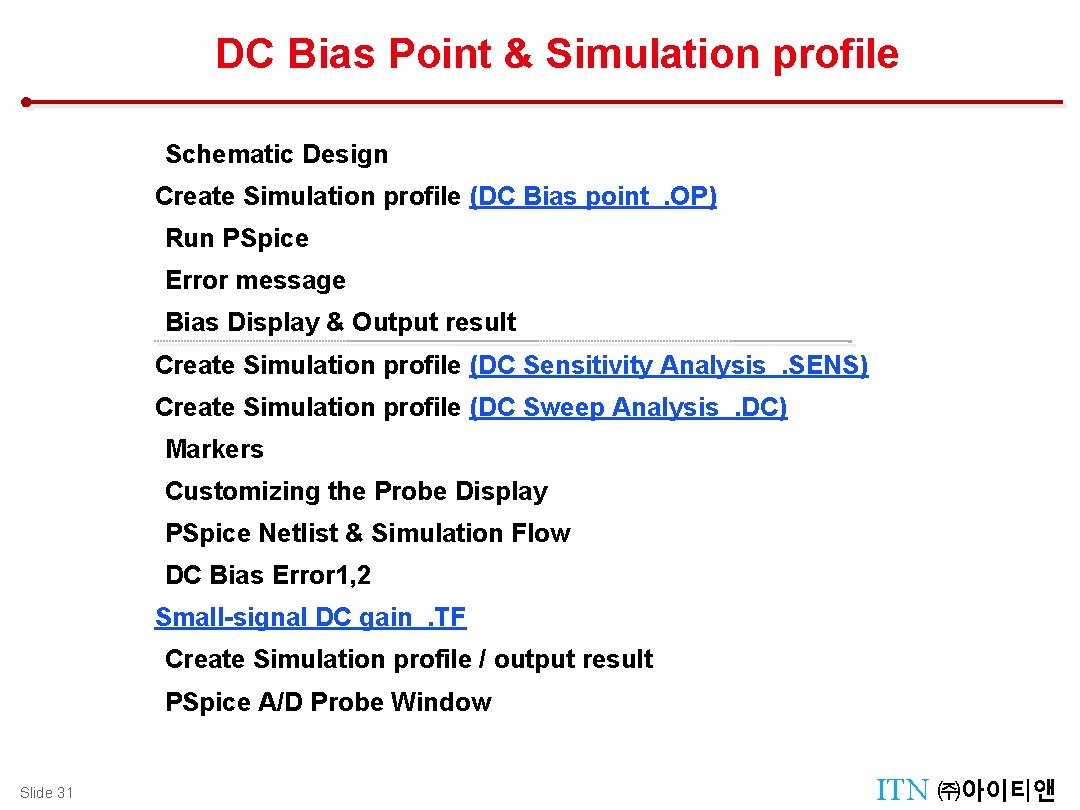

DC Bias Point & Simulation profile Design Tool Menu : Tool Palettes Schematic Design Create Simulation profile (DC Bias point. OP) Run PSpice Error message Bias Display & Output result Create Simulation profile (DC Sensitivity Analysis. SENS) Create Simulation profile (DC Sweep Analysis. DC) Markers Customizing the Probe Display PSpice Netlist & Simulation Flow DC Bias Error 1, 2 Small-signal DC gain. TF Create Simulation profile / output result PSpice A/D Probe Window Slide 31 ITN ㈜아이티앤

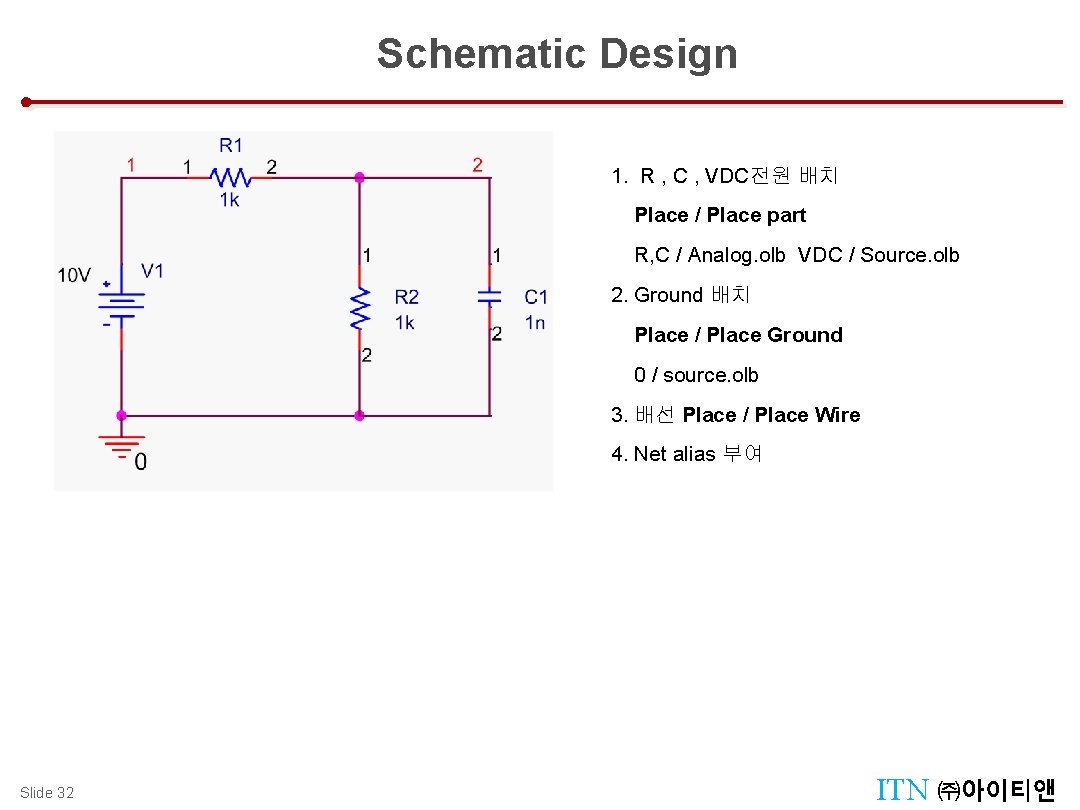

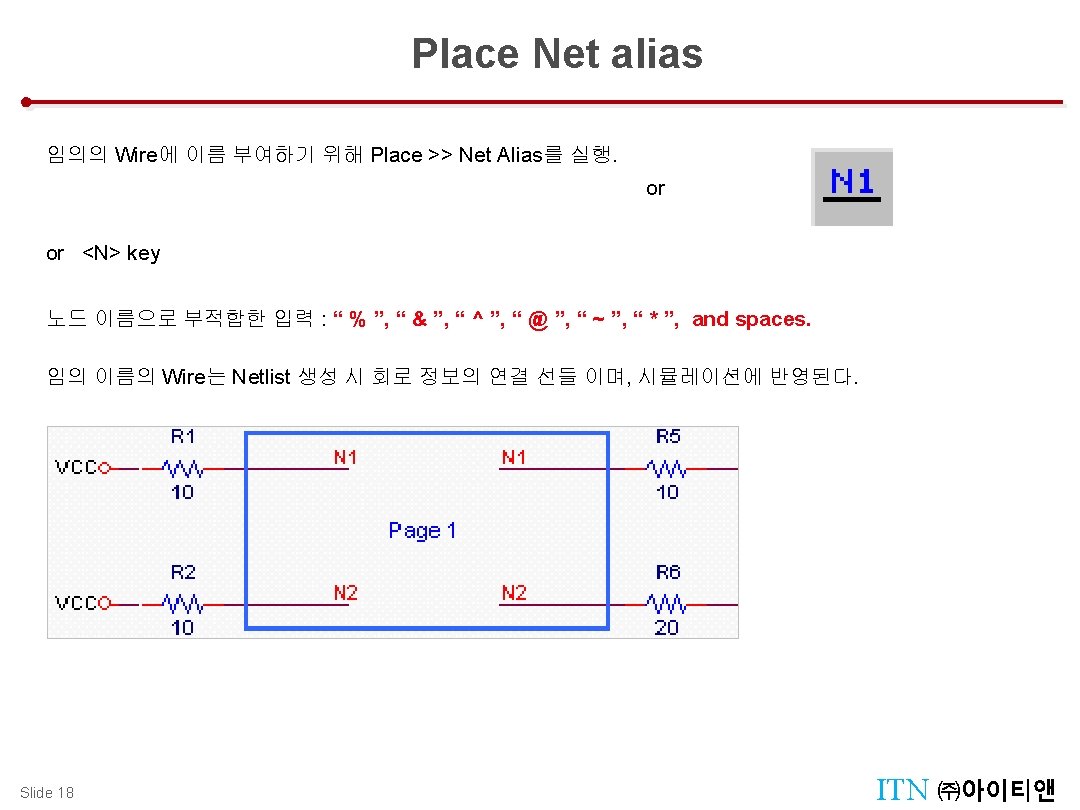

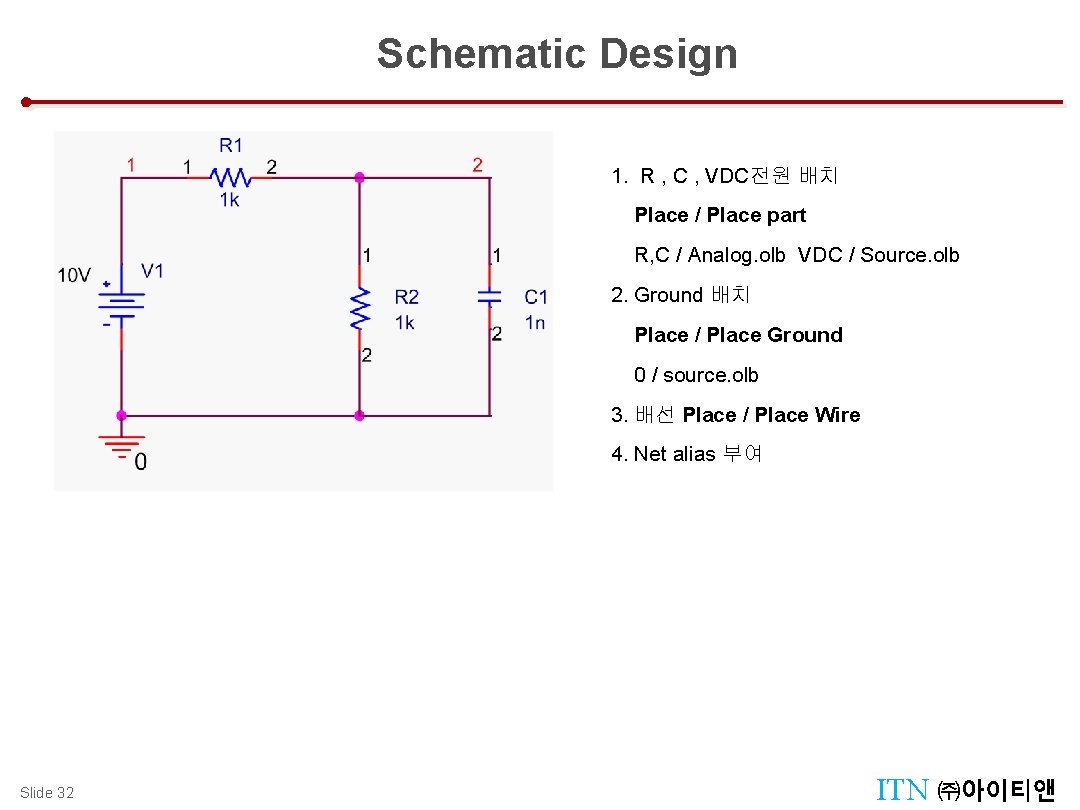

Design Tool Menu : Tool Palettes Schematic Design 1. R , C , VDC전원 배치 Place / Place part R, C / Analog. olb VDC / Source. olb 2. Ground 배치 Place / Place Ground 0 / source. olb 3. 배선 Place / Place Wire 4. Net alias 부여 Slide 32 ITN ㈜아이티앤

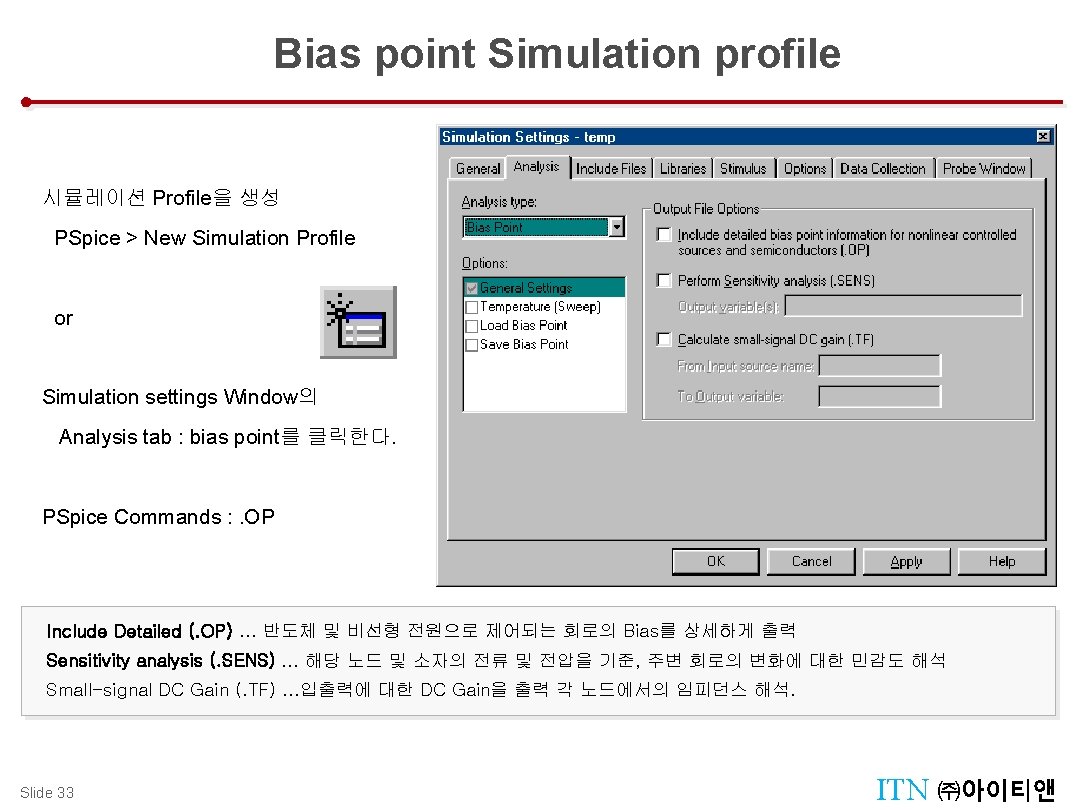

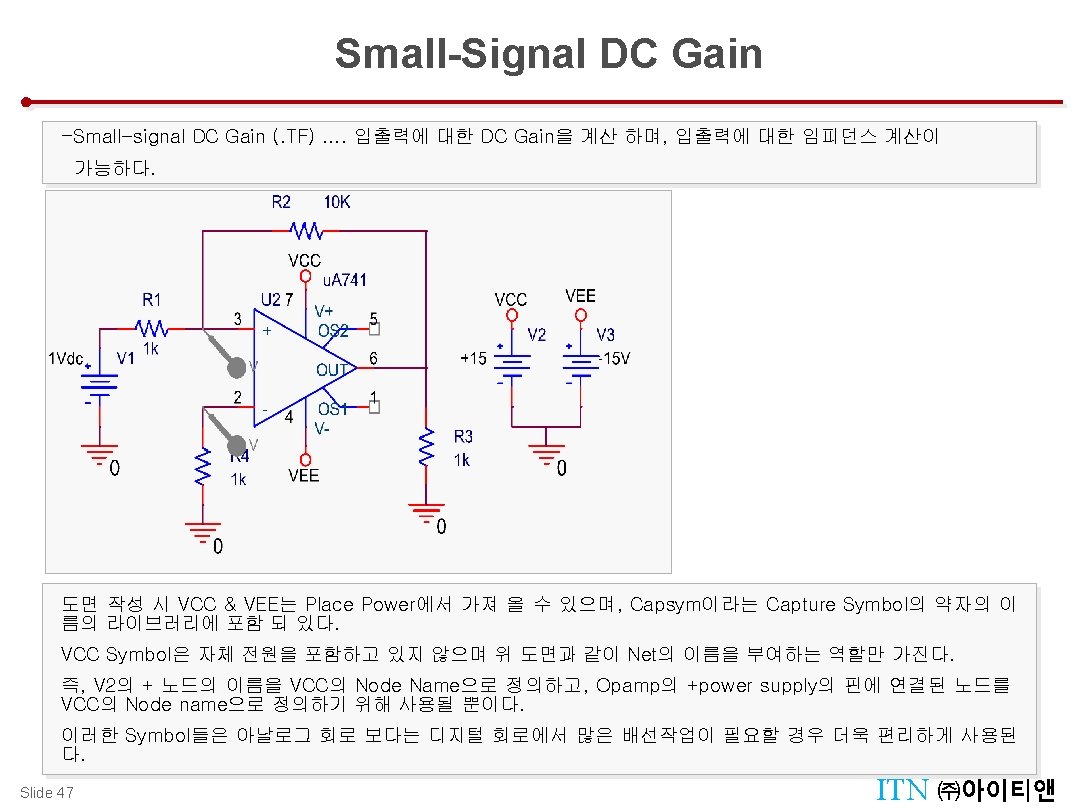

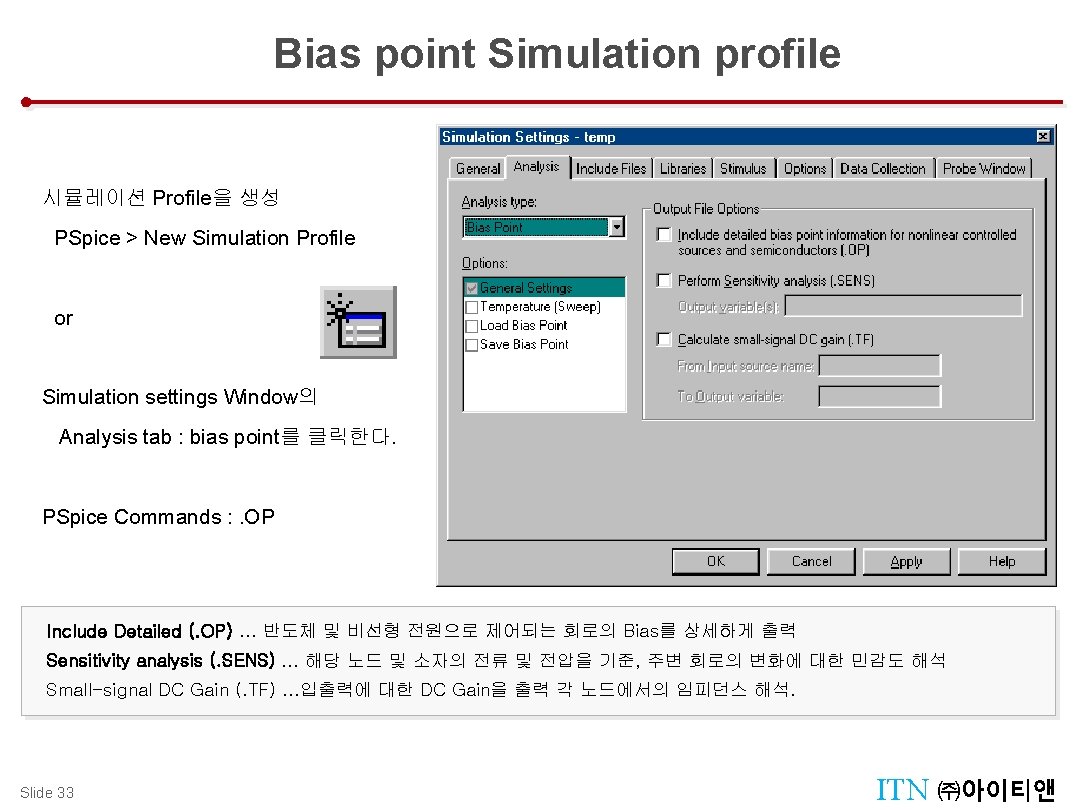

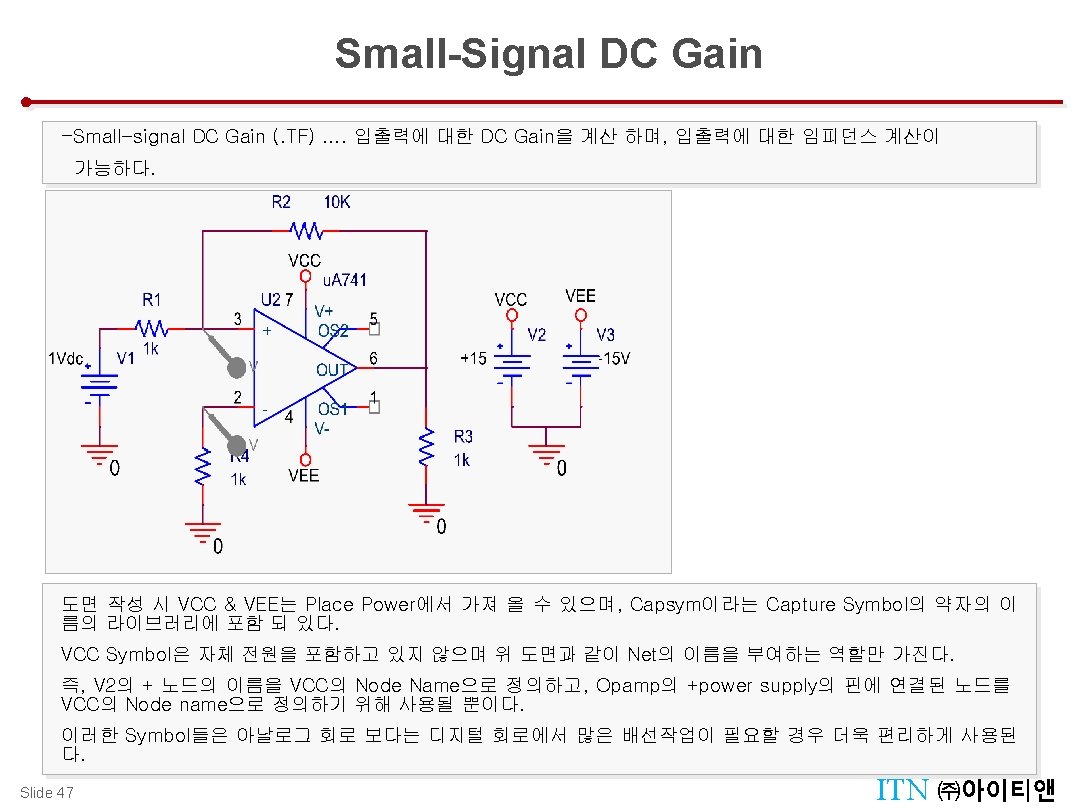

Bias point Simulation profile Design Tool Menu : Tool Palettes 시뮬레이션 Profile을 생성 PSpice > New Simulation Profile or Simulation settings Window의 Analysis tab : bias point를 클릭한다. PSpice Commands : . OP Include Detailed (. OP) … 반도체 및 비선형 전원으로 제어되는 회로의 Bias를 상세하게 출력 Sensitivity analysis (. SENS) … 해당 노드 및 소자의 전류 및 전압을 기준, 주변 회로의 변화에 대한 민감도 해석 Small-signal DC Gain (. TF) …입출력에 대한 DC Gain을 출력 각 노드에서의 임피던스 해석. Slide 33 ITN ㈜아이티앤

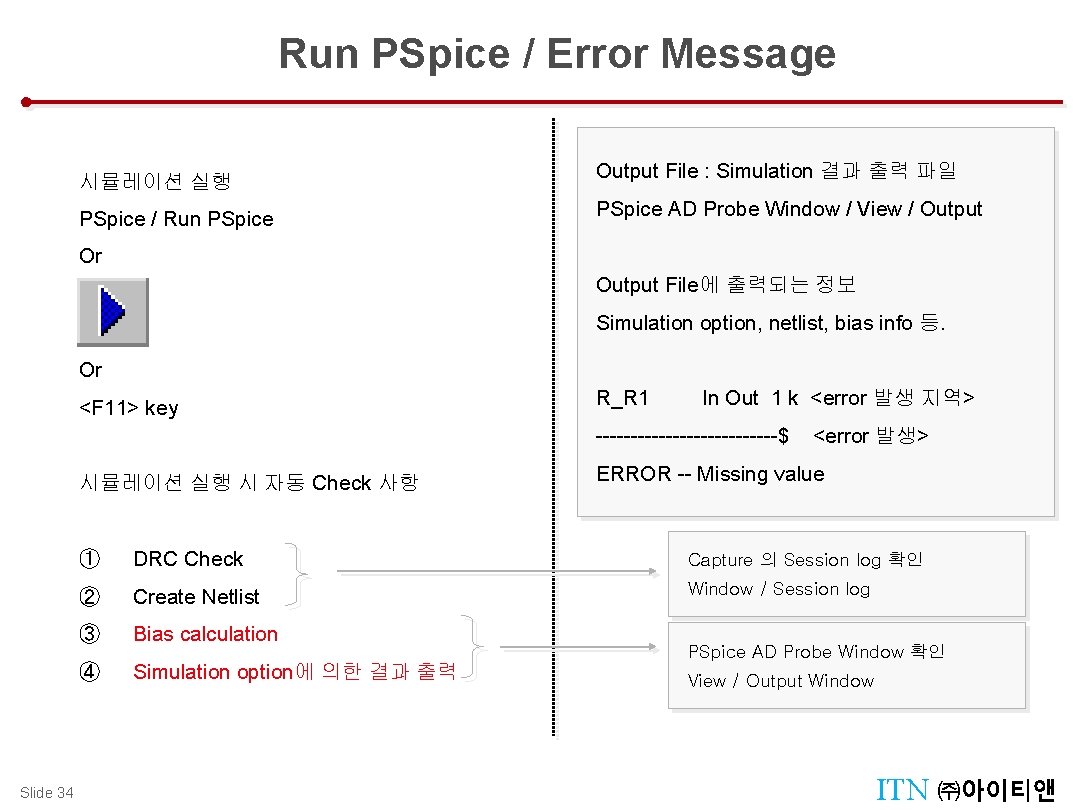

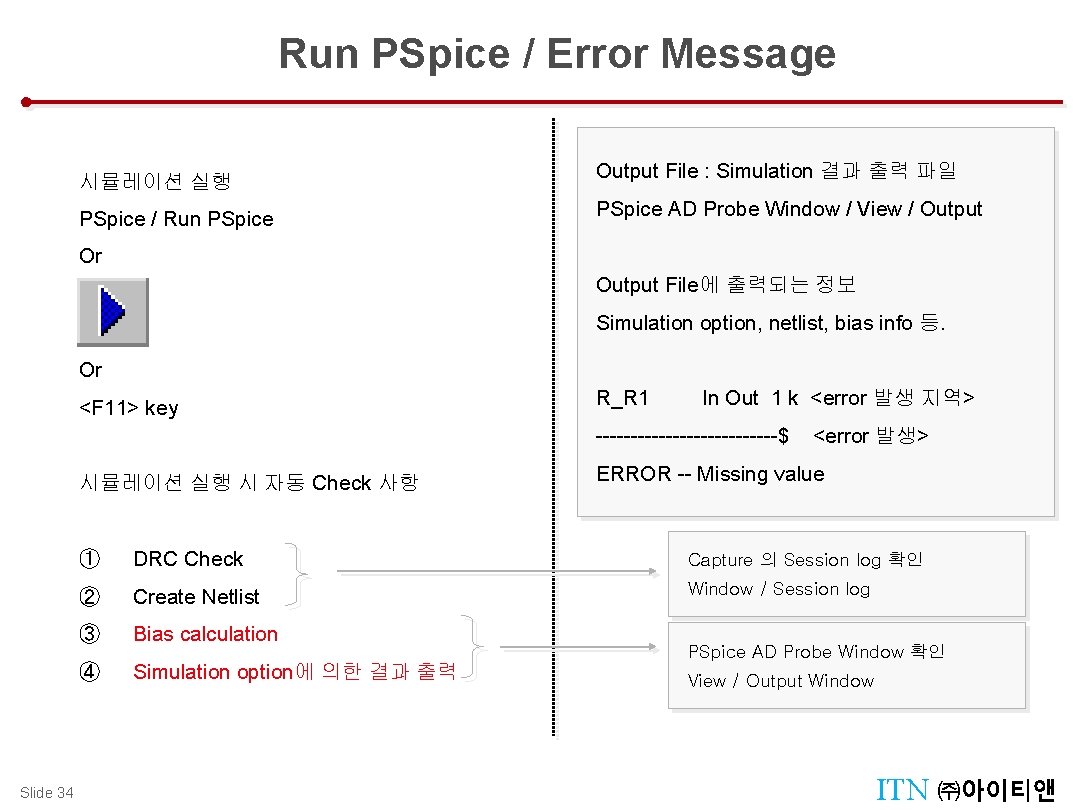

Run PSpice / Error Message Design Tool Menu : Tool Palettes 시뮬레이션 실행 Output File : Simulation 결과 출력 파일 PSpice / Run PSpice AD Probe Window / View / Output Or Output File에 출력되는 정보 Simulation option, netlist, bias info 등. Or <F 11> key R_R 1 In Out 1 k <error 발생 지역> -------------$ <error 발생> 시뮬레이션 실행 시 자동 Check 사항 Slide 34 ERROR -- Missing value ① DRC Check Capture 의 Session log 확인 ② Create Netlist Window / Session log ③ Bias calculation ④ Simulation option에 의한 결과 출력 PSpice AD Probe Window 확인 View / Output Window ITN ㈜아이티앤

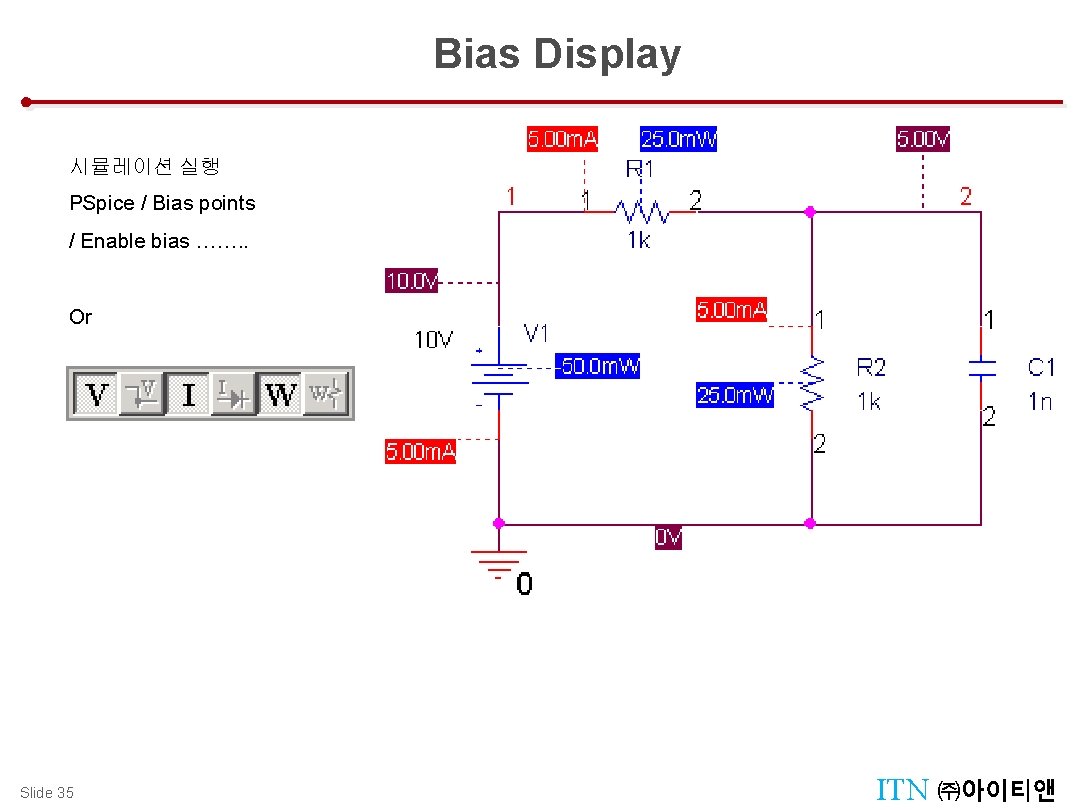

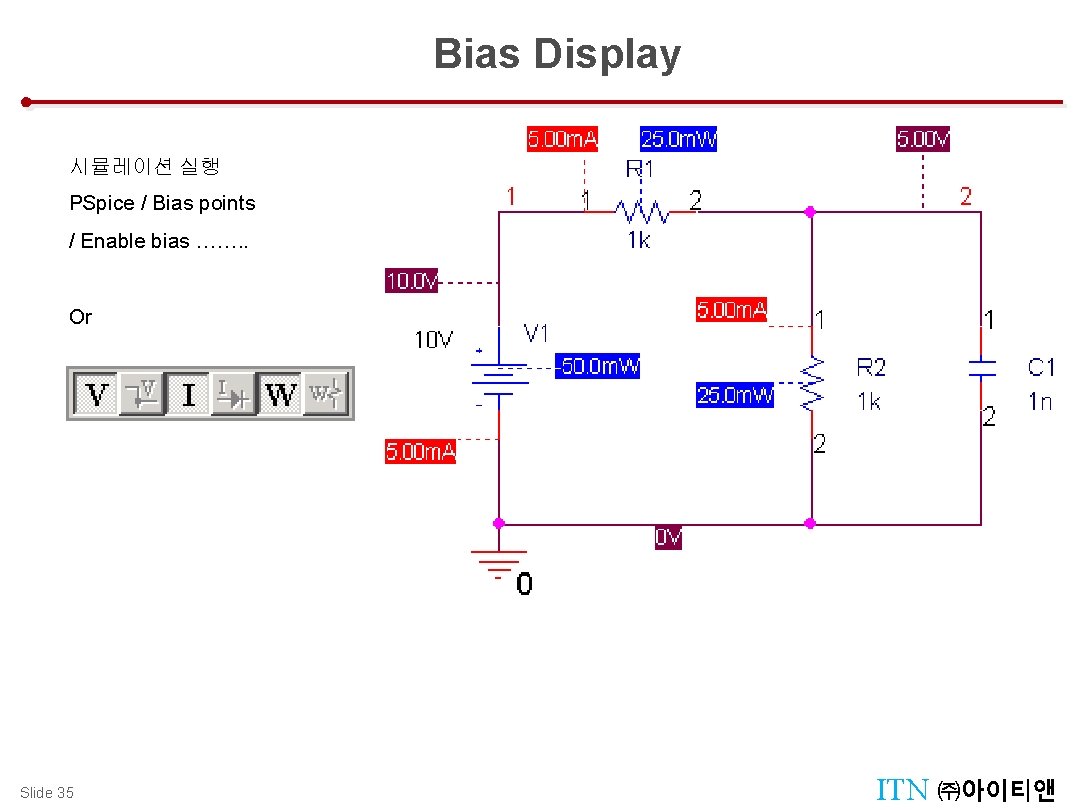

Design Tool Menu : Tool Palettes Bias Display 시뮬레이션 실행 PSpice / Bias points / Enable bias ……. . Or Slide 35 ITN ㈜아이티앤

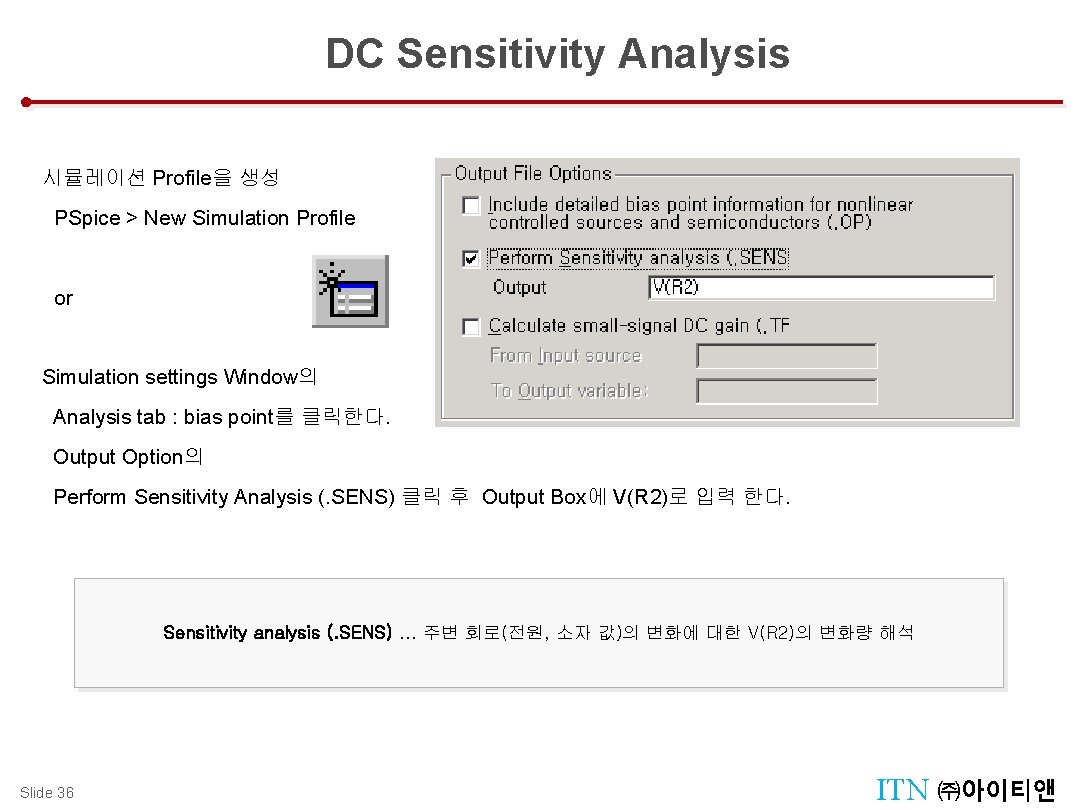

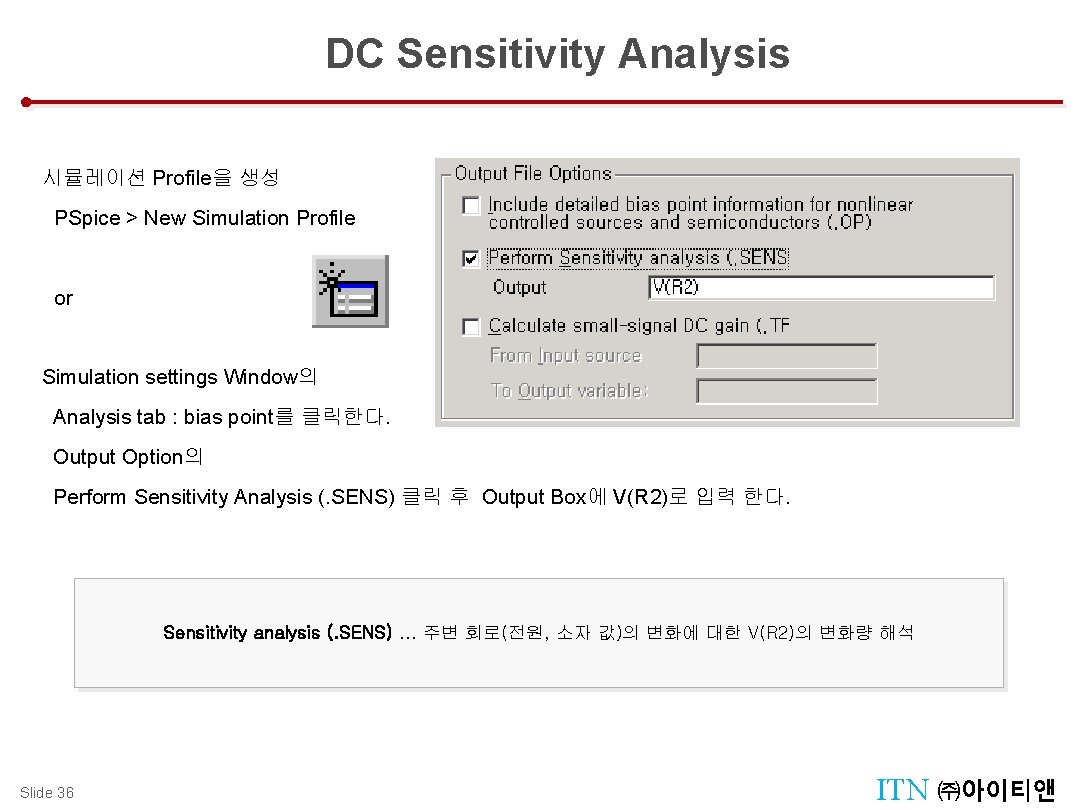

DC Sensitivity Analysis Design Tool Menu : Tool Palettes 시뮬레이션 Profile을 생성 PSpice > New Simulation Profile or Simulation settings Window의 Analysis tab : bias point를 클릭한다. Output Option의 Perform Sensitivity Analysis (. SENS) 클릭 후 Output Box에 V(R 2)로 입력 한다. Sensitivity analysis (. SENS) … 주변 회로(전원, 소자 값)의 변화에 대한 V(R 2)의 변화량 해석 Slide 36 ITN ㈜아이티앤

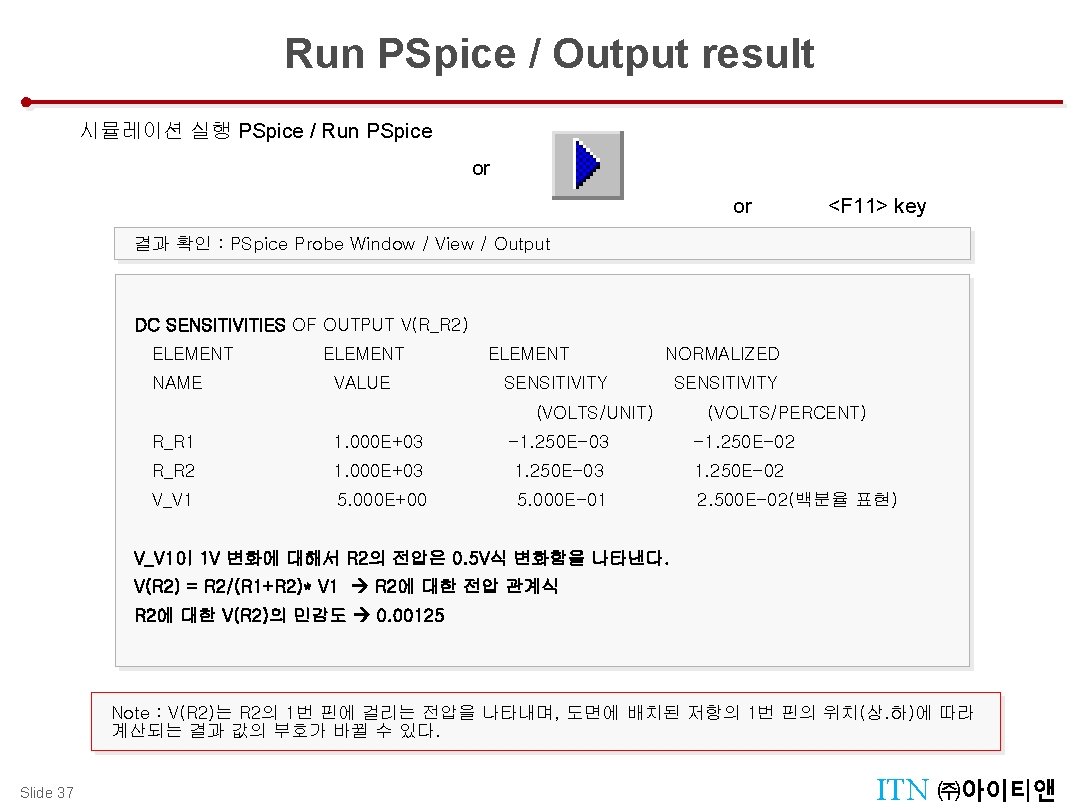

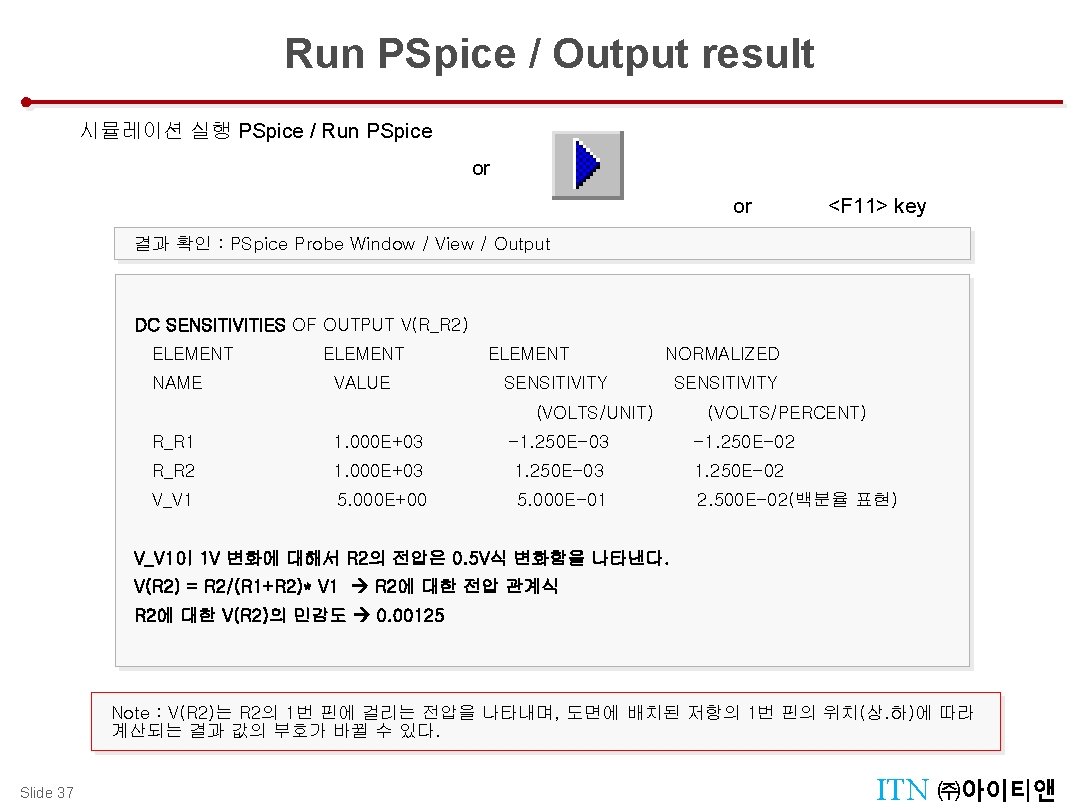

Run PSpice / Output result Design Tool Menu : Tool Palettes 시뮬레이션 실행 PSpice / Run PSpice or or <F 11> key 결과 확인 : PSpice Probe Window / View / Output DC SENSITIVITIES OF OUTPUT V(R_R 2) ELEMENT NAME ELEMENT VALUE ELEMENT NORMALIZED SENSITIVITY (VOLTS/UNIT) SENSITIVITY (VOLTS/PERCENT) R_R 1 1. 000 E+03 -1. 250 E-02 R_R 2 1. 000 E+03 1. 250 E-02 V_V 1 5. 000 E+00 5. 000 E-01 2. 500 E-02(백분율 표현) V_V 1이 1 V 변화에 대해서 R 2의 전압은 0. 5 V식 변화함을 나타낸다. V(R 2) = R 2/(R 1+R 2)* V 1 R 2에 대한 전압 관계식 R 2에 대한 V(R 2)의 민감도 0. 00125 Note : V(R 2)는 R 2의 1번 핀에 걸리는 전압을 나타내며, 도면에 배치된 저항의 1번 핀의 위치(상. 하)에 따라 계산되는 결과 값의 부호가 바뀔 수 있다. Slide 37 ITN ㈜아이티앤

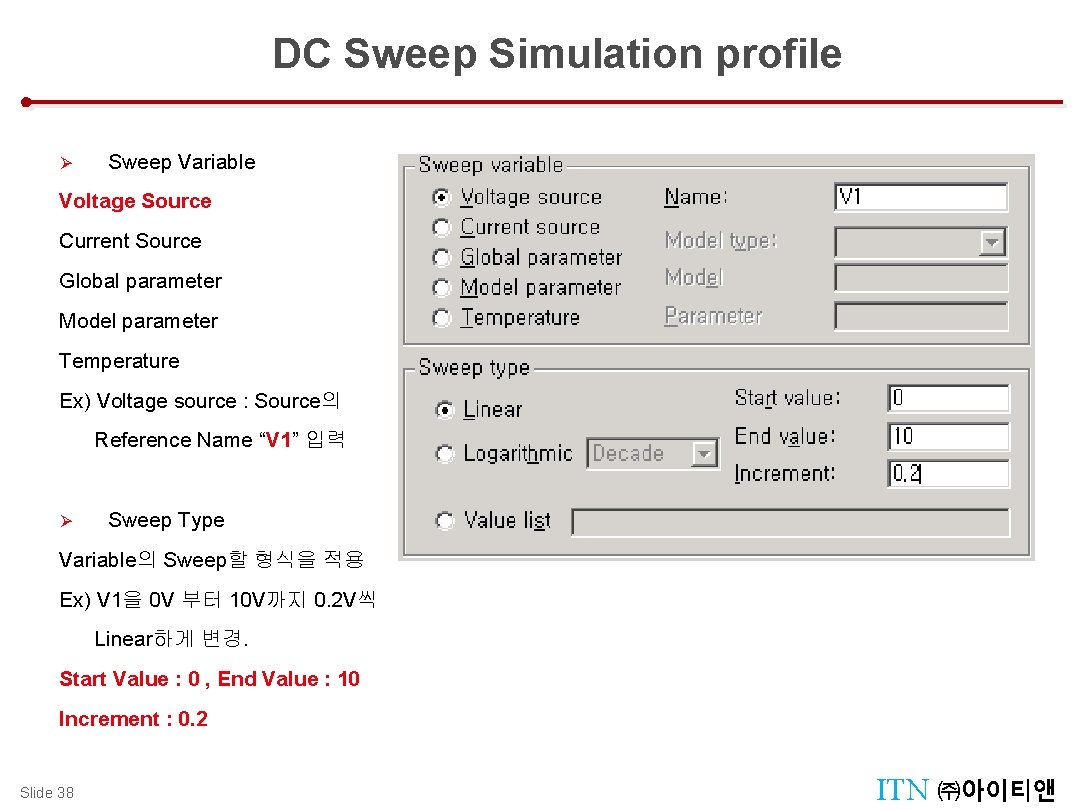

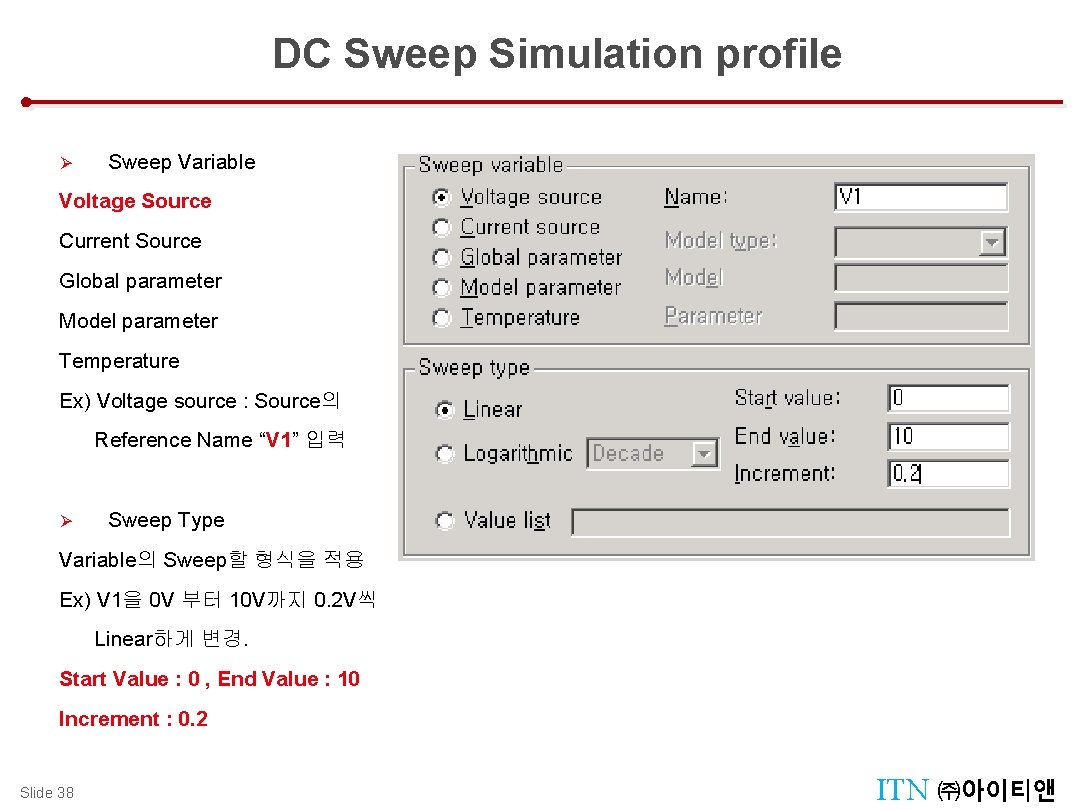

DC Sweep Simulation profile Design Tool Menu : Tool Palettes Ø Sweep Variable Voltage Source Current Source Global parameter Model parameter Temperature Ex) Voltage source : Source의 Reference Name “V 1” 입력 Ø Sweep Type Variable의 Sweep할 형식을 적용 Ex) V 1을 0 V 부터 10 V까지 0. 2 V씩 Linear하게 변경. Start Value : 0 , End Value : 10 Increment : 0. 2 Slide 38 ITN ㈜아이티앤

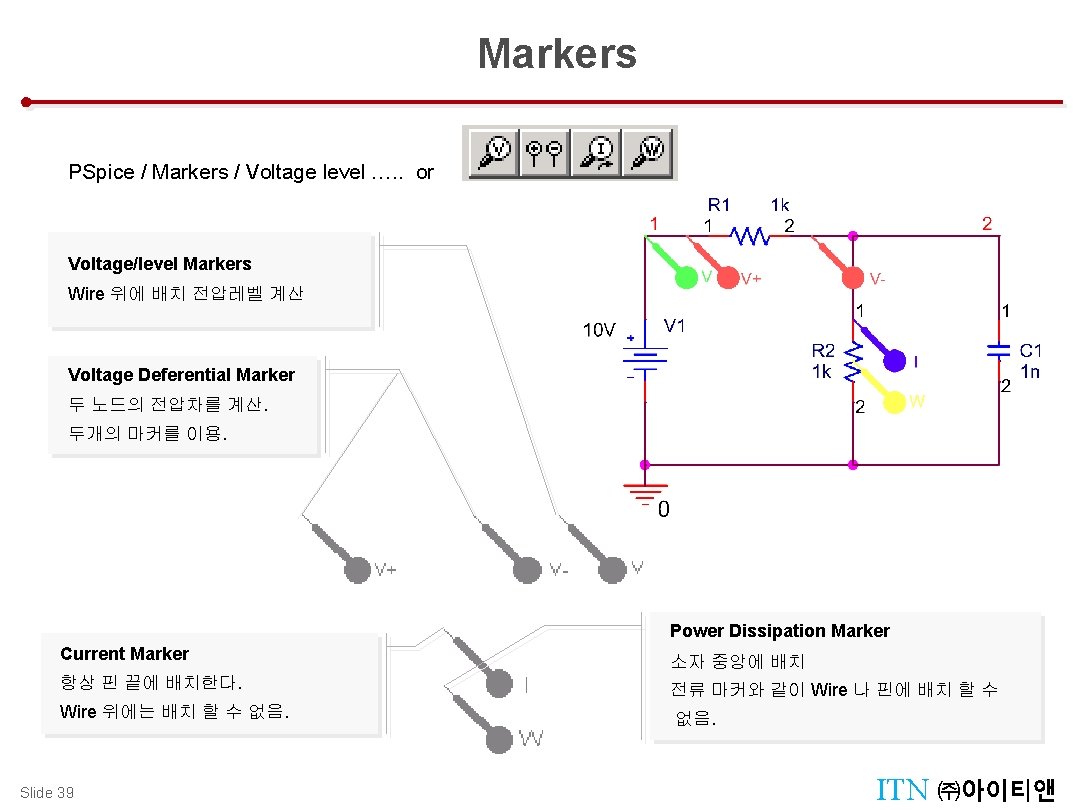

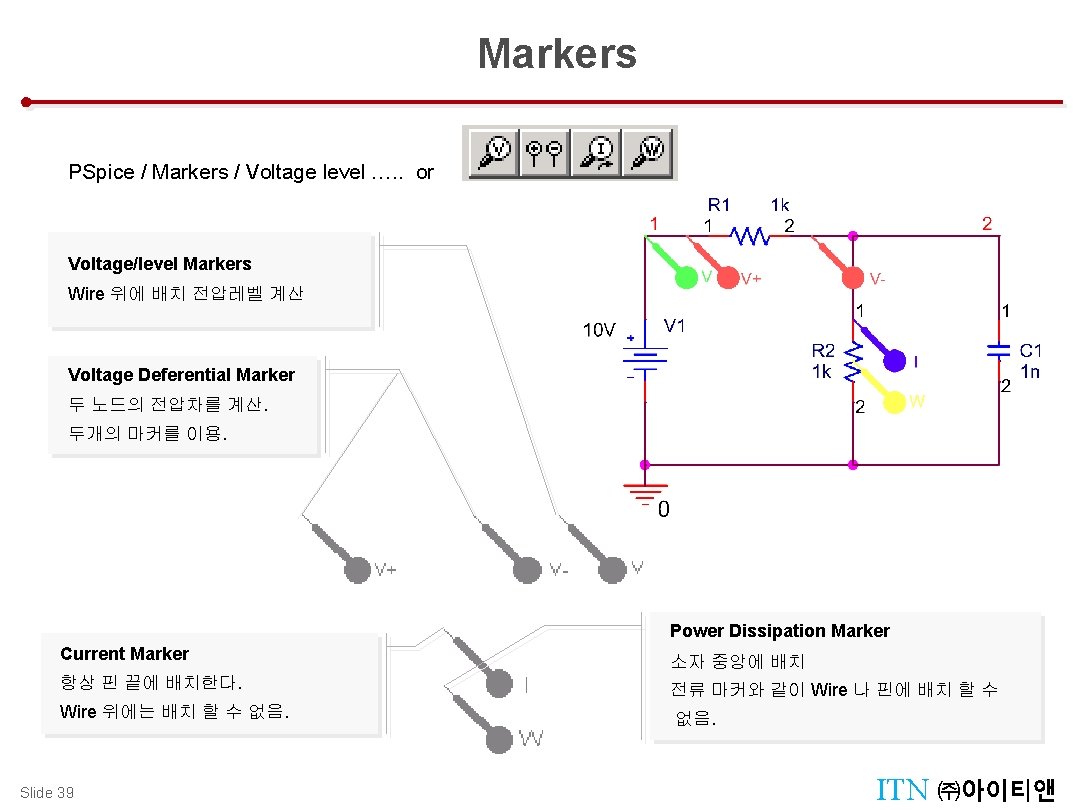

Design Tool Menu : Tool Palettes Markers PSpice / Markers / Voltage level …. . or Voltage/level Markers Wire 위에 배치 전압레벨 계산 Voltage Deferential Marker 두 노드의 전압차를 계산. 두개의 마커를 이용. Power Dissipation Marker Current Marker 소자 중앙에 배치 항상 핀 끝에 배치한다. 전류 마커와 같이 Wire 나 핀에 배치 할 수 Wire 위에는 배치 할 수 없음. Slide 39 ITN ㈜아이티앤

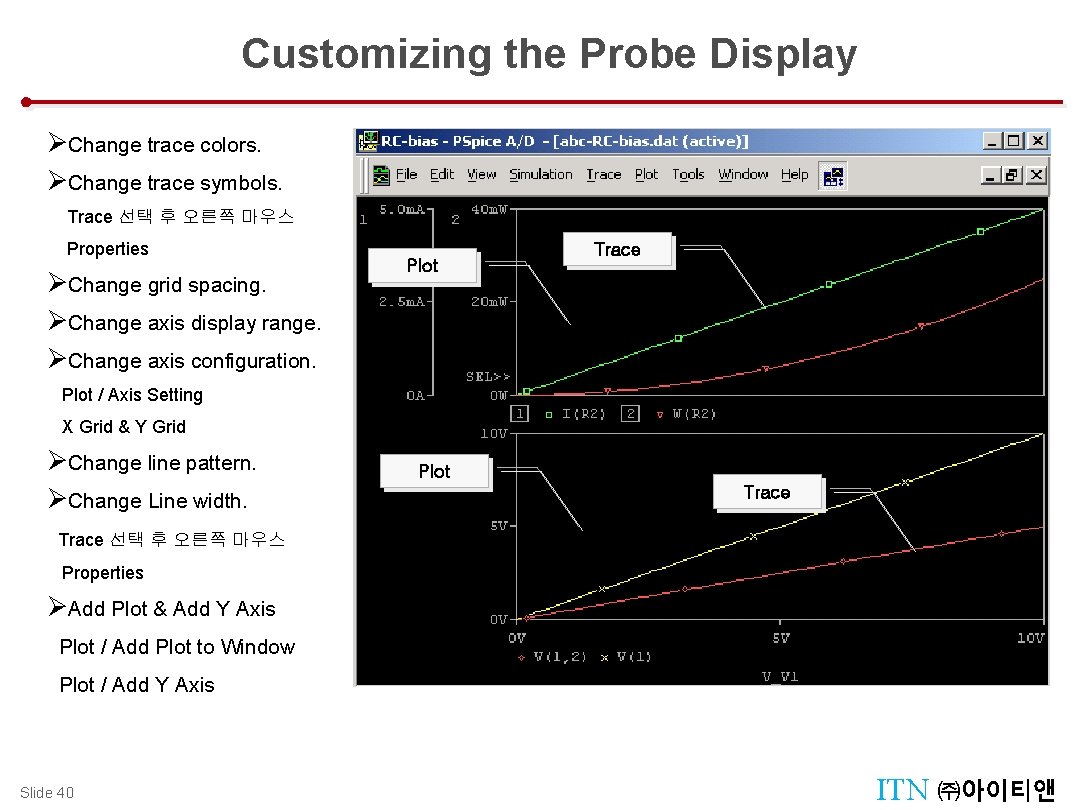

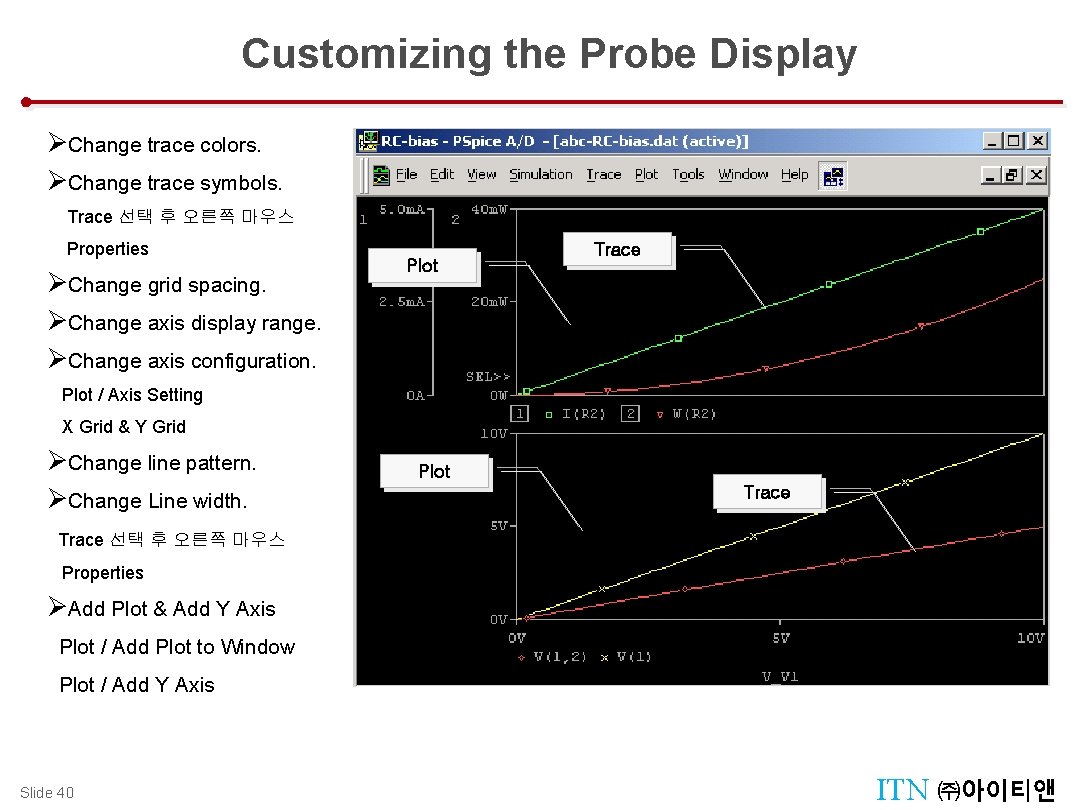

Customizing the Probe Display Design Tool Menu : Tool Palettes ØChange trace colors. ØChange trace symbols. Trace 선택 후 오른쪽 마우스 Properties ØChange grid spacing. ØChange axis display range. ØChange axis configuration. Plot Trace Plot / Axis Setting X Grid & Y Grid ØChange line pattern. ØChange Line width. Plot Trace 선택 후 오른쪽 마우스 Properties ØAdd Plot & Add Y Axis Plot / Add Plot to Window Plot / Add Y Axis Slide 40 ITN ㈜아이티앤

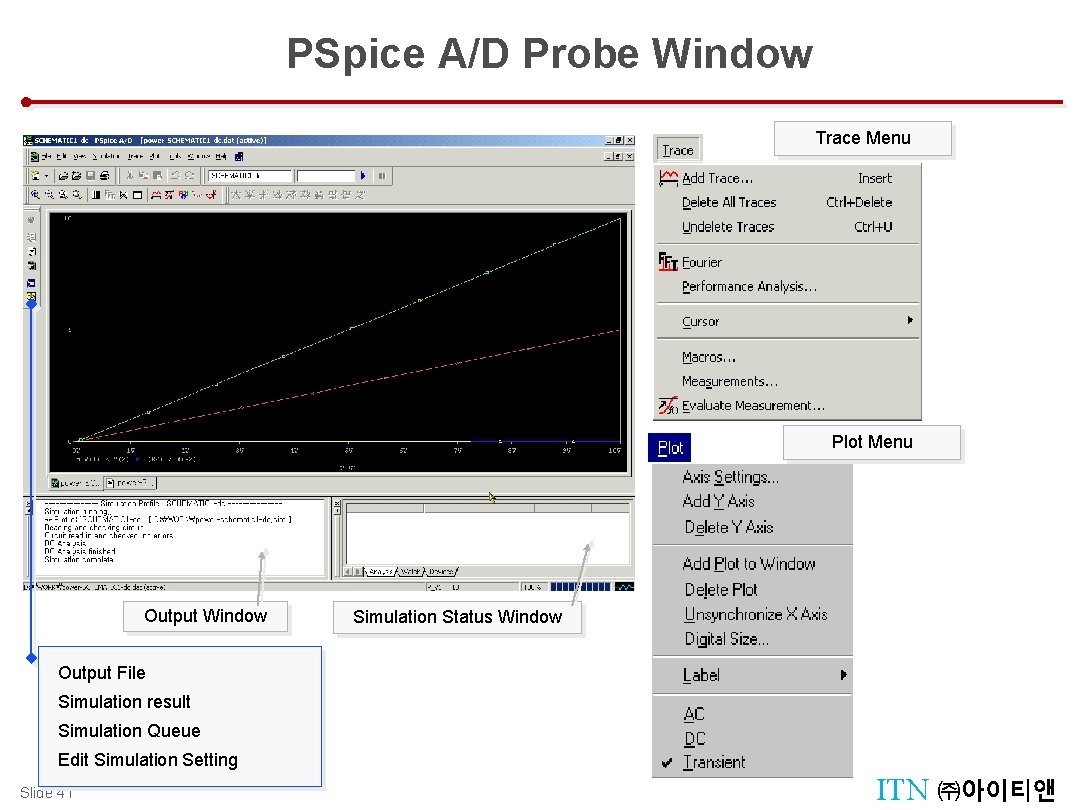

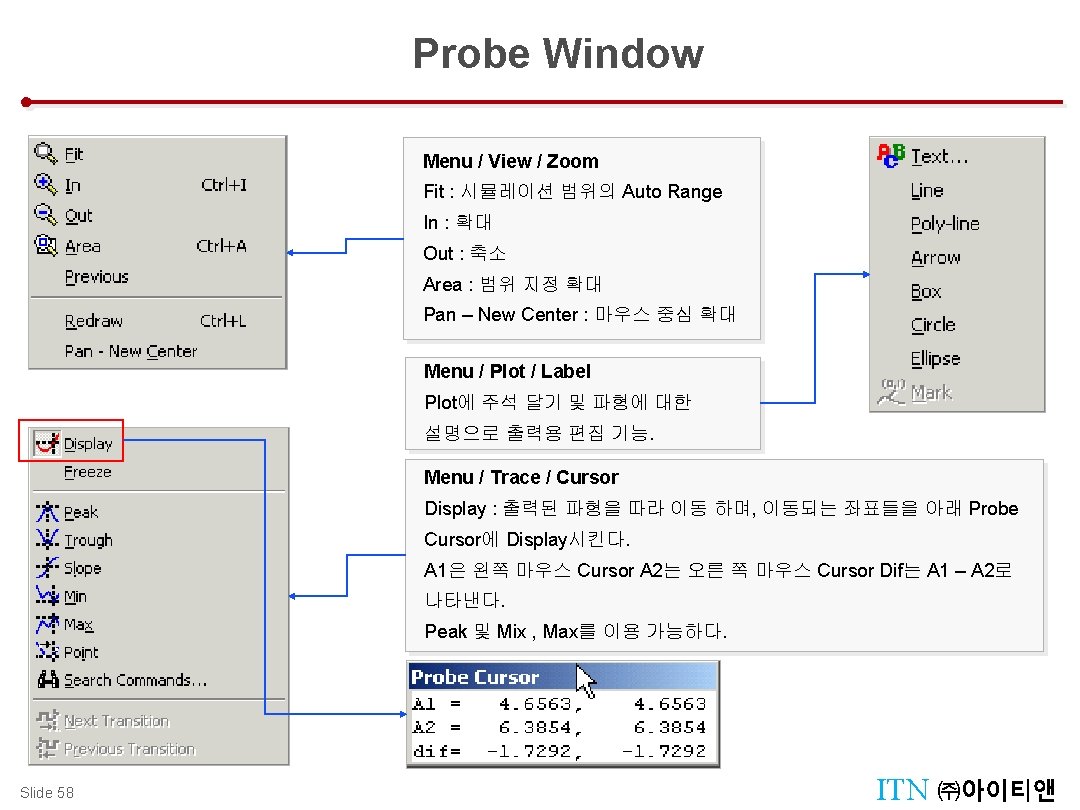

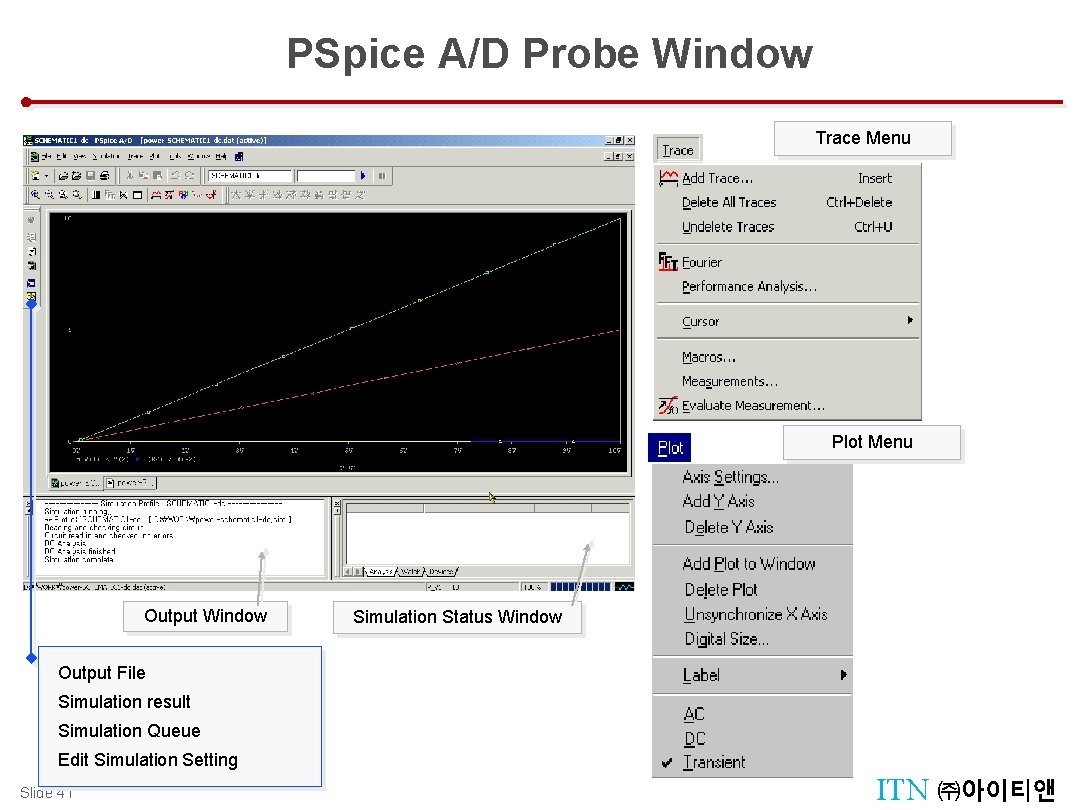

PSpice A/D Probe Window Trace Menu Plot Menu Output Window Simulation Status Window Output File Simulation result Simulation Queue Edit Simulation Setting Slide 41 ITN ㈜아이티앤

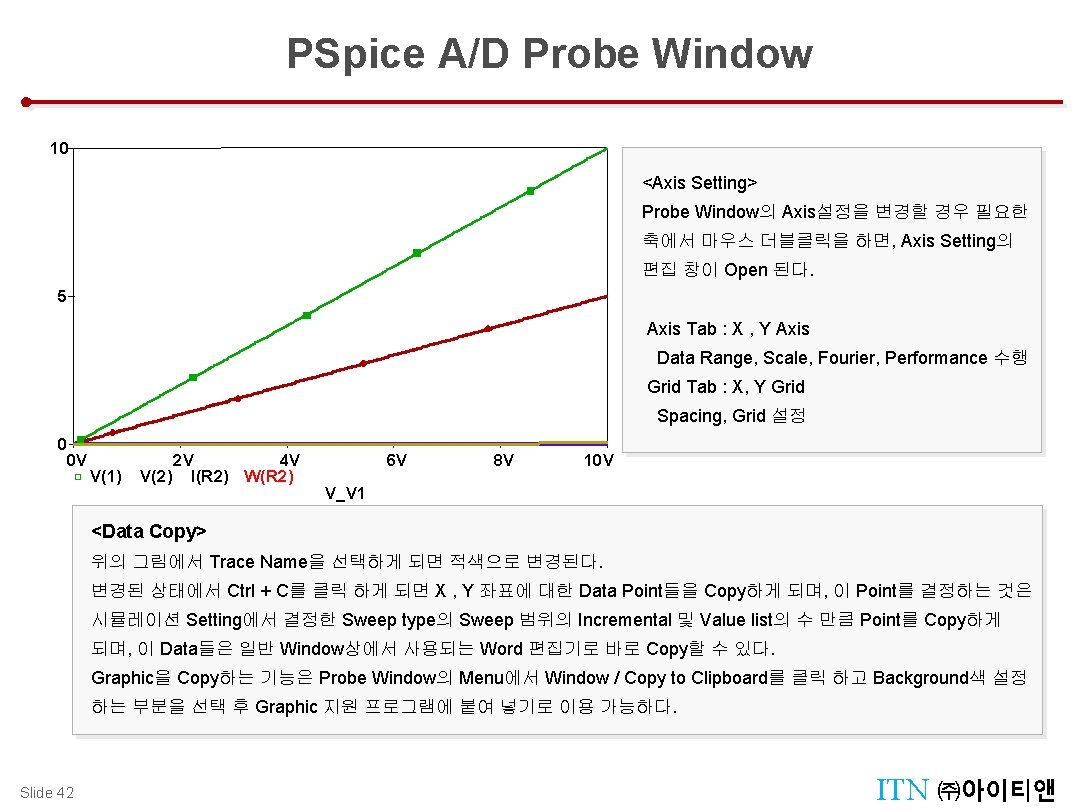

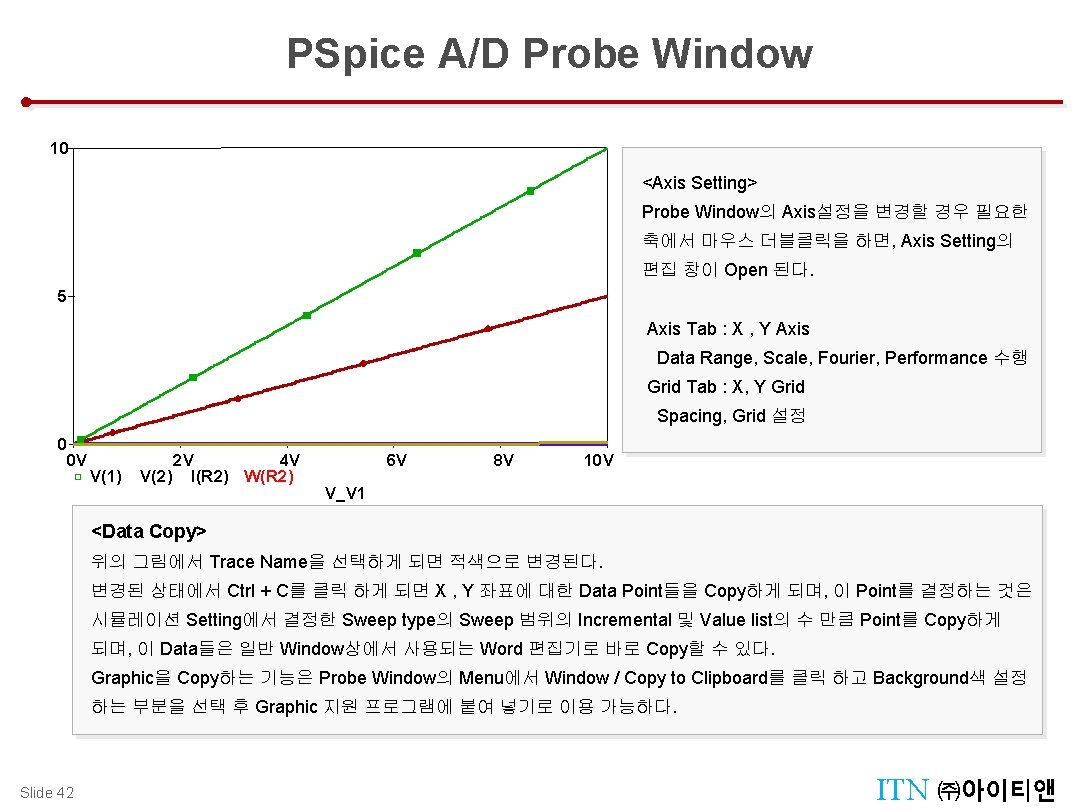

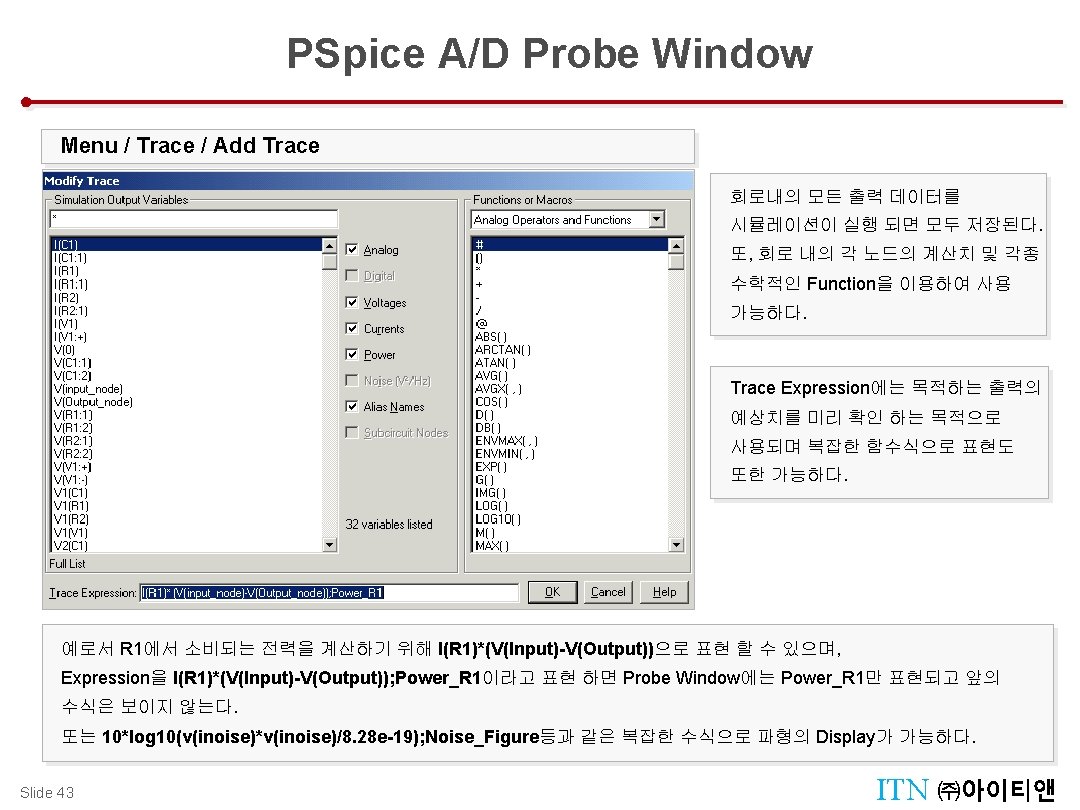

PSpice A/D Probe Window 10 <Axis Setting> Probe Window의 Axis설정을 변경할 경우 필요한 축에서 마우스 더블클릭을 하면, Axis Setting의 편집 창이 Open 된다. 5 Axis Tab : X , Y Axis Data Range, Scale, Fourier, Performance 수행 Grid Tab : X, Y Grid Spacing, Grid 설정 0 0 V V(1) 2 V 4 V V(2) I(R 2) W(R 2) 6 V 8 V 10 V V_V 1 <Data Copy> 위의 그림에서 Trace Name을 선택하게 되면 적색으로 변경된다. 변경된 상태에서 Ctrl + C를 클릭 하게 되면 X , Y 좌표에 대한 Data Point들을 Copy하게 되며, 이 Point를 결정하는 것은 시뮬레이션 Setting에서 결정한 Sweep type의 Sweep 범위의 Incremental 및 Value list의 수 만큼 Point를 Copy하게 되며, 이 Data들은 일반 Window상에서 사용되는 Word 편집기로 바로 Copy할 수 있다. Graphic을 Copy하는 기능은 Probe Window의 Menu에서 Window / Copy to Clipboard를 클릭 하고 Background색 설정 하는 부분을 선택 후 Graphic 지원 프로그램에 붙여 넣기로 이용 가능하다. Slide 42 ITN ㈜아이티앤

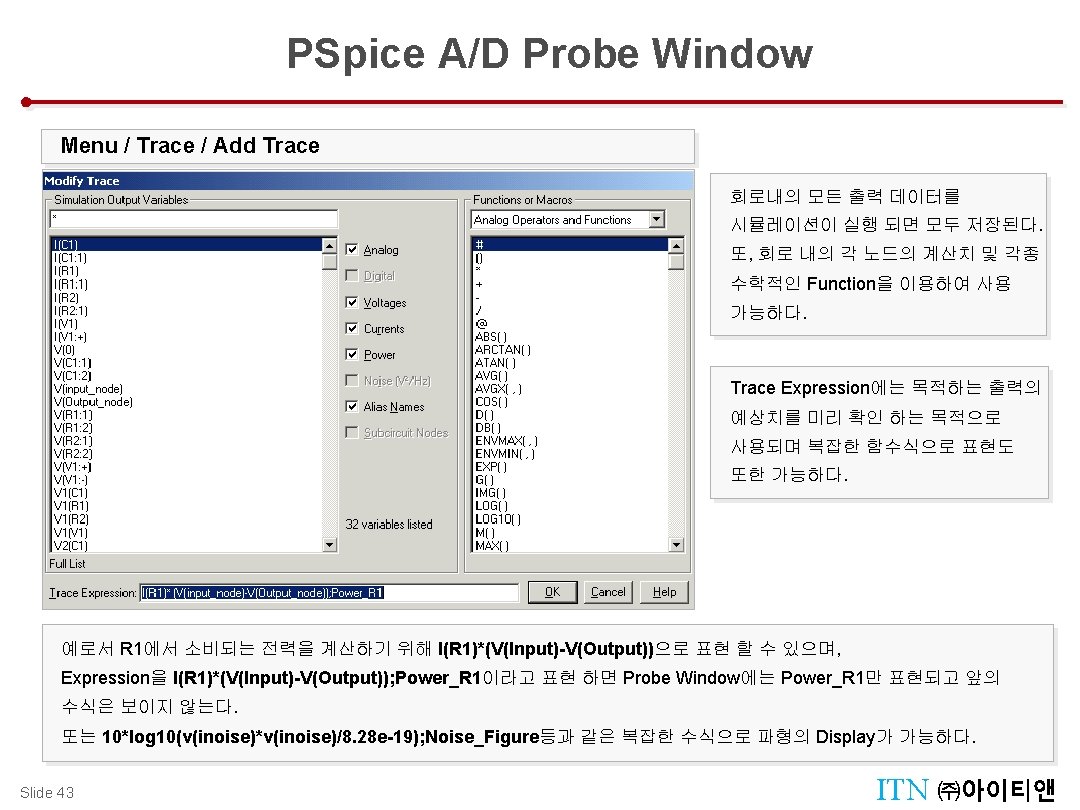

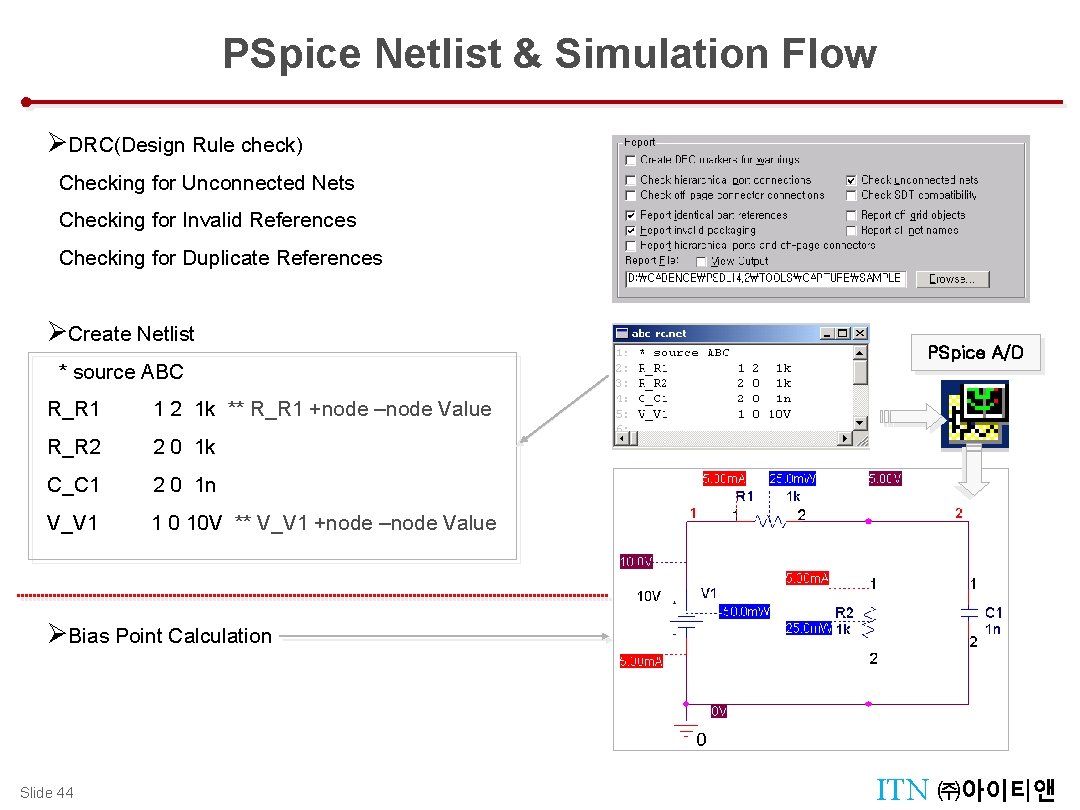

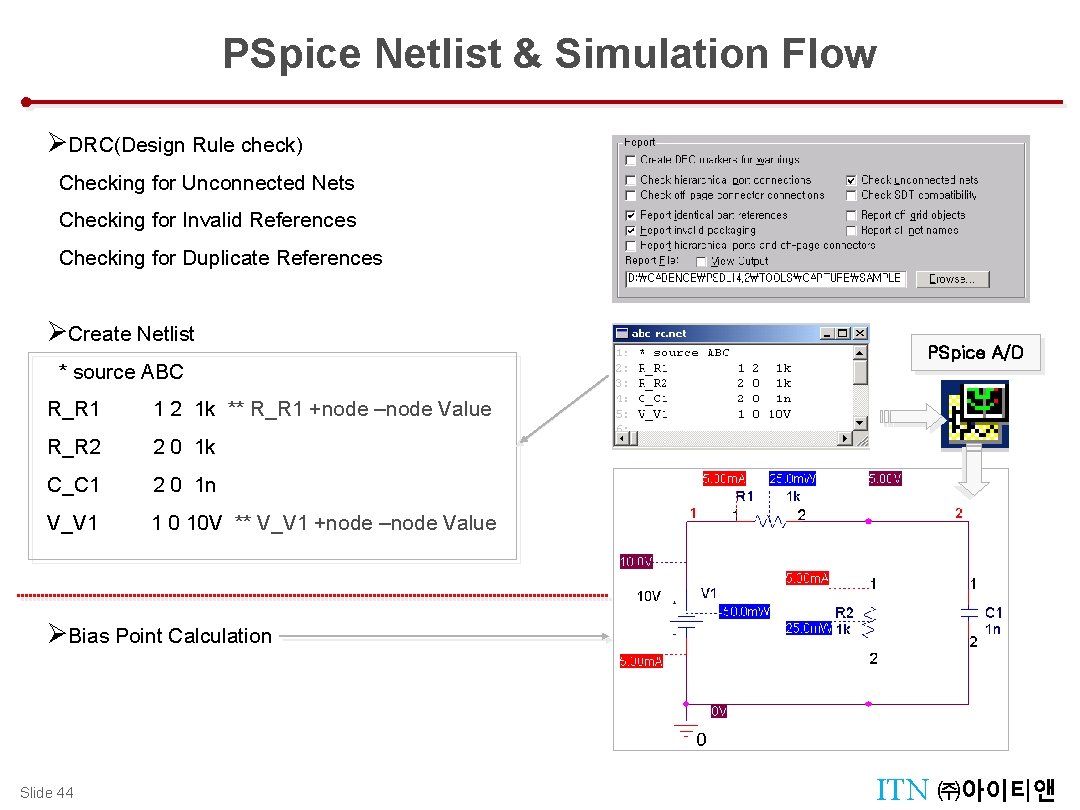

PSpice Netlist & Simulation Flow Design Tool Menu : Tool Palettes ØDRC(Design Rule check) Checking for Unconnected Nets Checking for Invalid References Checking for Duplicate References ØCreate Netlist * source ABC PSpice A/D R_R 1 1 2 1 k ** R_R 1 +node –node Value R_R 2 2 0 1 k C_C 1 2 0 1 n V_V 1 1 0 10 V ** V_V 1 +node –node Value ØBias Point Calculation Slide 44 ITN ㈜아이티앤

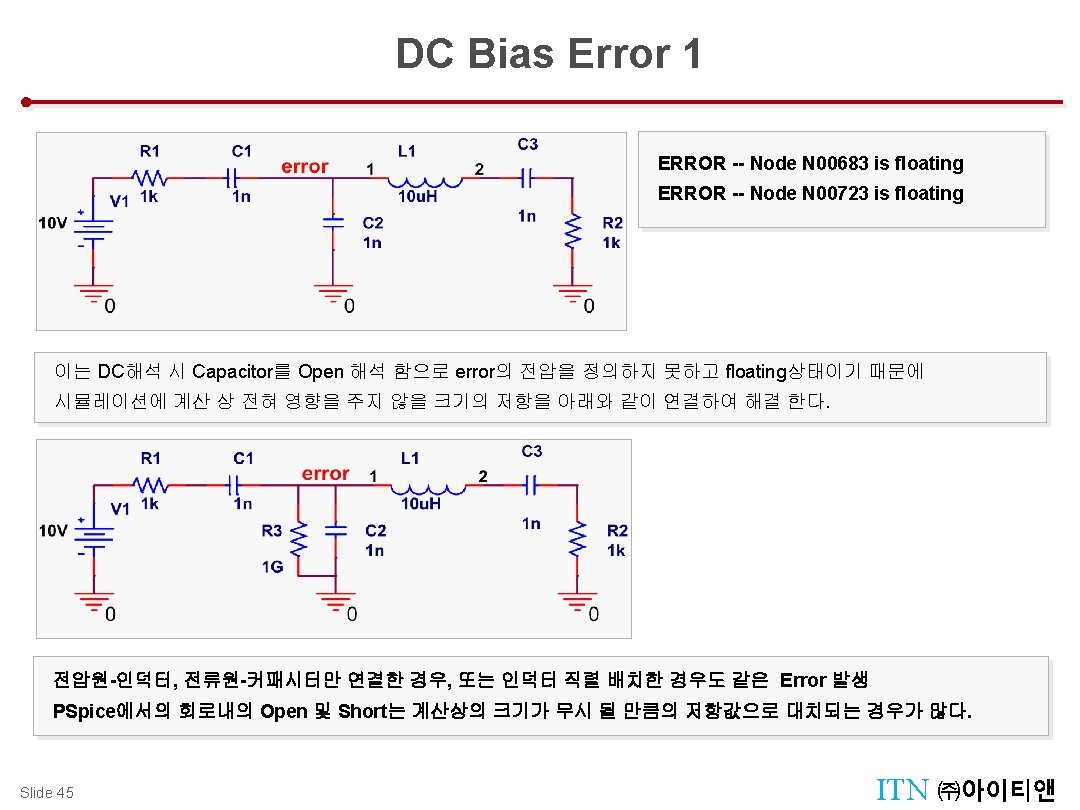

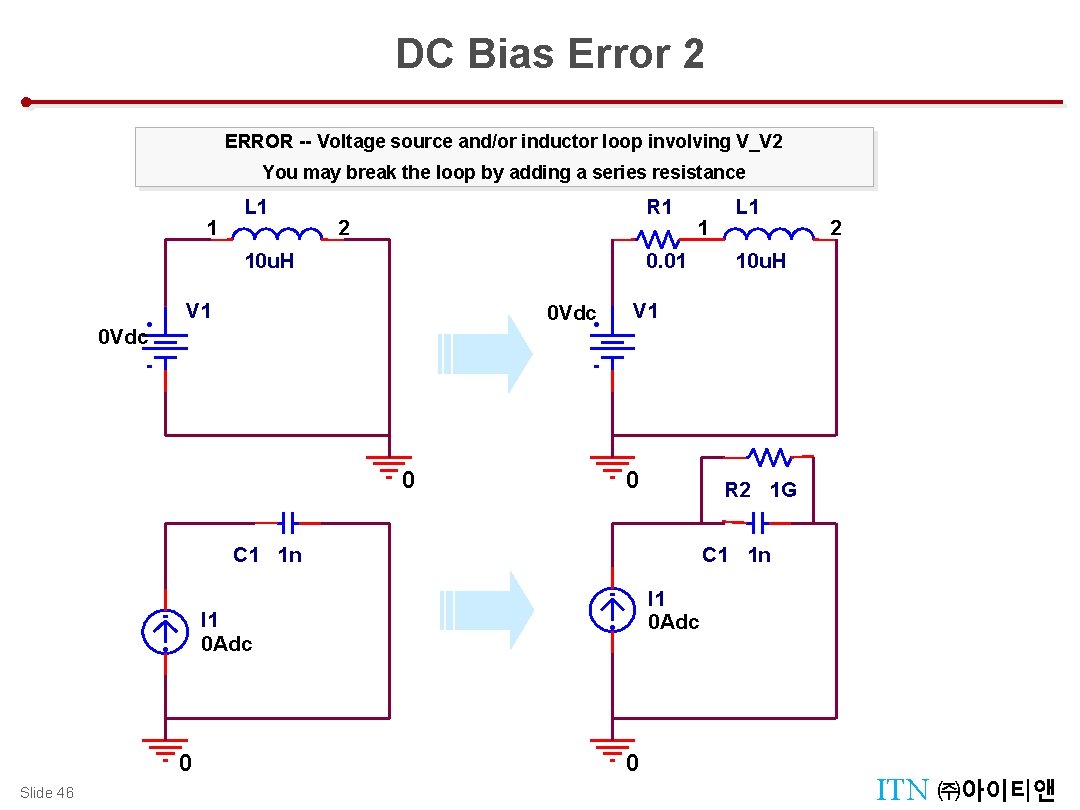

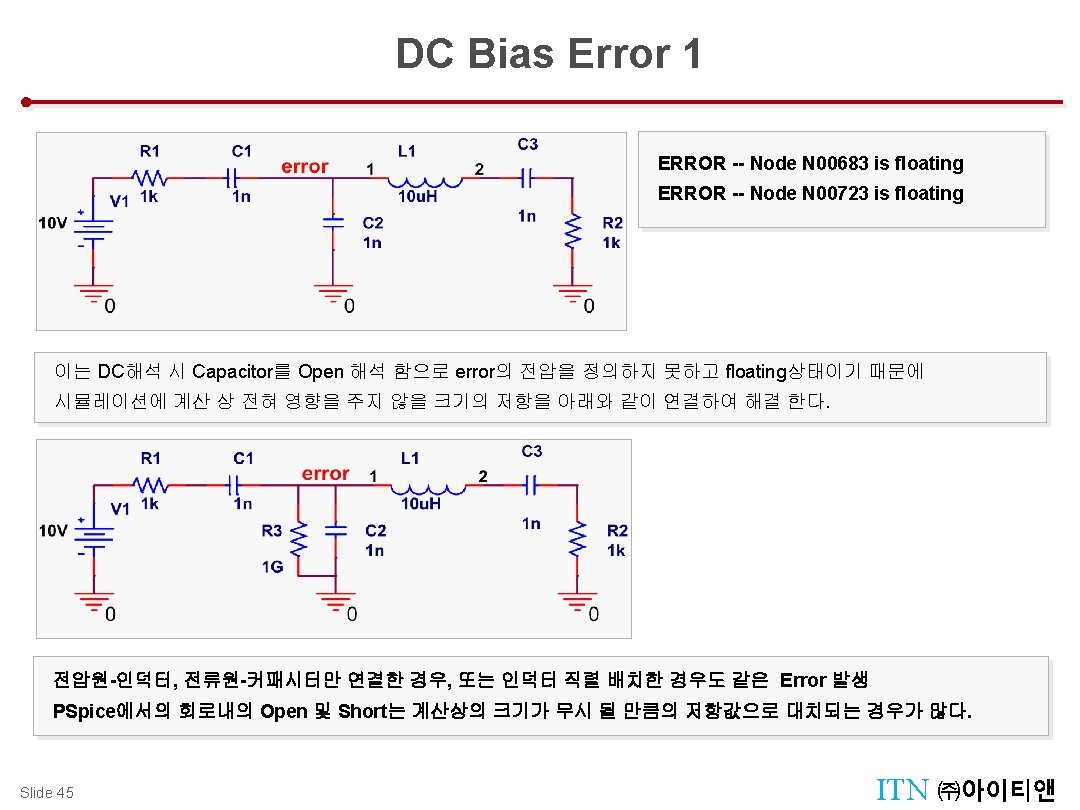

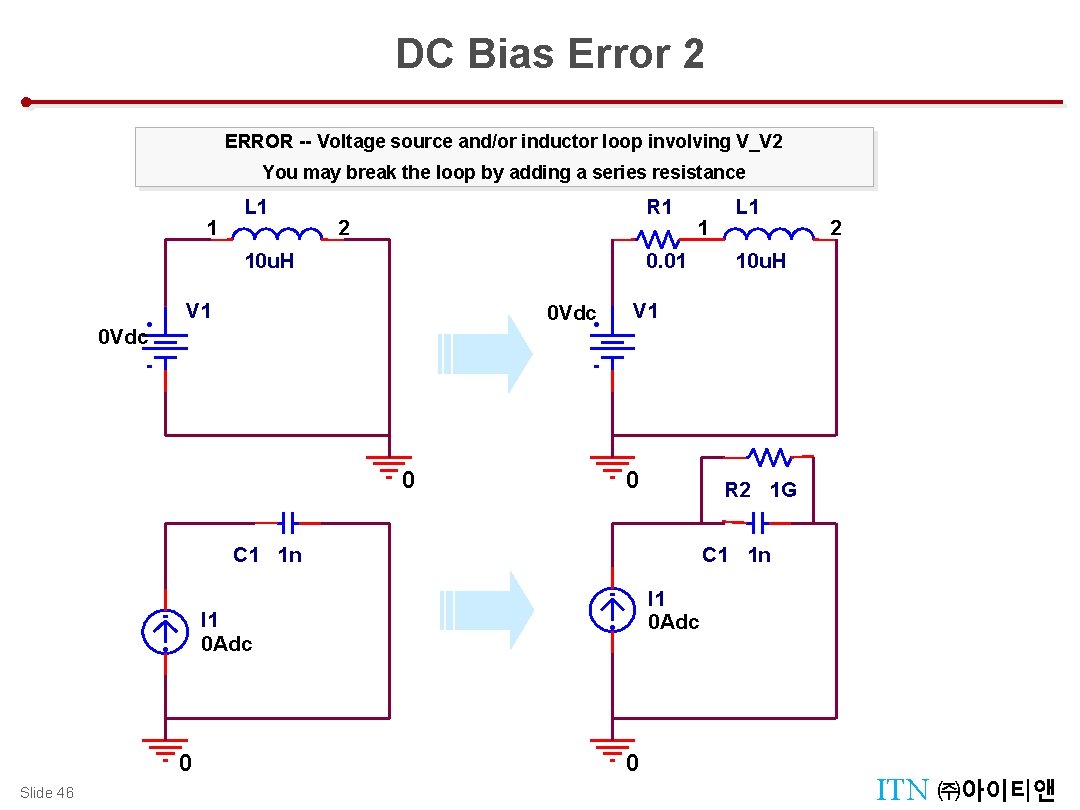

DC Bias Error 2 Design Structure ERROR -- Voltage source and/or inductor loop involving V_V 2 You may break the loop by adding a series resistance 1 L 1 R 1 2 10 u. H 1 0. 01 V 1 0 Vdc L 1 2 10 u. H V 1 0 Vdc 0 0 R 2 1 G C 1 1 n I 1 0 Adc 0 Slide 46 0 ITN ㈜아이티앤

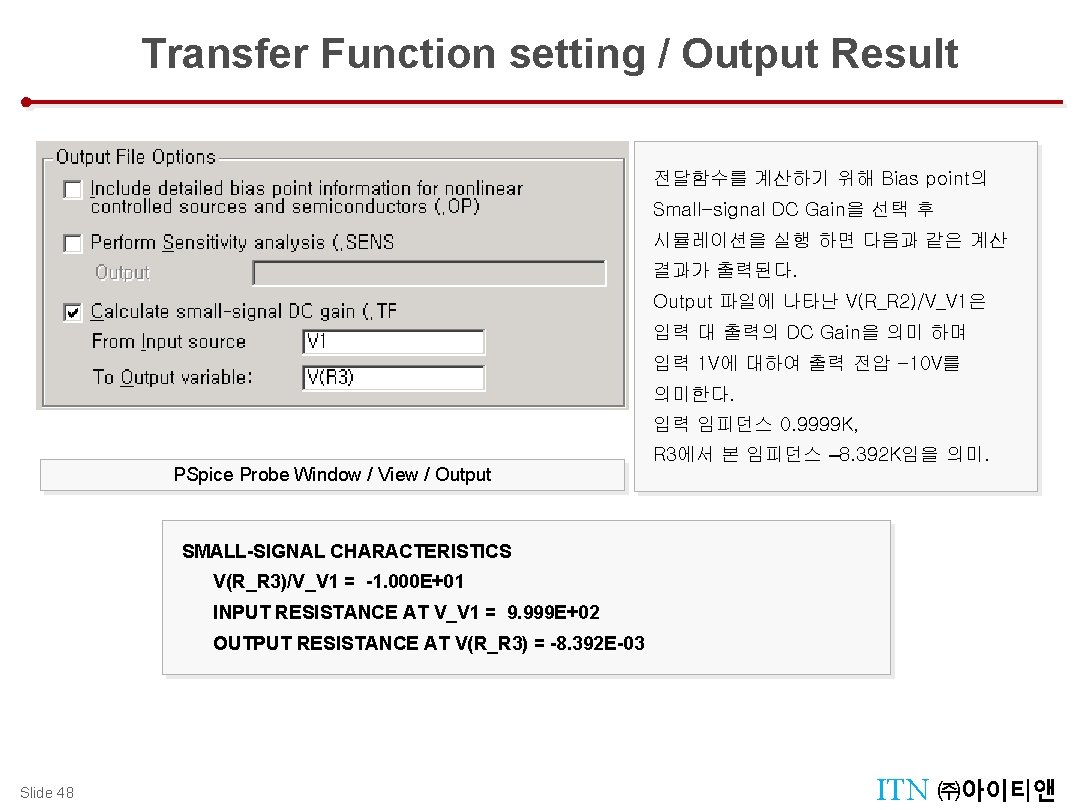

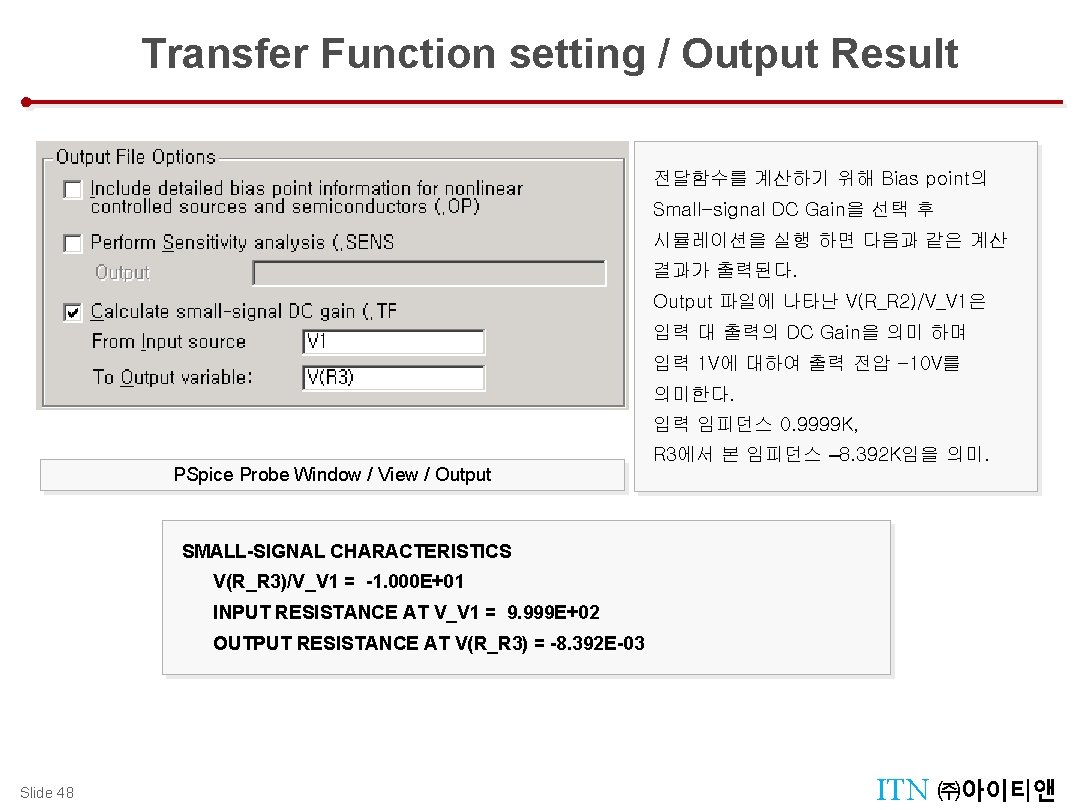

Transfer Function setting / Output Result Design Management : Manager Tool 전달함수를 계산하기 위해 Bias point의 Small-signal DC Gain을 선택 후 시뮬레이션을 실행 하면 다음과 같은 계산 결과가 출력된다. Output 파일에 나타난 V(R_R 2)/V_V 1은 입력 대 출력의 DC Gain을 의미 하며 입력 1 V에 대하여 출력 전압 -10 V를 의미한다. 입력 임피던스 0. 9999 K, PSpice Probe Window / View / Output R 3에서 본 임피던스 – 8. 392 K임을 의미. SMALL-SIGNAL CHARACTERISTICS V(R_R 3)/V_V 1 = -1. 000 E+01 INPUT RESISTANCE AT V_V 1 = 9. 999 E+02 OUTPUT RESISTANCE AT V(R_R 3) = -8. 392 E-03 Slide 48 ITN ㈜아이티앤

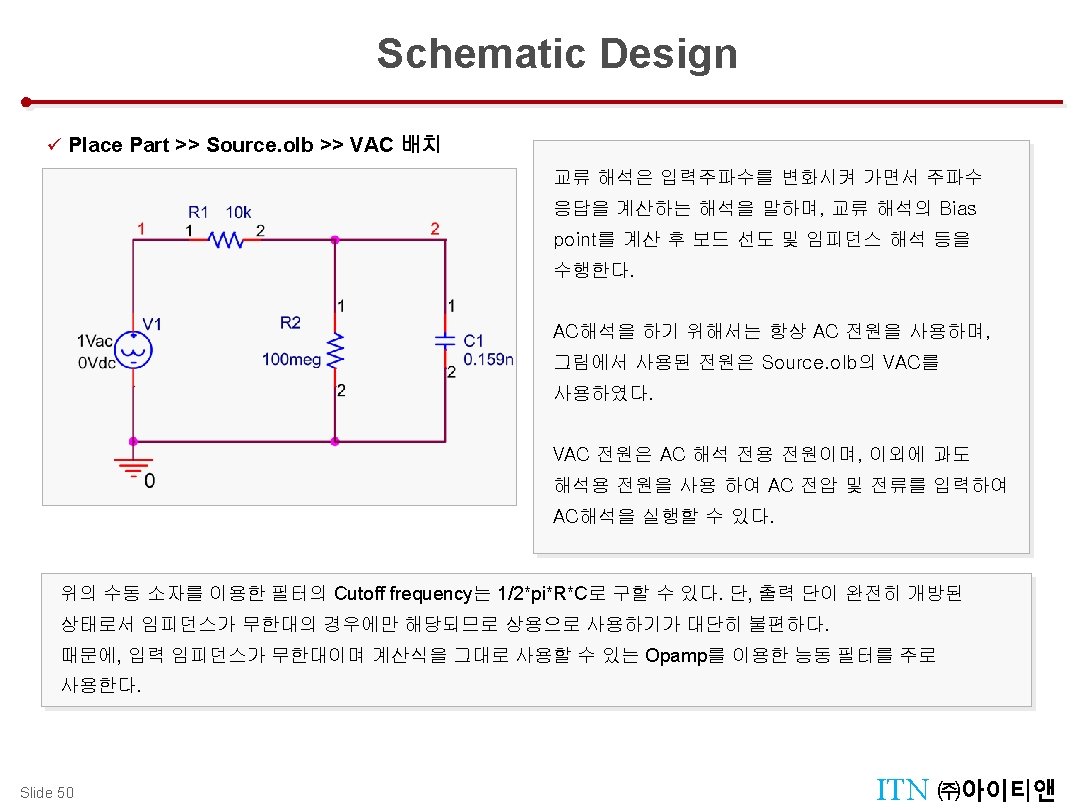

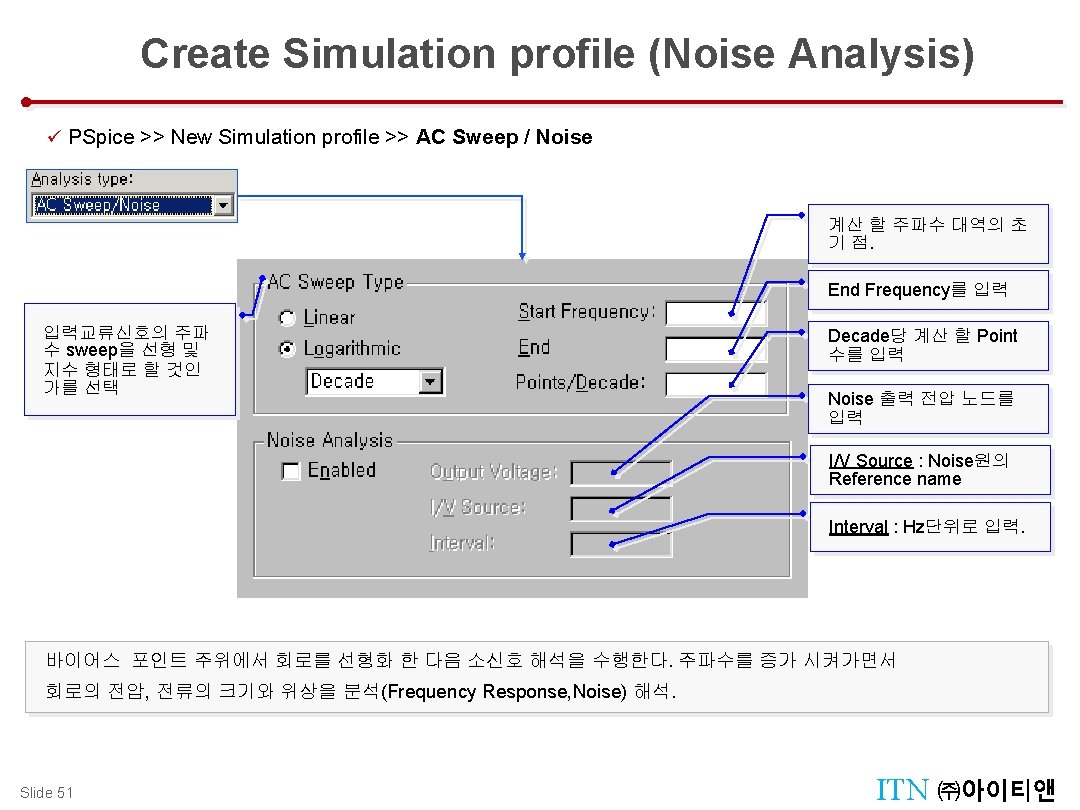

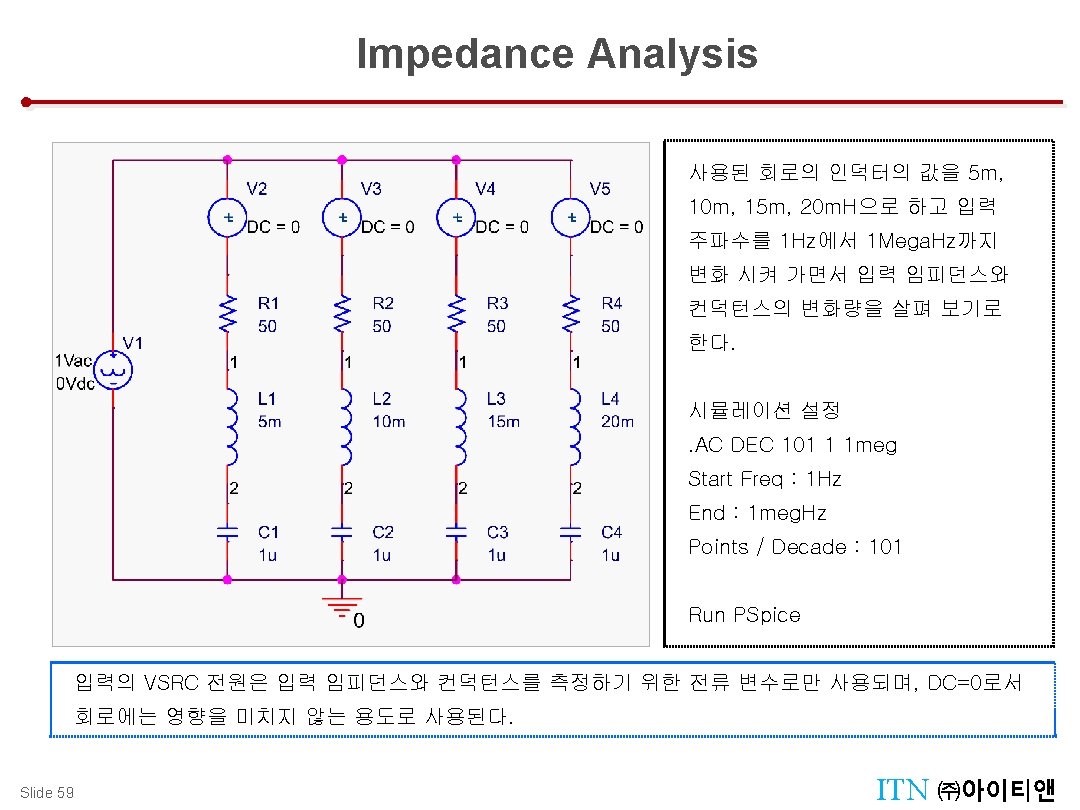

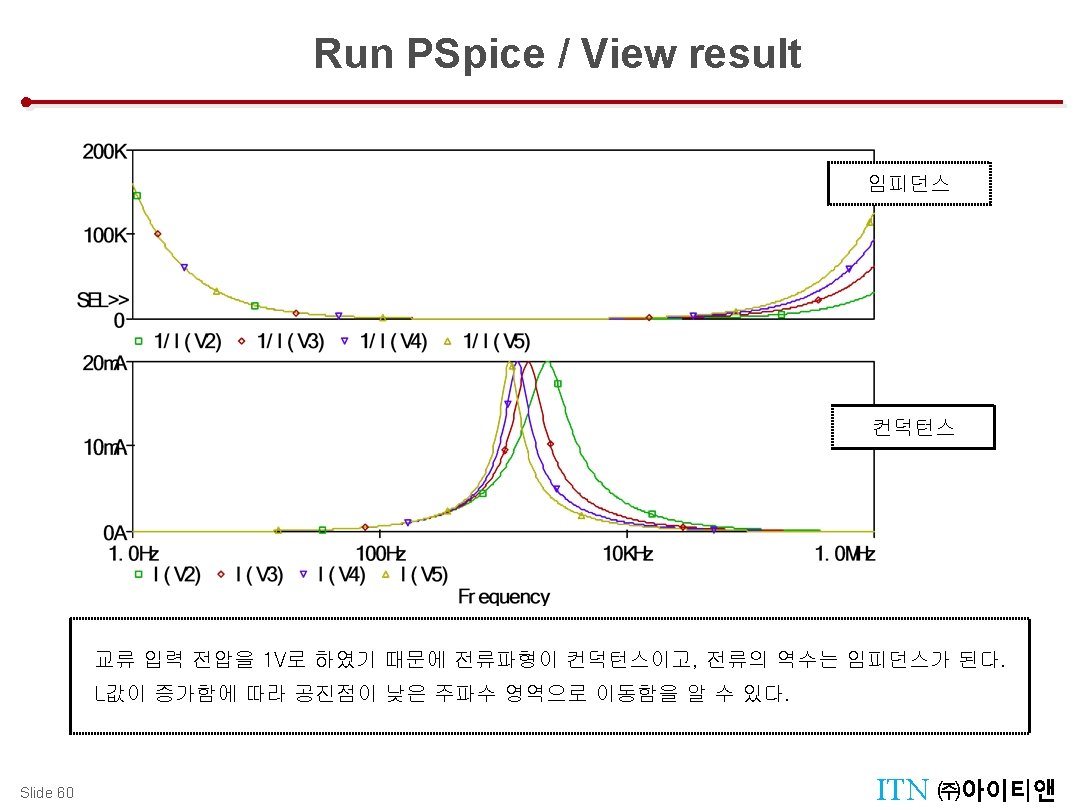

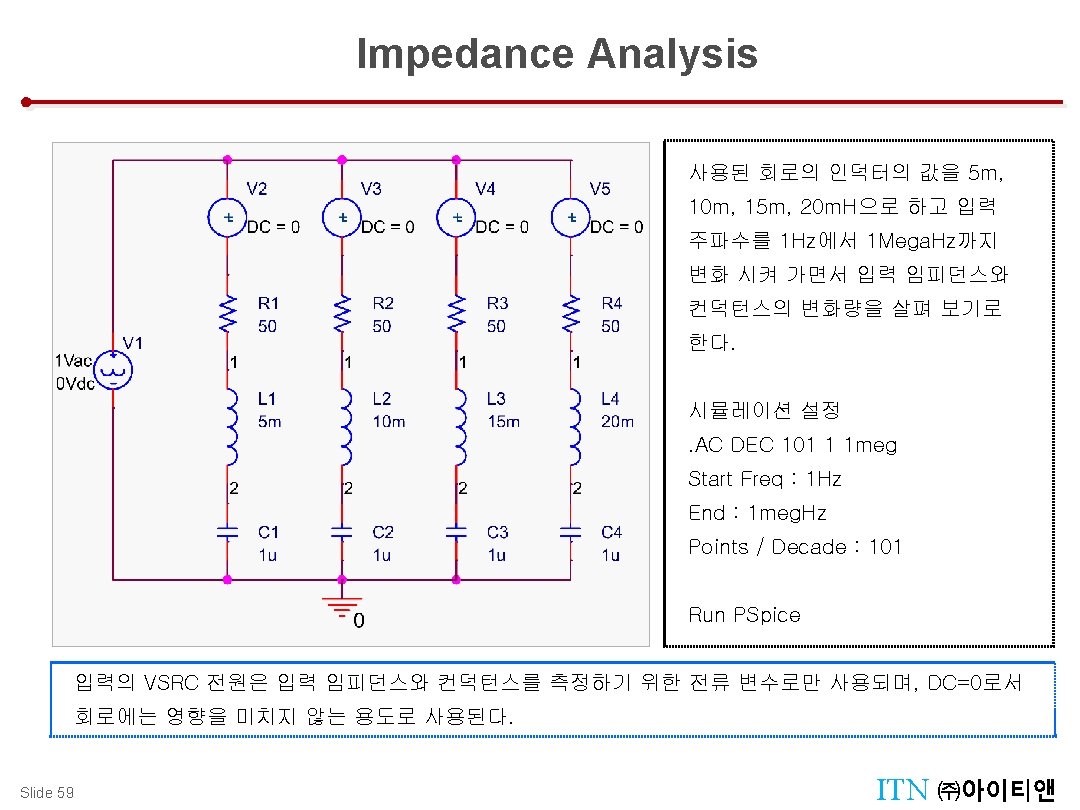

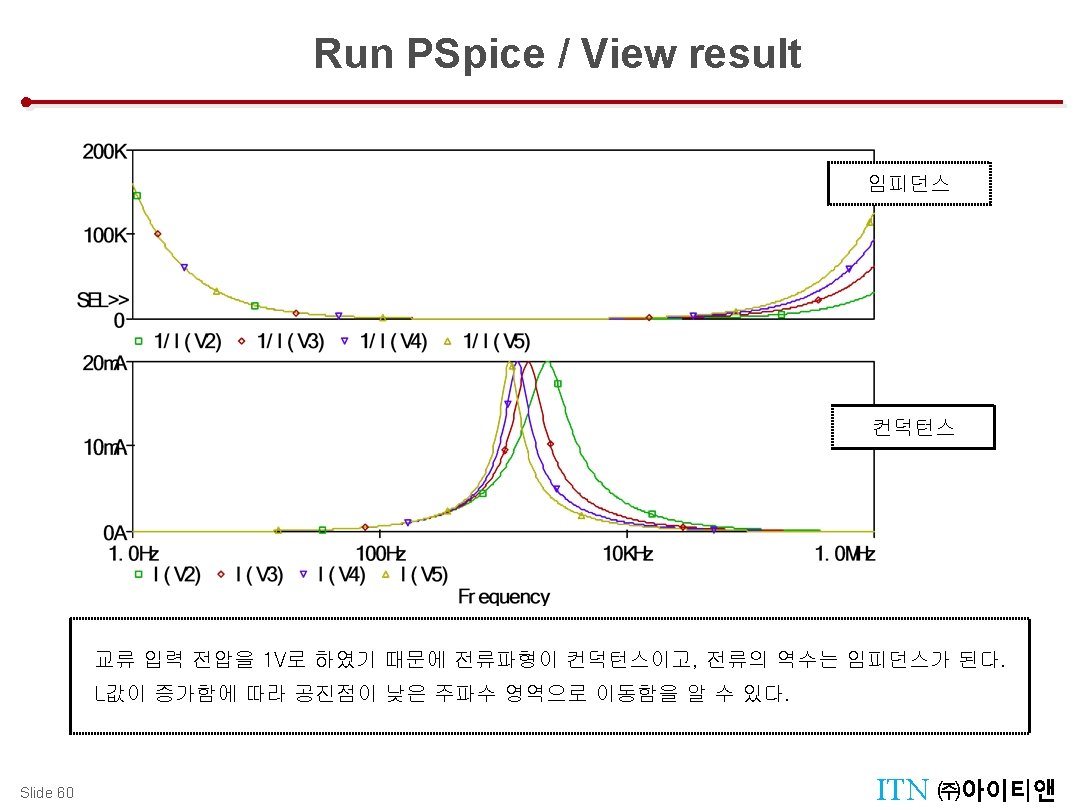

AC Sweep Analysis Design Tool Menu : Tool Palettes Design Management : Manager Tool Schematic Design (only AC Source) Create AC Simulation profile (Noise analysis) Use advanced markers / Run PSpice View result ; use toggle cursor Use measurement result View result 1 (Noise Analysis) View result 2 (Noise Analysis) Trace Expression Probe Window Impedance Analysis Run PSpice & View result Slide 49 ITN ㈜아이티앤

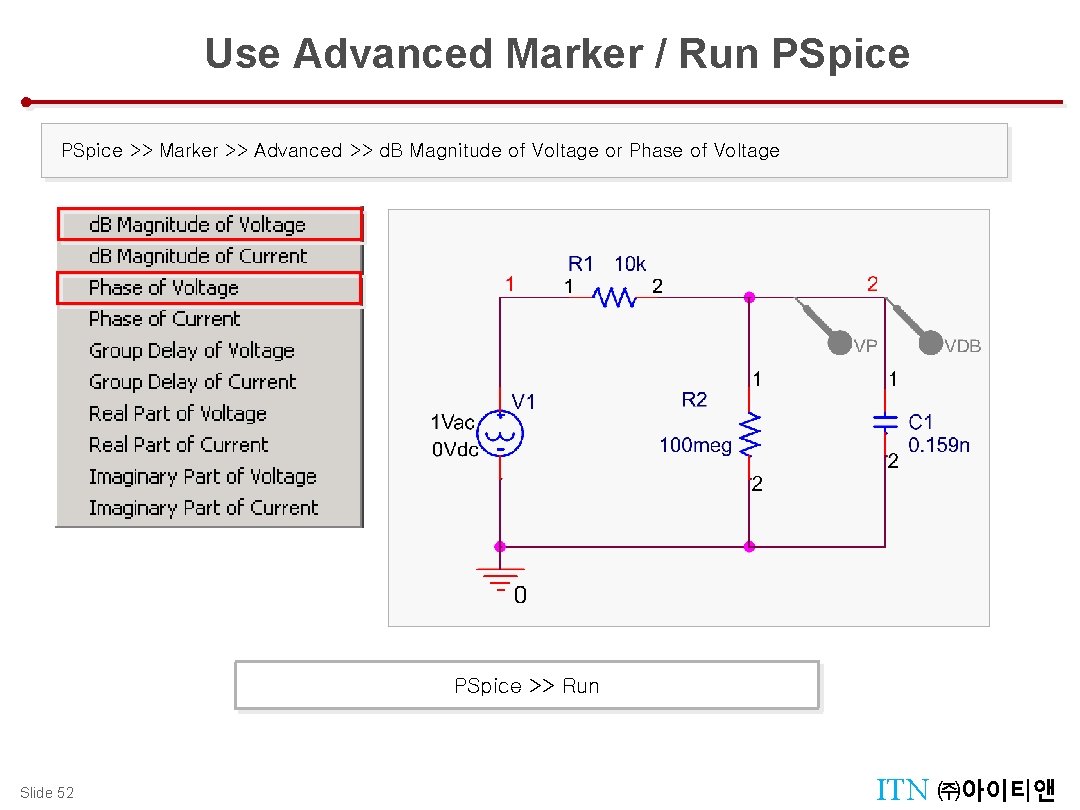

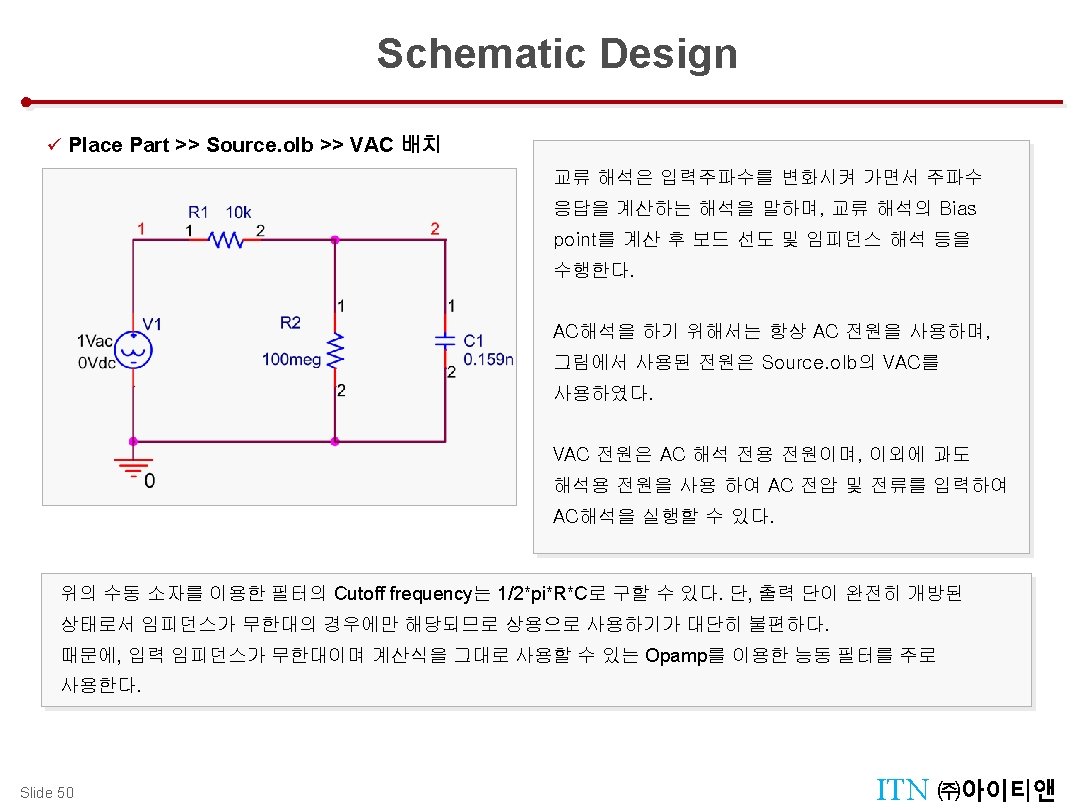

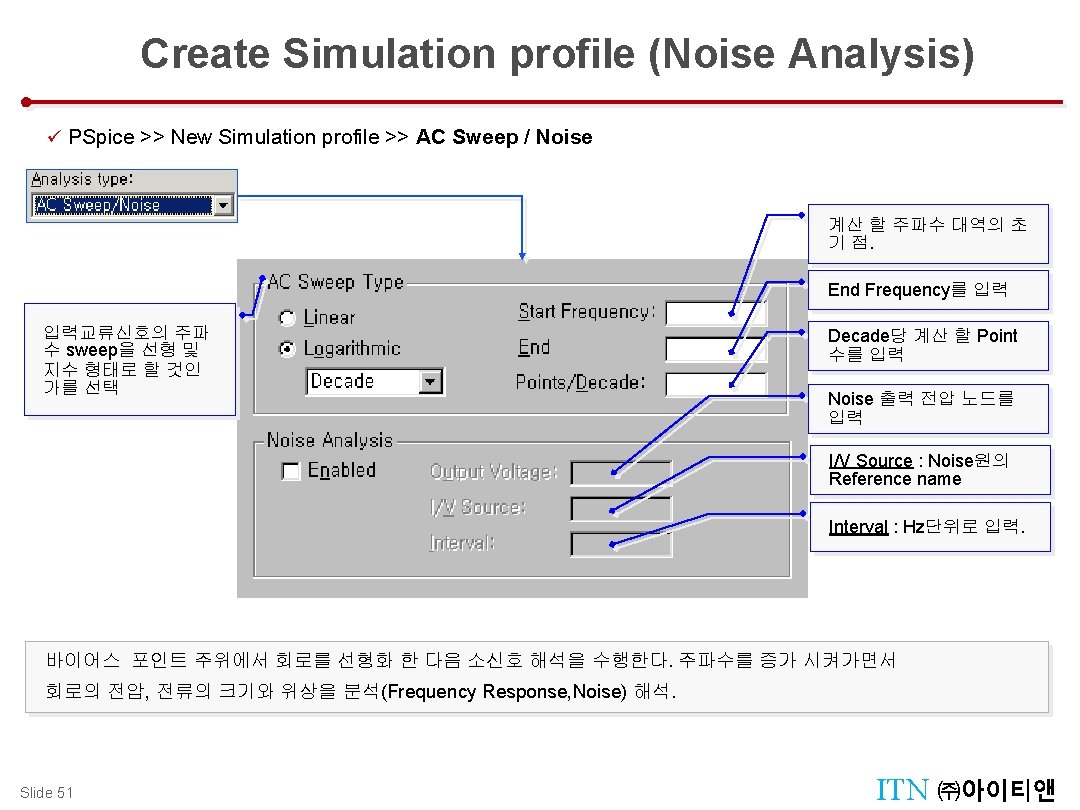

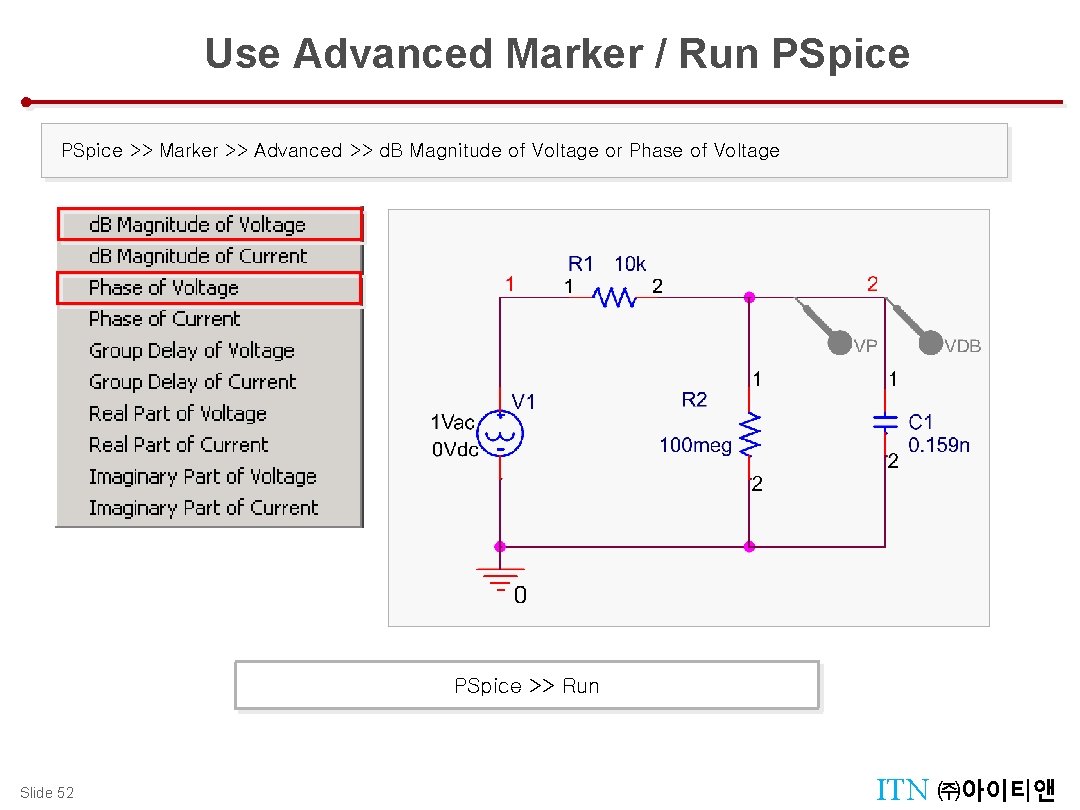

Use Advanced Marker / Run PSpice >> Marker >> Advanced >> d. B Magnitude of Voltage or Phase of Voltage PSpice >> Run Slide 52 ITN ㈜아이티앤

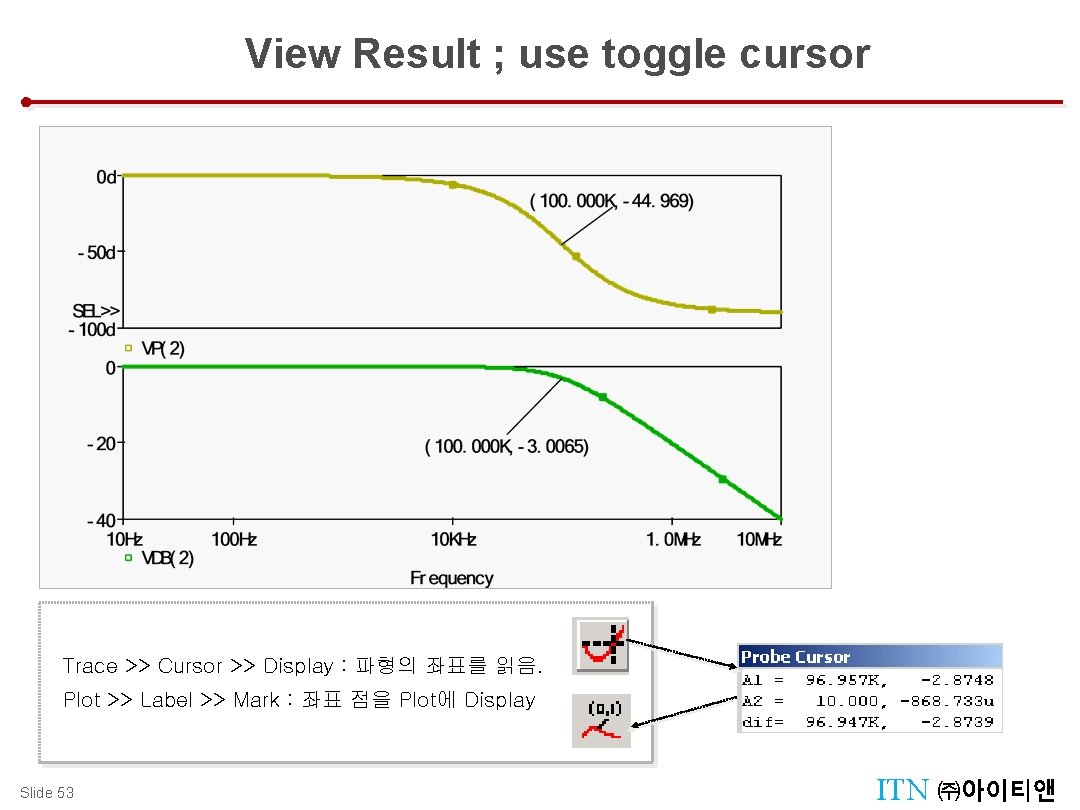

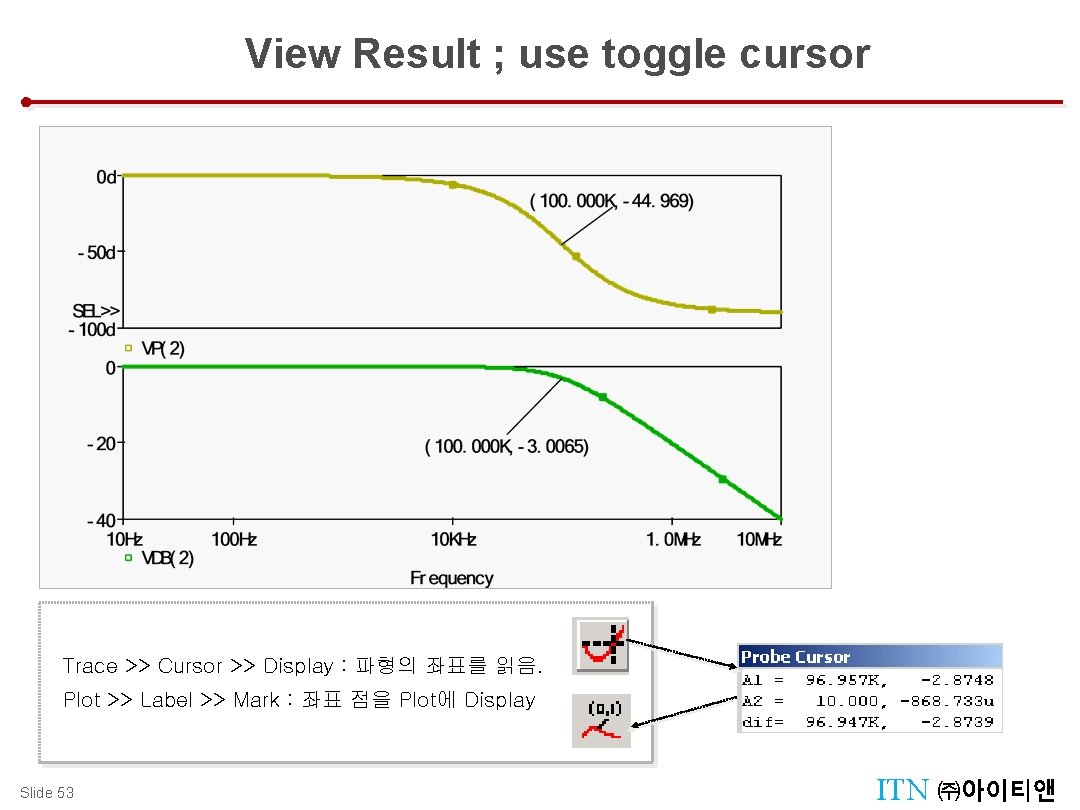

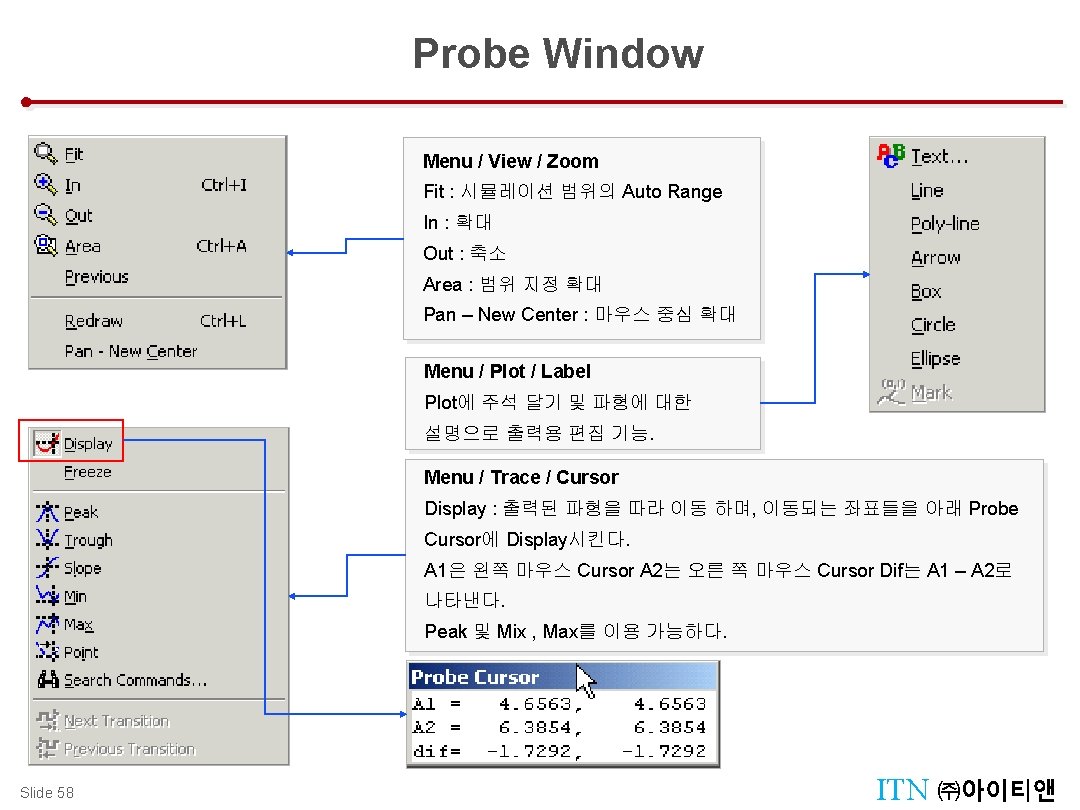

View Result ; use toggle cursor Design Management : Manager Tool Trace >> Cursor >> Display : 파형의 좌표를 읽음. Plot >> Label >> Mark : 좌표 점을 Plot에 Display Slide 53 ITN ㈜아이티앤

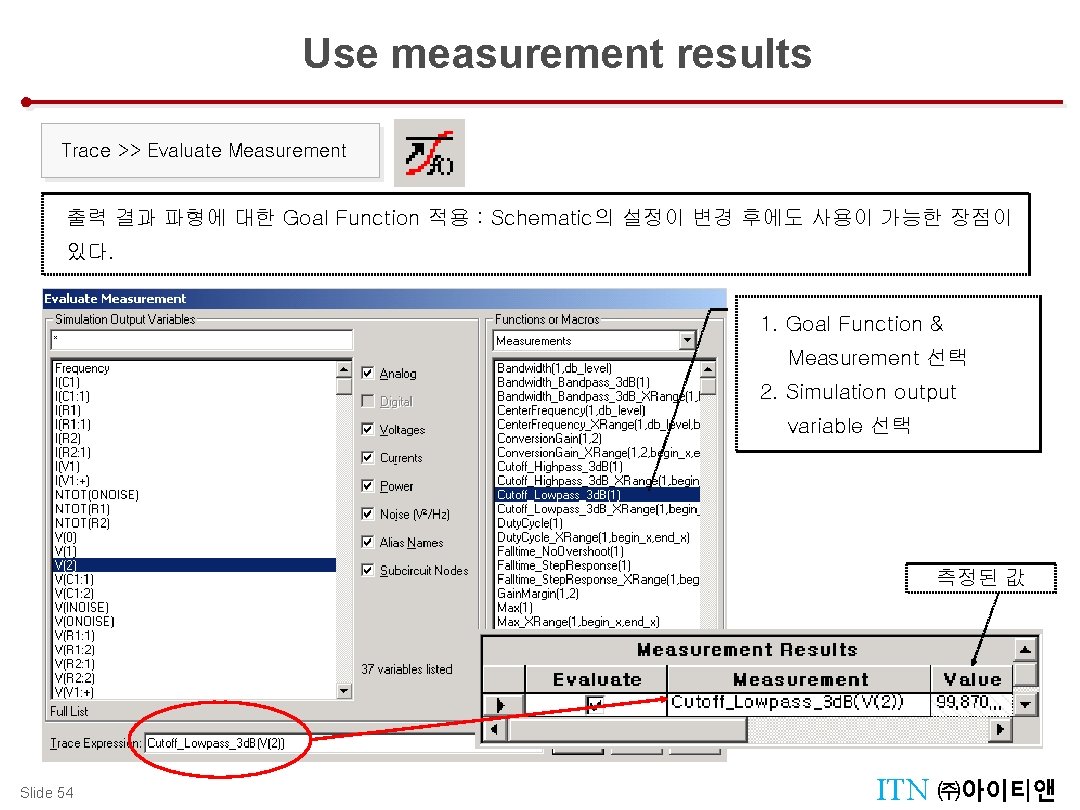

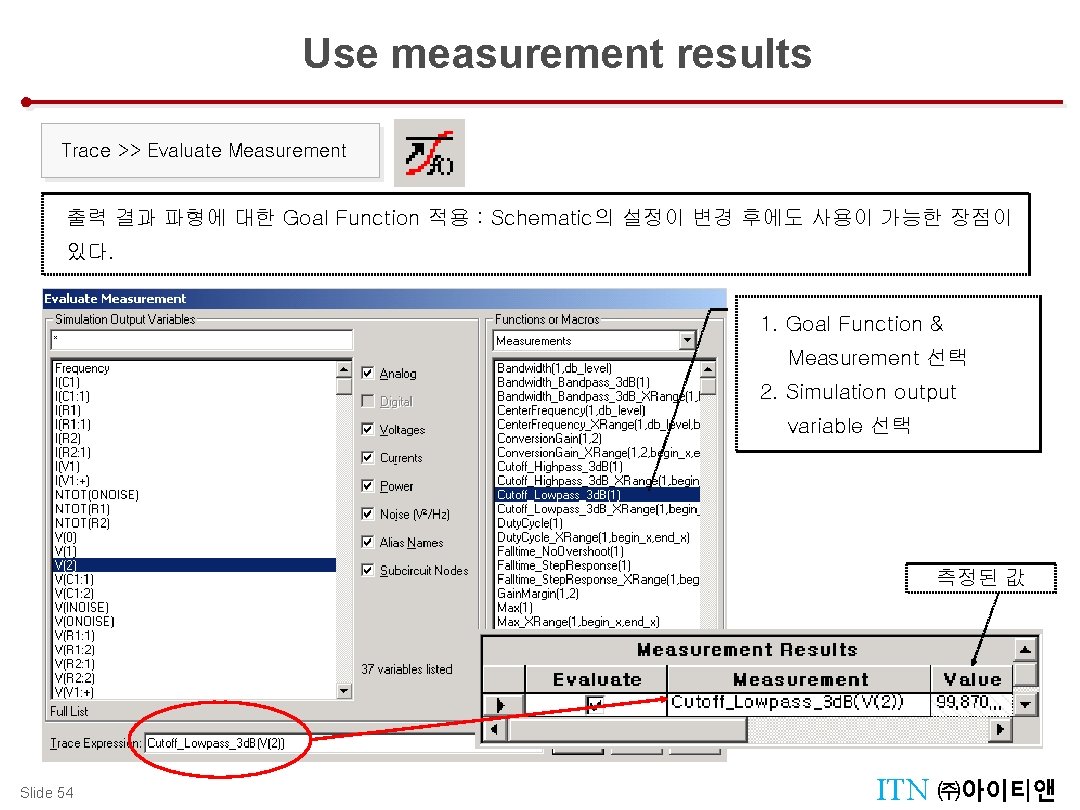

Use measurement results Design Management : Manager Tool Trace >> Evaluate Measurement 출력 결과 파형에 대한 Goal Function 적용 : Schematic의 설정이 변경 후에도 사용이 가능한 장점이 있다. 1. Goal Function & Measurement 선택 2. Simulation output variable 선택 측정된 값 Slide 54 ITN ㈜아이티앤

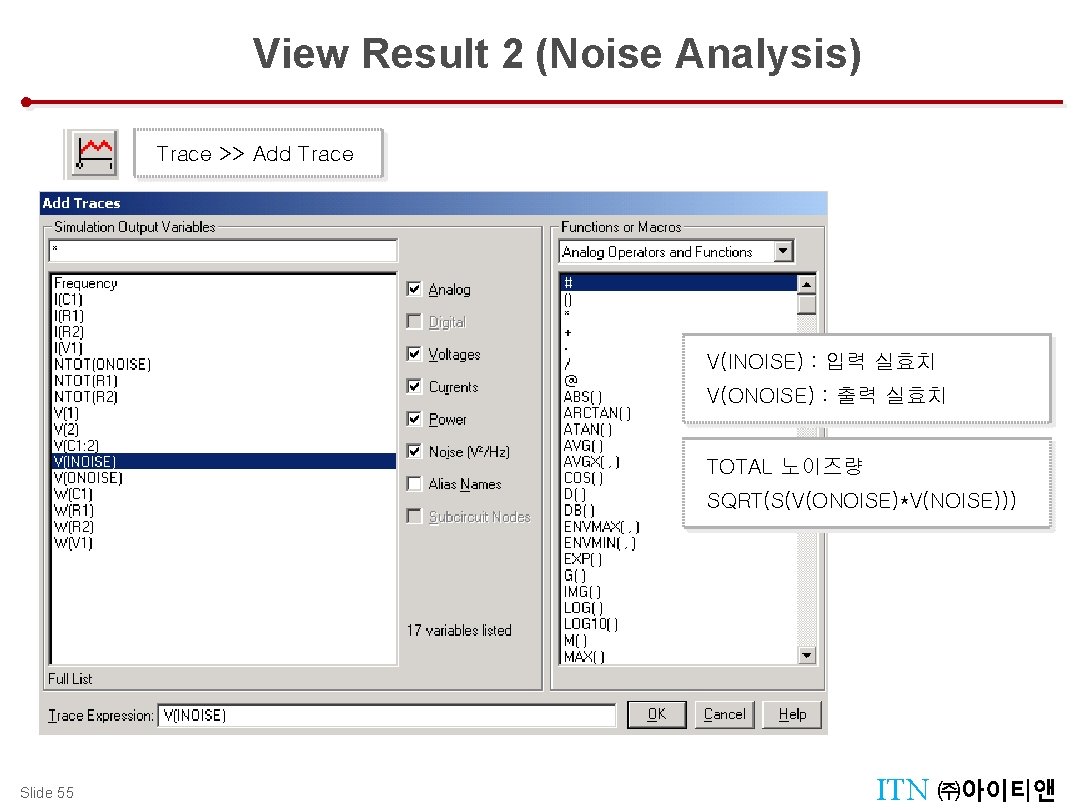

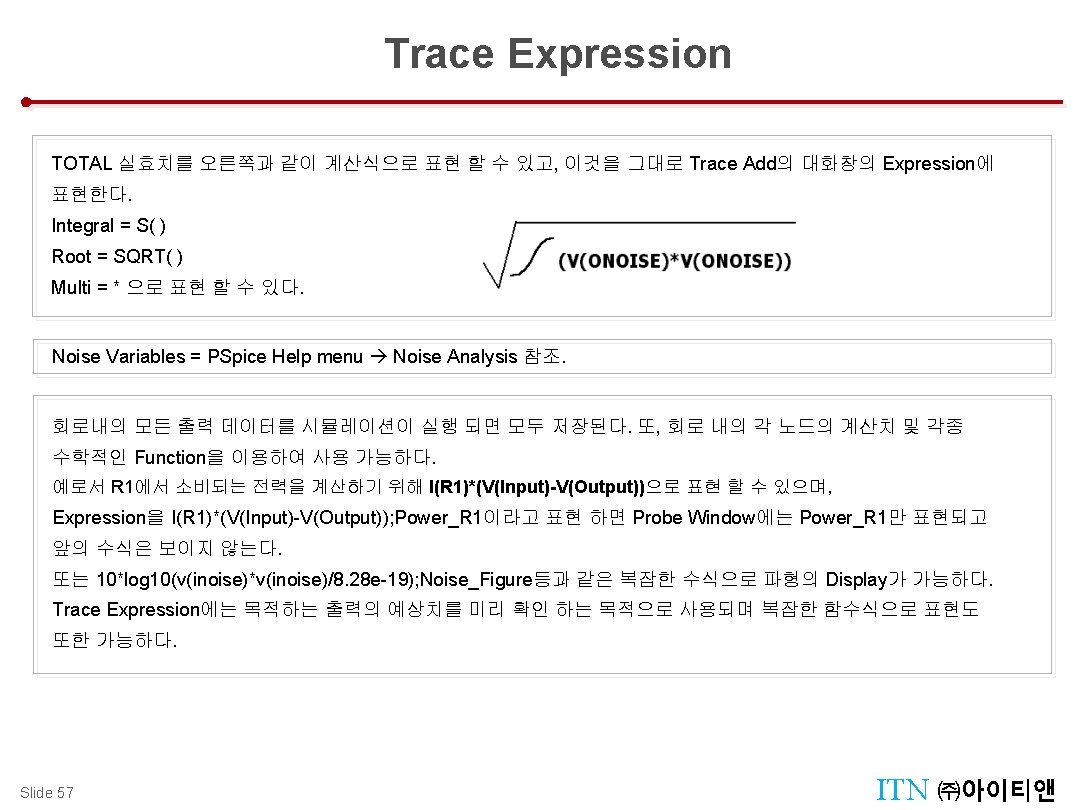

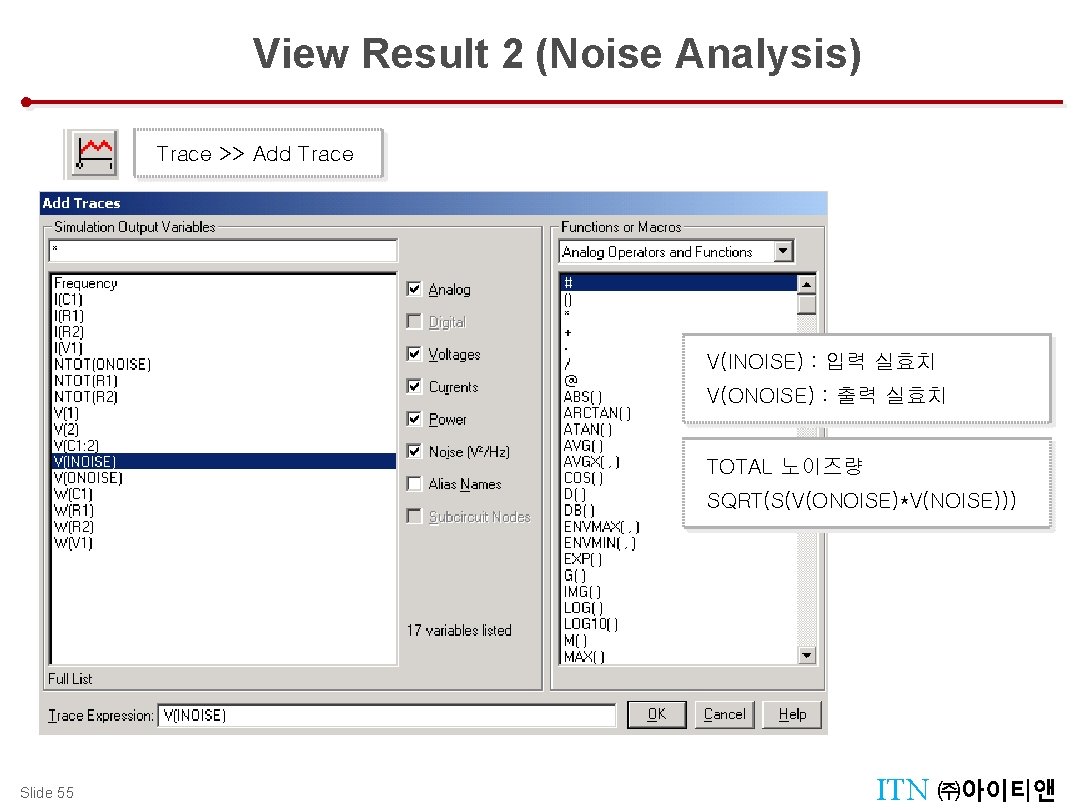

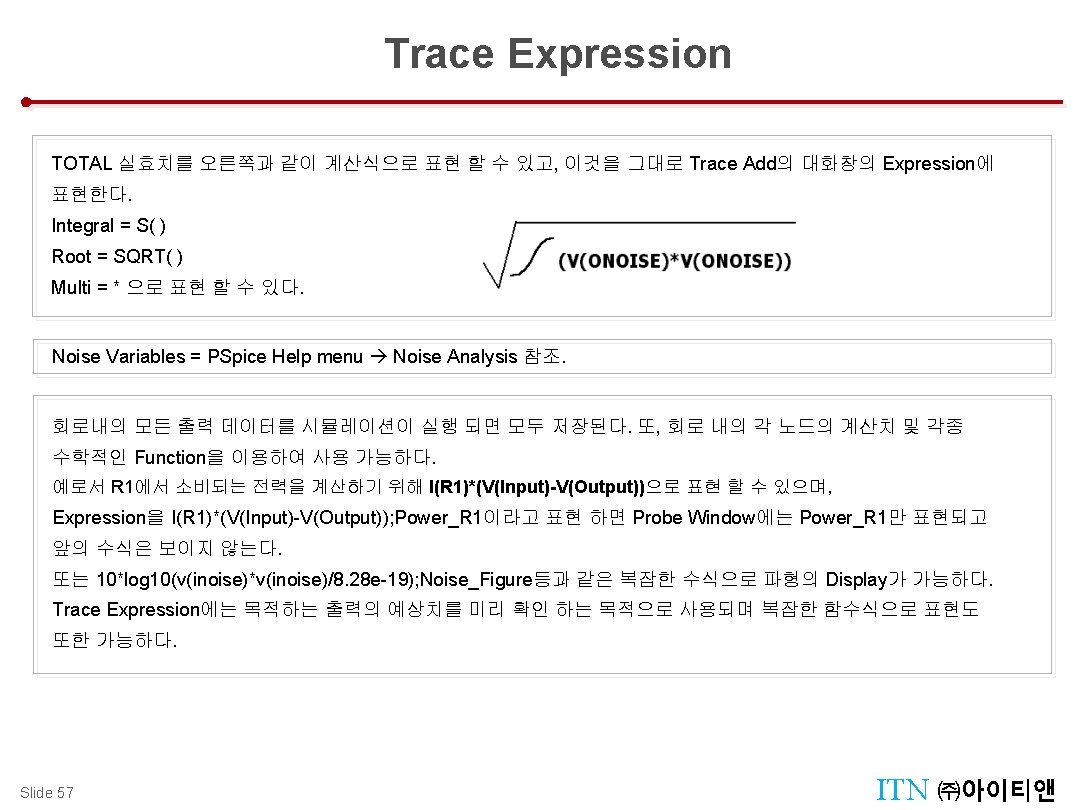

View Result 2 (Noise Analysis) Design Management : Manager Tool Trace >> Add Trace V(INOISE) : 입력 실효치 V(ONOISE) : 출력 실효치 TOTAL 노이즈량 SQRT(S(V(ONOISE)*V(NOISE))) Slide 55 ITN ㈜아이티앤

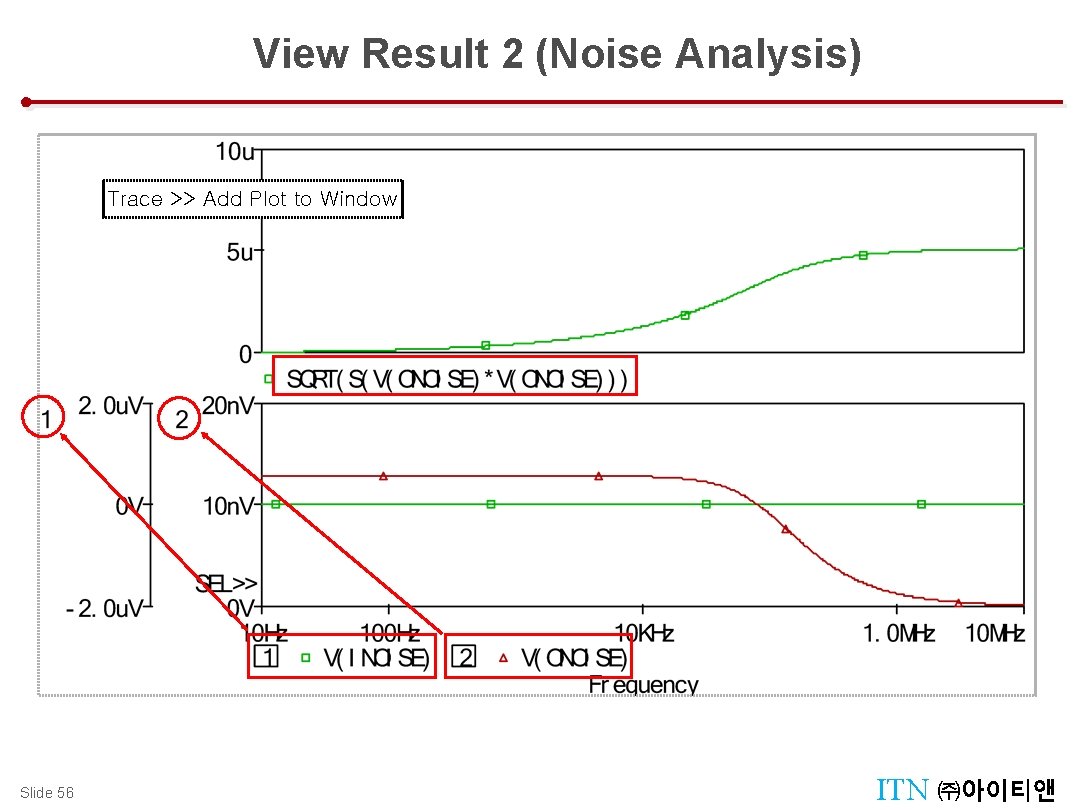

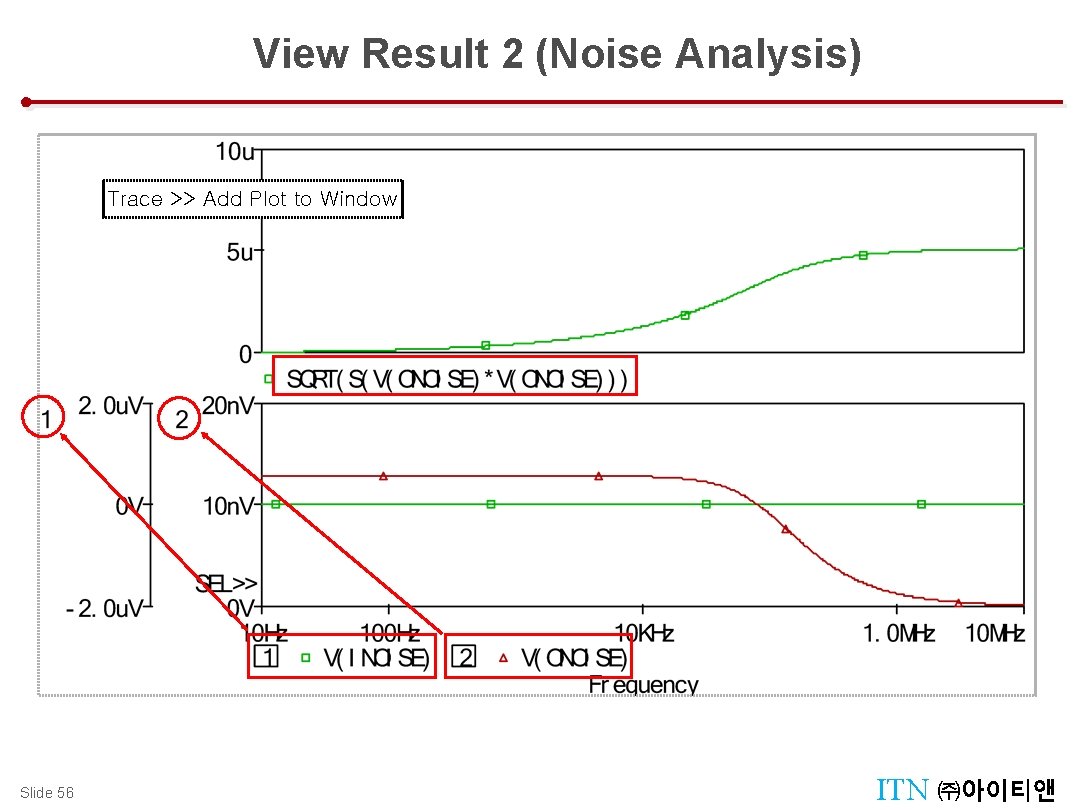

View Result 2 (Noise Analysis) Design Management : Manager Tool Trace >> Add Plot to Window Slide 56 ITN ㈜아이티앤

Simulating a Text Circuit File Design Tool Menu : Tool Palettes Design Management : Manager Tool Create a PSpice circuit file in the Text Editor. Understand the structure of a circuit file. Understand the structure of a subcircuit. Perform an analysis on a text circuit file. View the results in the Probe Window. Slide 61 ITN ㈜아이티앤

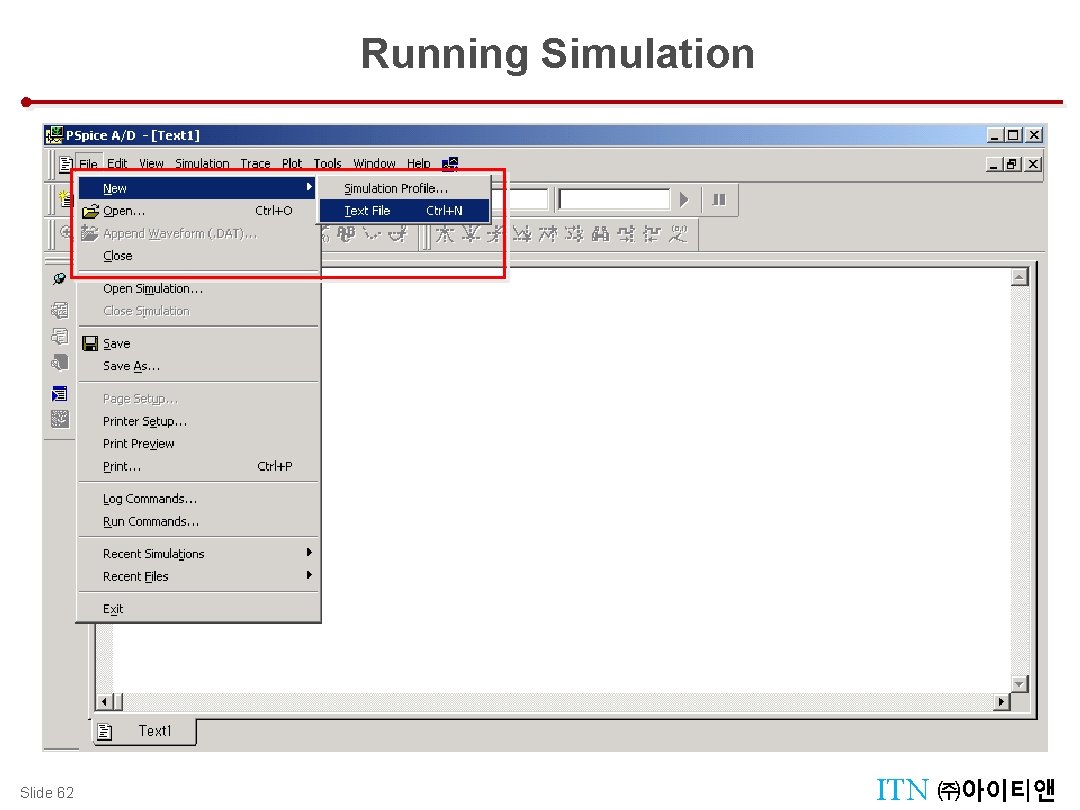

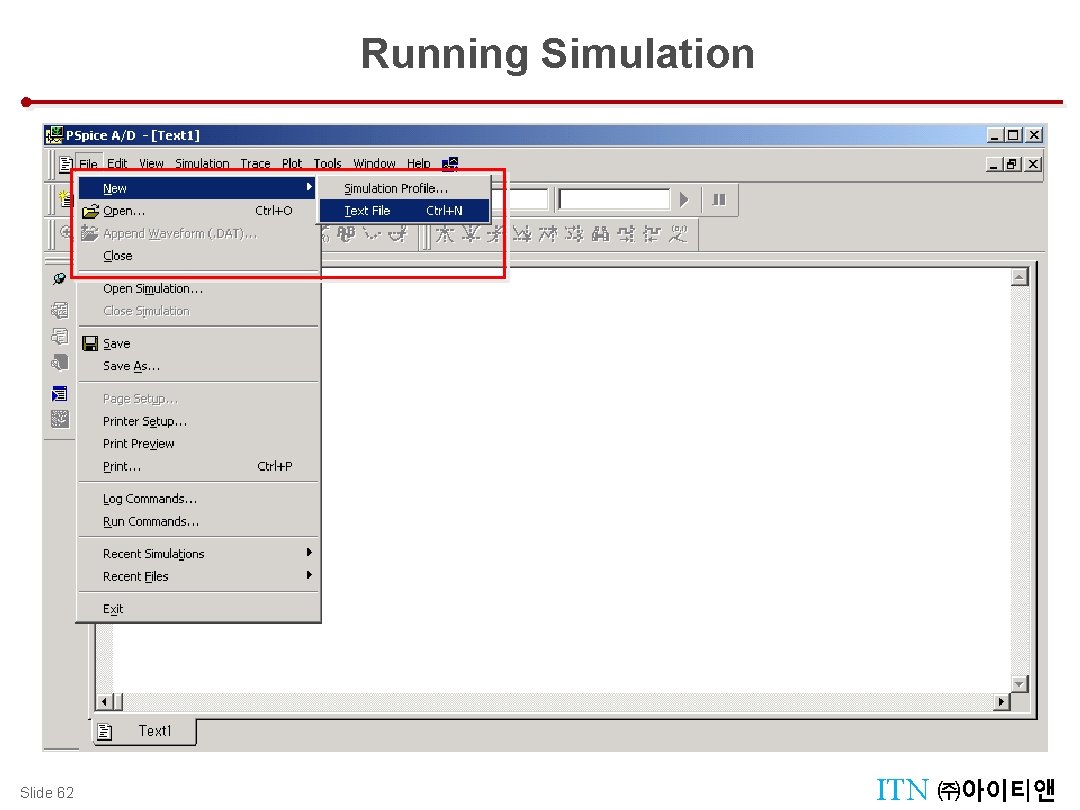

Running Simulation Design Tool Menu : Tool Palettes Design Management : Manager Tool Slide 62 ITN ㈜아이티앤

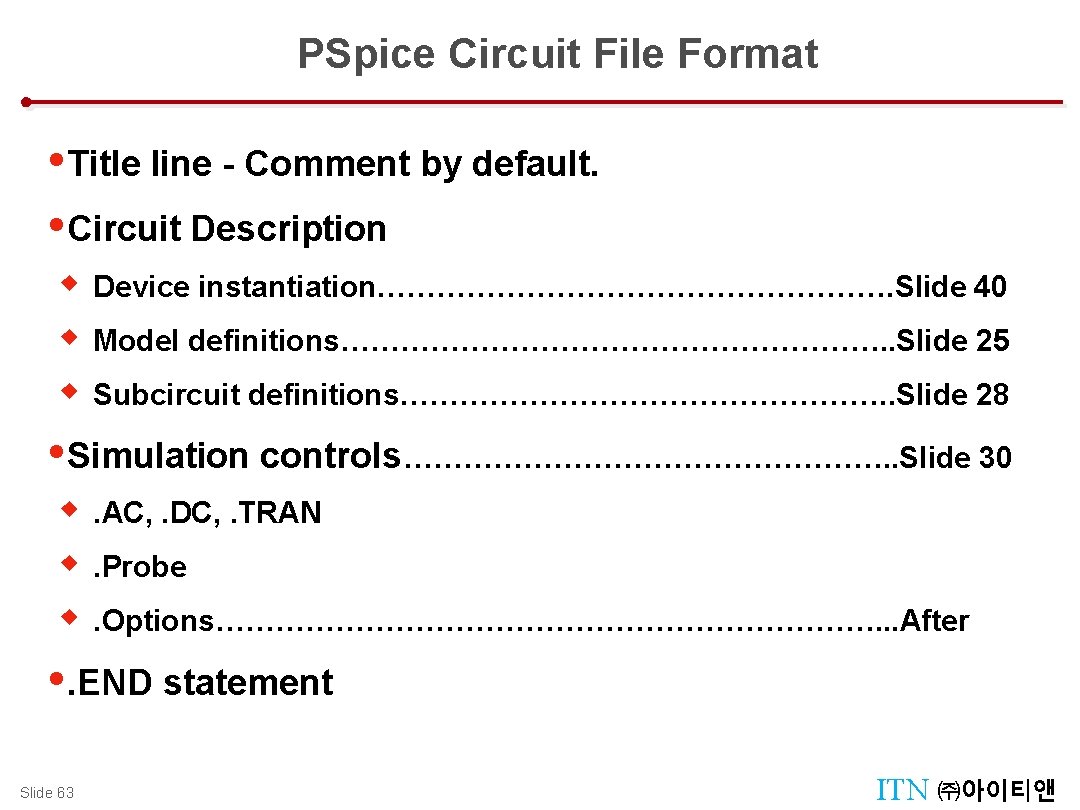

PSpice Circuit File Format Design Tool Menu : Tool Palettes Design Management : Manager Tool Title line - Comment by default. Circuit Description w w w Device instantiation………………………. Slide 40 Model definitions………………………. . Slide 25 Subcircuit definitions……………………. . Slide 28 Simulation controls……………………. . Slide 30 w w w . AC, . DC, . TRAN. Probe. Options……………………………. . . After . END statement Slide 63 ITN ㈜아이티앤

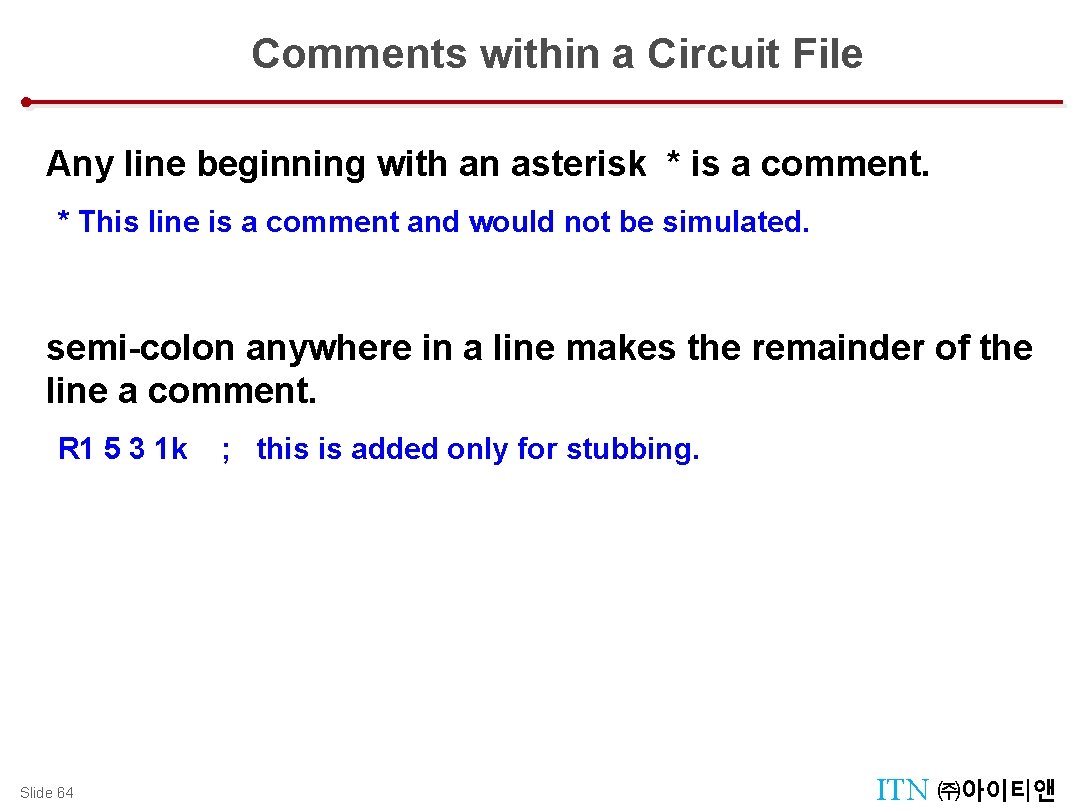

Comments within a Circuit File Design Tool Menu : Tool Palettes Design Management : Manager Tool Any line beginning with an asterisk * is a comment. * This line is a comment and would not be simulated. semi-colon anywhere in a line makes the remainder of the line a comment. R 1 5 3 1 k Slide 64 ; this is added only for stubbing. ITN ㈜아이티앤

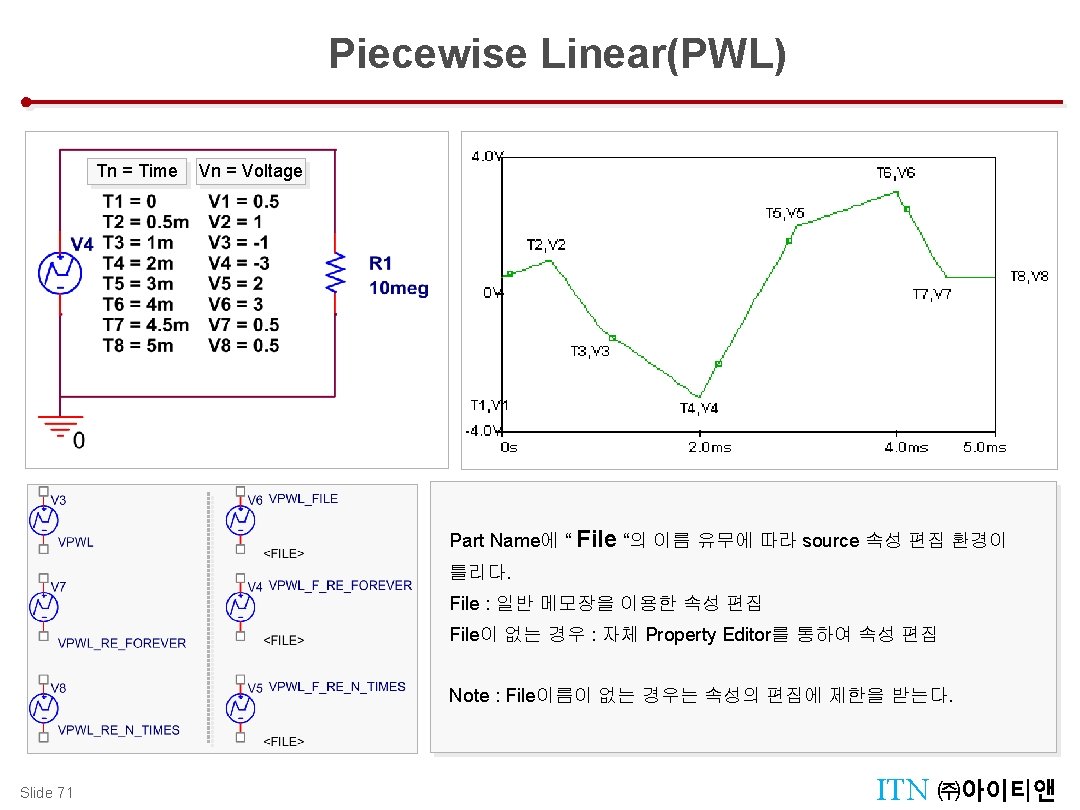

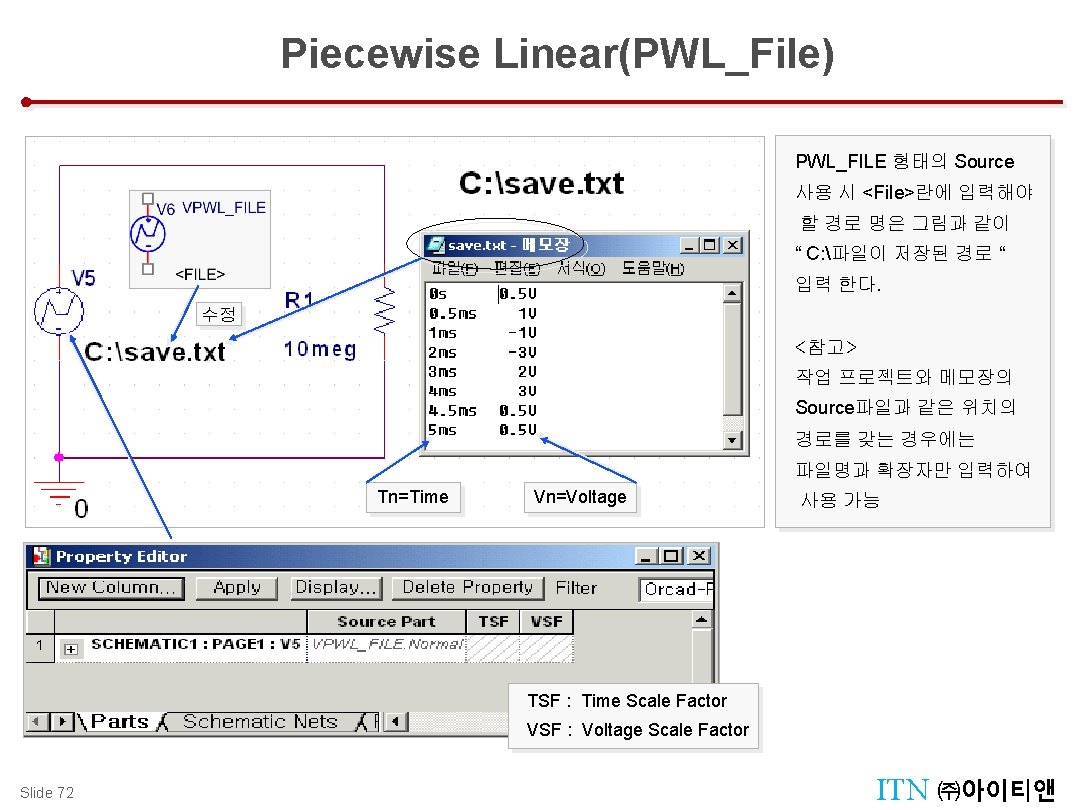

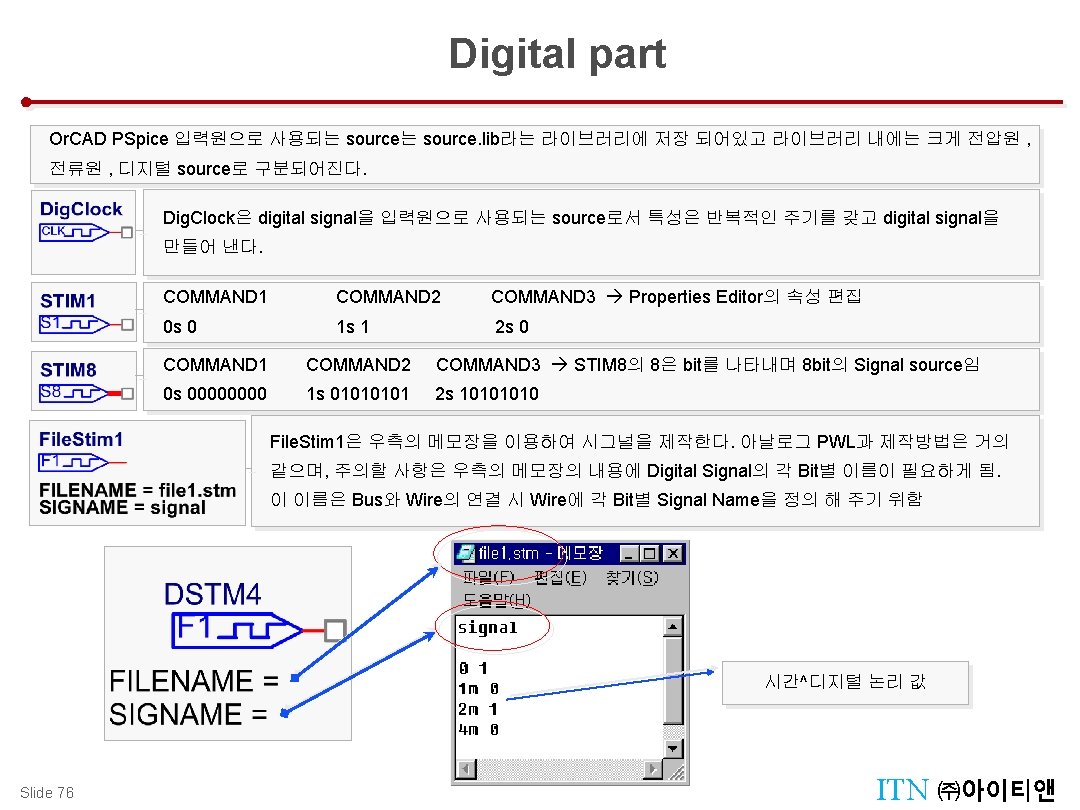

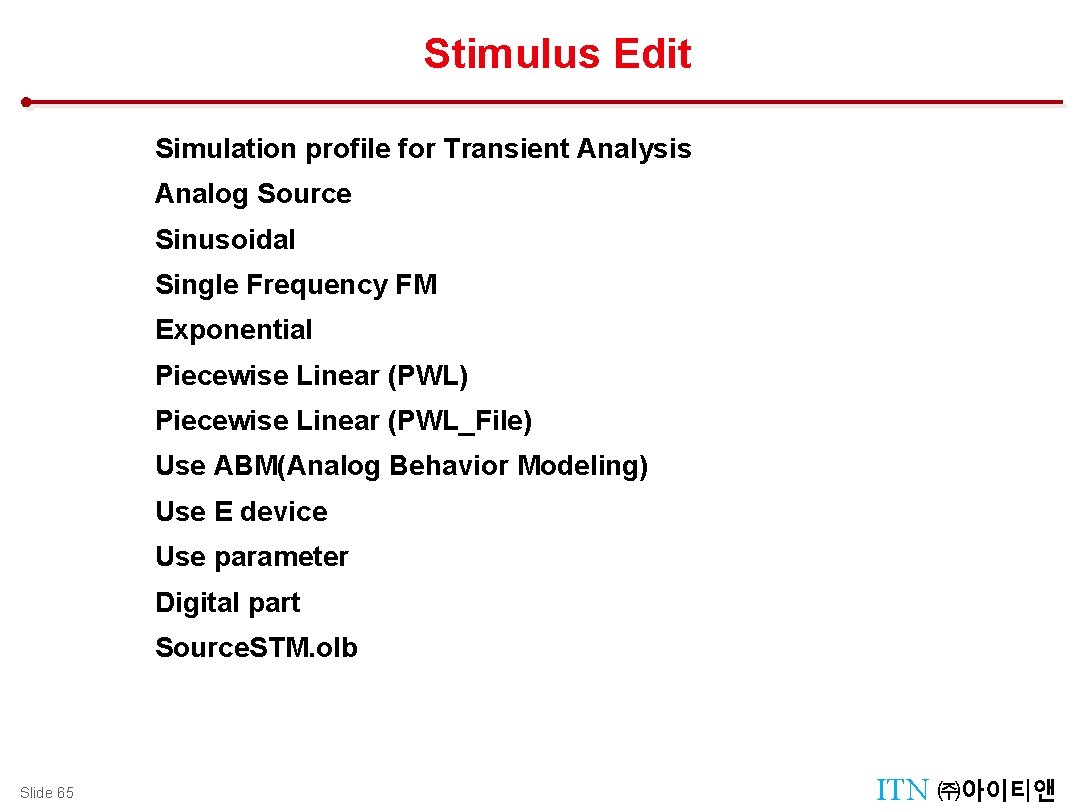

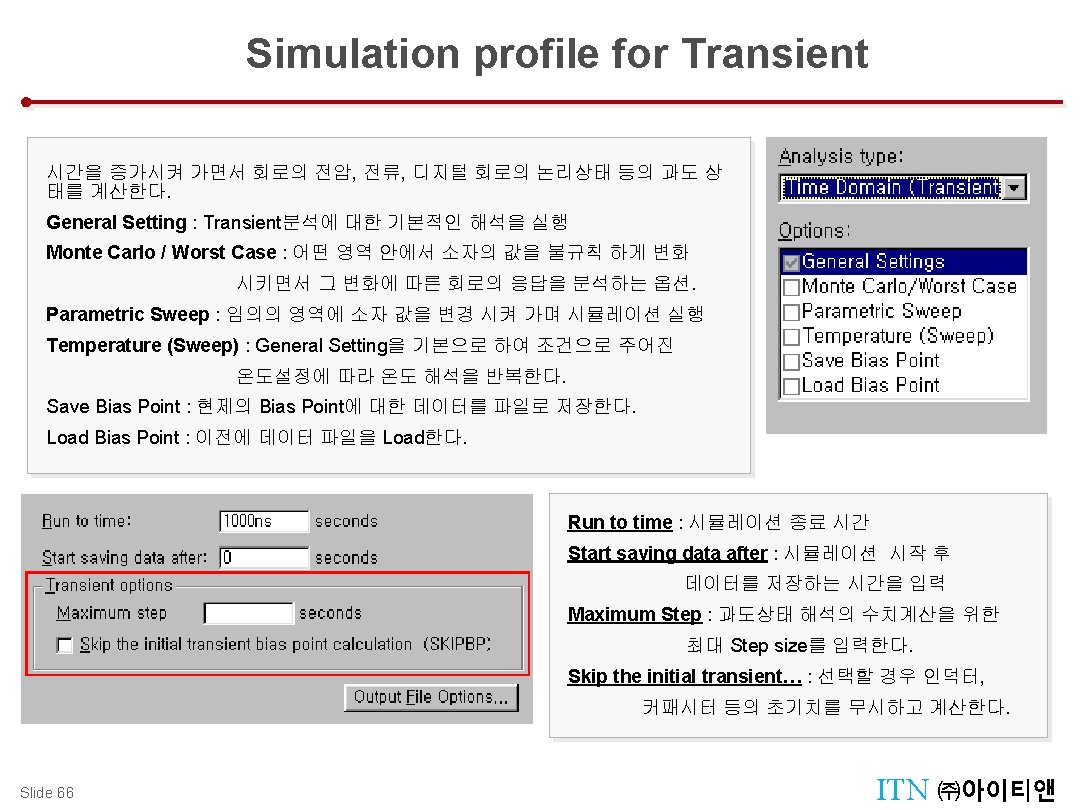

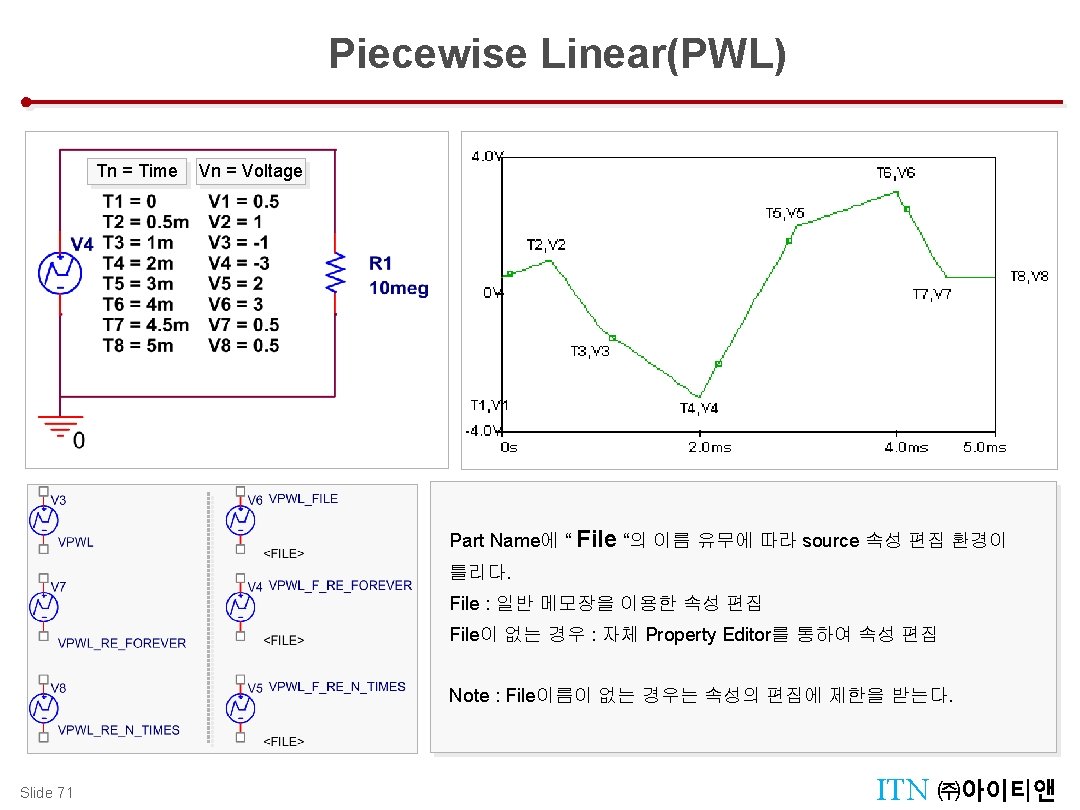

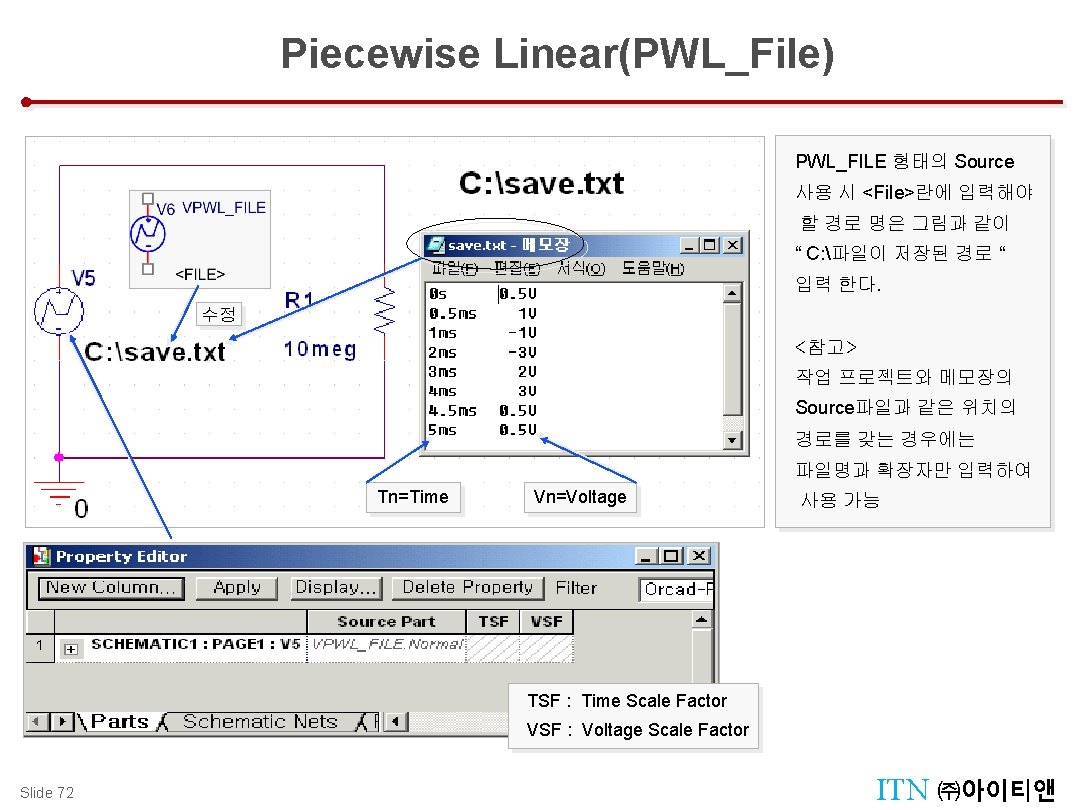

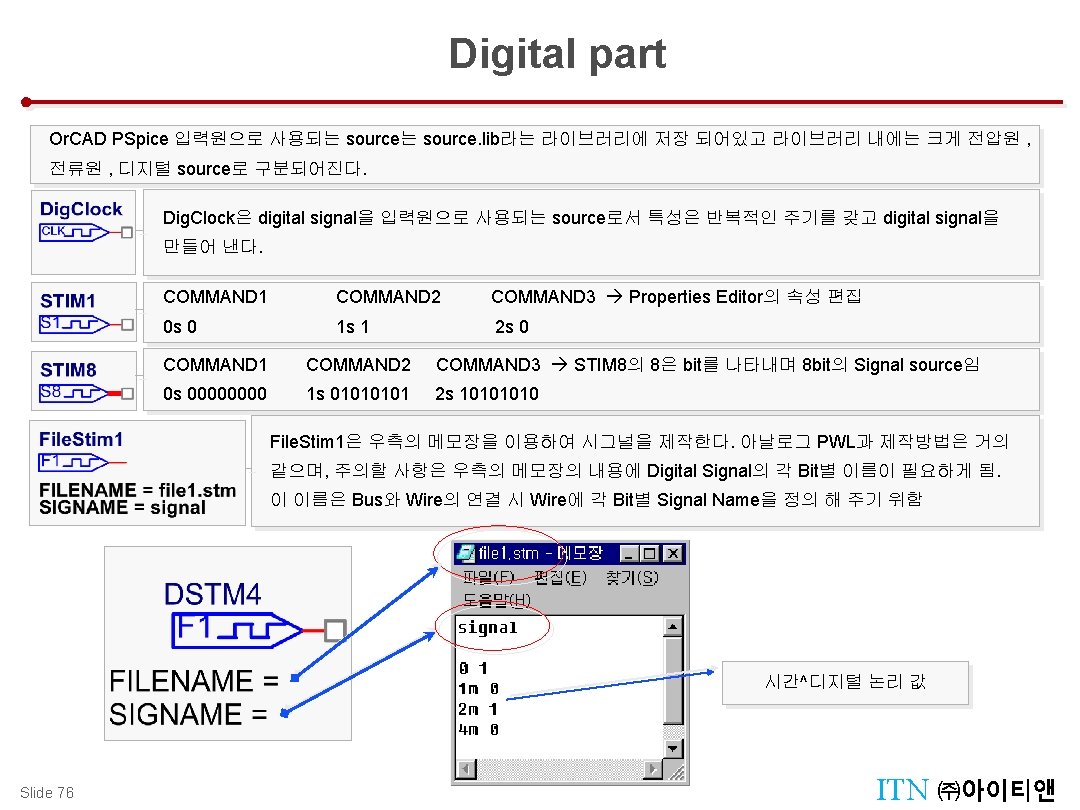

Design Management : Manager Tool Stimulus Edit Simulation profile for Transient Analysis Analog Source Sinusoidal Single Frequency FM Exponential Piecewise Linear (PWL) Piecewise Linear (PWL_File) Use ABM(Analog Behavior Modeling) Use E device Use parameter Digital part Source. STM. olb Slide 65 ITN ㈜아이티앤

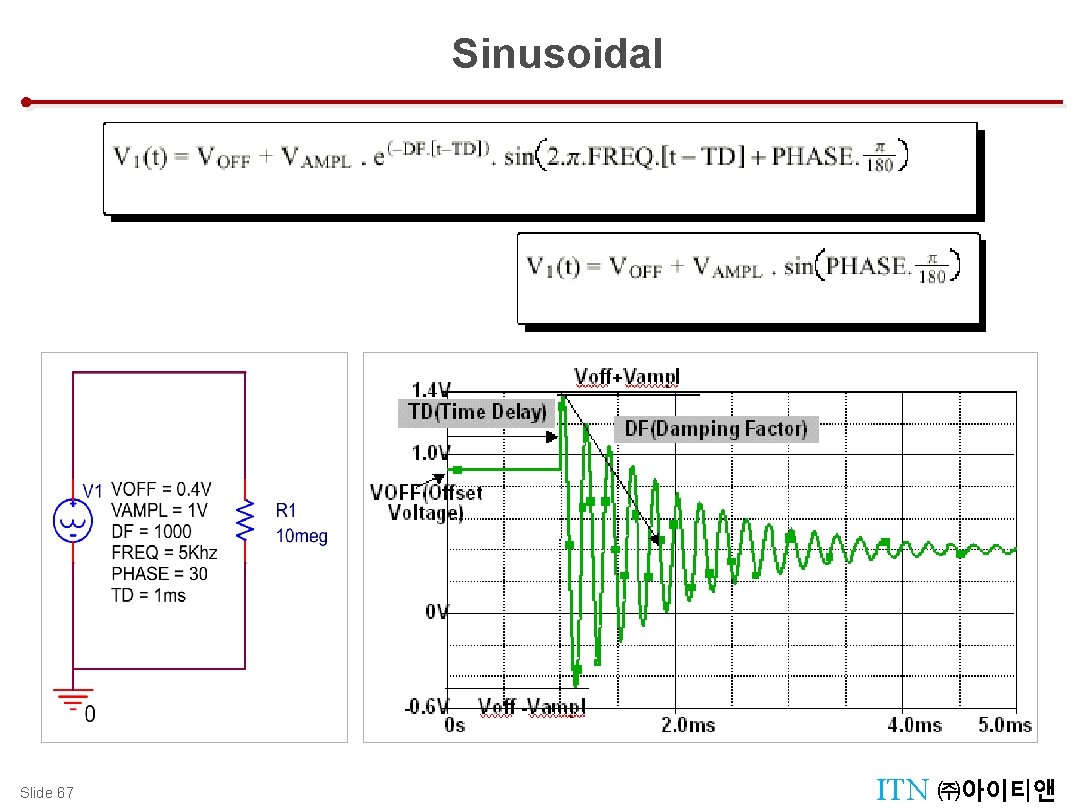

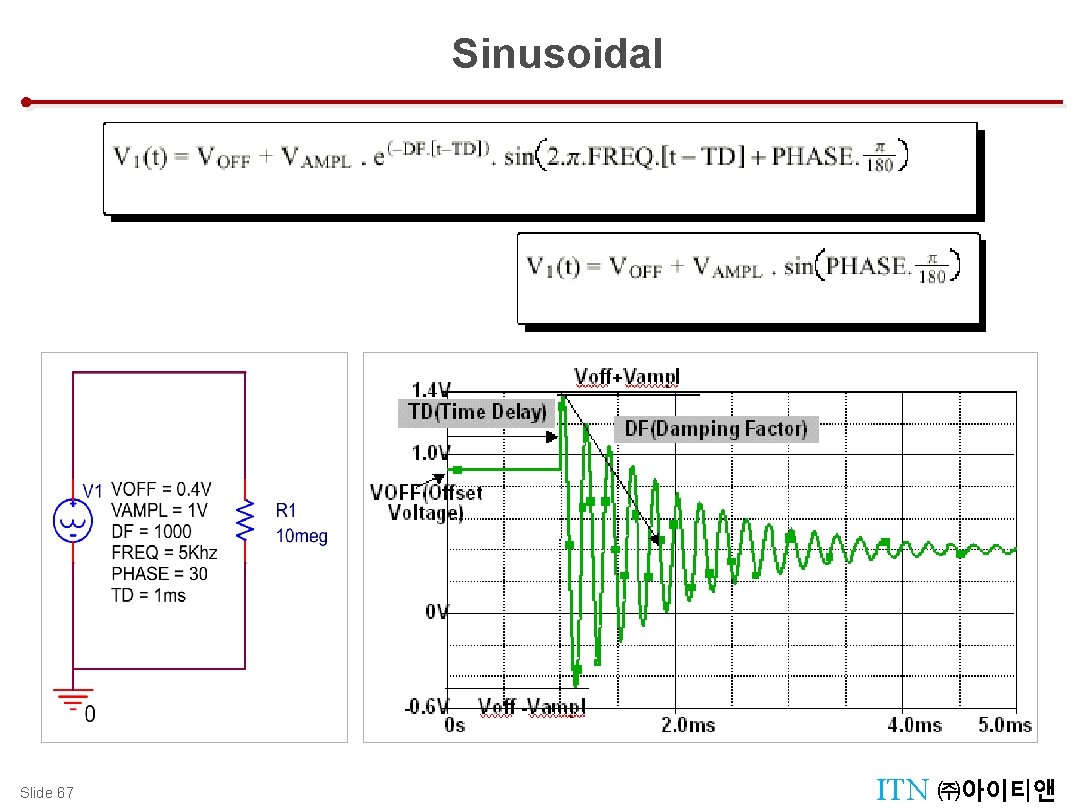

Source V I Sin Slide 67 Sinusoidal ITN ㈜아이티앤

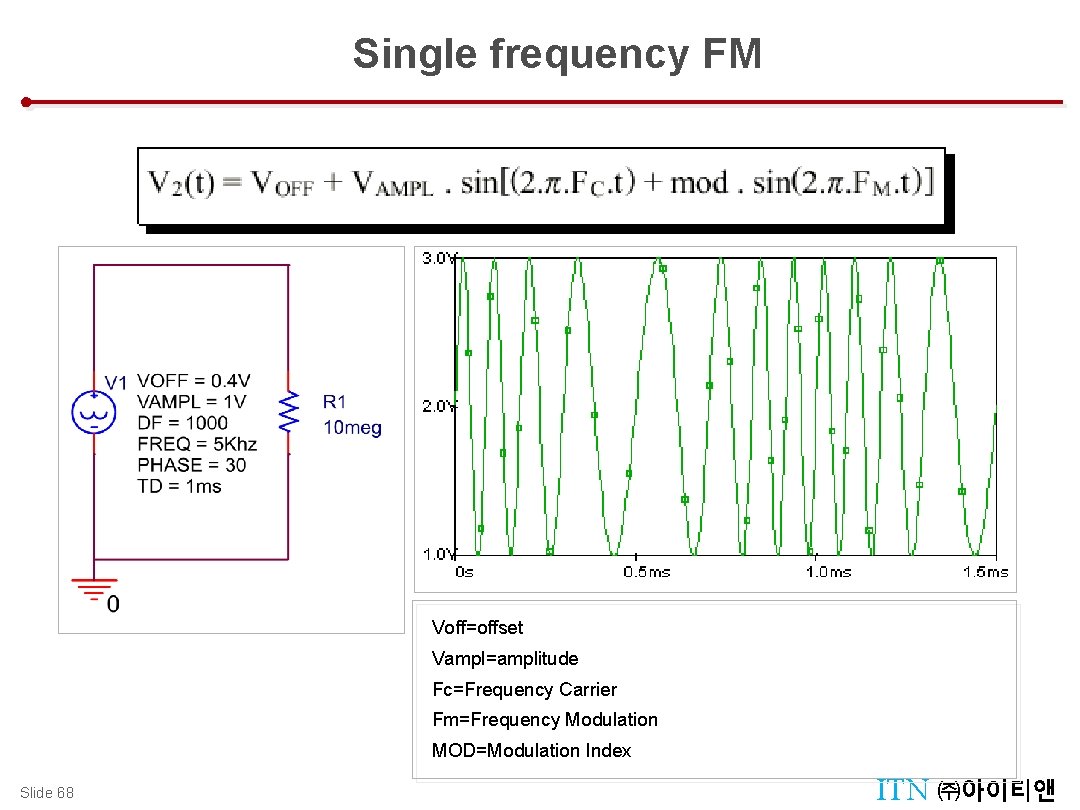

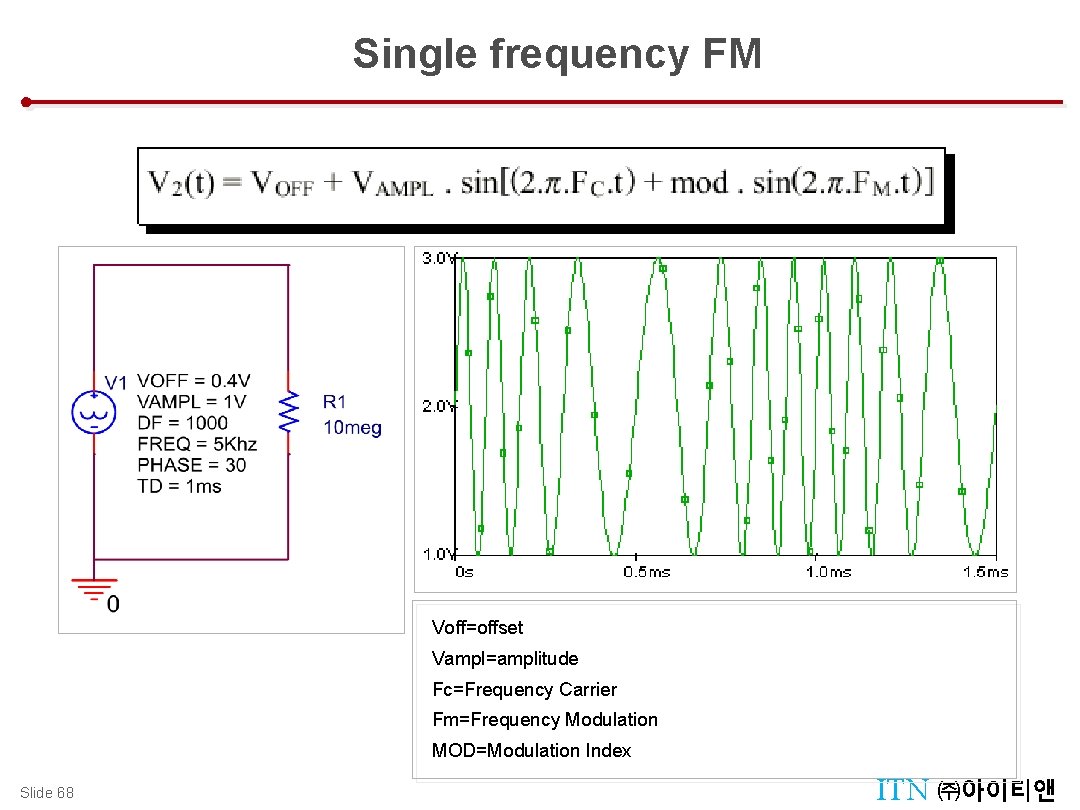

Source SFFM Single frequency FM Voff=offset Vampl=amplitude Fc=Frequency Carrier Fm=Frequency Modulation MOD=Modulation Index Slide 68 ITN ㈜아이티앤

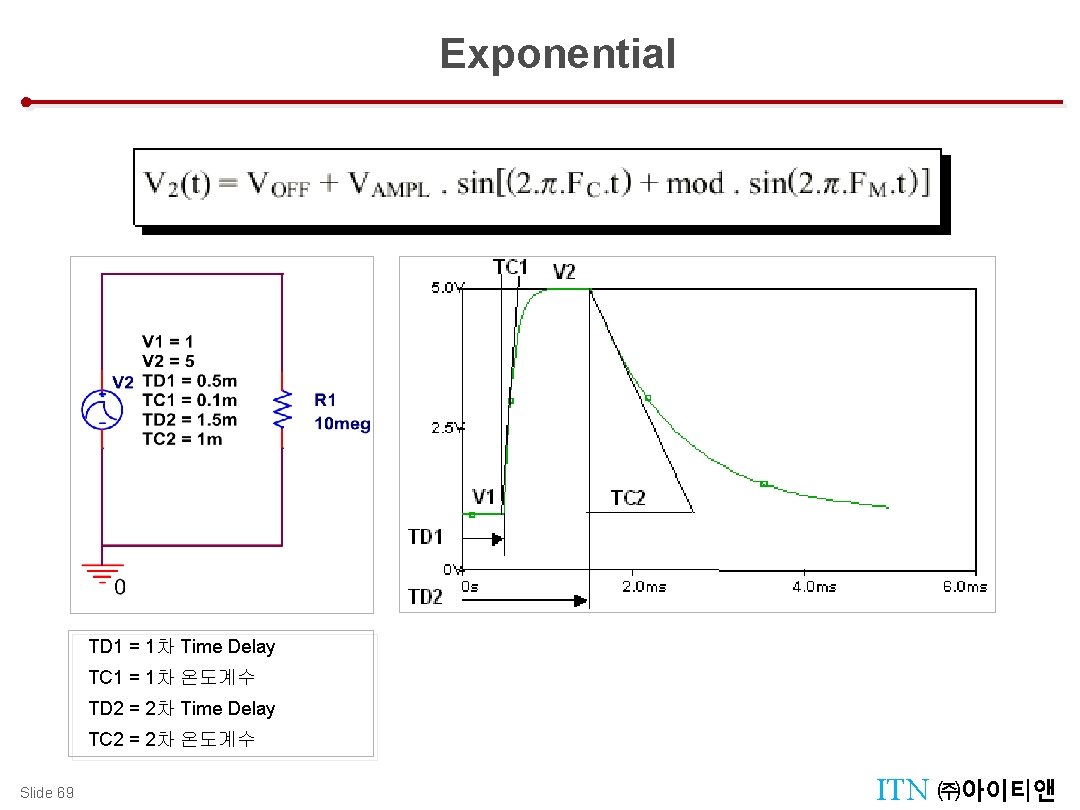

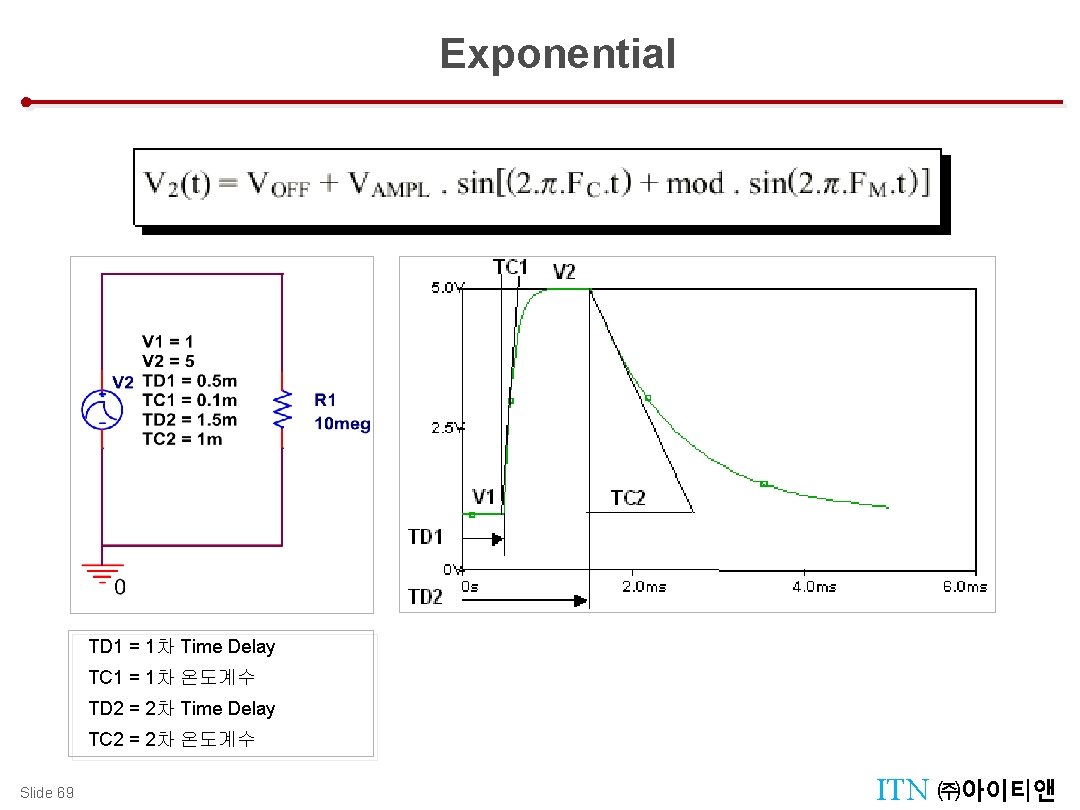

Source Exponential TD 1 = 1차 Time Delay TC 1 = 1차 온도계수 TD 2 = 2차 Time Delay TC 2 = 2차 온도계수 Slide 69 ITN ㈜아이티앤

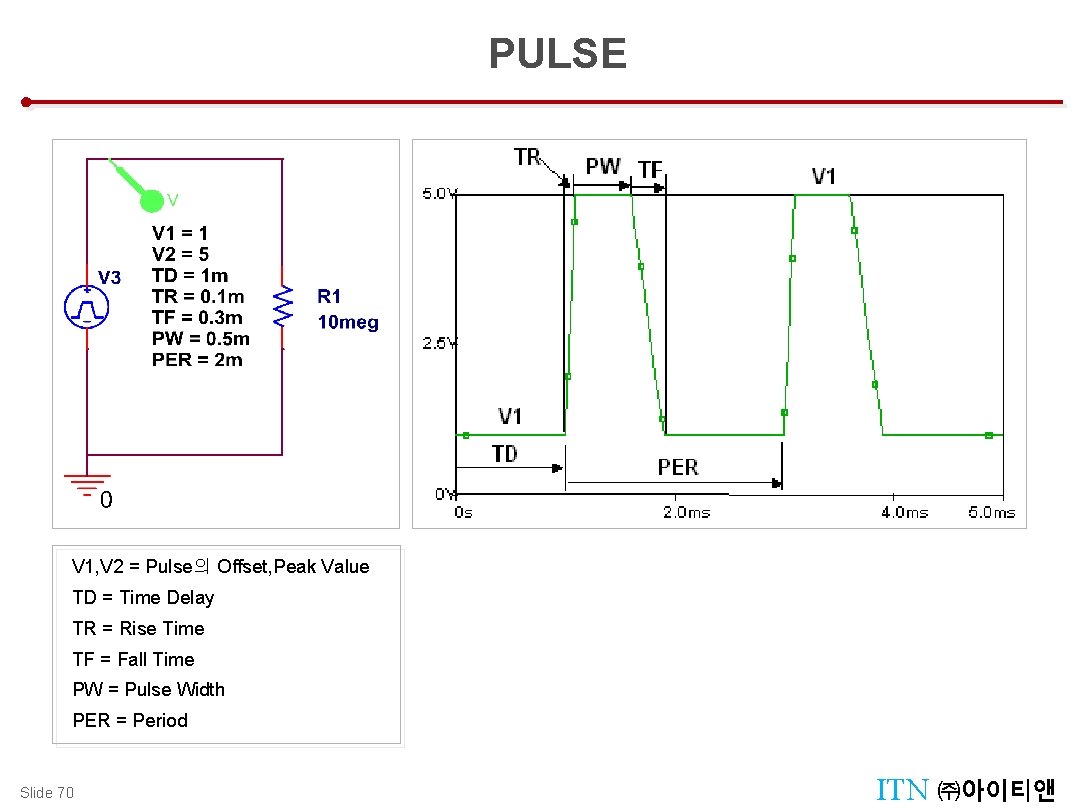

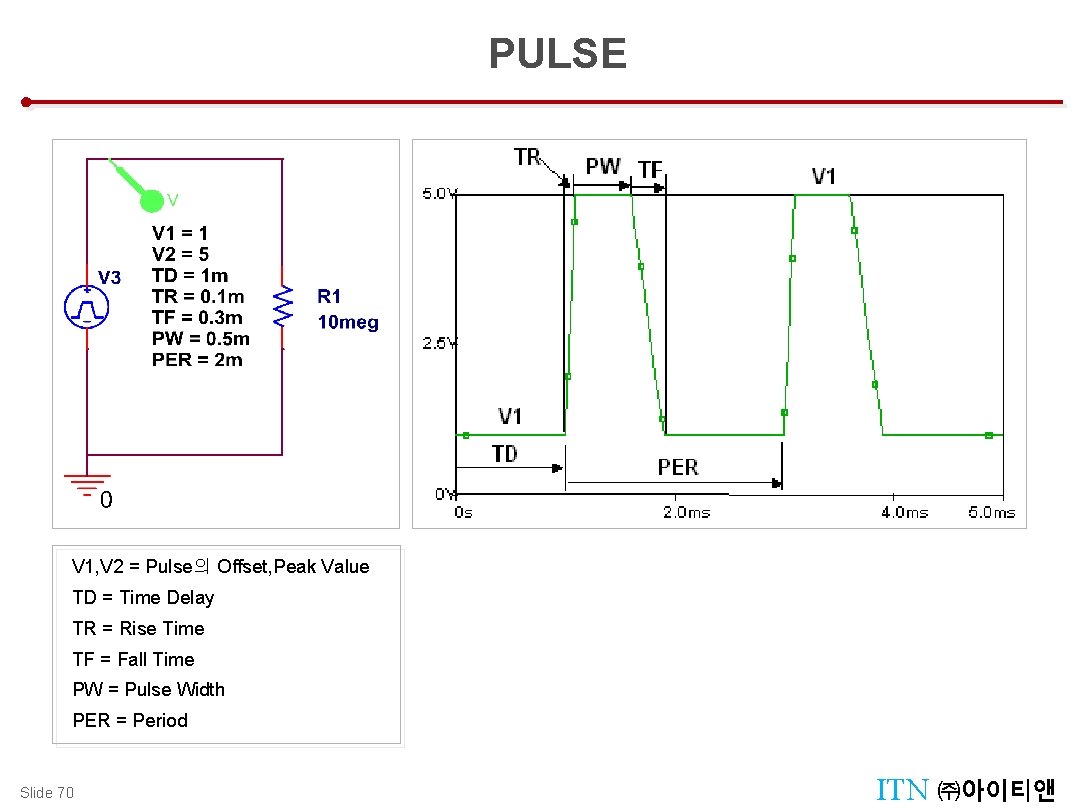

Source Pulse PULSE V 1, V 2 = Pulse의 Offset, Peak Value TD = Time Delay TR = Rise Time TF = Fall Time PW = Pulse Width PER = Period Slide 70 ITN ㈜아이티앤

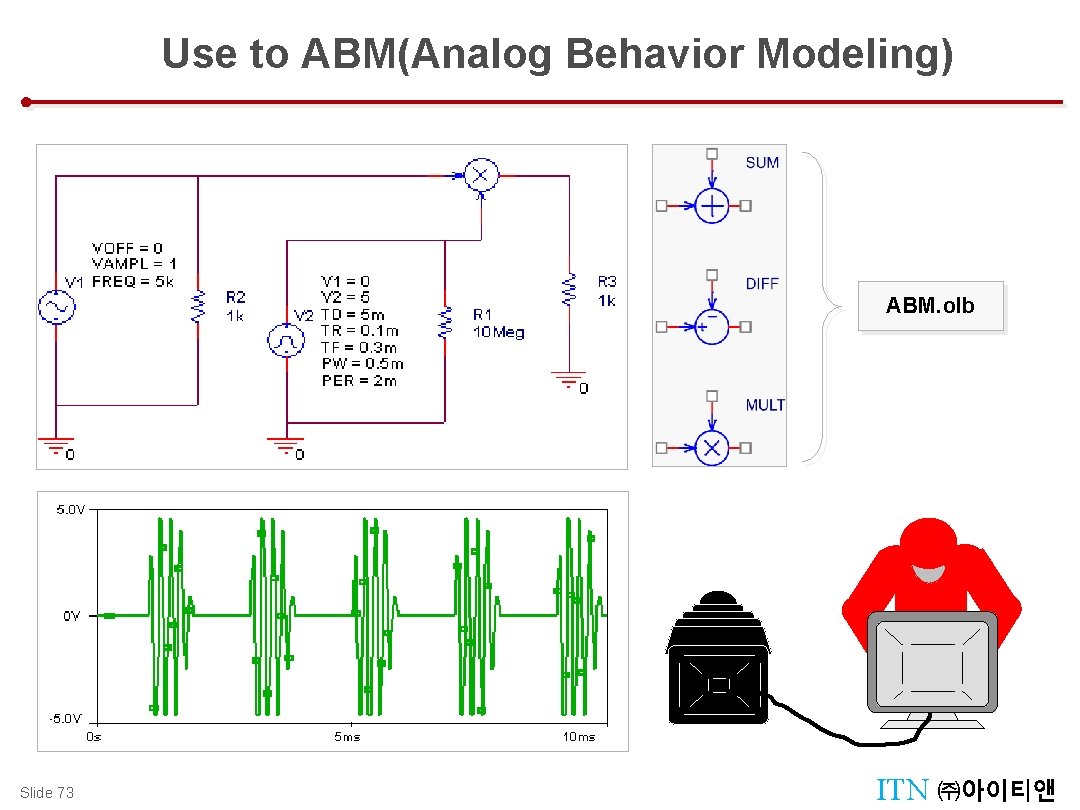

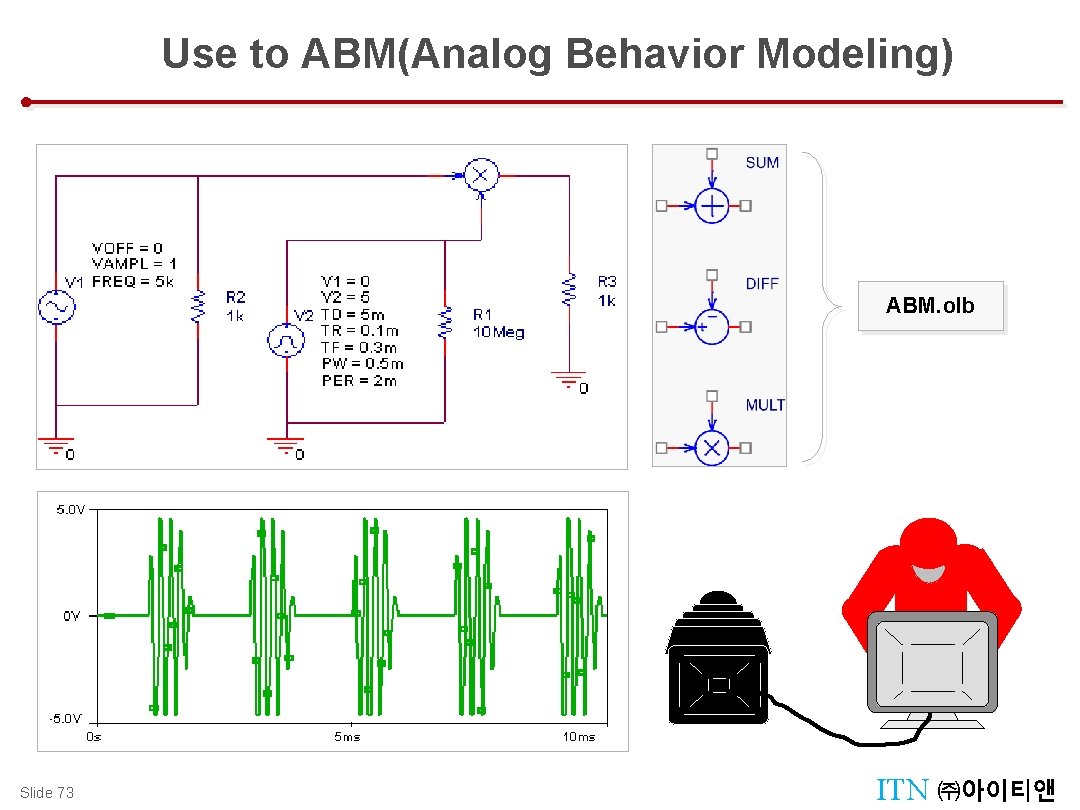

Use to ABM(Analog Behavior Modeling) Source (AMB - MULT) ABM. olb Slide 73 ITN ㈜아이티앤

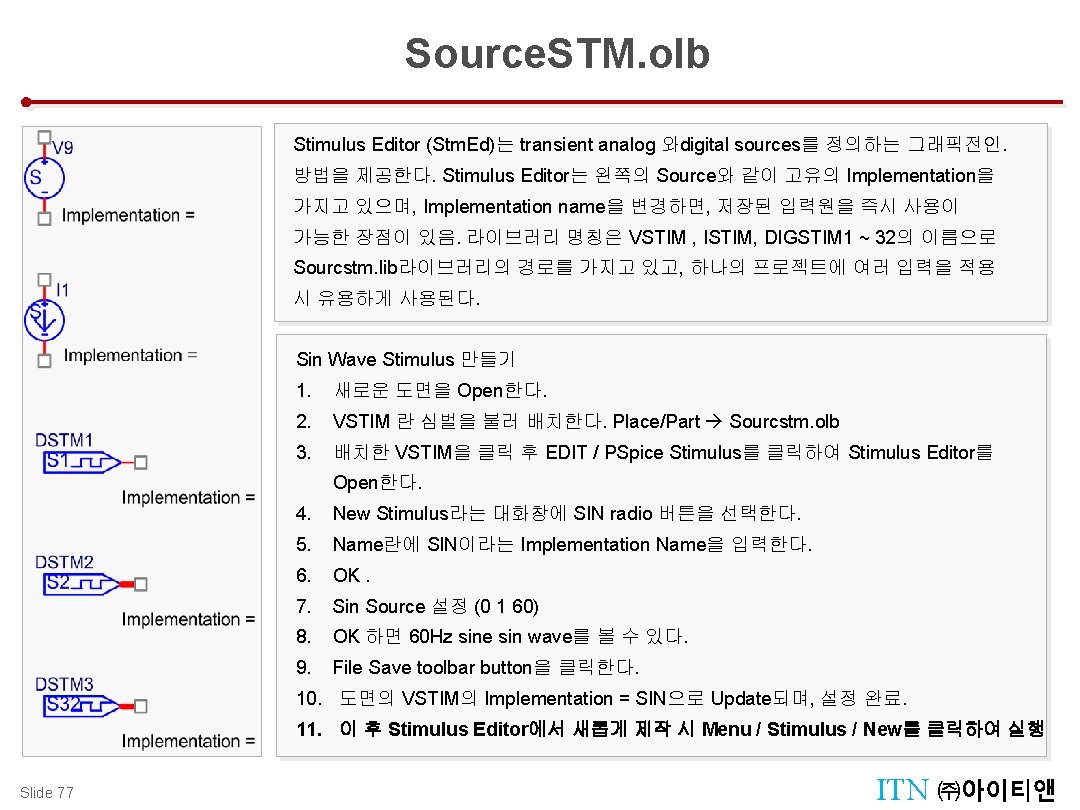

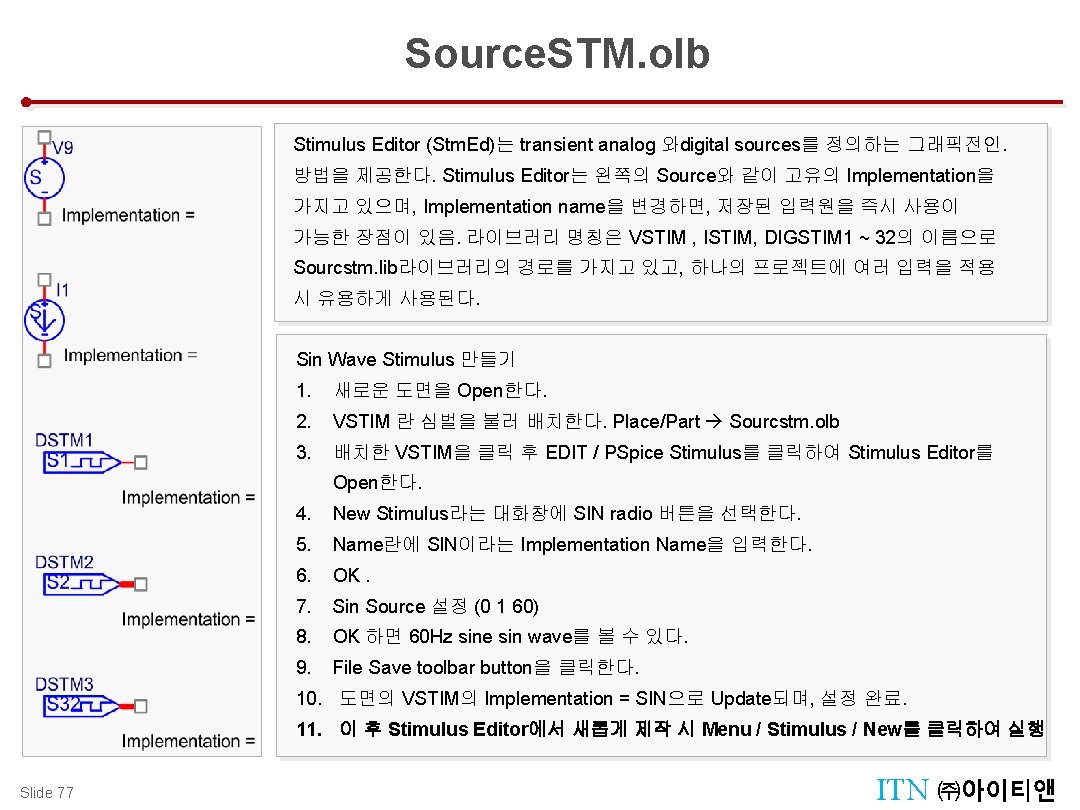

Source. STM. olb Stimulus Editor (Stm. Ed)는 transient analog 와digital sources를 정의하는 그래픽전인. 방법을 제공한다. Stimulus Editor는 왼쪽의 Source와 같이 고유의 Implementation을 가지고 있으며, Implementation name을 변경하면, 저장된 입력원을 즉시 사용이 가능한 장점이 있음. 라이브러리 명칭은 VSTIM , ISTIM, DIGSTIM 1 ~ 32의 이름으로 Sourcstm. lib라이브러리의 경로를 가지고 있고, 하나의 프로젝트에 여러 입력을 적용 시 유용하게 사용된다. Sin Wave Stimulus 만들기 1. 새로운 도면을 Open한다. 2. VSTIM 란 심벌을 불러 배치한다. Place/Part Sourcstm. olb 3. 배치한 VSTIM을 클릭 후 EDIT / PSpice Stimulus를 클릭하여 Stimulus Editor를 Open한다. 4. New Stimulus라는 대화창에 SIN radio 버튼을 선택한다. 5. Name란에 SIN이라는 Implementation Name을 입력한다. 6. OK. 7. Sin Source 설정 (0 1 60) 8. OK 하면 60 Hz sine sin wave를 볼 수 있다. 9. File Save toolbar button을 클릭한다. 10. 도면의 VSTIM의 Implementation = SIN으로 Update되며, 설정 완료. 11. 이 후 Stimulus Editor에서 새롭게 제작 시 Menu / Stimulus / New를 클릭하여 실행 Slide 77 ITN ㈜아이티앤

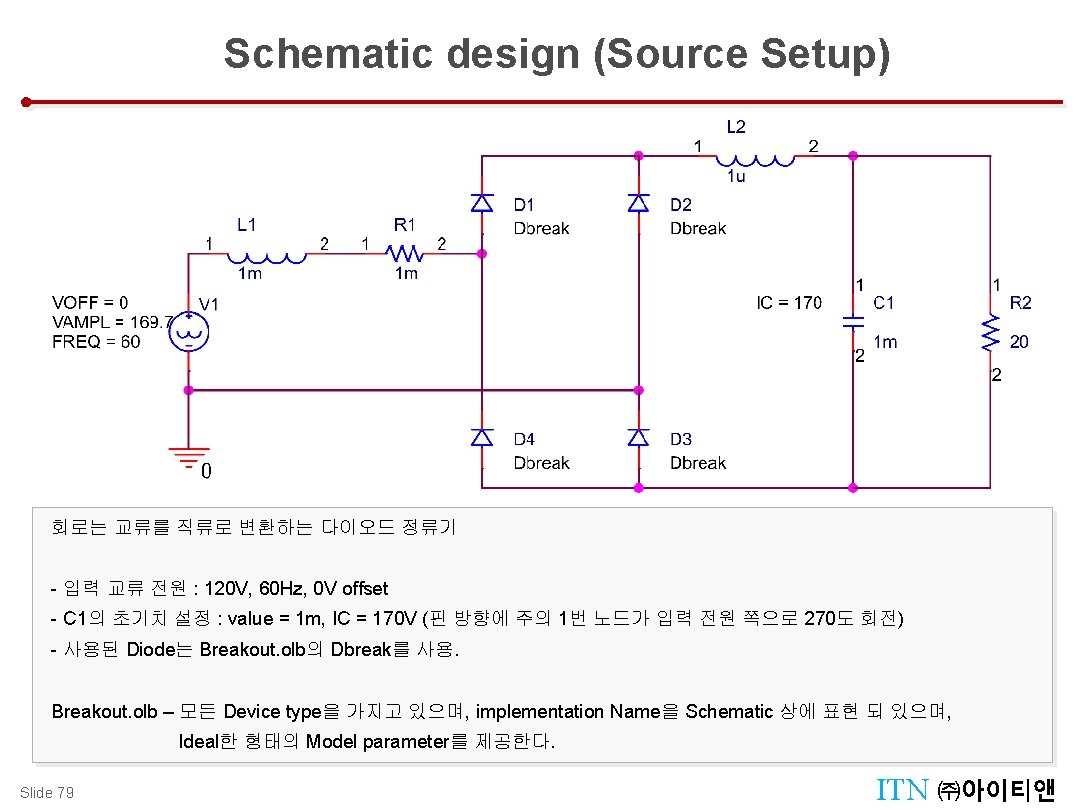

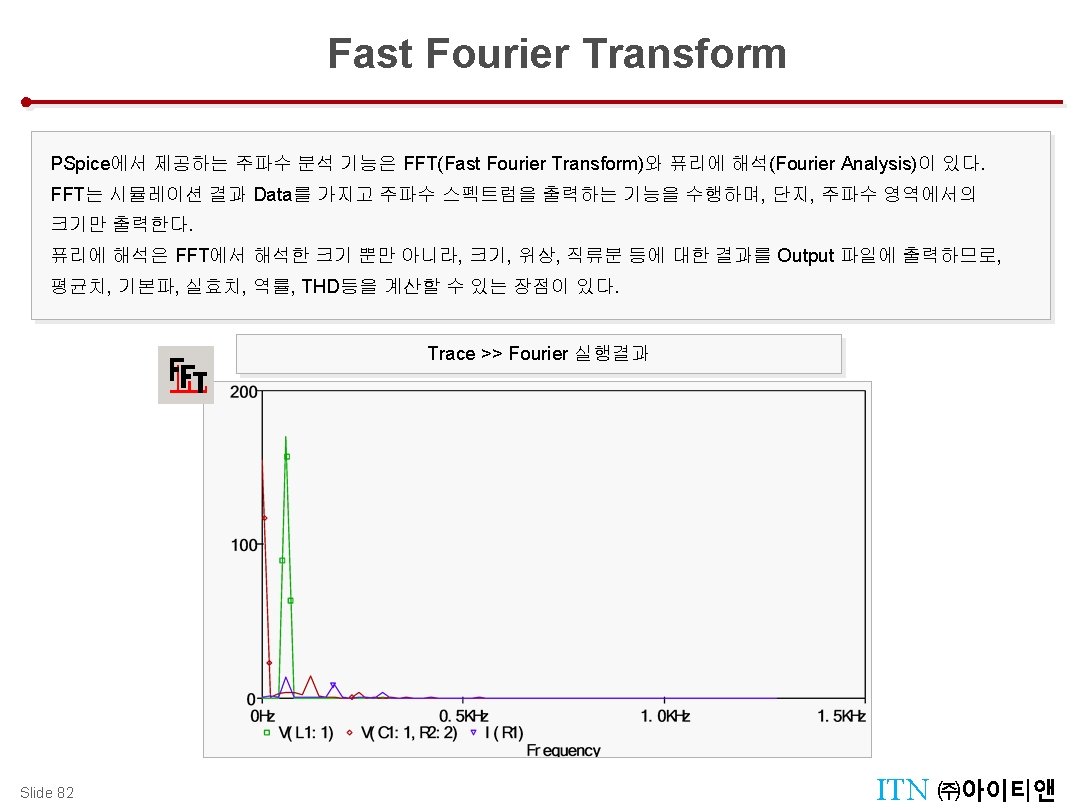

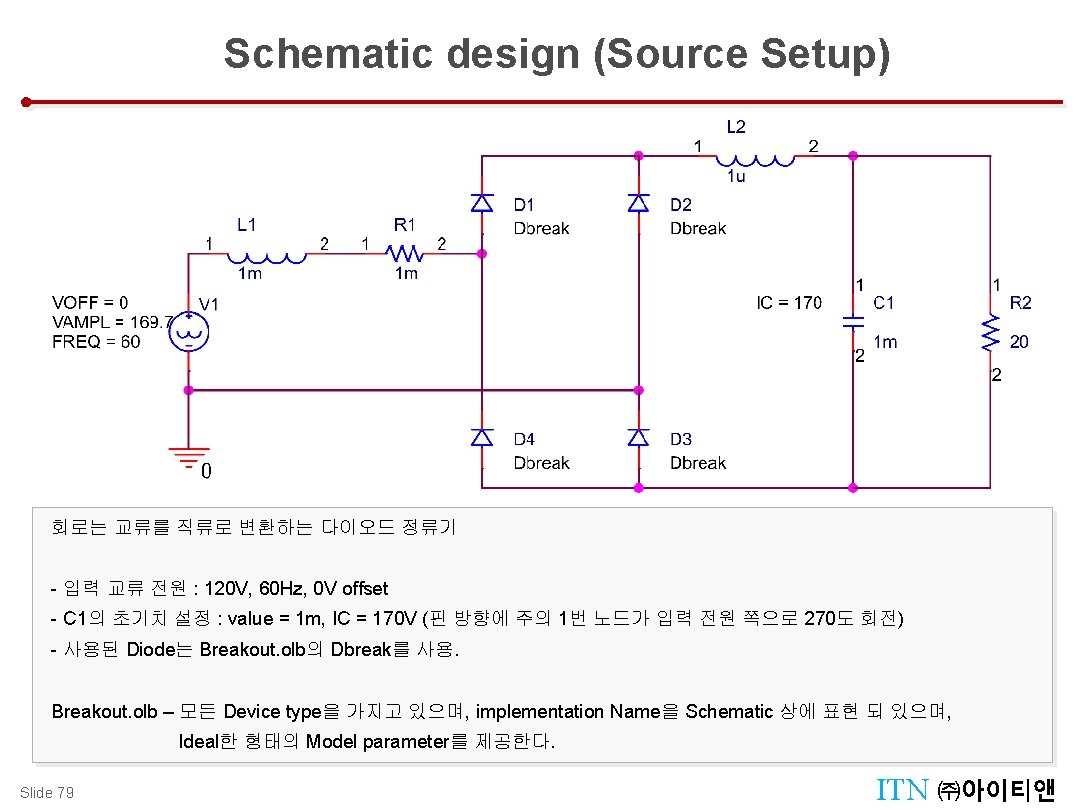

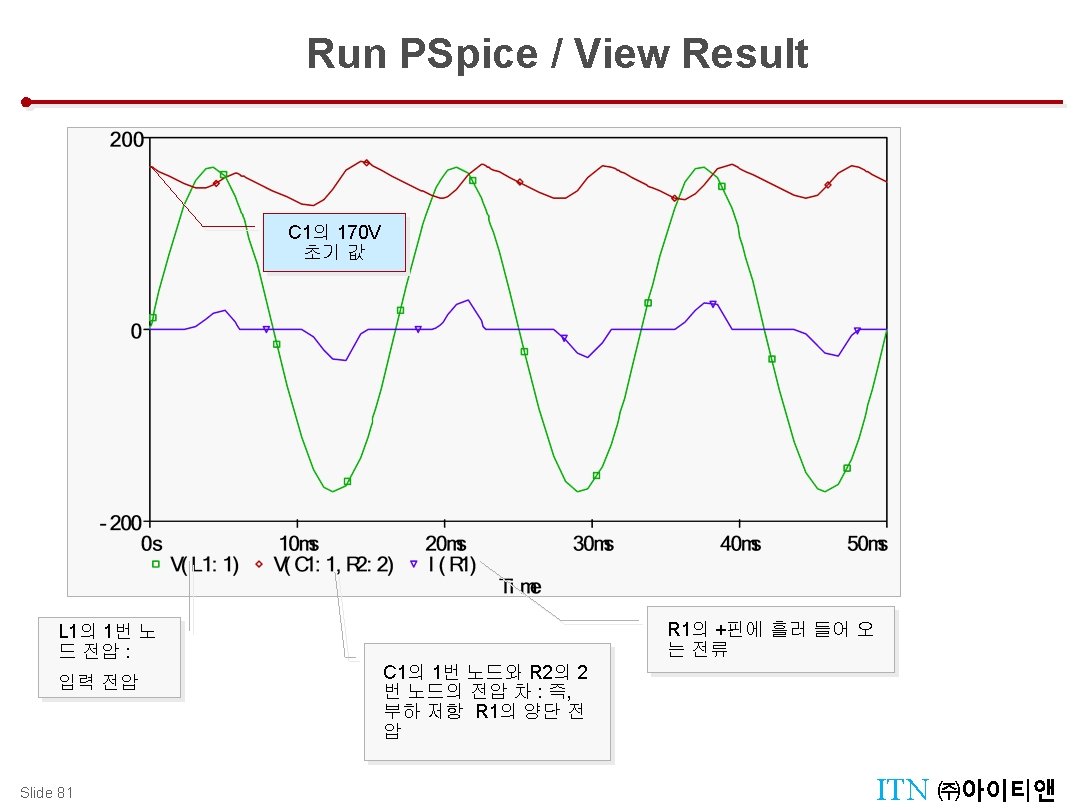

Transient Analysis Design Management : Manager Tool 과도 해석은 시간영역에서 입력 신호에 대한 출력을 결정하는 해석으로 DC해석에서의 인덕터의 단락, 커패시터의 오픈의 해석과는 다르다. 항상 L 과 C의 현재의 계산값을 초기치로 하여 다음 스텝의 계산을 수행한다. Schematic design (Source Setup) Create Simulation profile(Transient Analysis) Run PSpice & View result Create Simulation profile(Fourier Analysis) Run PSpice & View result Slide 78 ITN ㈜아이티앤

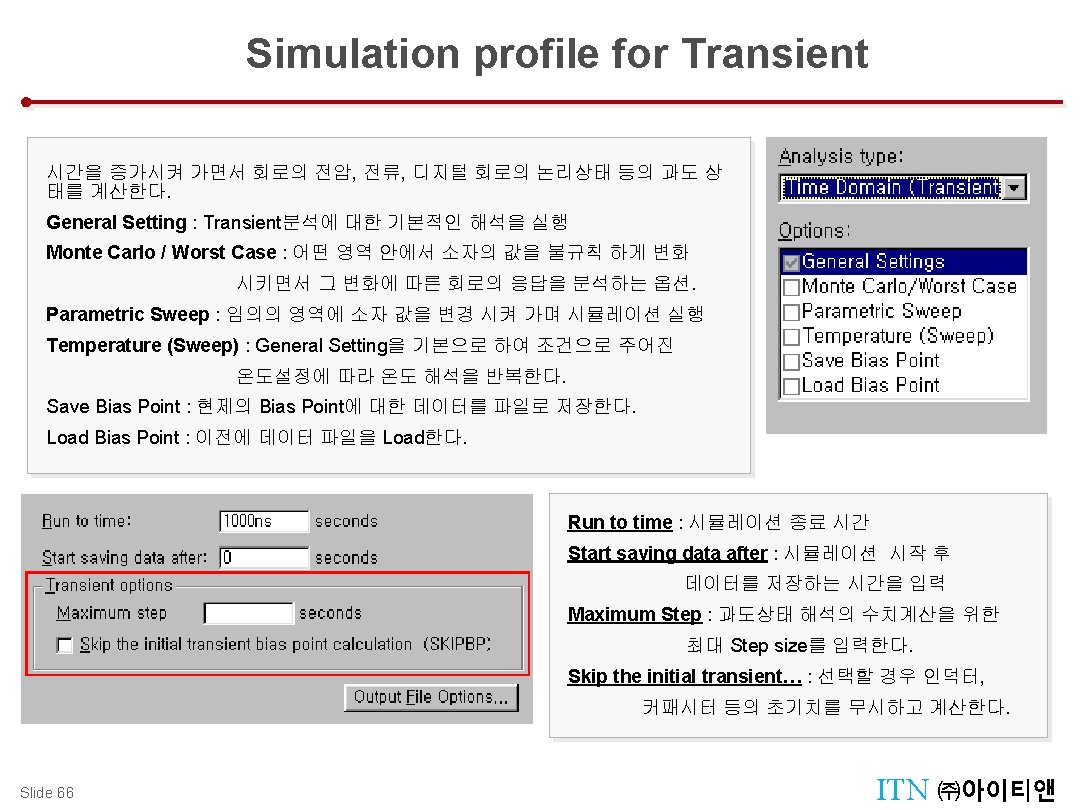

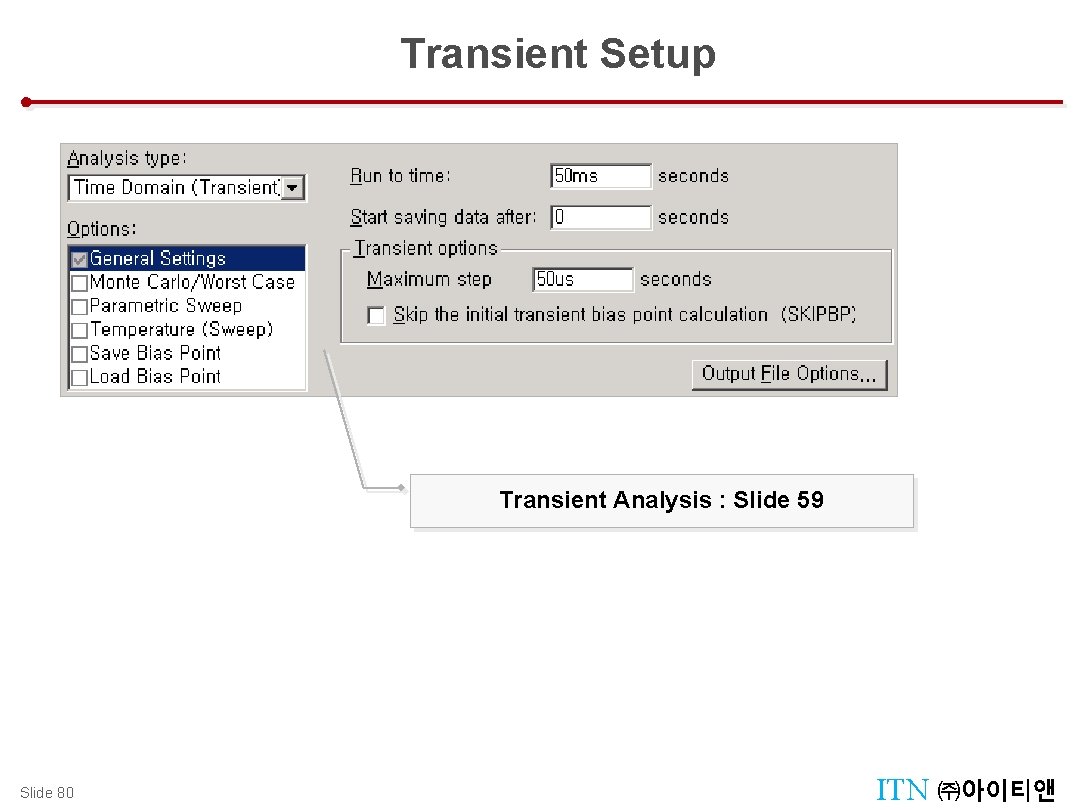

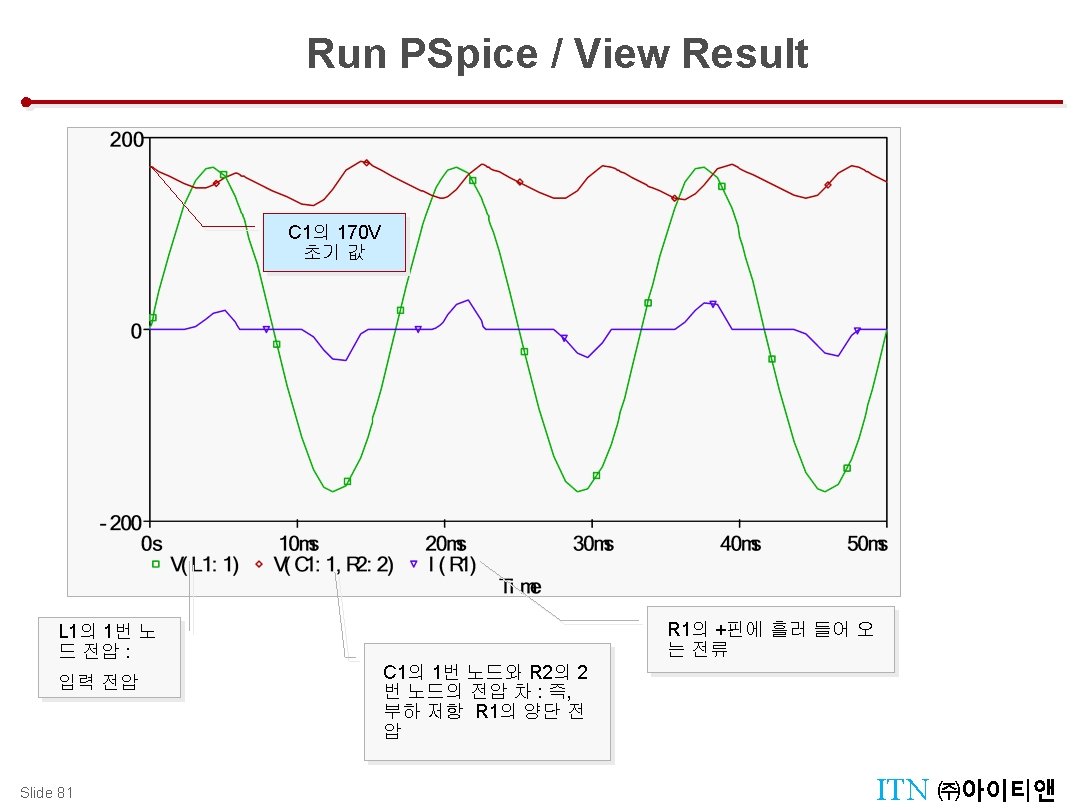

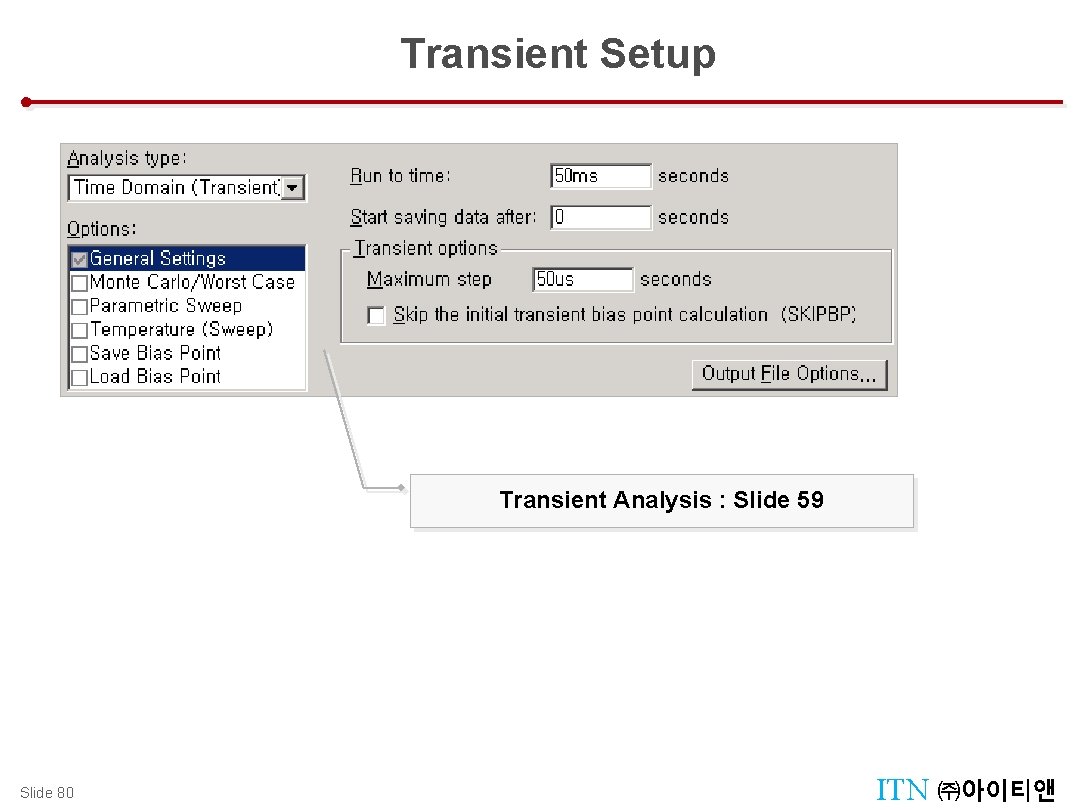

Transient Setup Transient Analysis : Slide 59 Slide 80 ITN ㈜아이티앤

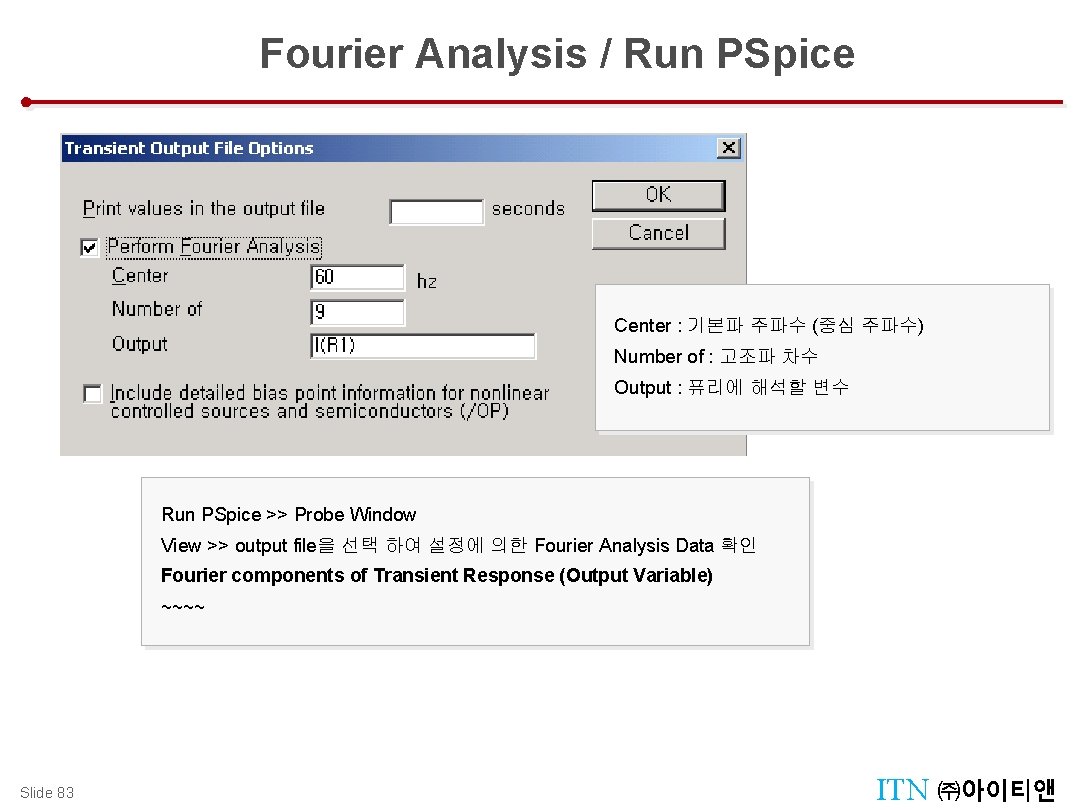

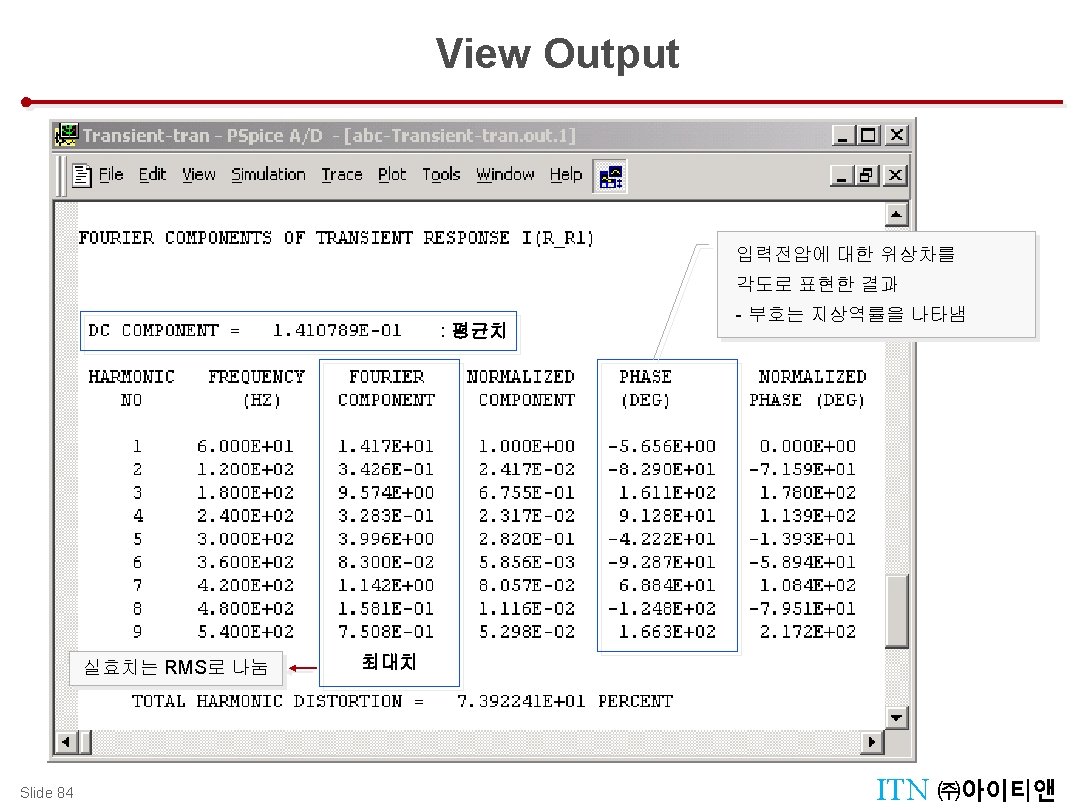

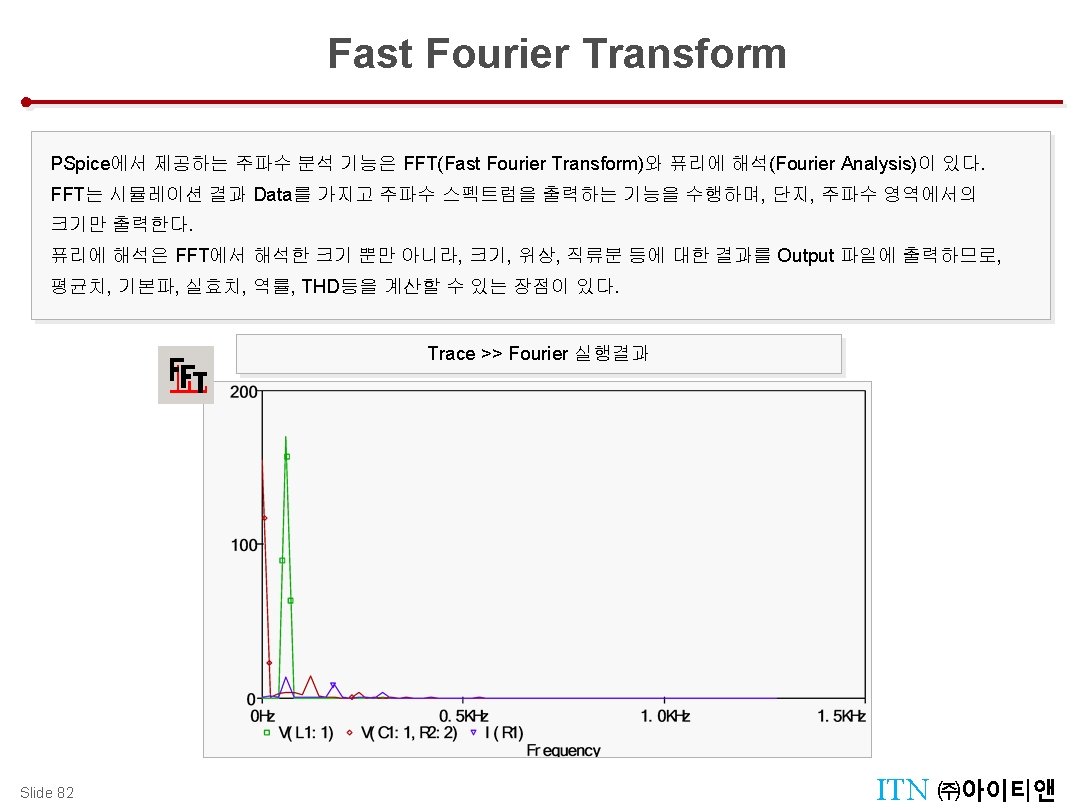

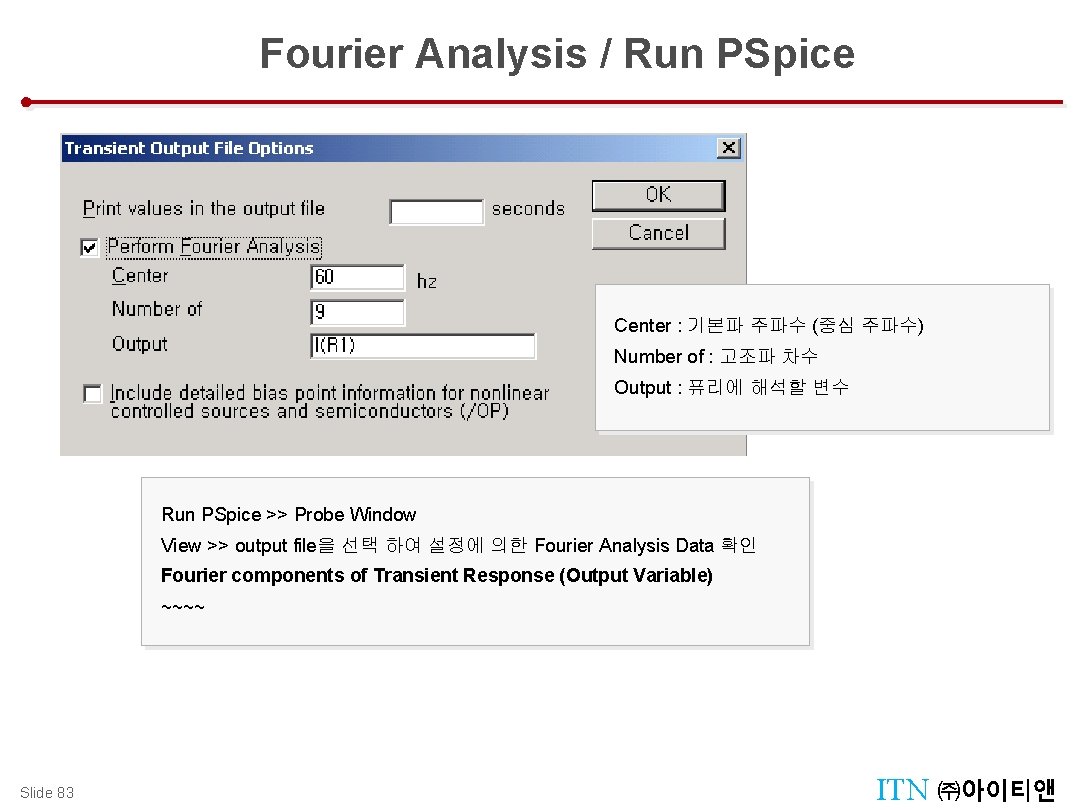

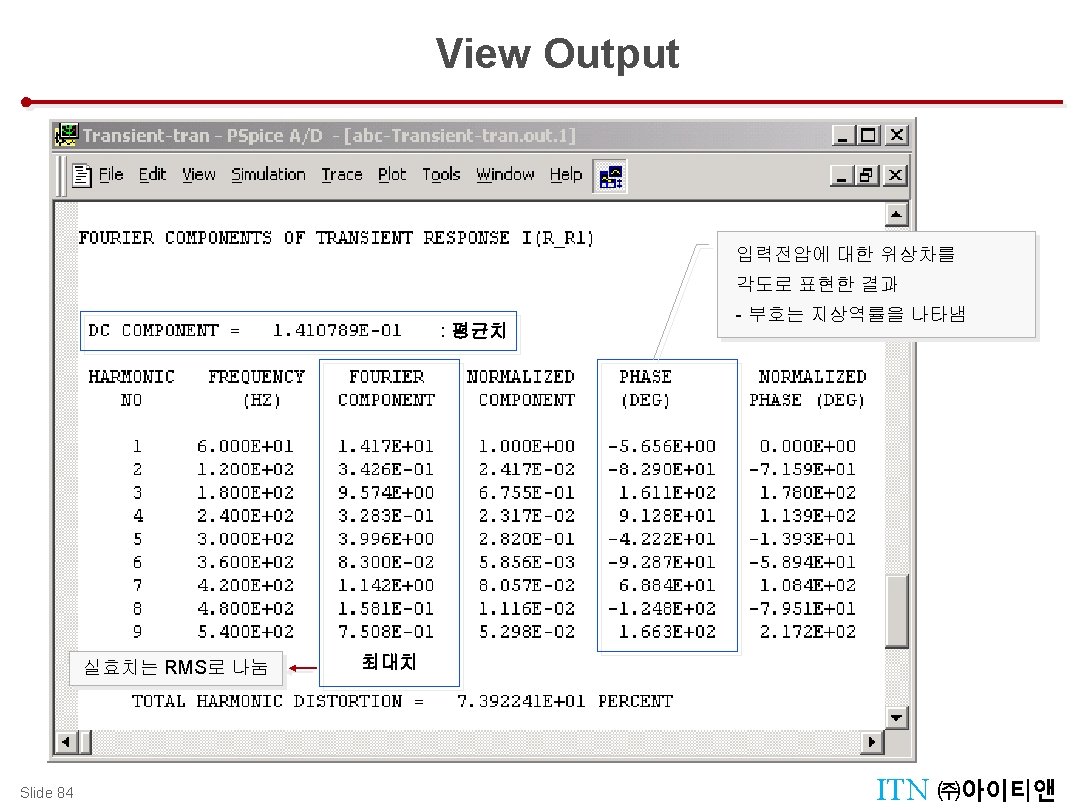

Fourier Analysis / Run PSpice Center : 기본파 주파수 (중심 주파수) Number of : 고조파 차수 Output : 퓨리에 해석할 변수 Run PSpice >> Probe Window View >> output file을 선택 하여 설정에 의한 Fourier Analysis Data 확인 Fourier components of Transient Response (Output Variable) ~~~~ Slide 83 ITN ㈜아이티앤

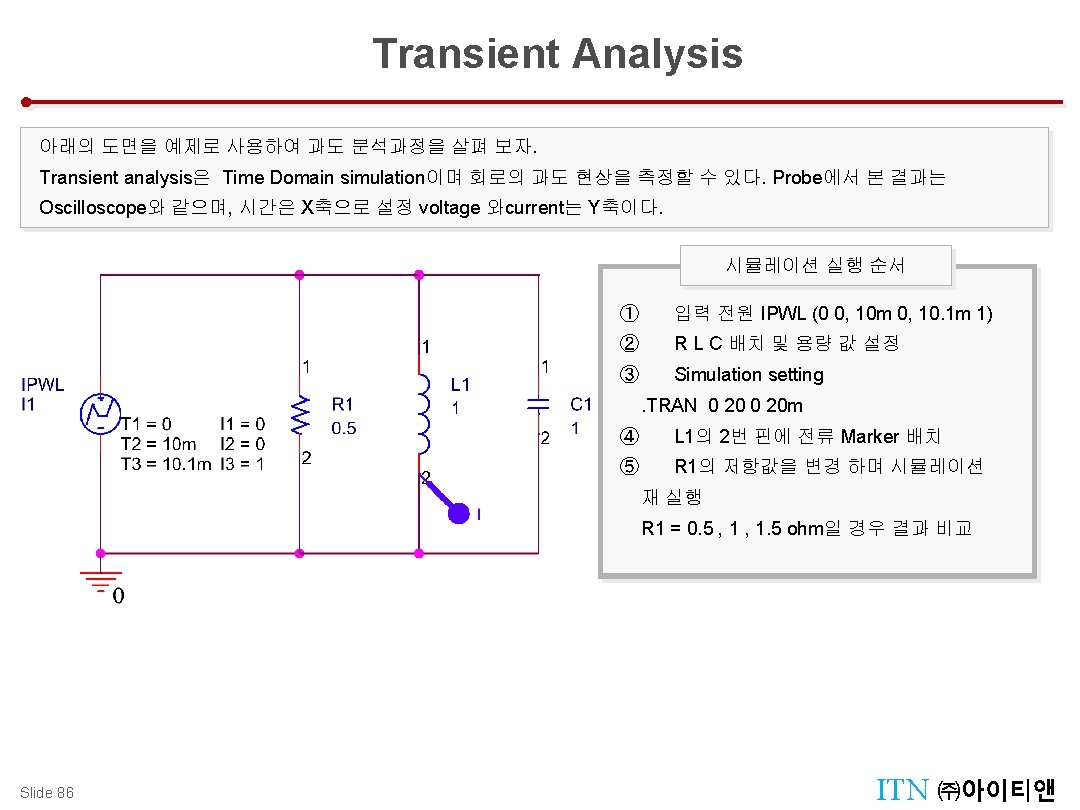

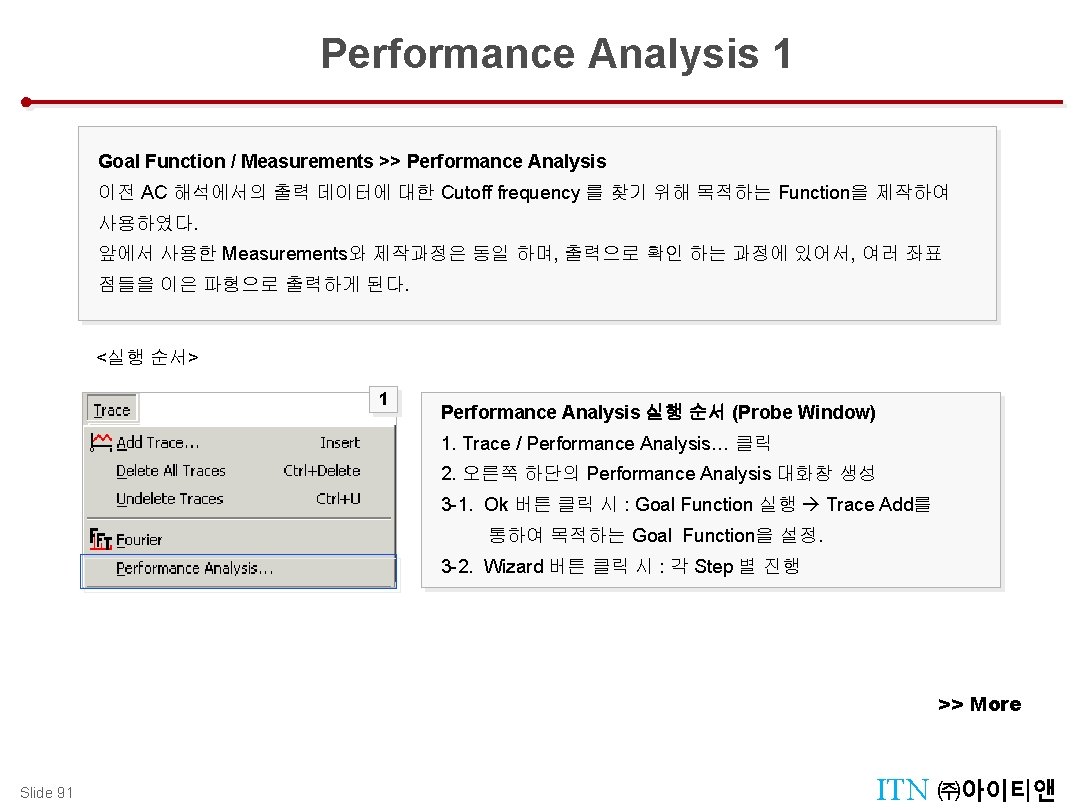

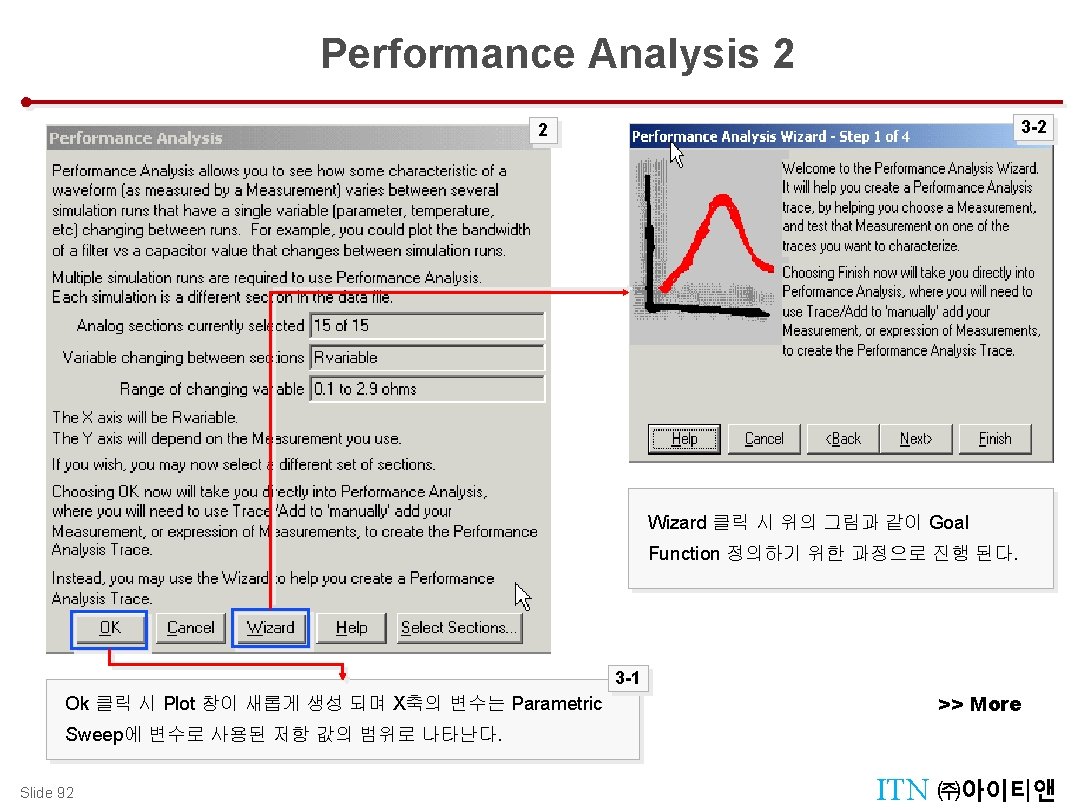

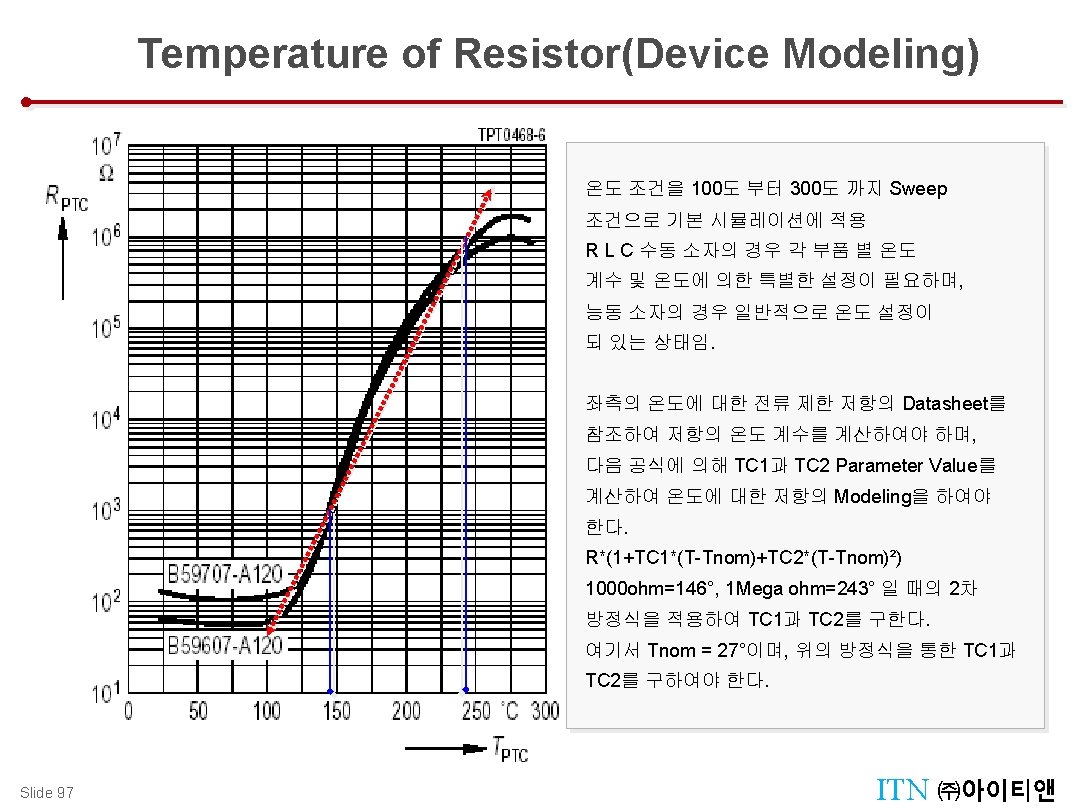

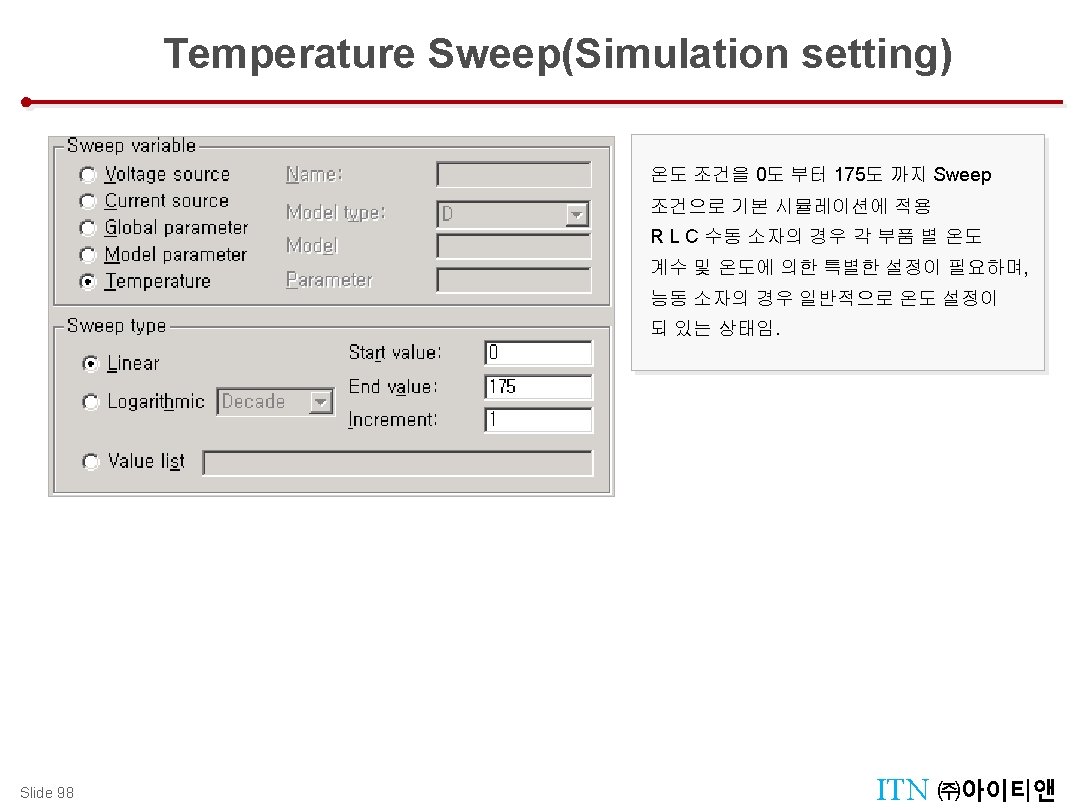

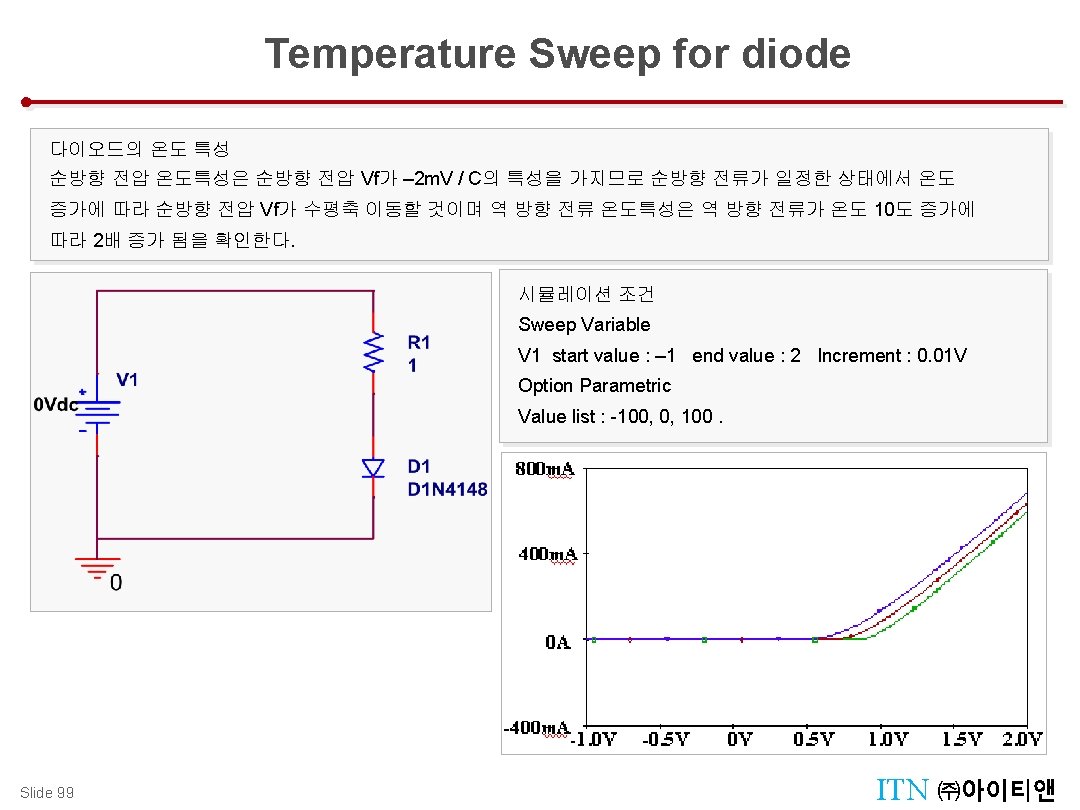

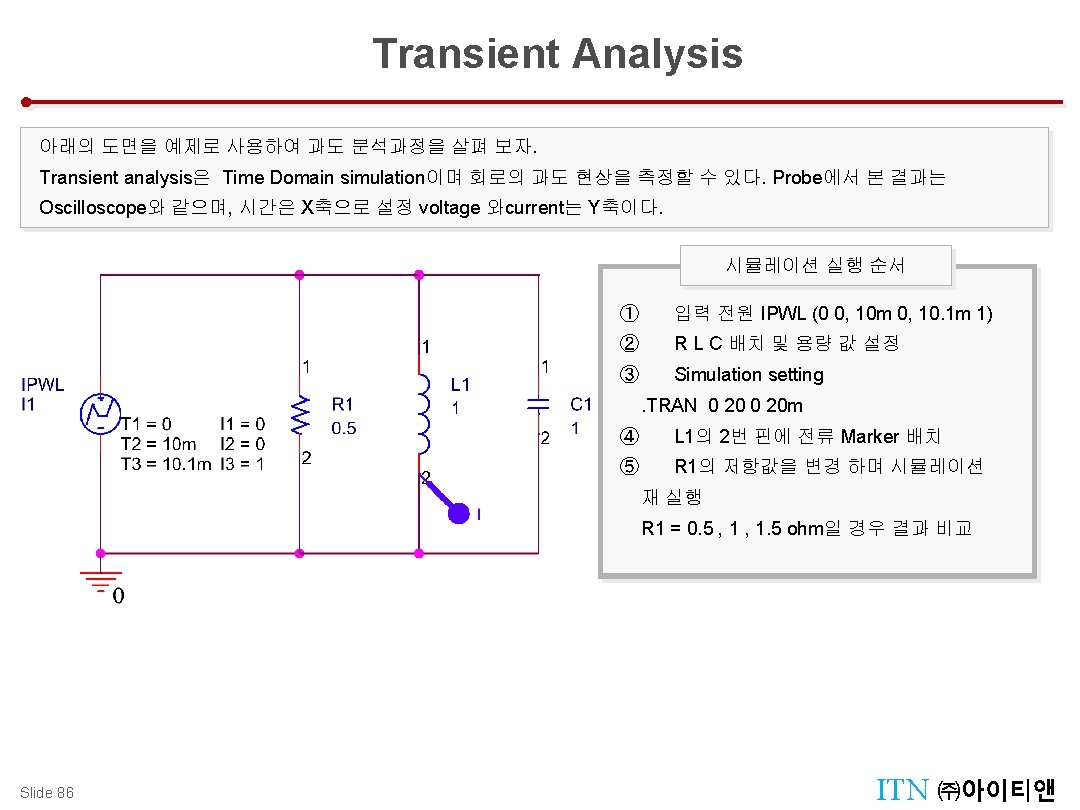

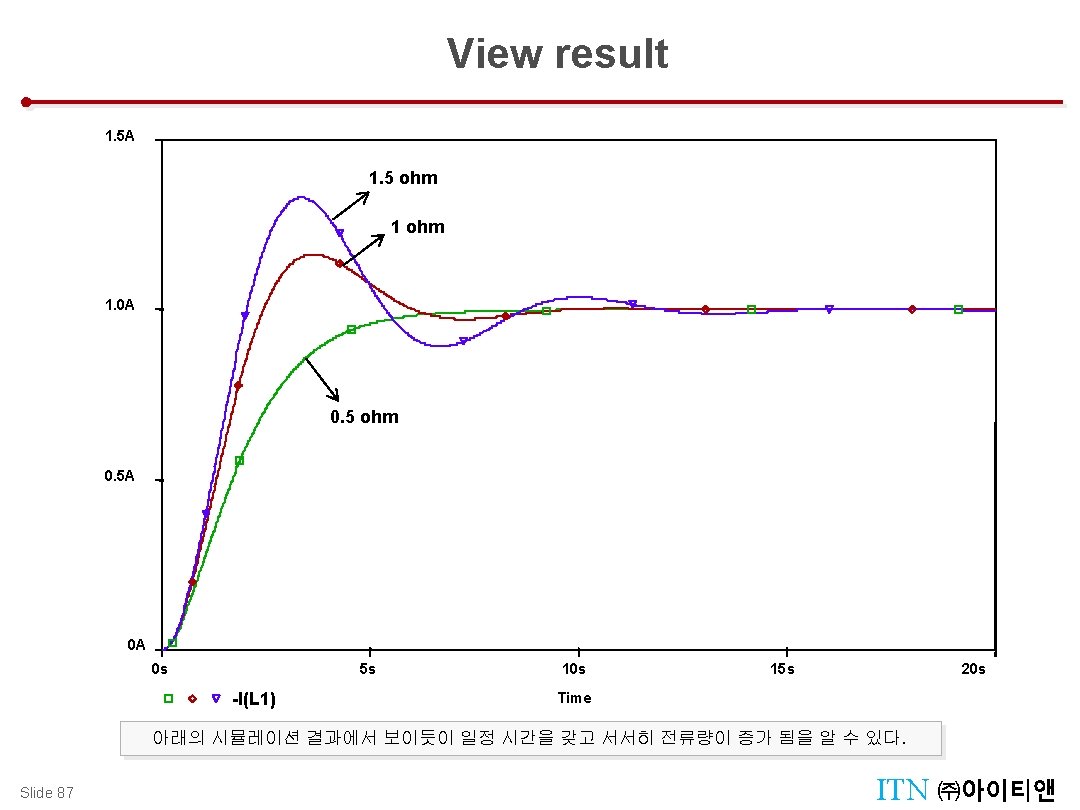

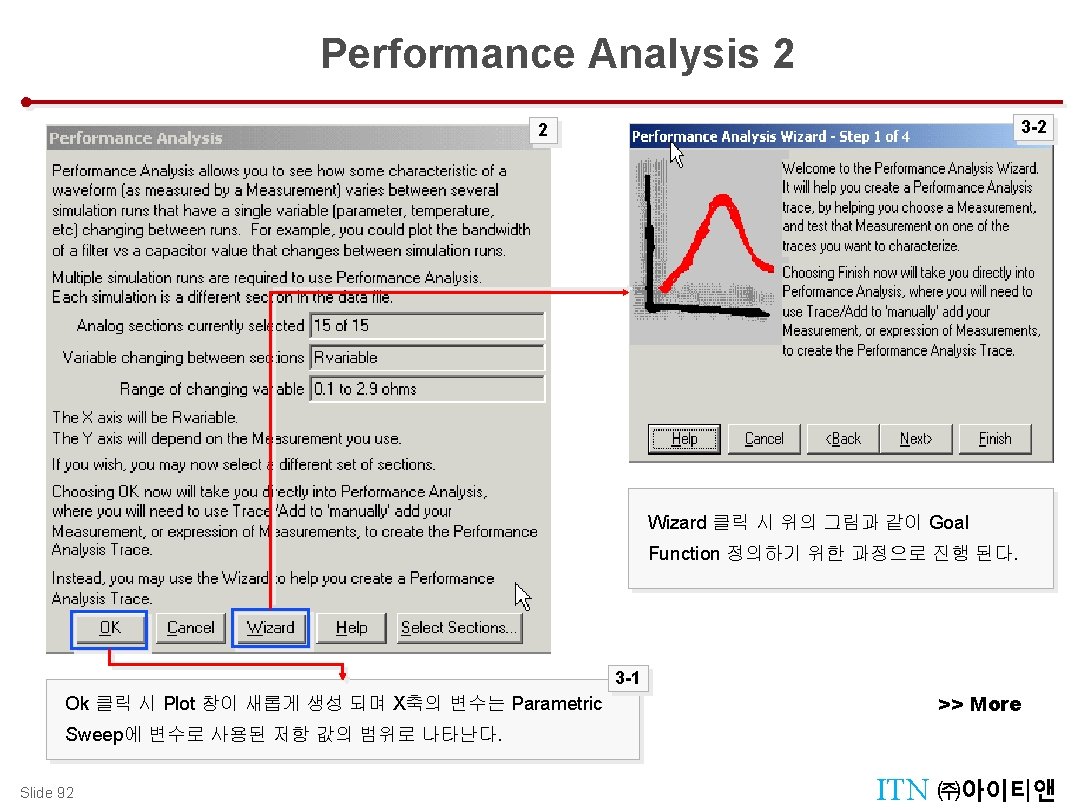

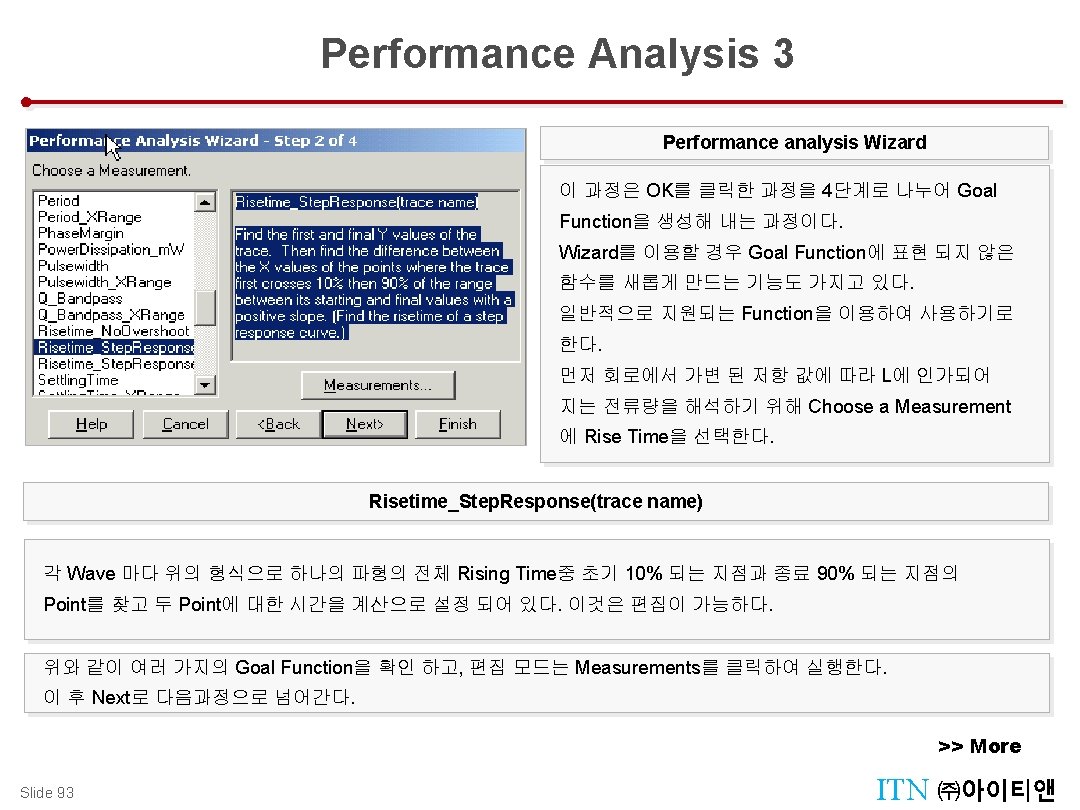

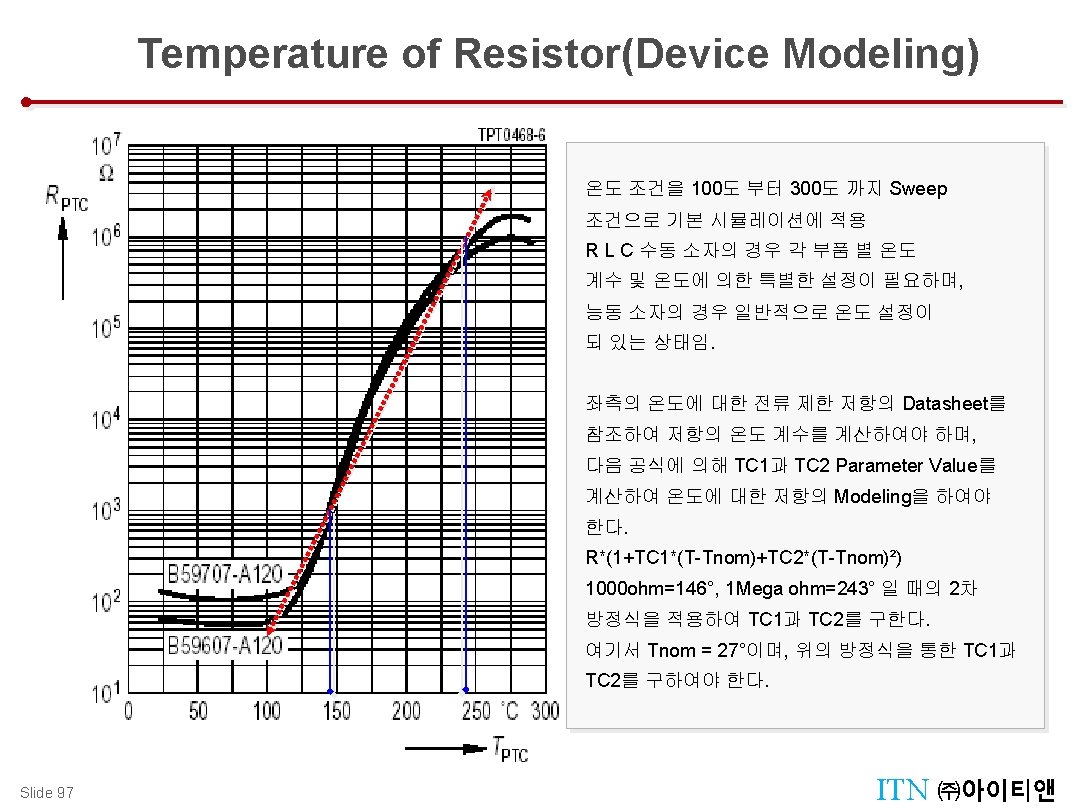

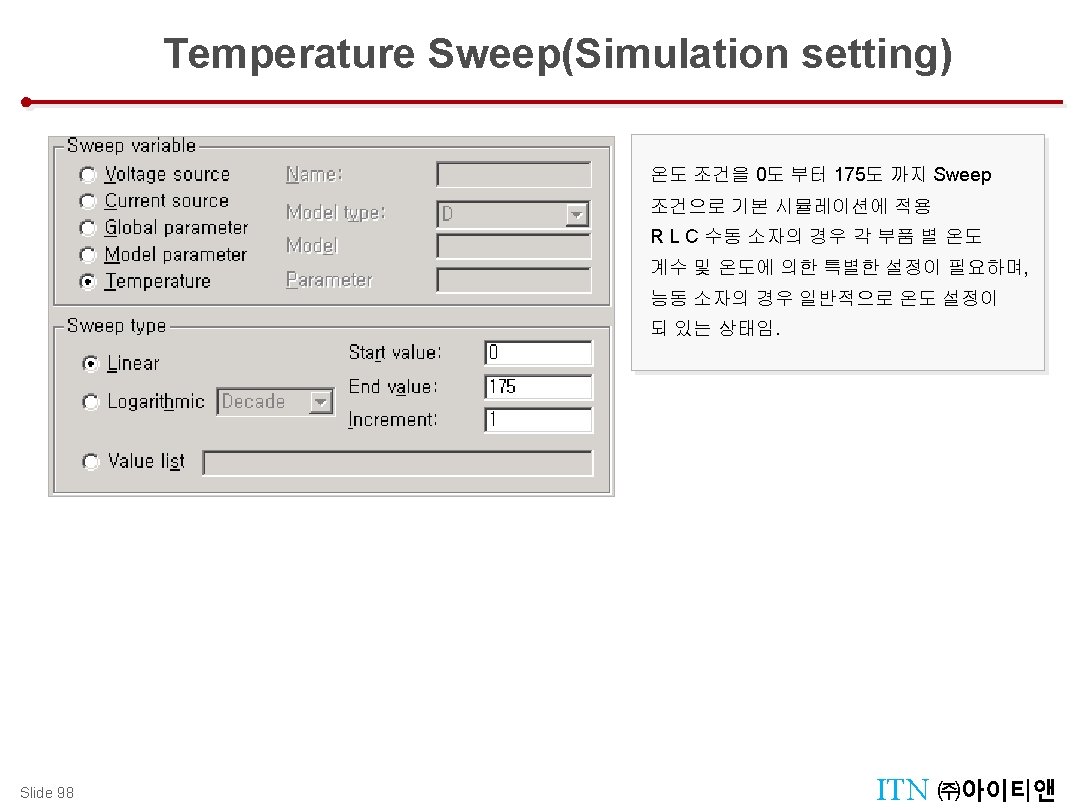

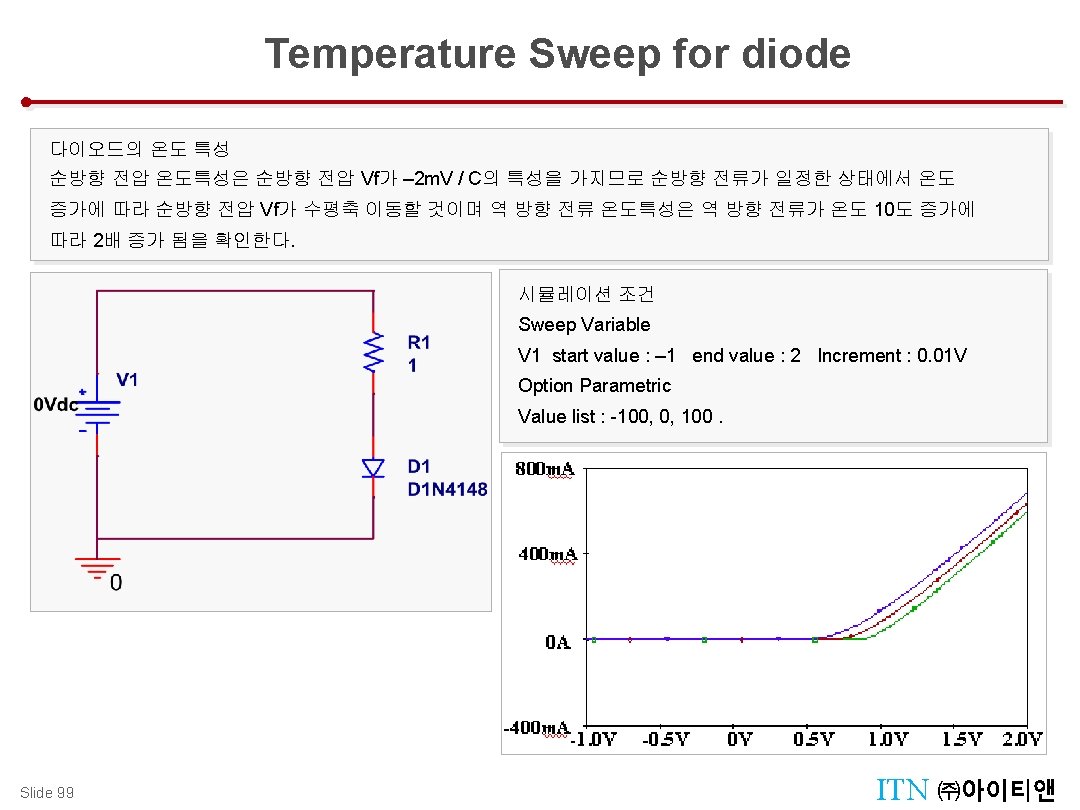

Parametric Analysis Design Management : Manager Tool Transient Analysis View Results. Param setting 1 (Schematic Entry). Param Setting 2 (Simulation setting) Run PSpice & View Result Performance Analysis & View Result Type of Device parameter Temperature of Resistor (Device Modeling) Temperature Sweep (Simulation Setting) Temperature Sweep for diode Slide 85 ITN ㈜아이티앤

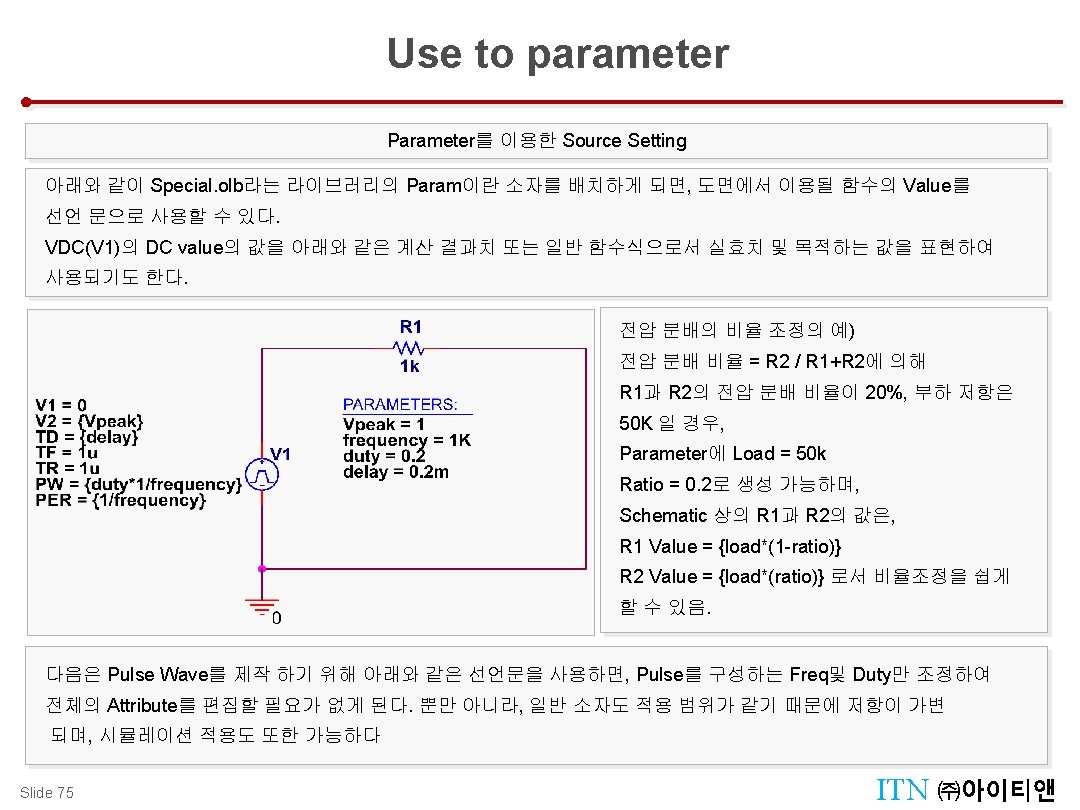

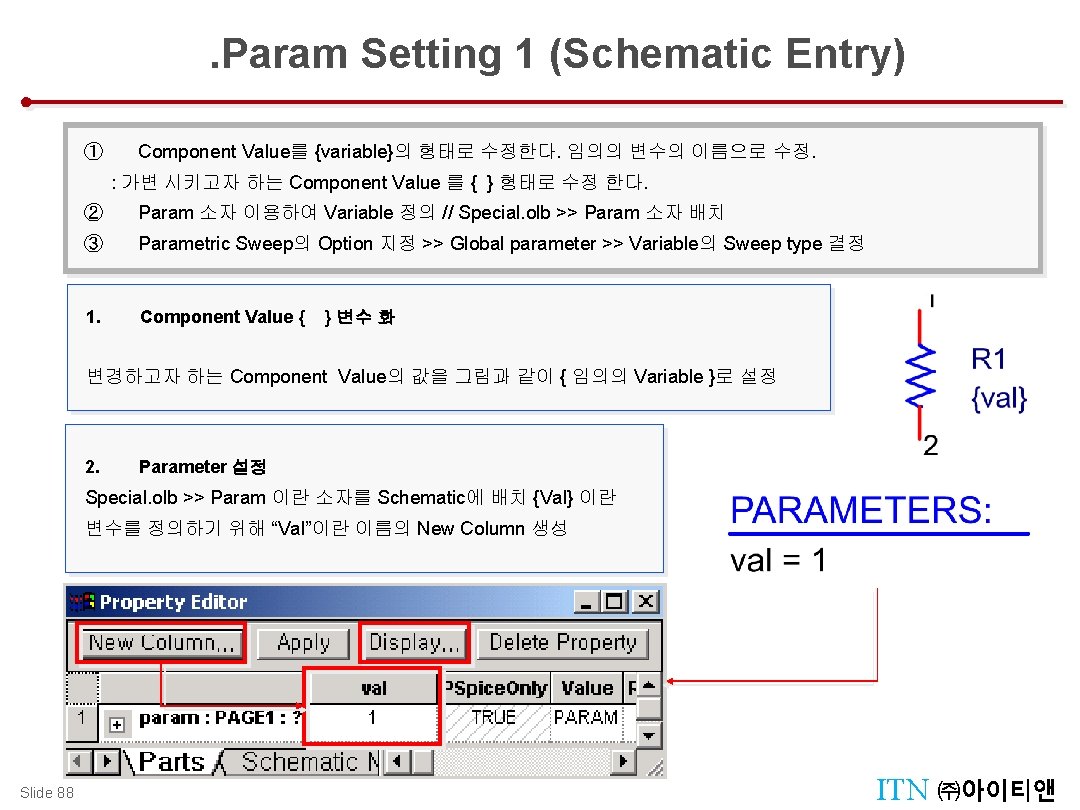

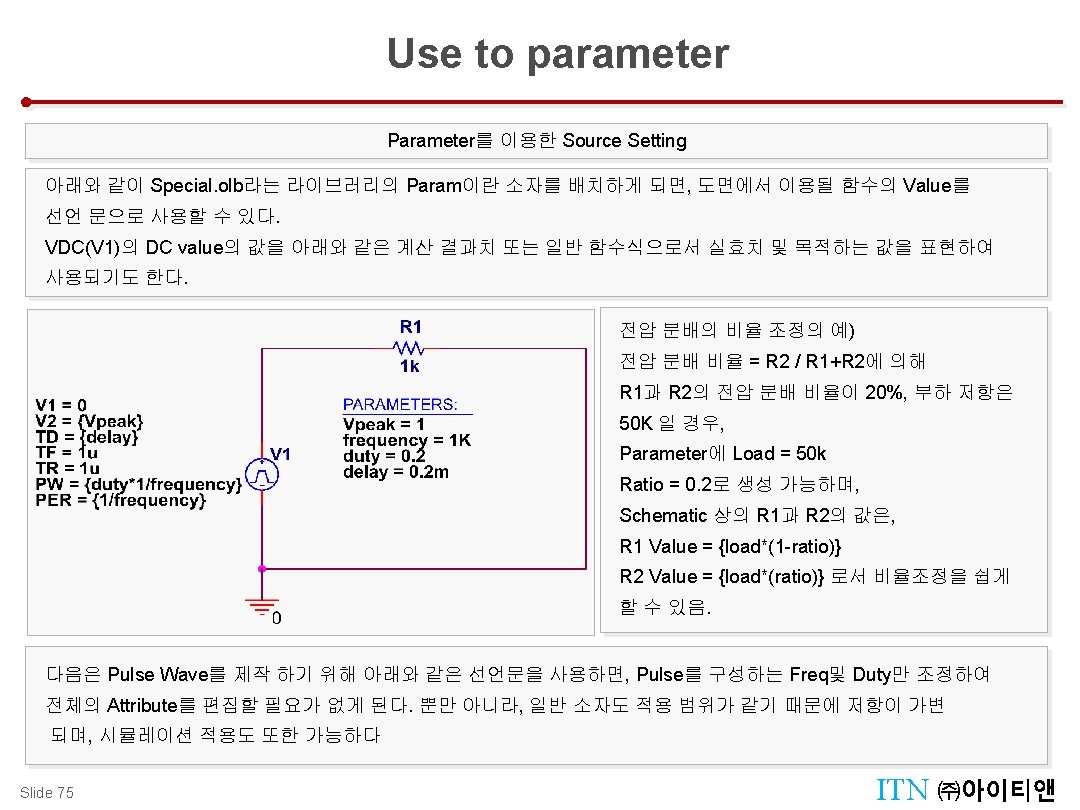

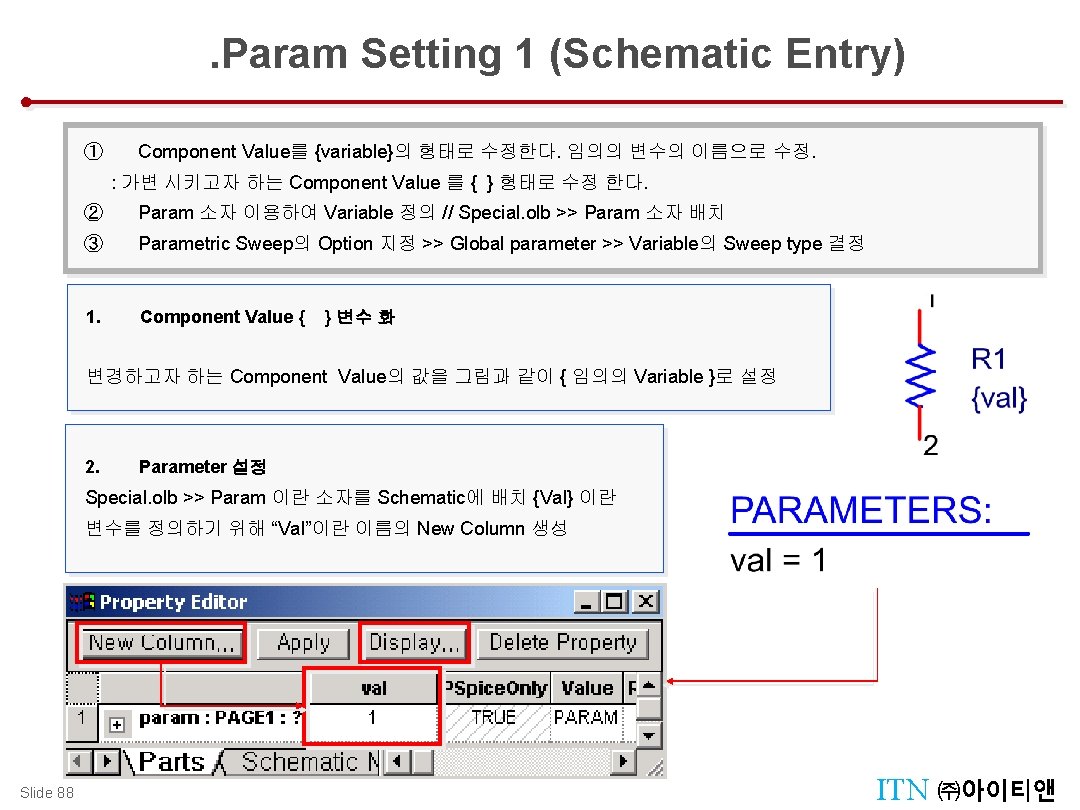

. Param Setting 1 (Schematic Entry) ① Component Value를 {variable}의 형태로 수정한다. 임의의 변수의 이름으로 수정. : 가변 시키고자 하는 Component Value 를 { } 형태로 수정 한다. ② Param 소자 이용하여 Variable 정의 // Special. olb >> Param 소자 배치 ③ Parametric Sweep의 Option 지정 >> Global parameter >> Variable의 Sweep type 결정 1. Component Value { } 변수 화 변경하고자 하는 Component Value의 값을 그림과 같이 { 임의의 Variable }로 설정 2. Parameter 설정 Special. olb >> Param 이란 소자를 Schematic에 배치 {Val} 이란 변수를 정의하기 위해 “Val”이란 이름의 New Column 생성 Slide 88 ITN ㈜아이티앤

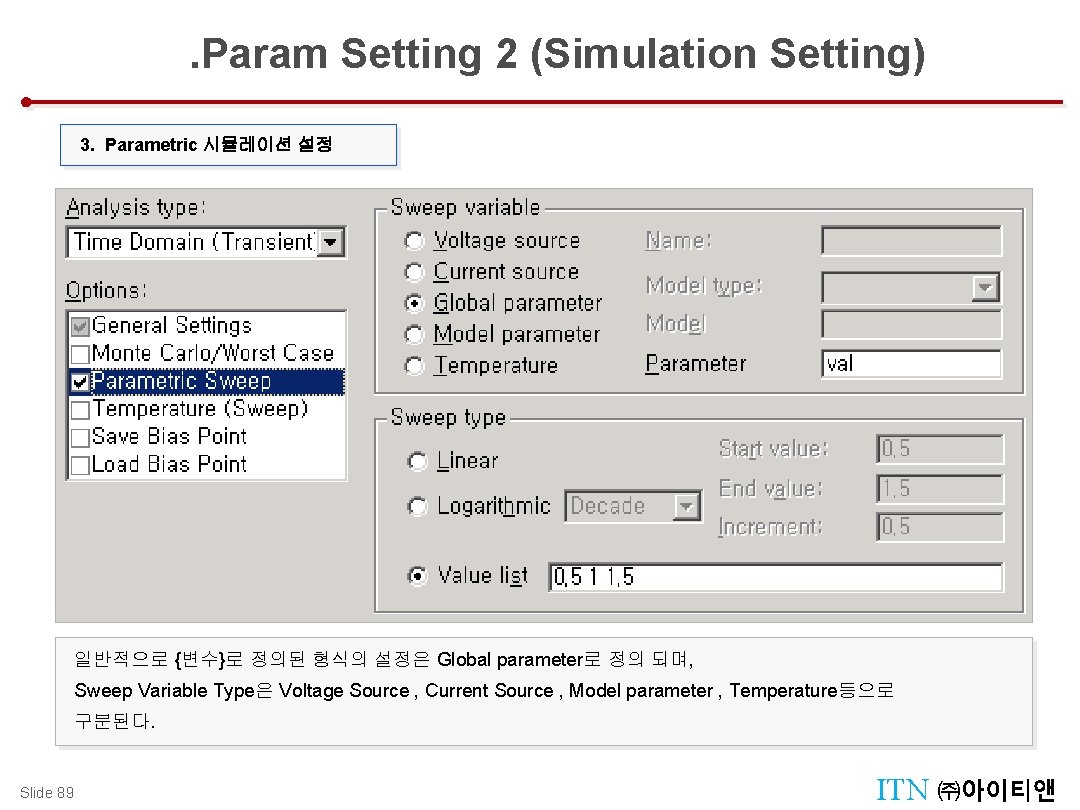

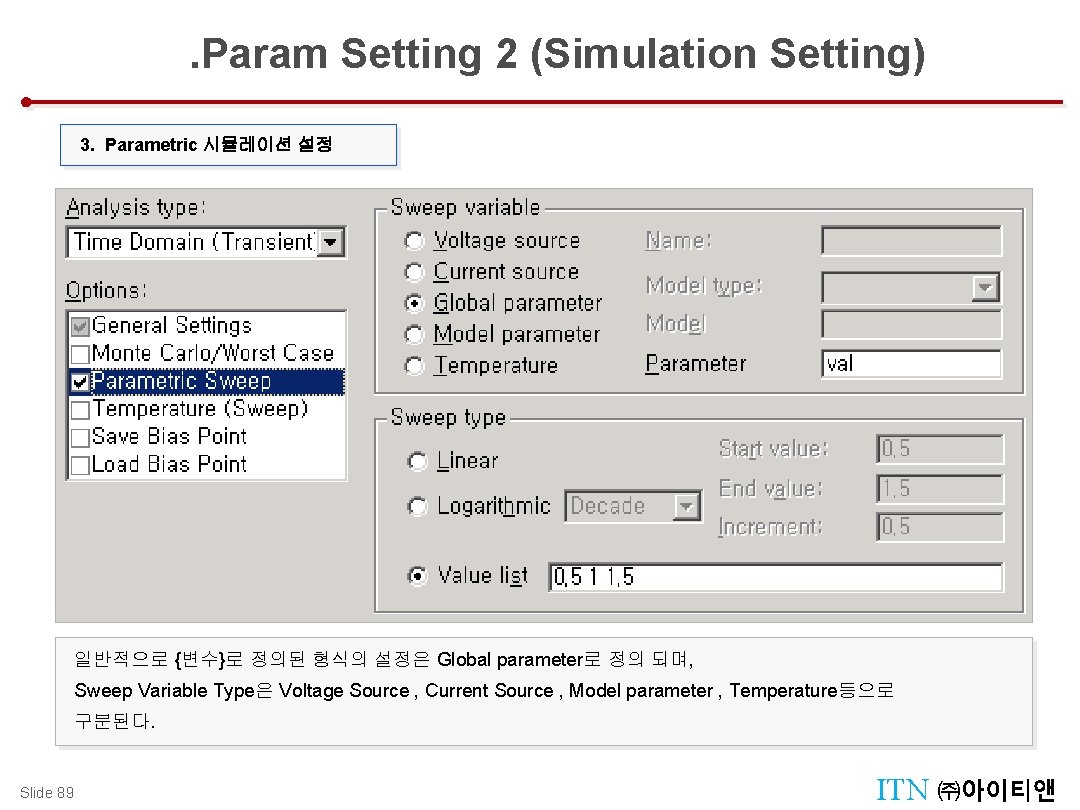

. Param Setting 2 (Simulation Setting) 3. Parametric 시뮬레이션 설정 일반적으로 {변수}로 정의된 형식의 설정은 Global parameter로 정의 되며, Sweep Variable Type은 Voltage Source , Current Source , Model parameter , Temperature등으로 구분된다. Slide 89 ITN ㈜아이티앤

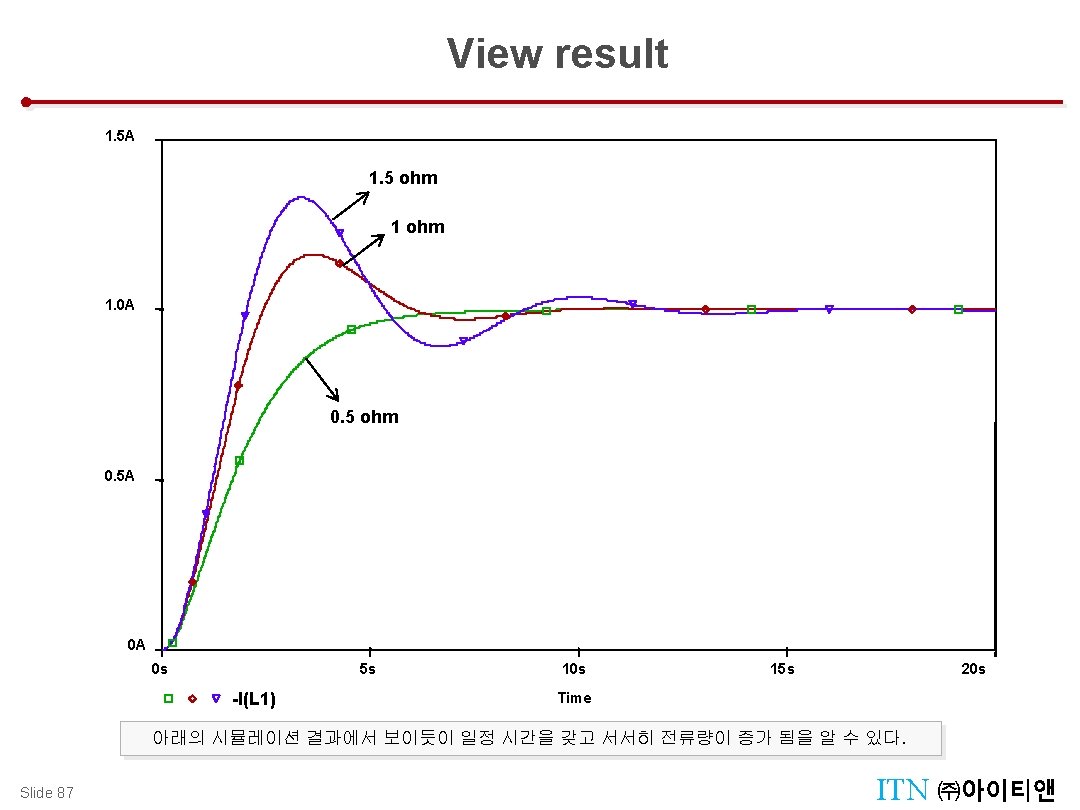

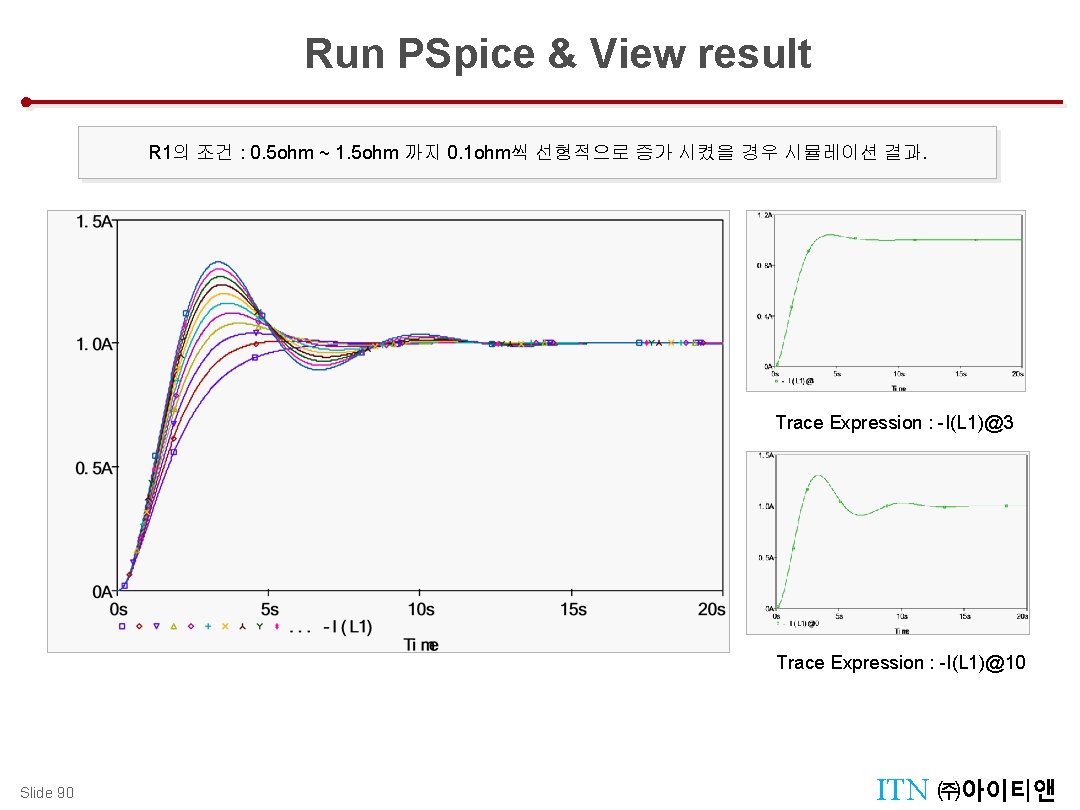

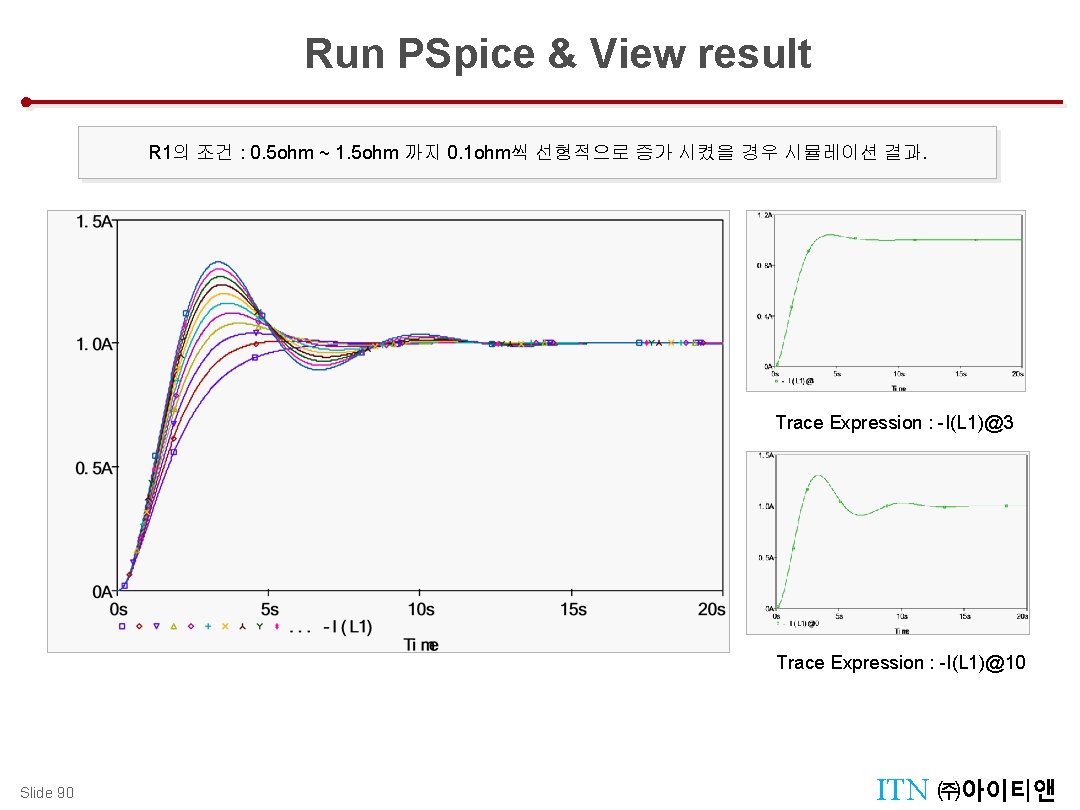

Run PSpice & View result R 1의 조건 : 0. 5 ohm ~ 1. 5 ohm 까지 0. 1 ohm씩 선형적으로 증가 시켰을 경우 시뮬레이션 결과. Trace Expression : -I(L 1)@3 Trace Expression : -I(L 1)@10 Slide 90 ITN ㈜아이티앤

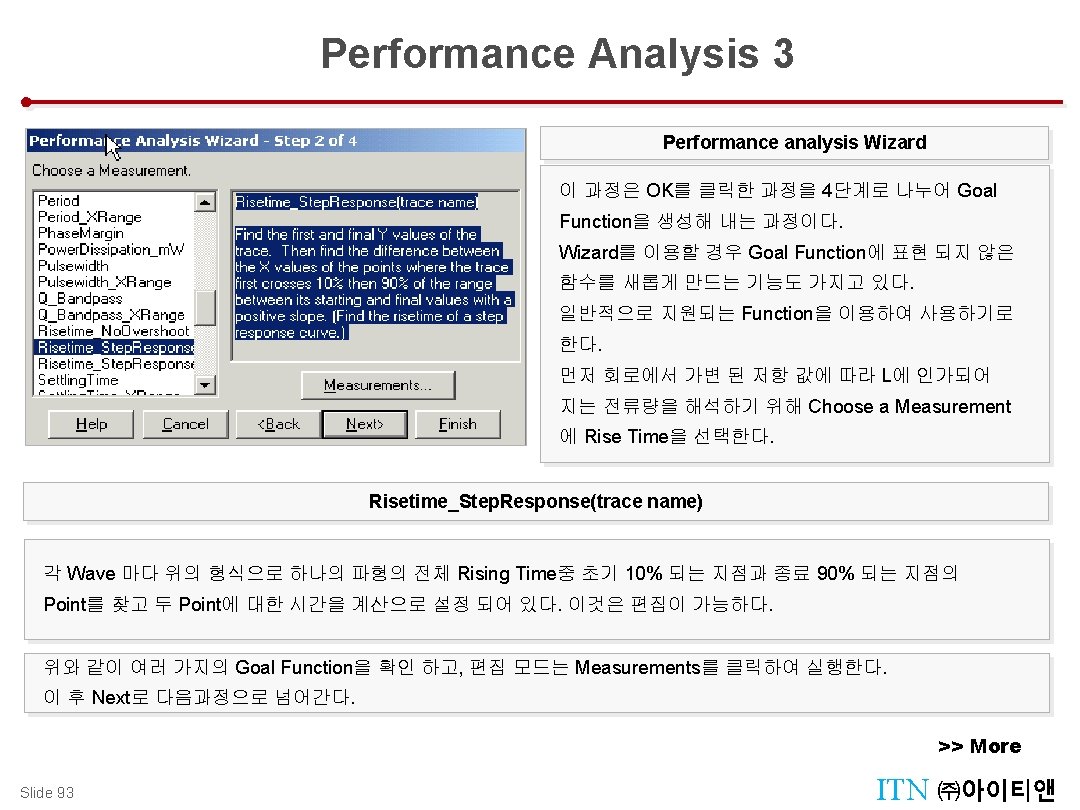

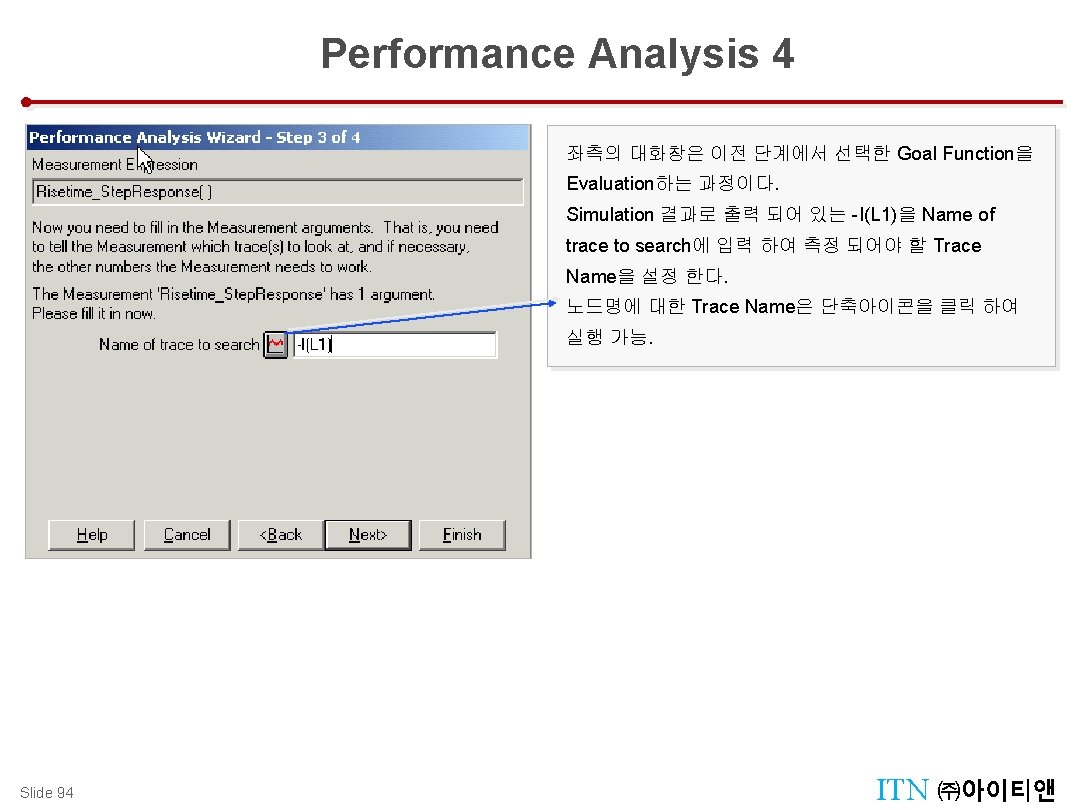

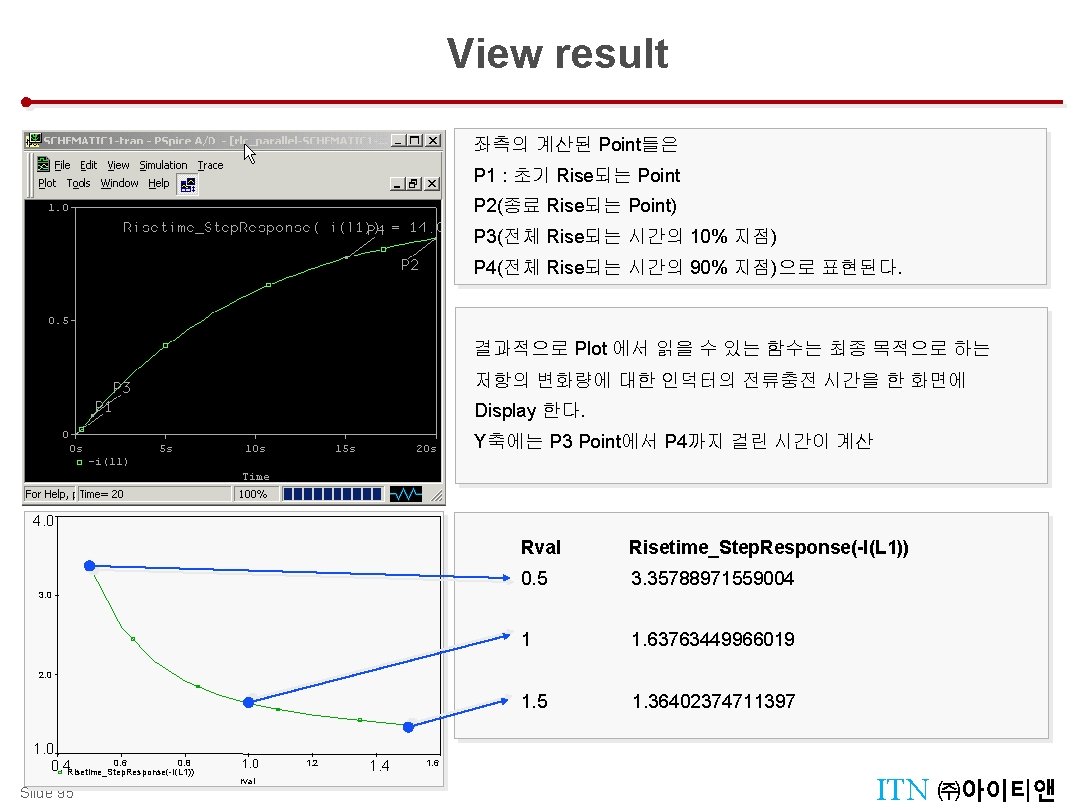

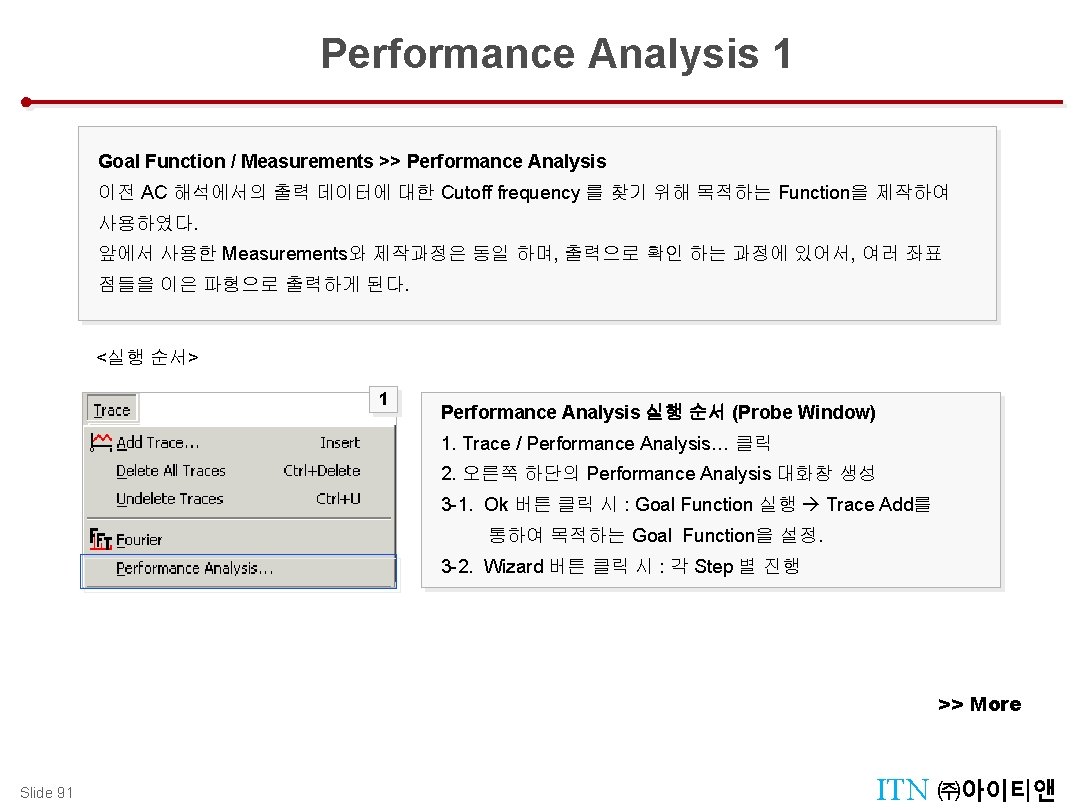

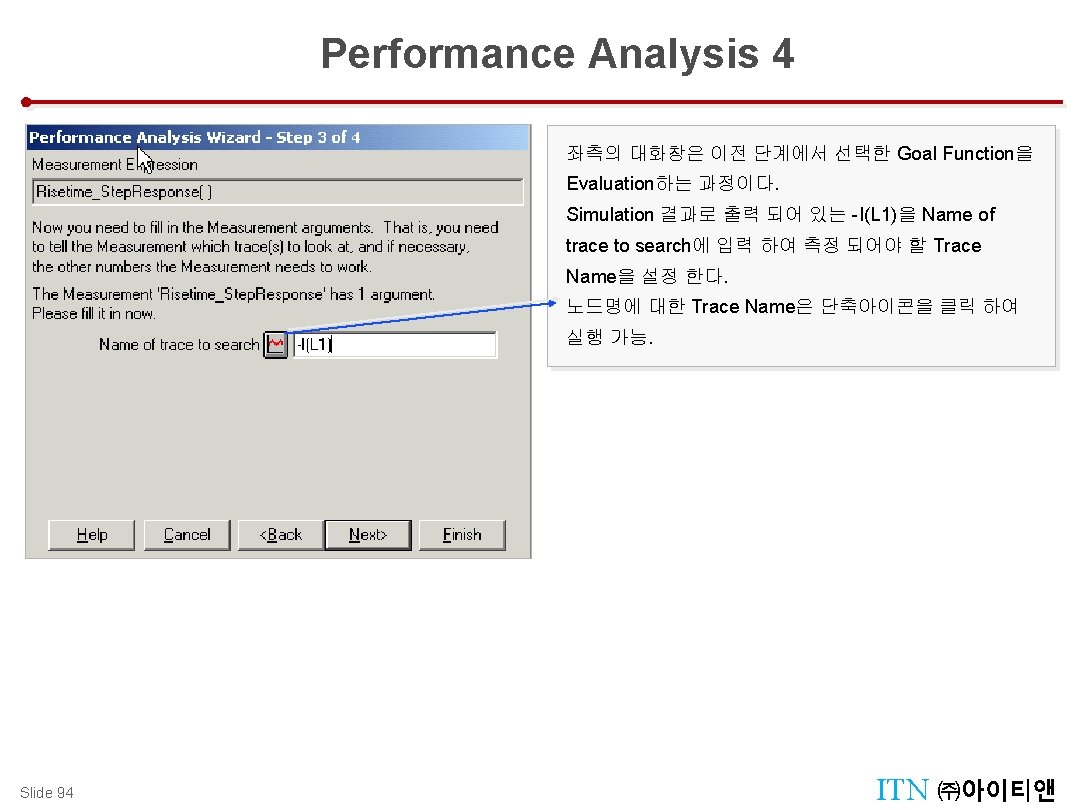

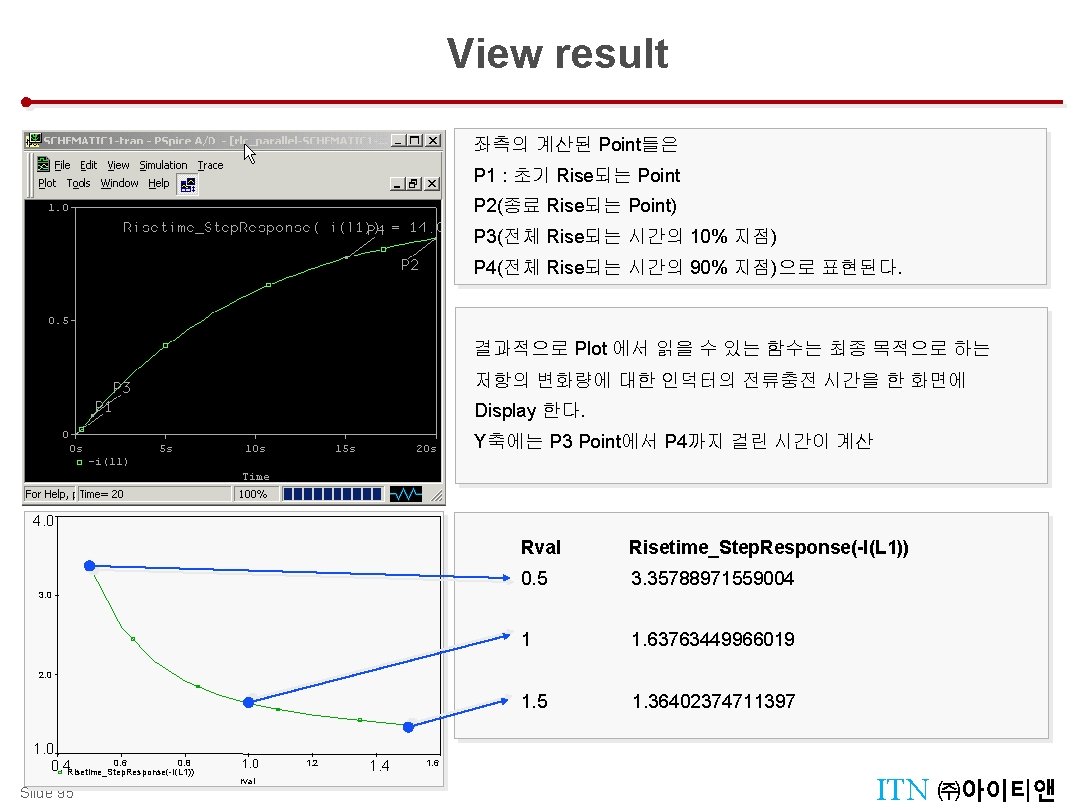

View result Performance analysis : Step 3 좌측의 계산된 Point들은 P 1 : 초기 Rise되는 Point P 2(종료 Rise되는 Point) P 3(전체 Rise되는 시간의 10% 지점) P 4(전체 Rise되는 시간의 90% 지점)으로 표현된다. 결과적으로 Plot 에서 읽을 수 있는 함수는 최종 목적으로 하는 저항의 변화량에 대한 인덕터의 전류충전 시간을 한 화면에 Display 한다. Y축에는 P 3 Point에서 P 4까지 걸린 시간이 계산 4. 0 Rval Risetime_Step. Response(-I(L 1)) 0. 5 3. 35788971559004 3. 0 1 1. 63763449966019 2. 0 1. 5 1. 0 0. 6 0. 8 0. 4 Risetime_Step. Response(-I(L 1)) Slide 95 1. 0 rval 1. 2 1. 4 1. 36402374711397 1. 6 ITN ㈜아이티앤

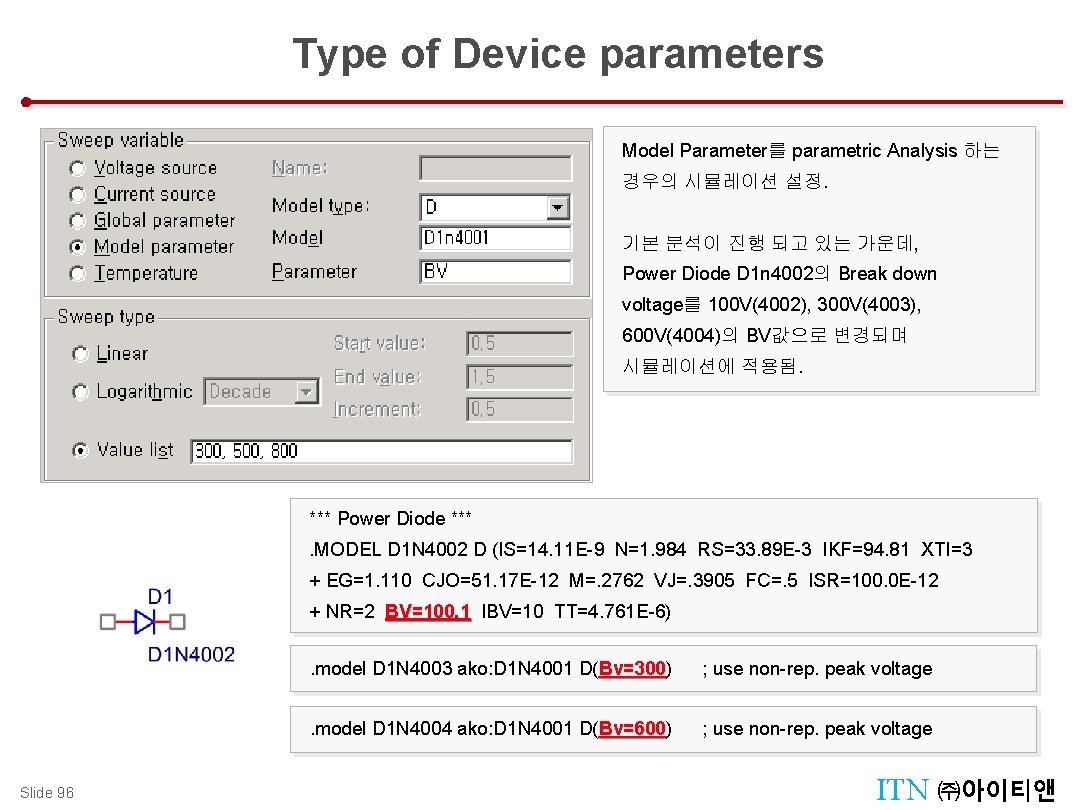

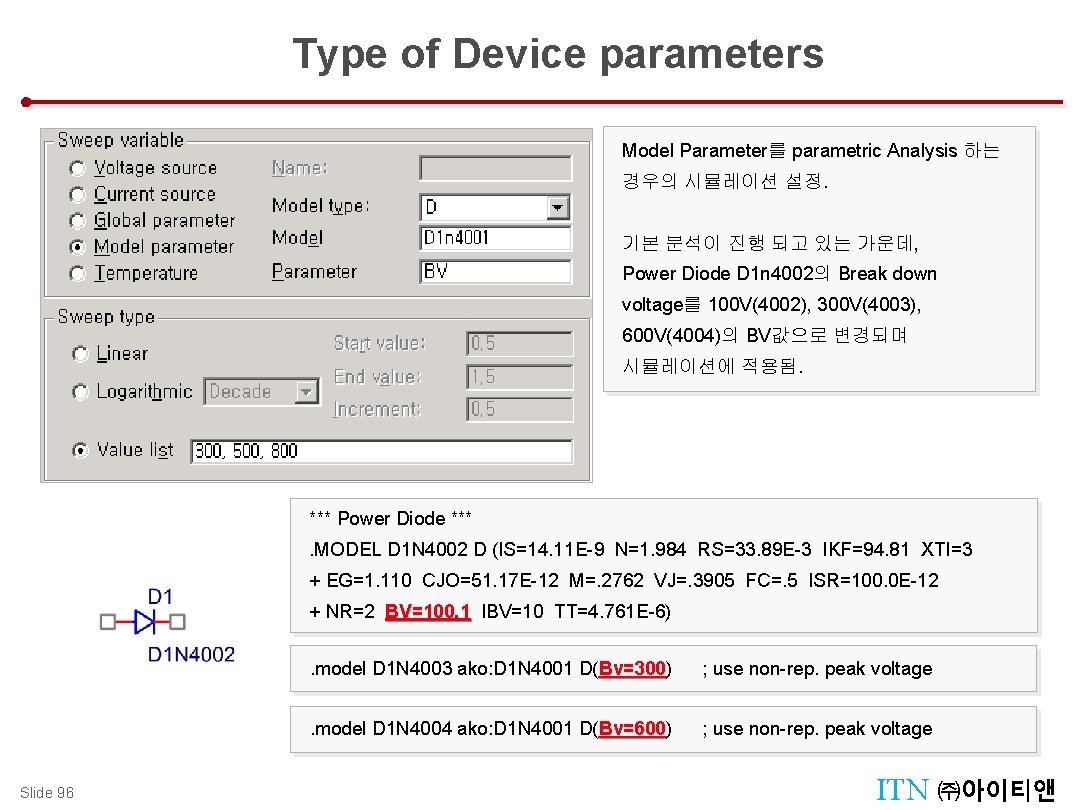

Type of Device parameters Model Parameter를 parametric Analysis 하는 경우의 시뮬레이션 설정. 기본 분석이 진행 되고 있는 가운데, Power Diode D 1 n 4002의 Break down voltage를 100 V(4002), 300 V(4003), 600 V(4004)의 BV값으로 변경되며 시뮬레이션에 적용됨. *** Power Diode ***. MODEL D 1 N 4002 D (IS=14. 11 E-9 N=1. 984 RS=33. 89 E-3 IKF=94. 81 XTI=3 + EG=1. 110 CJO=51. 17 E-12 M=. 2762 VJ=. 3905 FC=. 5 ISR=100. 0 E-12 + NR=2 BV=100. 1 IBV=10 TT=4. 761 E-6) BV=100. 1 Slide 96 . model D 1 N 4003 ako: D 1 N 4001 D(Bv=300) Bv=300 ; use non-rep. peak voltage . model D 1 N 4004 ako: D 1 N 4001 D(Bv=600) Bv=600 ; use non-rep. peak voltage ITN ㈜아이티앤

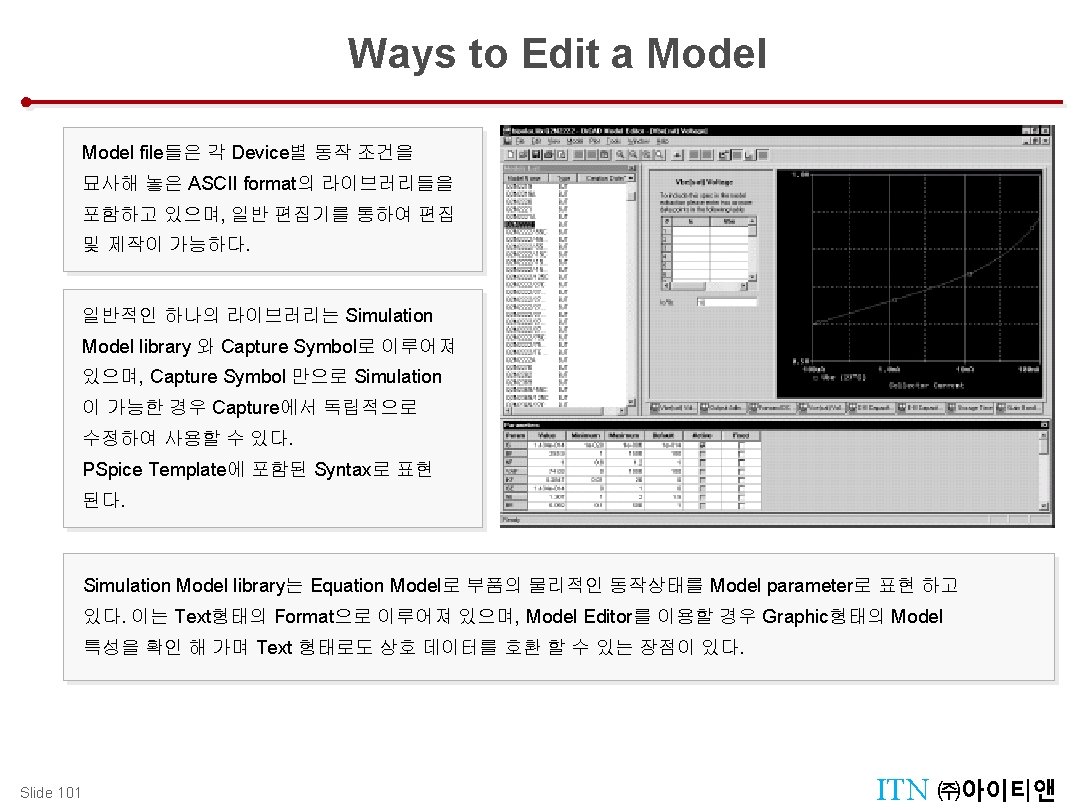

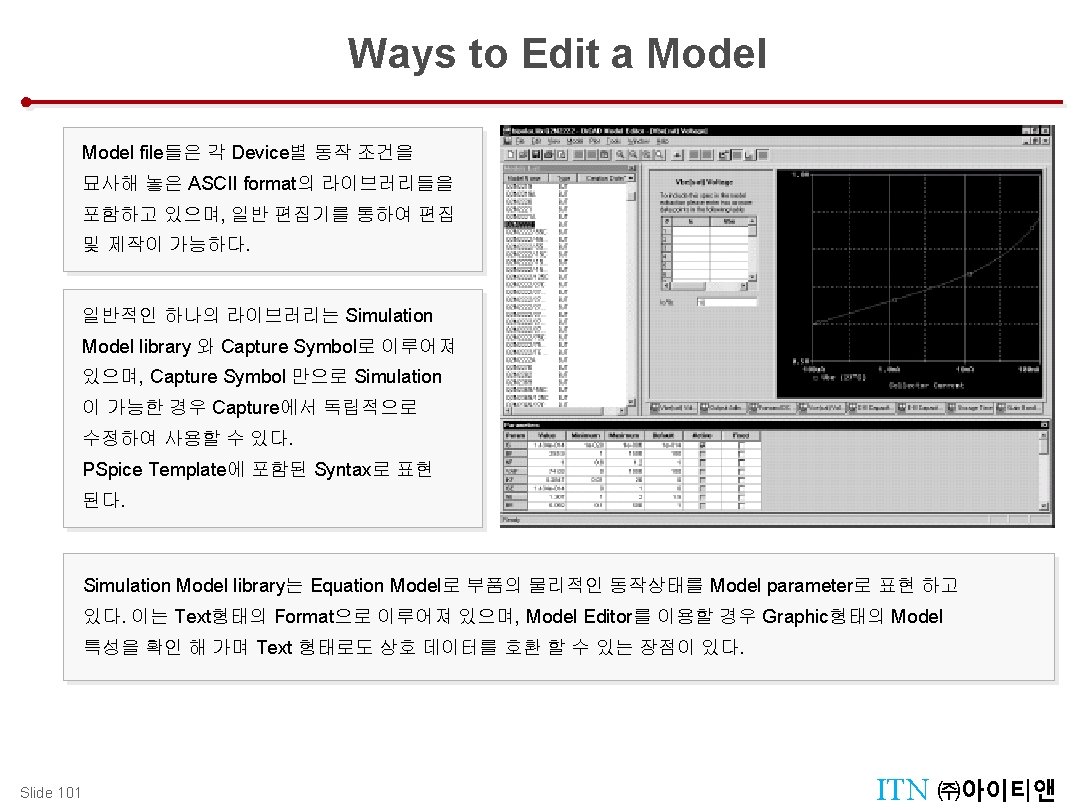

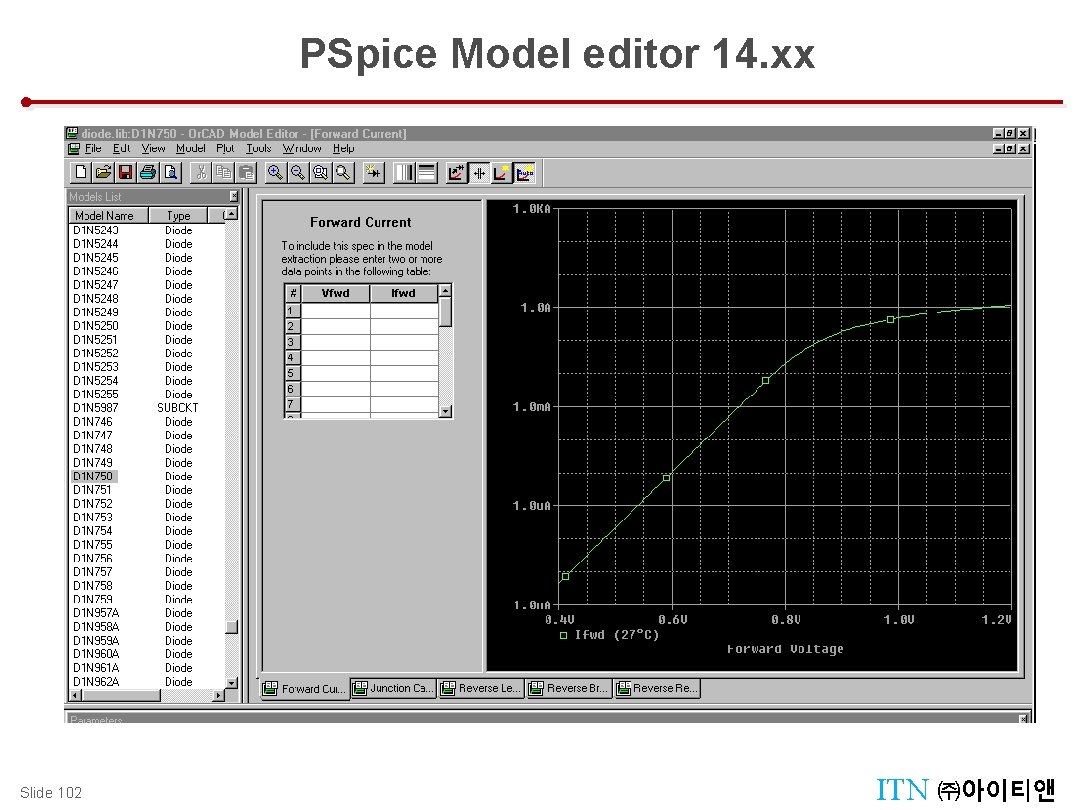

Design Management : Manager Tool Model Editor Way to edit a model PSpice model editor 14. xx PSpice model editor 14. 2 Web patch Local and Global model libraries Referencing a model Editing model parameter Model editor structure 1 (Model list) Model editor structure 2 (Spec entry) Model editor structure 3 ( Parameter table) Edit a Zener voltage Edit a diode model Slide 100 ITN ㈜아이티앤

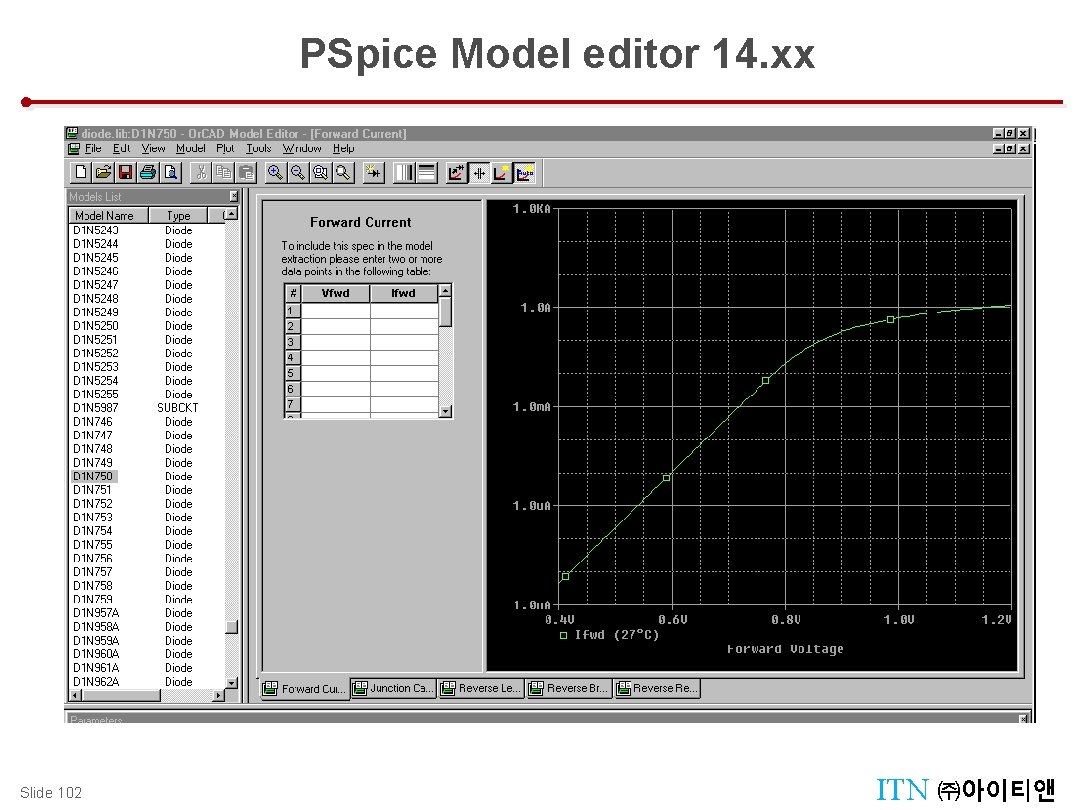

PSpice Model editor 14. xx Parametric Analysis (Temperature Sweep) Slide 102 ITN ㈜아이티앤

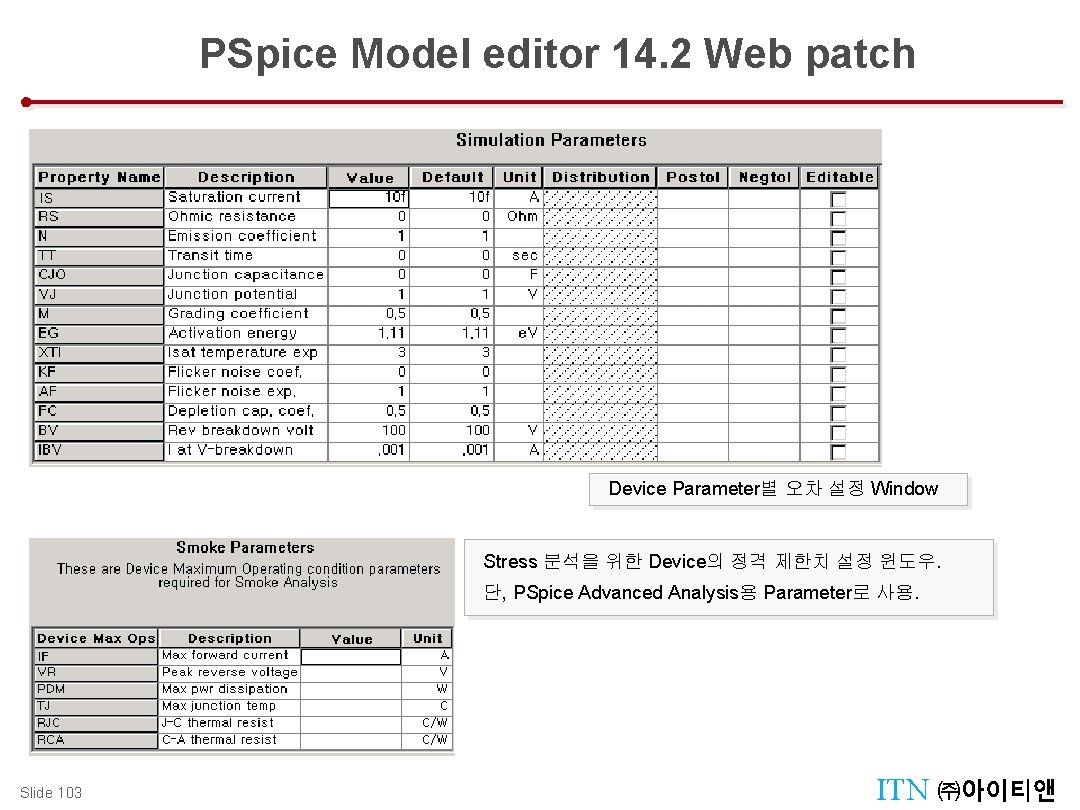

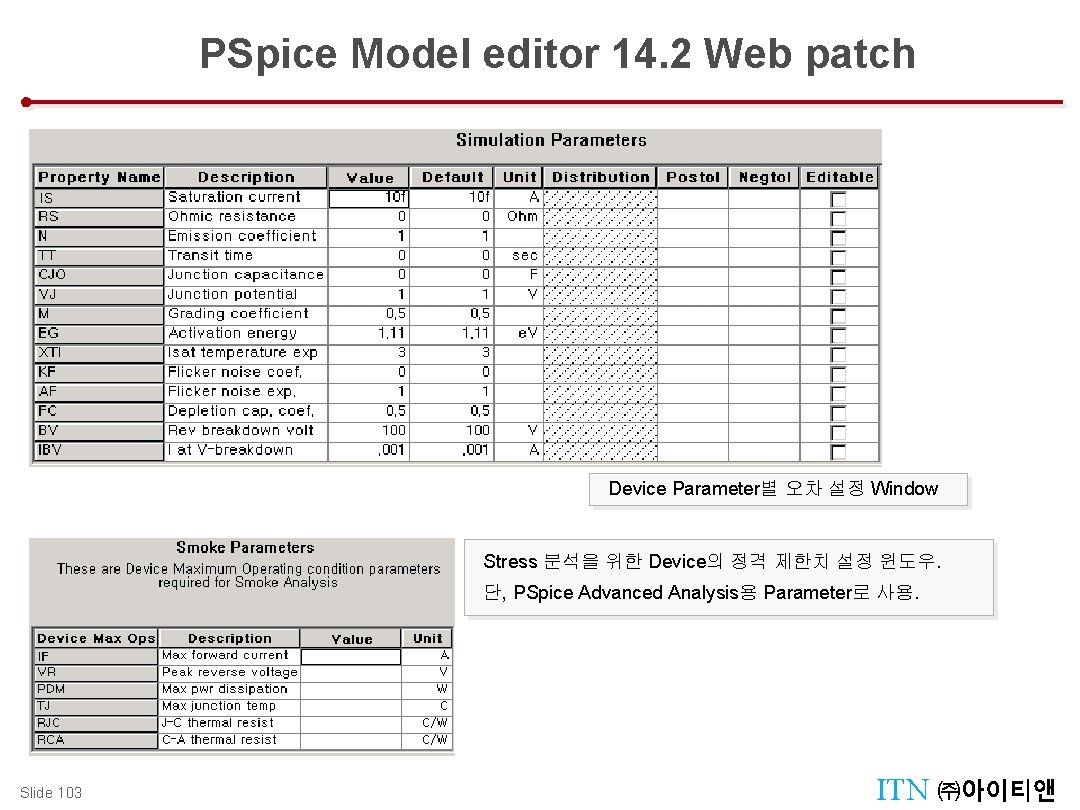

PSpice Model editor 14. 2 Web patch Parametric Analysis (Temperature Sweep) Device Parameter별 오차 설정 Window Stress 분석을 위한 Device의 정격 제한치 설정 윈도우. 단, PSpice Advanced Analysis용 Parameter로 사용. Slide 103 ITN ㈜아이티앤

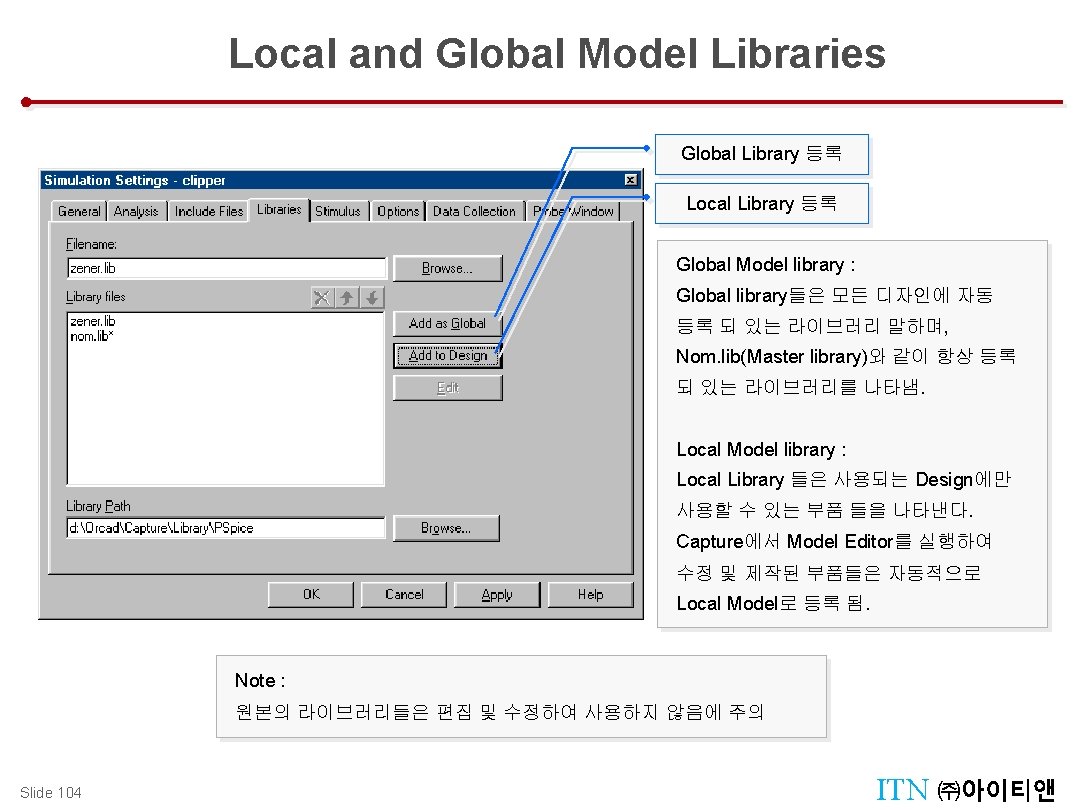

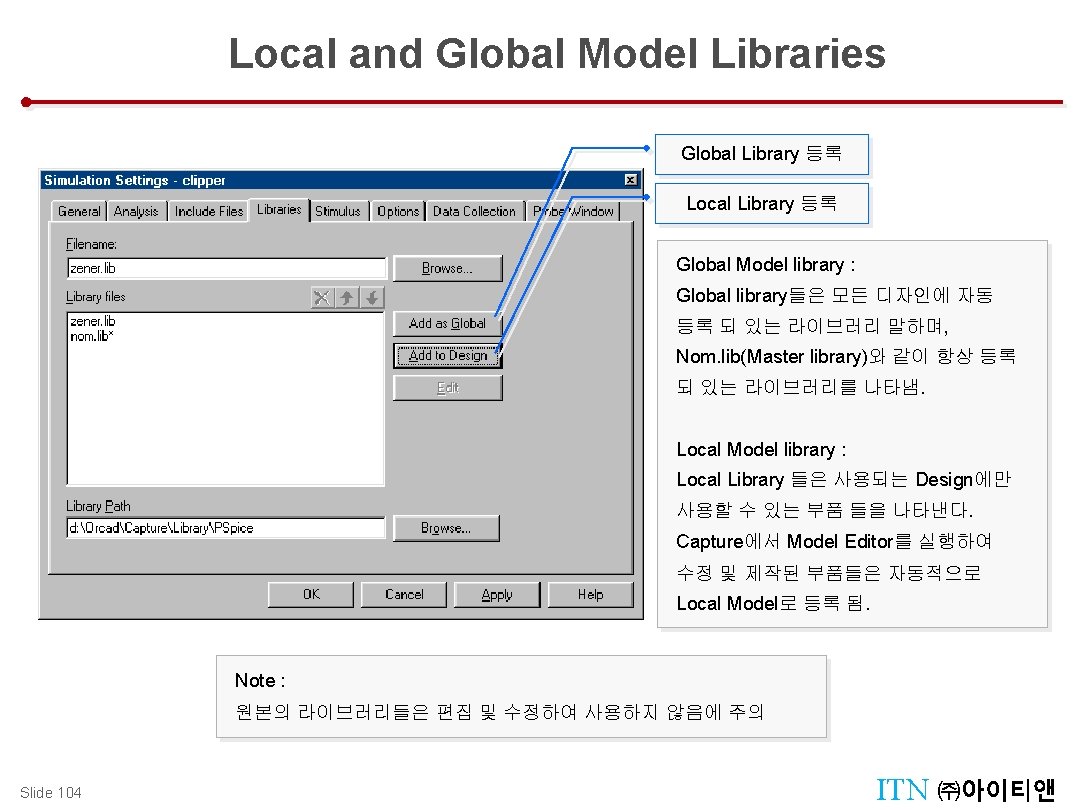

Local and Global Model Libraries Parametric Analysis (Temperature Sweep) Global Library 등록 Local Library 등록 Global Model library : Global library들은 모든 디자인에 자동 등록 되 있는 라이브러리 말하며, Nom. lib(Master library)와 같이 항상 등록 되 있는 라이브러리를 나타냄. Local Model library : Local Library 들은 사용되는 Design에만 사용할 수 있는 부품 들을 나타낸다. Capture에서 Model Editor를 실행하여 수정 및 제작된 부품들은 자동적으로 Local Model로 등록 됨. Note : 원본의 라이브러리들은 편집 및 수정하여 사용하지 않음에 주의 Slide 104 ITN ㈜아이티앤

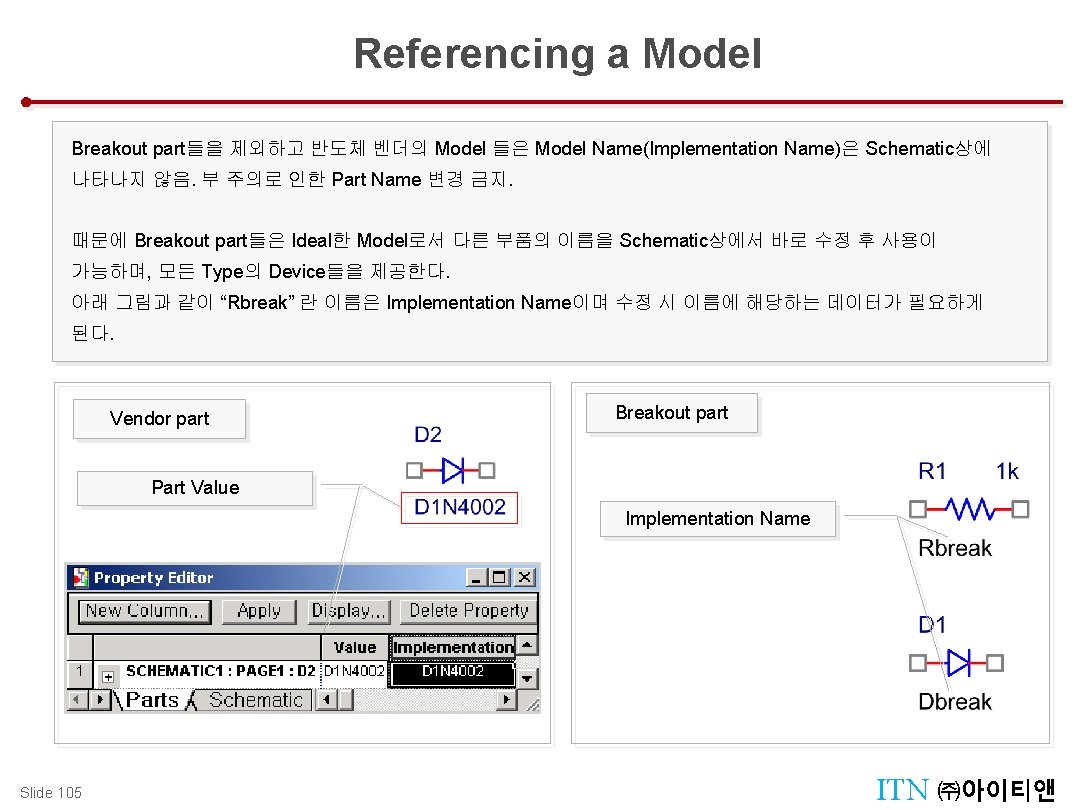

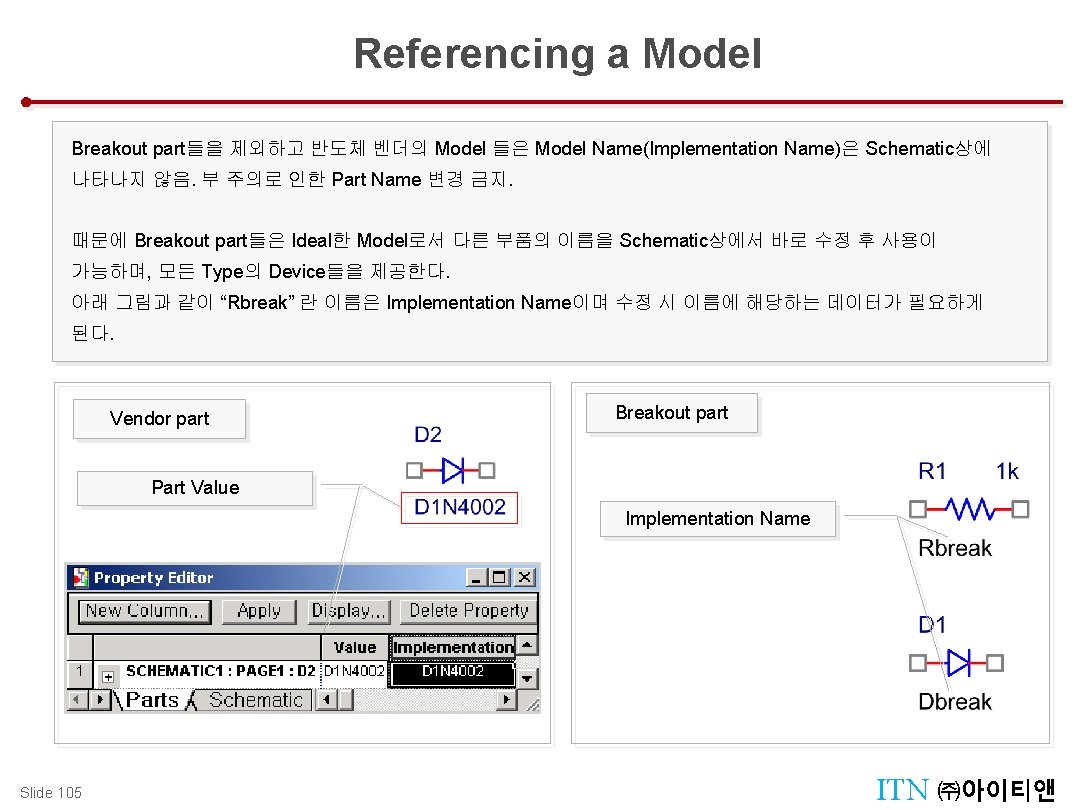

Referencing a Model Parametric Analysis (Temperature Sweep) Breakout part들을 제외하고 반도체 벤더의 Model 들은 Model Name(Implementation Name)은 Schematic상에 나타나지 않음. 부 주의로 인한 Part Name 변경 금지. 때문에 Breakout part들은 Ideal한 Model로서 다른 부품의 이름을 Schematic상에서 바로 수정 후 사용이 가능하며, 모든 Type의 Device들을 제공한다. 아래 그림과 같이 “Rbreak” 란 이름은 Implementation Name이며 수정 시 이름에 해당하는 데이터가 필요하게 된다. Vendor part Breakout part Part Value Implementation Name Slide 105 ITN ㈜아이티앤

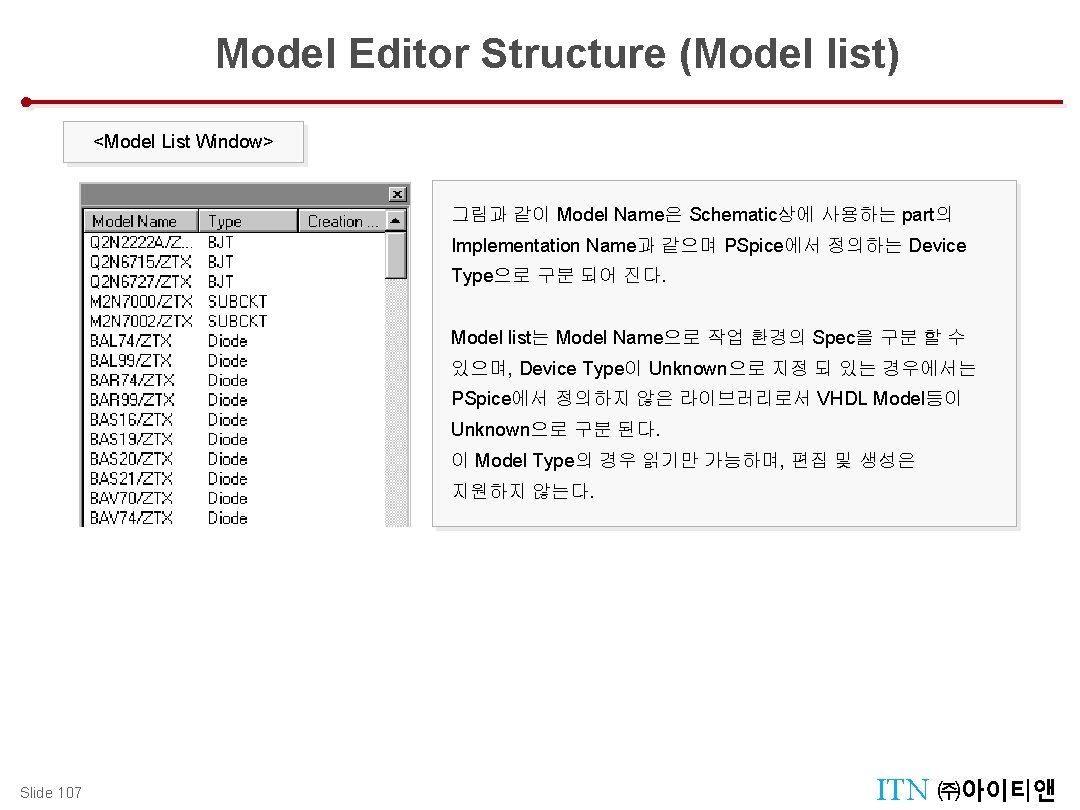

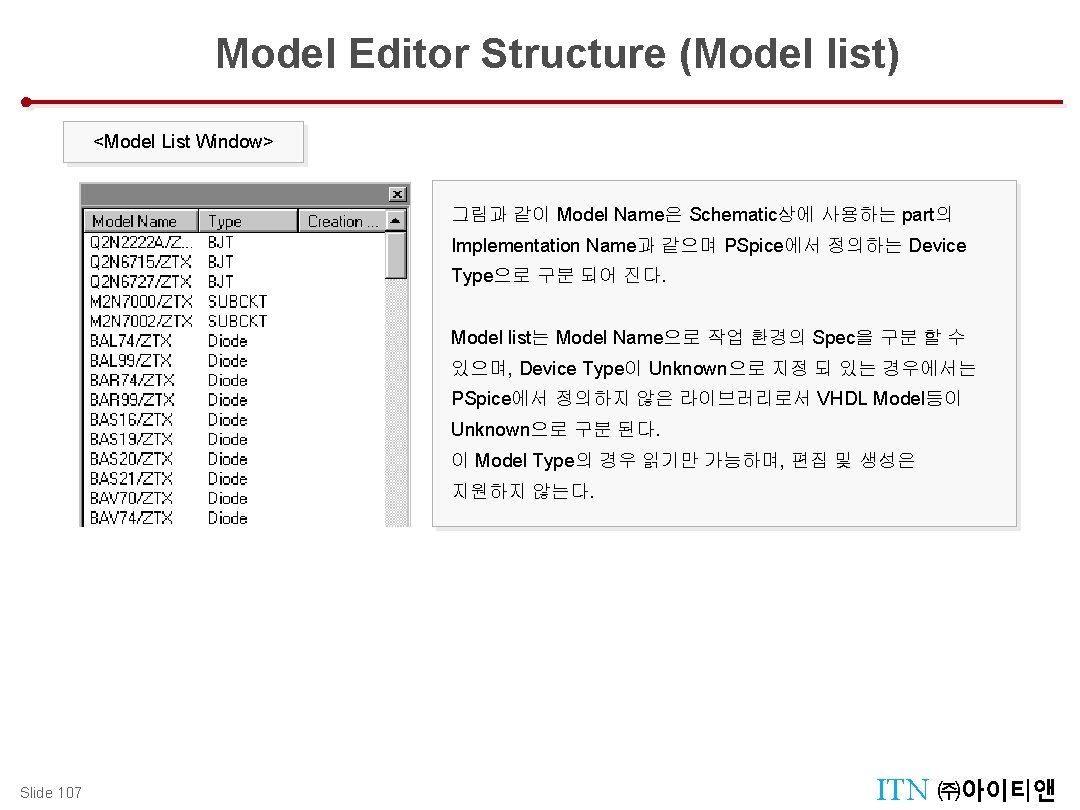

Model Editor Structure (Model list) Parametric Analysis (Temperature Sweep) <Model List Window> 그림과 같이 Model Name은 Schematic상에 사용하는 part의 Implementation Name과 같으며 PSpice에서 정의하는 Device Type으로 구분 되어 진다. Model list는 Model Name으로 작업 환경의 Spec을 구분 할 수 있으며, Device Type이 Unknown으로 지정 되 있는 경우에서는 PSpice에서 정의하지 않은 라이브러리로서 VHDL Model등이 Unknown으로 구분 된다. 이 Model Type의 경우 읽기만 가능하며, 편집 및 생성은 지원하지 않는다. Slide 107 ITN ㈜아이티앤

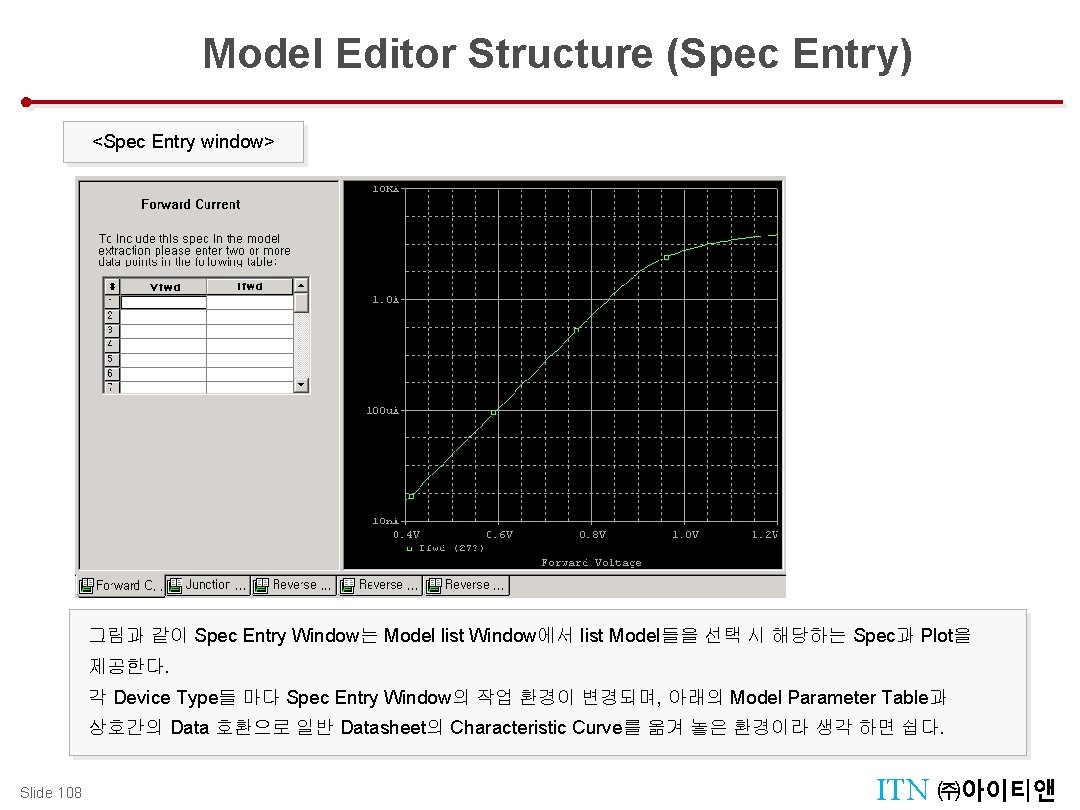

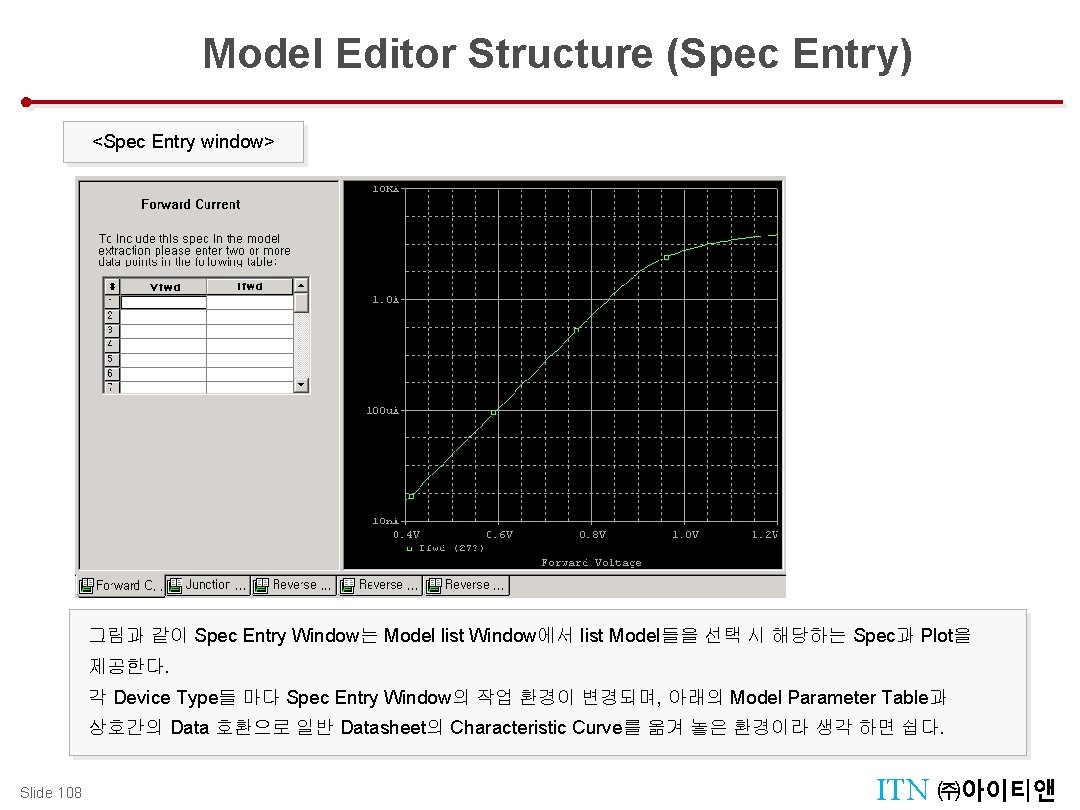

Model Editor Structure (Spec Entry) Parametric Analysis (Temperature Sweep) <Spec Entry window> 그림과 같이 Spec Entry Window는 Model list Window에서 list Model들을 선택 시 해당하는 Spec과 Plot을 제공한다. 각 Device Type들 마다 Spec Entry Window의 작업 환경이 변경되며, 아래의 Model Parameter Table과 상호간의 Data 호환으로 일반 Datasheet의 Characteristic Curve를 옮겨 놓은 환경이라 생각 하면 쉽다. Slide 108 ITN ㈜아이티앤

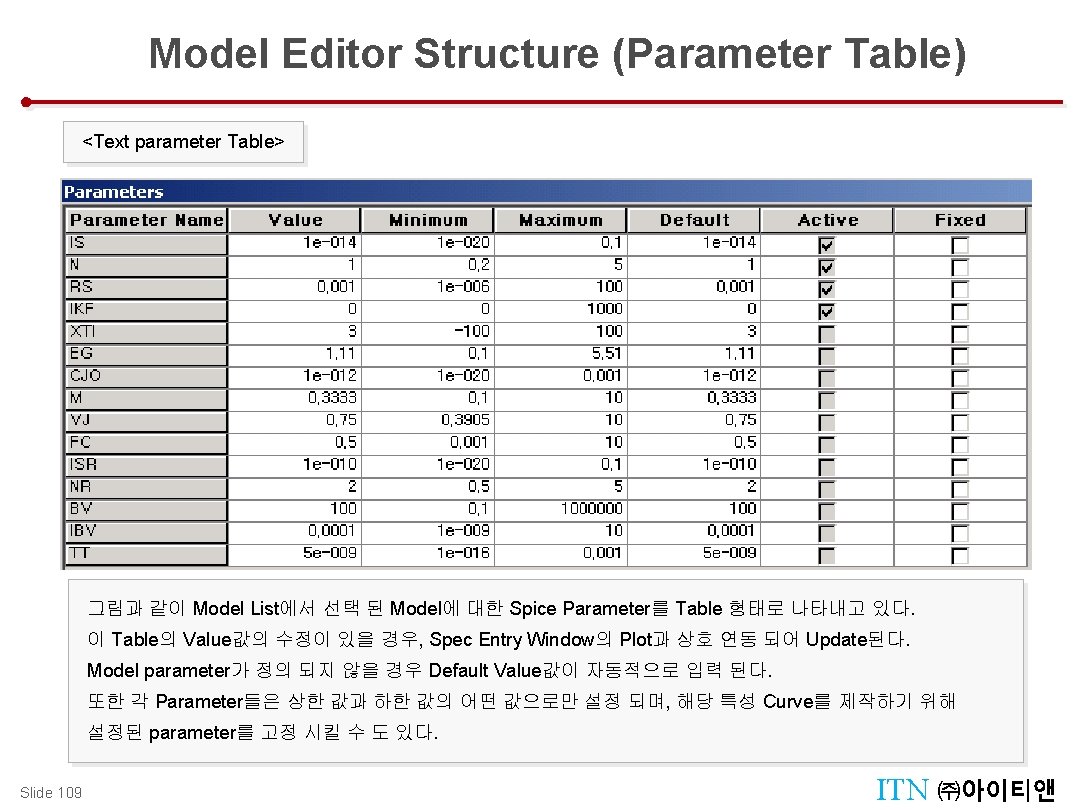

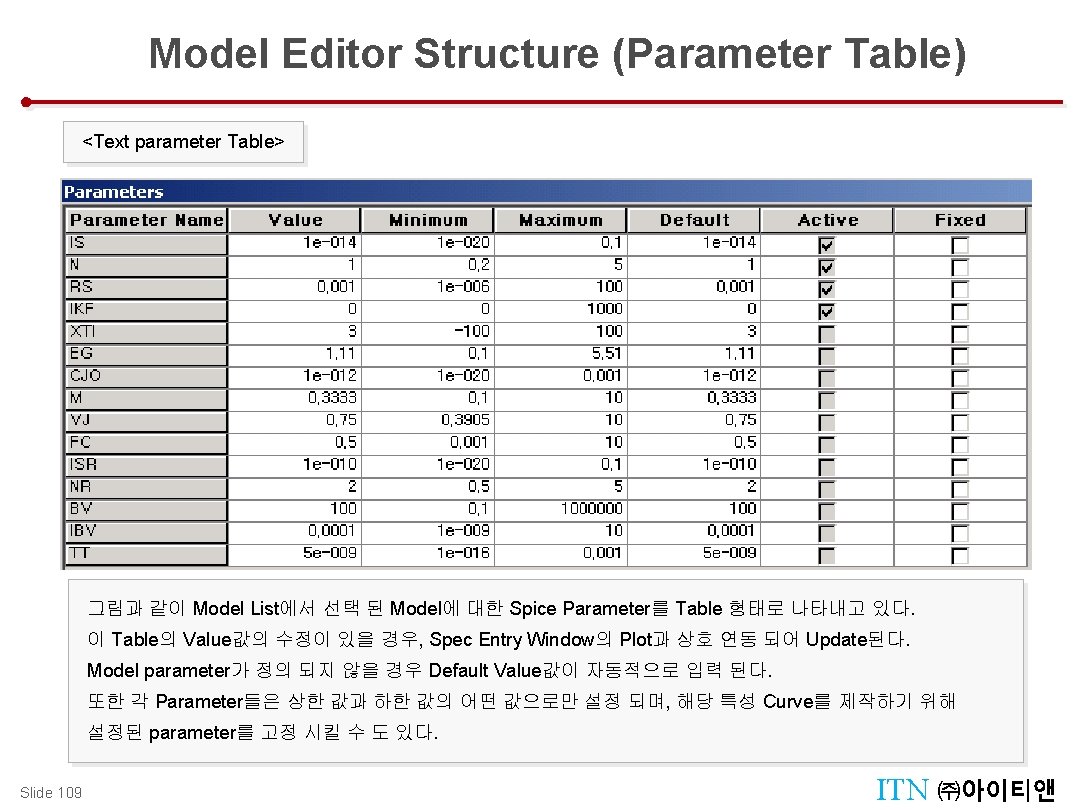

Model Editor Structure (Parameter Table) Parametric Analysis (Temperature Sweep) <Text parameter Table> 그림과 같이 Model List에서 선택 된 Model에 대한 Spice Parameter를 Table 형태로 나타내고 있다. 이 Table의 Value값의 수정이 있을 경우, Spec Entry Window의 Plot과 상호 연동 되어 Update된다. Model parameter가 정의 되지 않을 경우 Default Value값이 자동적으로 입력 된다. 또한 각 Parameter들은 상한 값과 하한 값의 어떤 값으로만 설정 되며, 해당 특성 Curve를 제작하기 위해 설정된 parameter를 고정 시킬 수 도 있다. Slide 109 ITN ㈜아이티앤

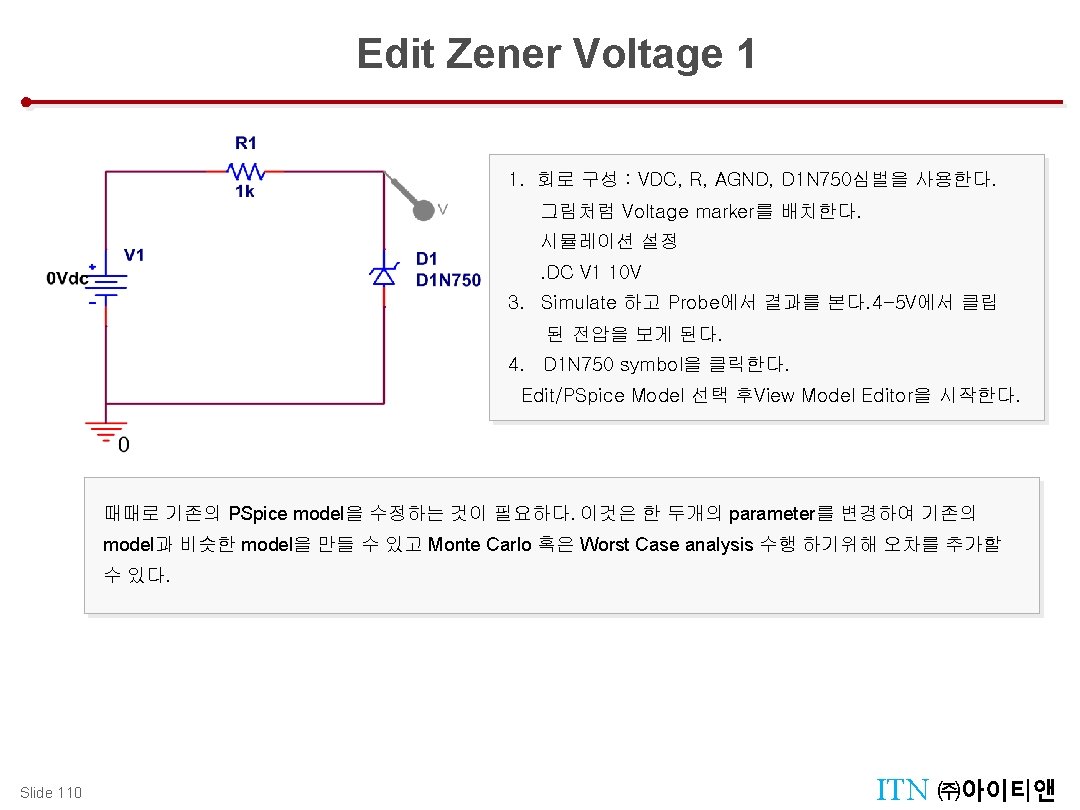

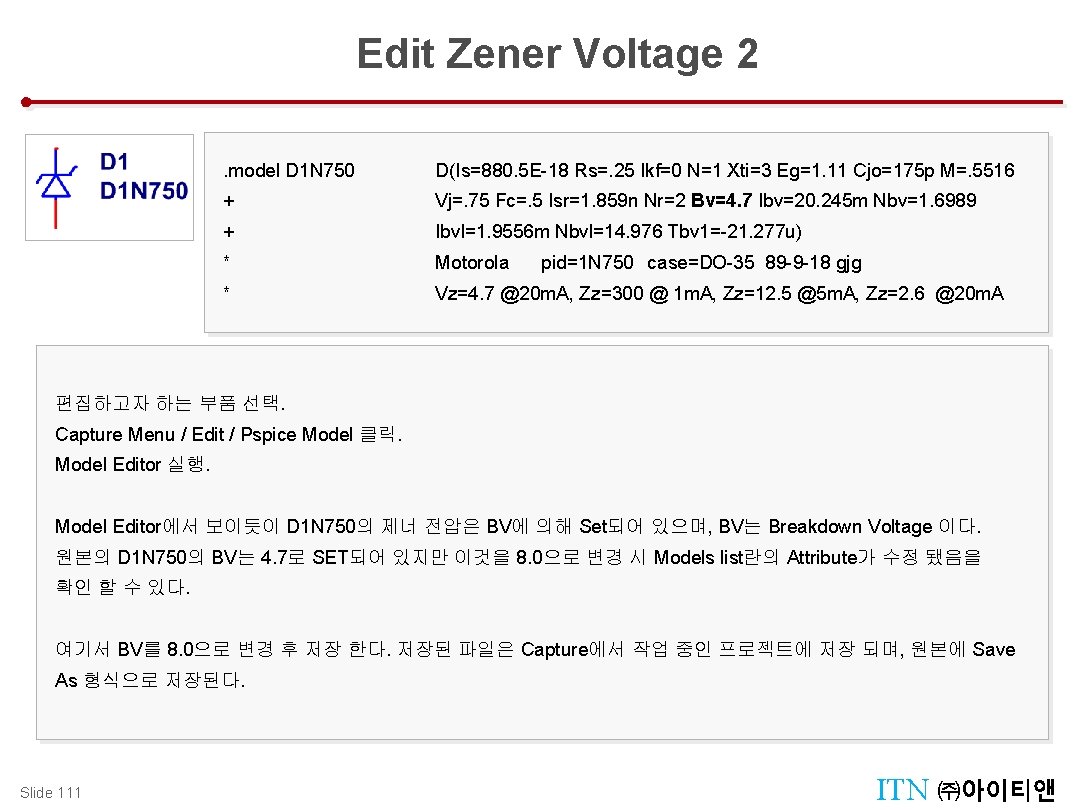

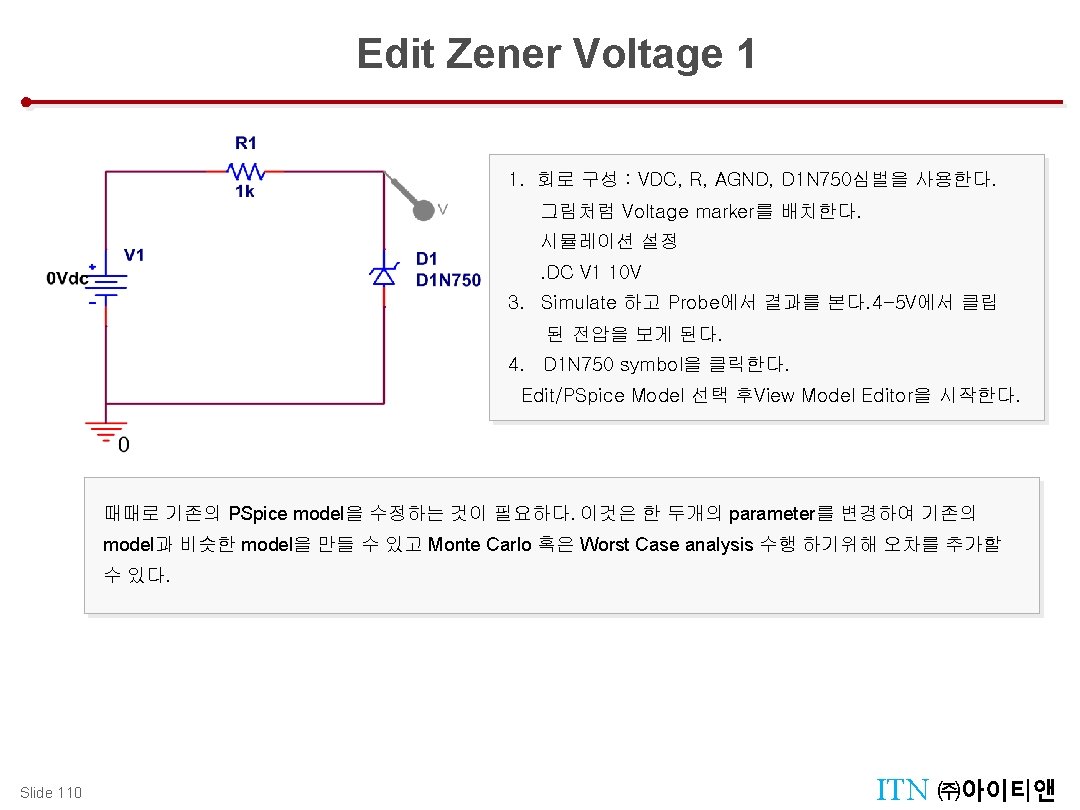

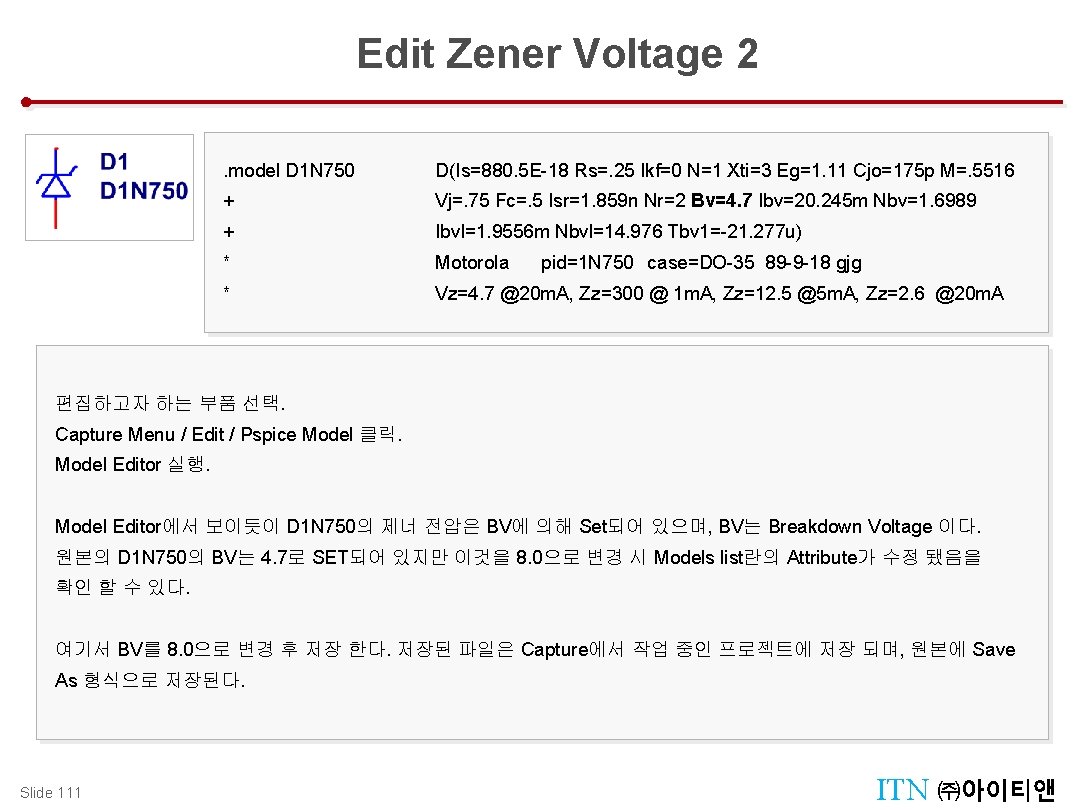

Edit Zener Voltage 2 Model Editor . model D 1 N 750 D(Is=880. 5 E-18 Rs=. 25 Ikf=0 N=1 Xti=3 Eg=1. 11 Cjo=175 p M=. 5516 + Vj=. 75 Fc=. 5 Isr=1. 859 n Nr=2 Bv=4. 7 Ibv=20. 245 m Nbv=1. 6989 + Ibvl=1. 9556 m Nbvl=14. 976 Tbv 1=-21. 277 u) * Motorola * Vz=4. 7 @20 m. A, Zz=300 @ 1 m. A, Zz=12. 5 @5 m. A, Zz=2. 6 @20 m. A pid=1 N 750 case=DO-35 89 -9 -18 gjg 편집하고자 하는 부품 선택. Capture Menu / Edit / Pspice Model 클릭. Model Editor 실행. Model Editor에서 보이듯이 D 1 N 750의 제너 전압은 BV에 의해 Set되어 있으며, BV는 Breakdown Voltage 이다. 원본의 D 1 N 750의 BV는 4. 7로 SET되어 있지만 이것을 8. 0으로 변경 시 Models list란의 Attribute가 수정 됐음을 확인 할 수 있다. 여기서 BV를 8. 0으로 변경 후 저장 한다. 저장된 파일은 Capture에서 작업 중인 프로젝트에 저장 되며, 원본에 Save As 형식으로 저장된다. Slide 111 ITN ㈜아이티앤

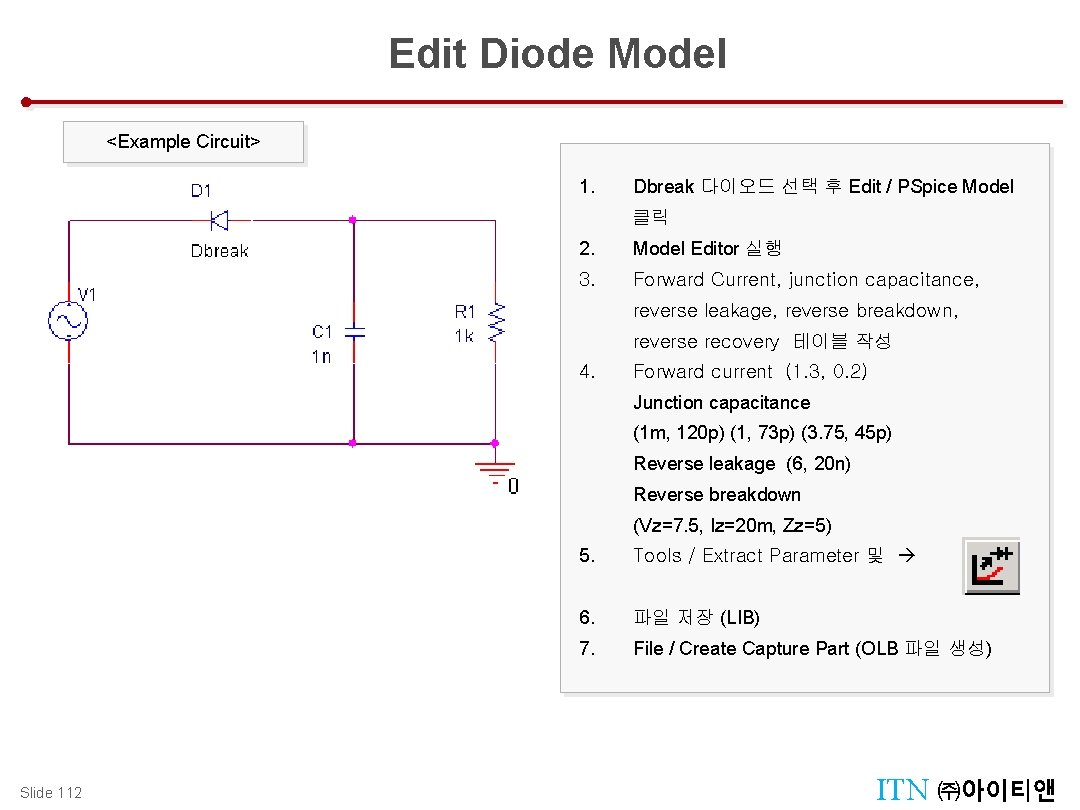

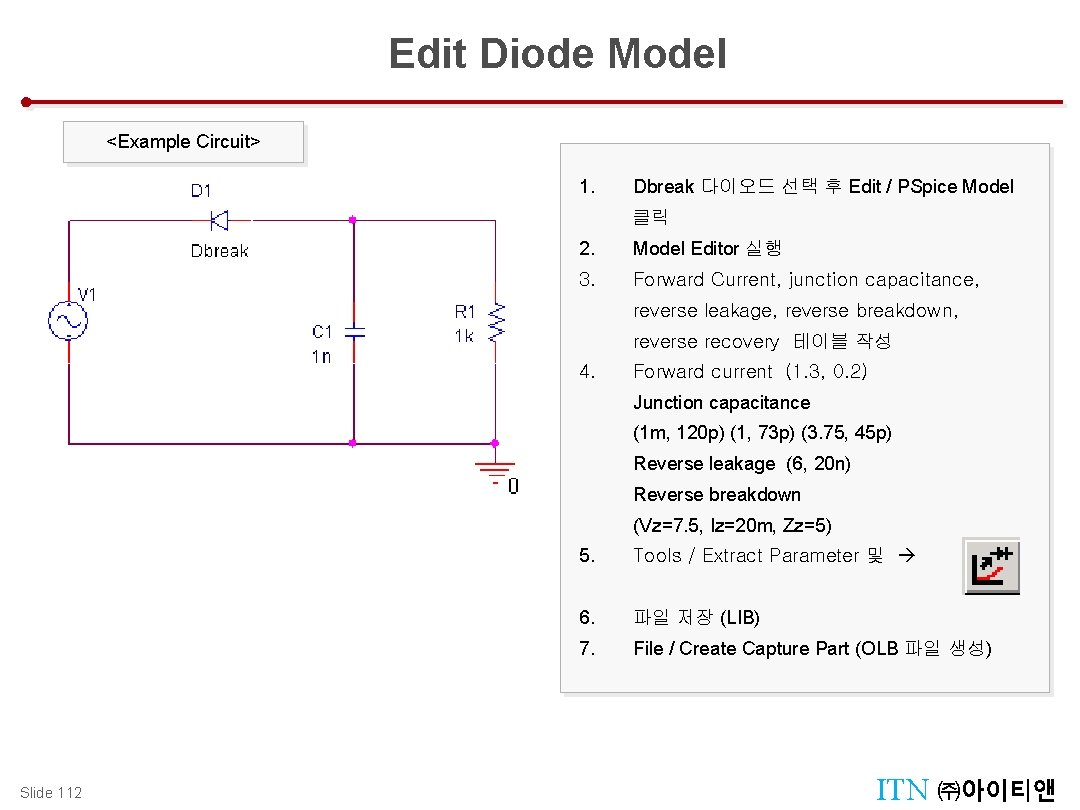

Edit Diode Model Parametric Analysis (Temperature Sweep) <Example Circuit> 1. Dbreak 다이오드 선택 후 Edit / PSpice Model 클릭 2. Model Editor 실행 3. Forward Current, junction capacitance, reverse leakage, reverse breakdown, reverse recovery 테이블 작성 4. Forward current (1. 3, 0. 2) Junction capacitance (1 m, 120 p) (1, 73 p) (3. 75, 45 p) Reverse leakage (6, 20 n) Reverse breakdown (Vz=7. 5, Iz=20 m, Zz=5) Slide 112 5. Tools / Extract Parameter 및 6. 파일 저장 (LIB) 7. File / Create Capture Part (OLB 파일 생성) ITN ㈜아이티앤

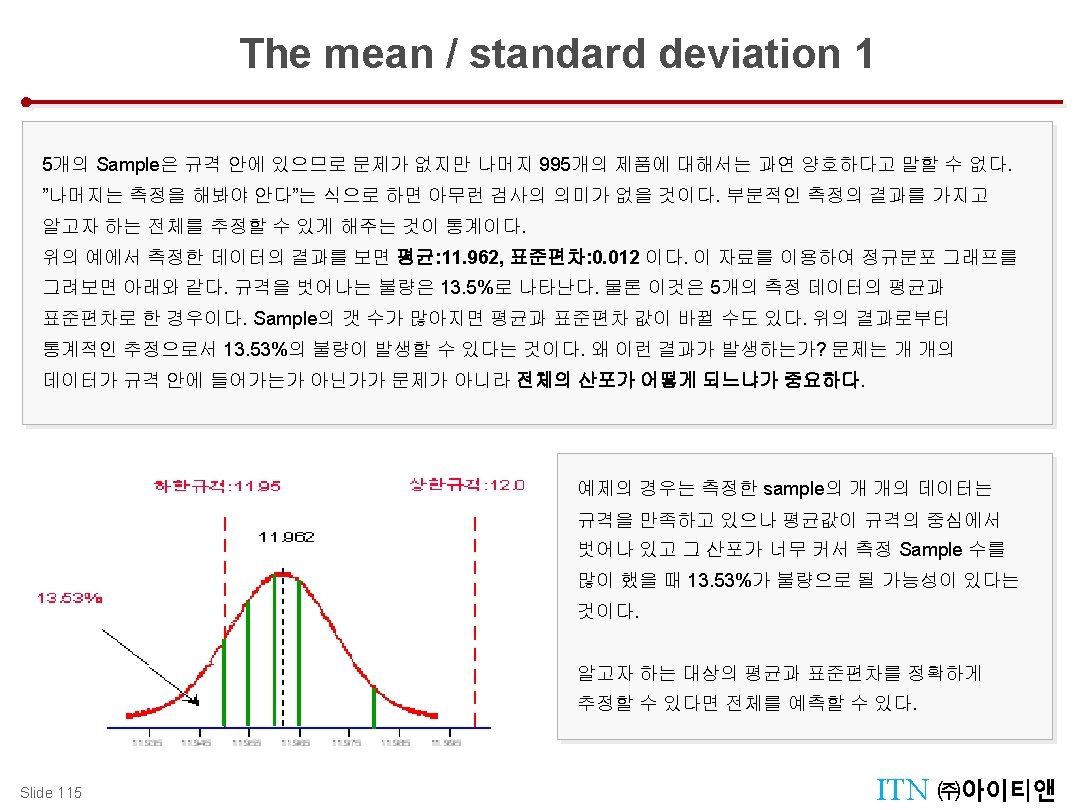

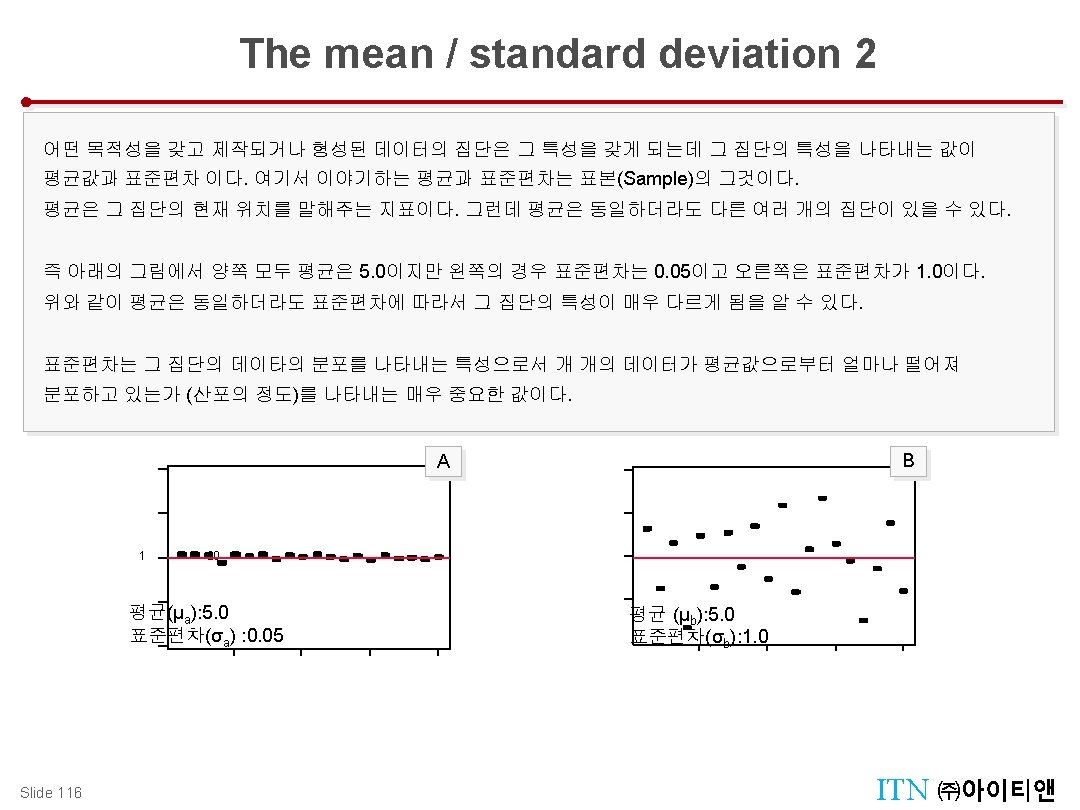

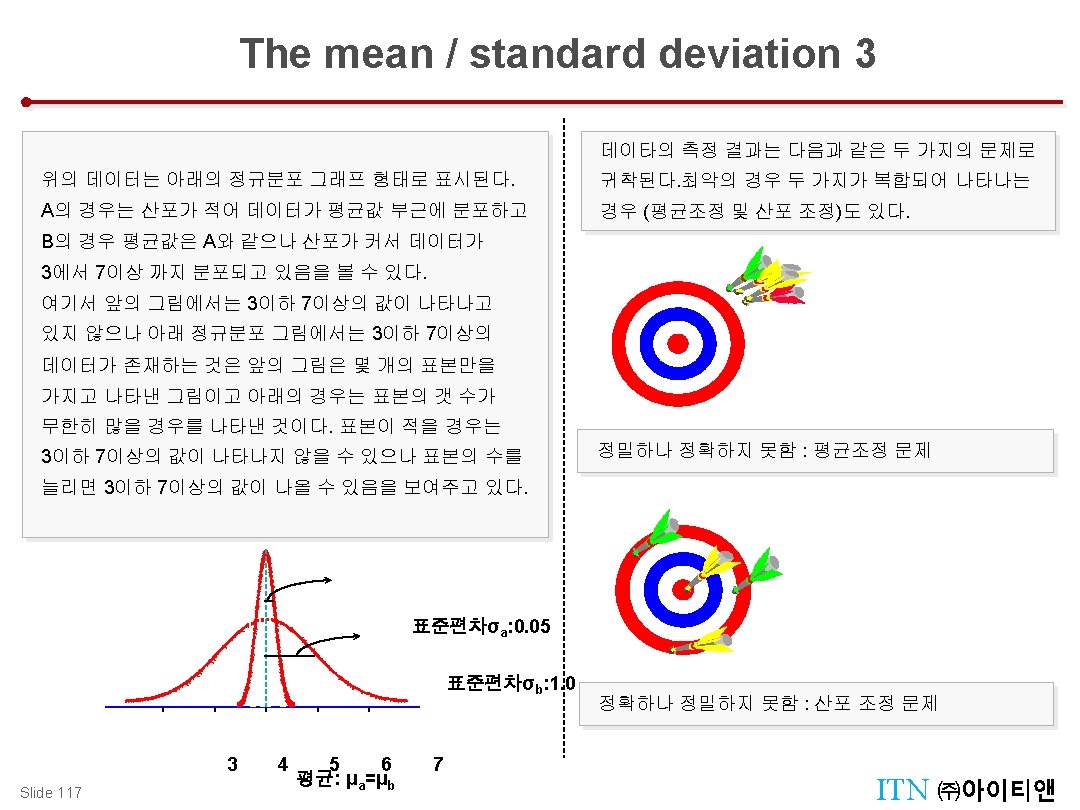

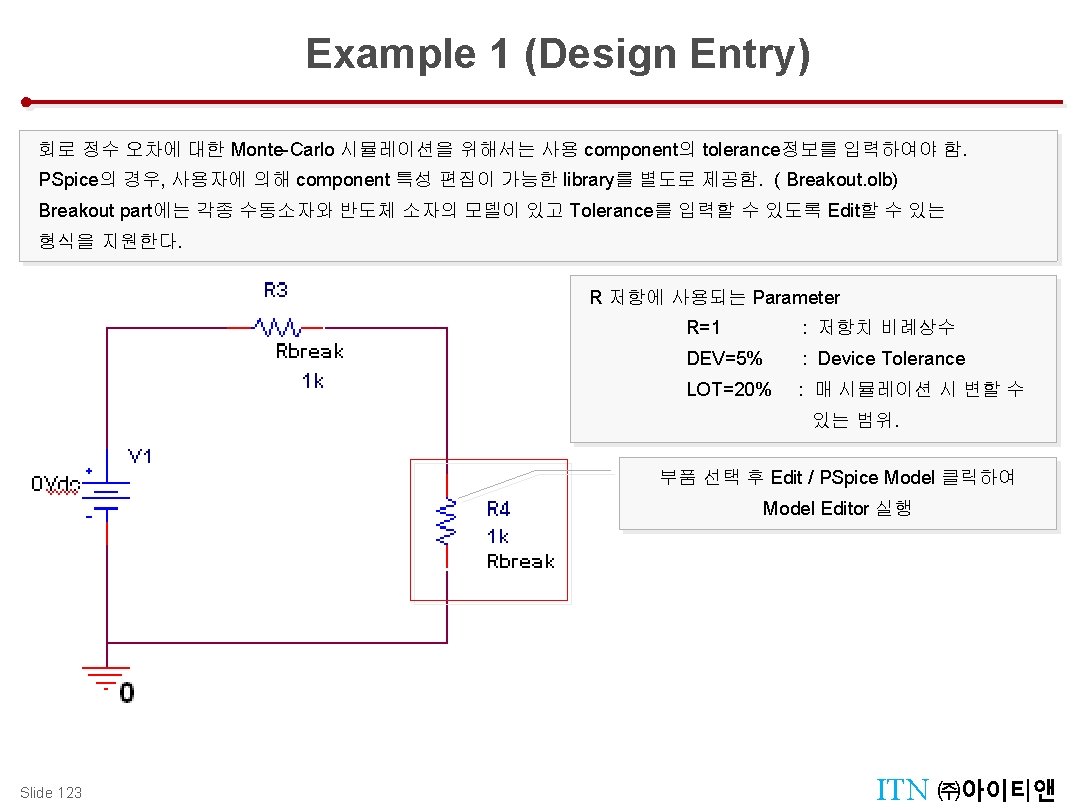

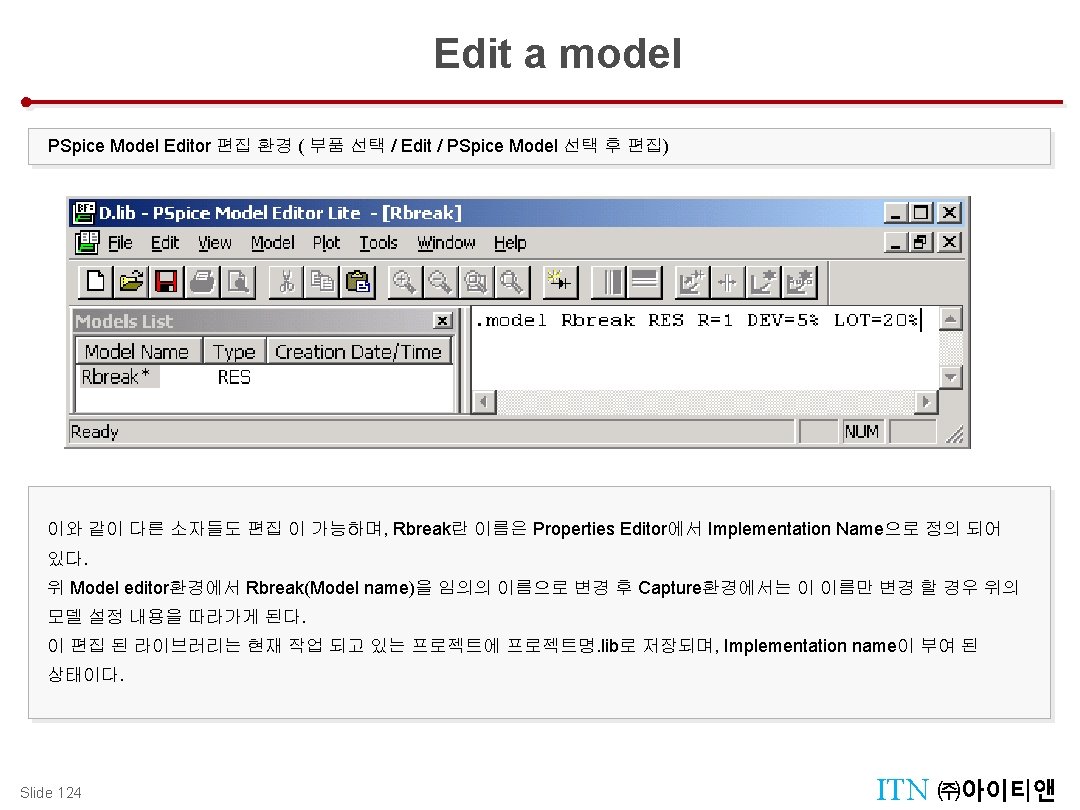

Monte Carlo Analysis Design Management : Manager Tool Statistical analysis The Mean / Standard Deviation Device and Lot Tolerances Setting up MC Analysis Setting up WC Analysis View Result & Histograms Example 1 (Design Entry) Edit a model Run pspice & performance Analysis View result & histogram Example 2 Slide 113 ITN ㈜아이티앤

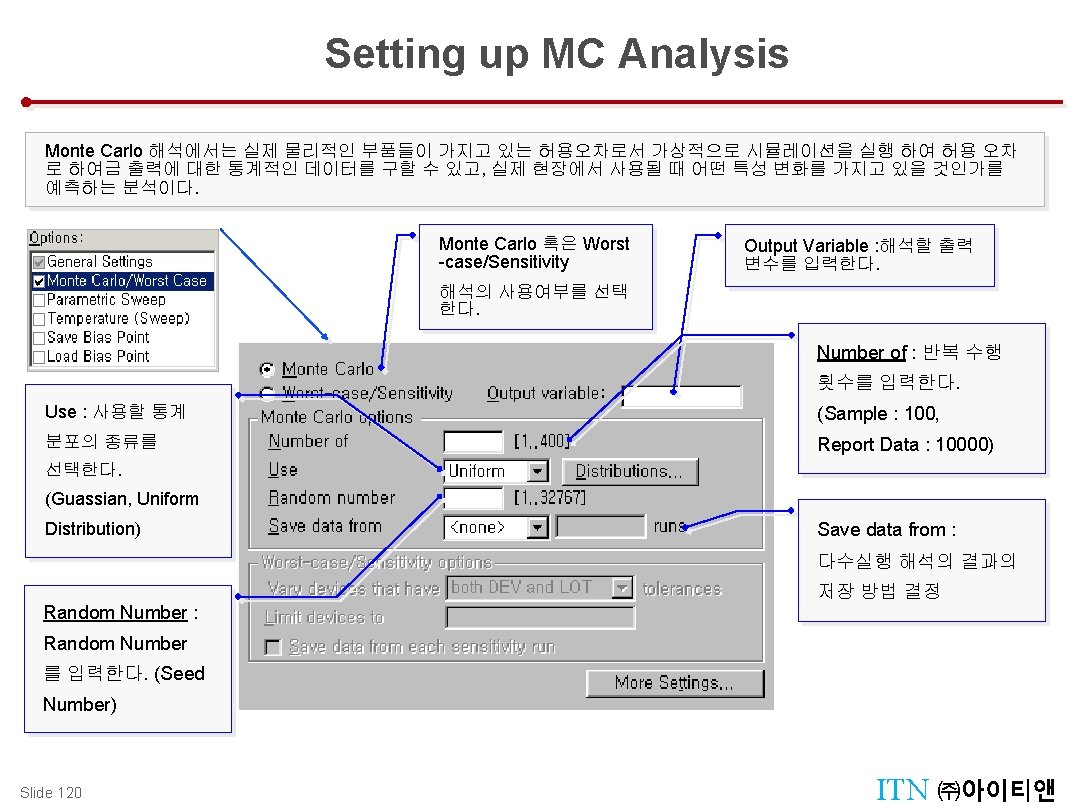

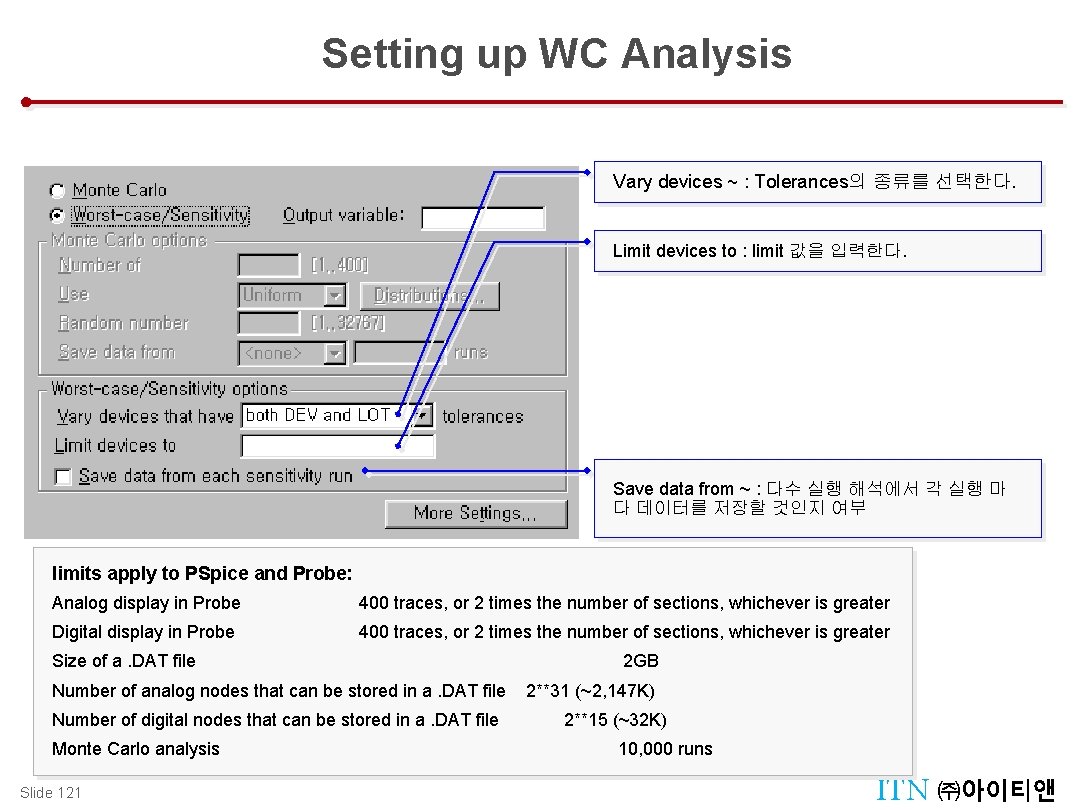

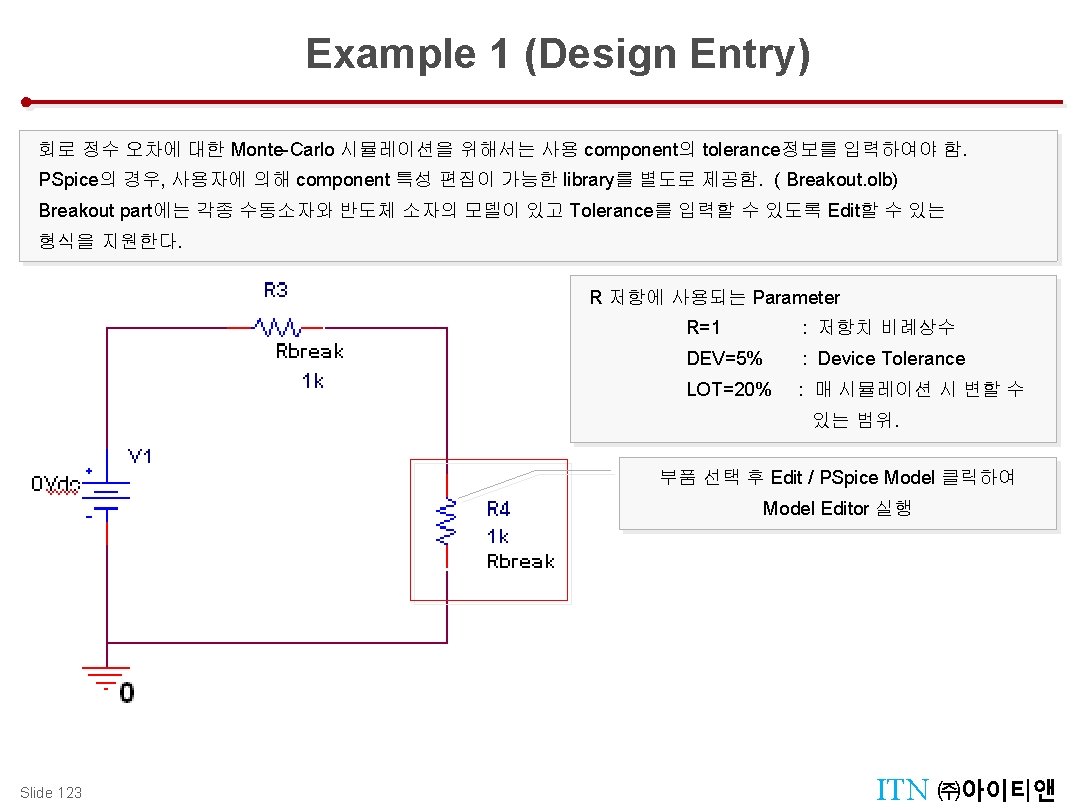

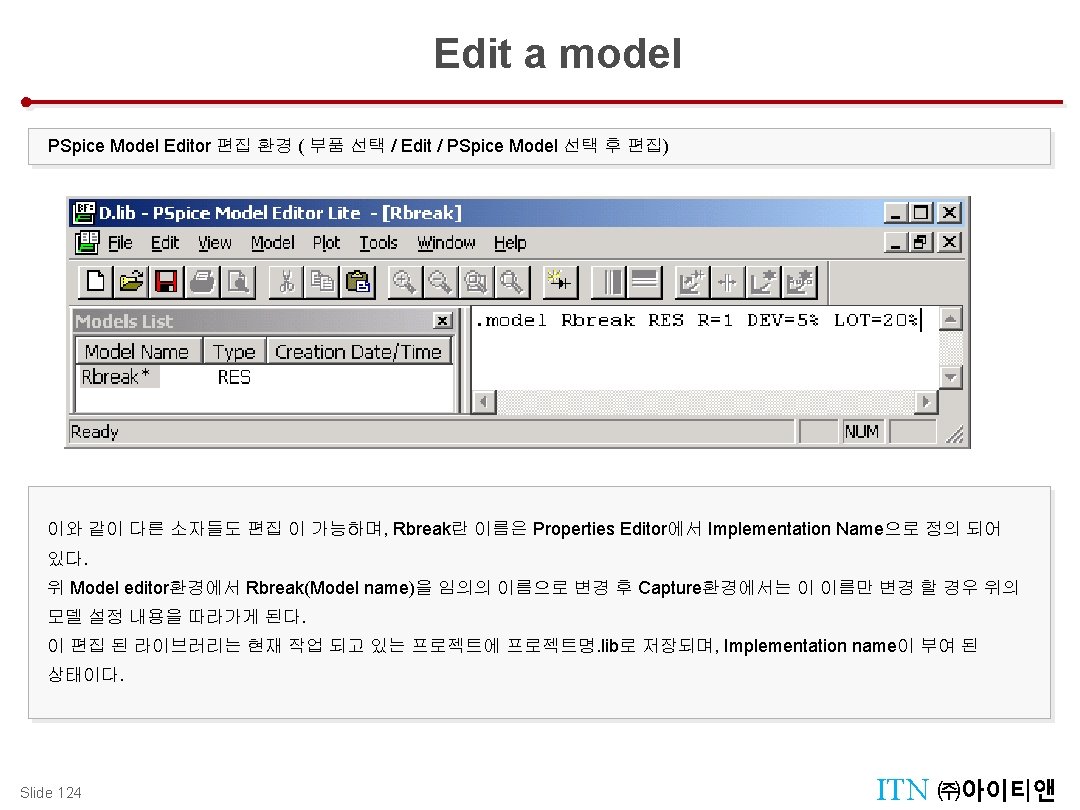

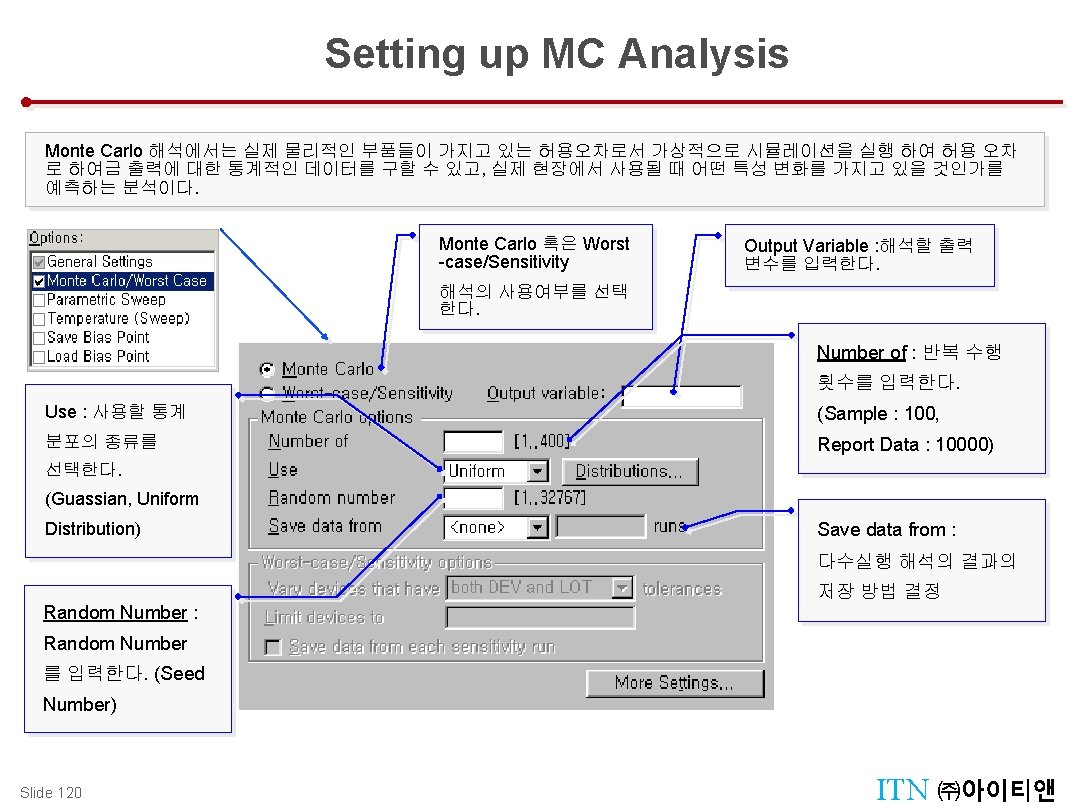

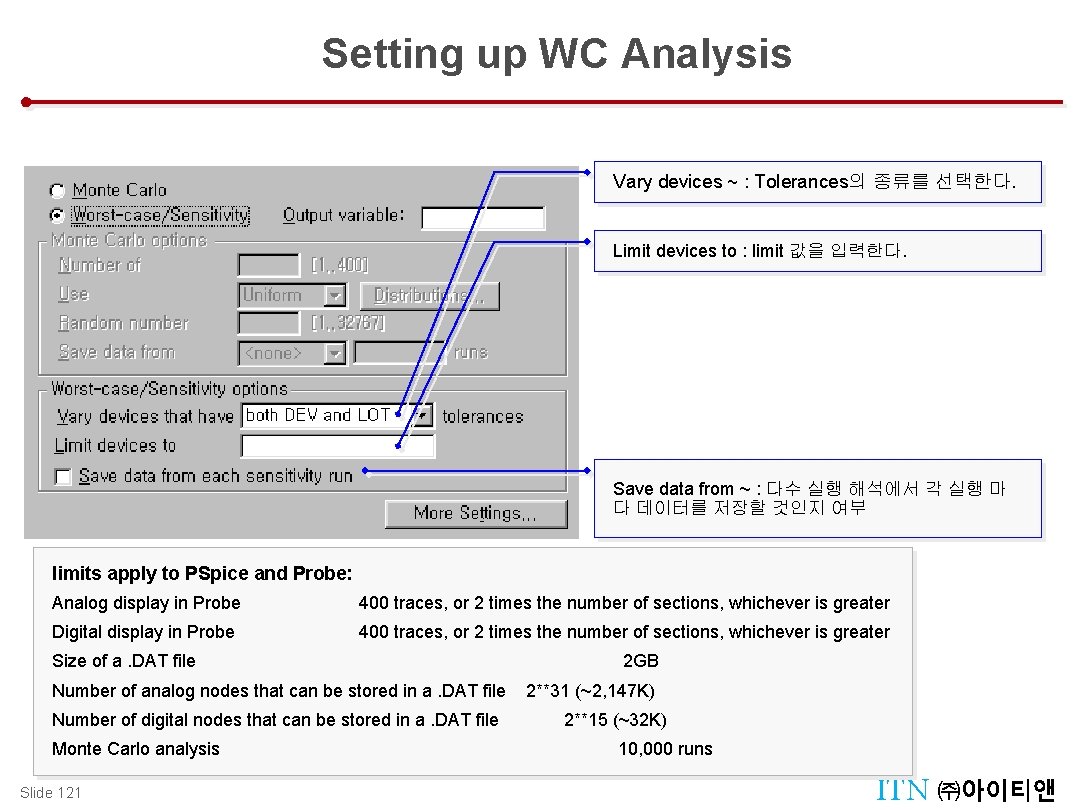

Setting up WC Analysis Vary devices ~ : Tolerances의 종류를 선택한다. Limit devices to : limit 값을 입력한다. Save data from ~ : 다수 실행 해석에서 각 실행 마 다 데이터를 저장할 것인지 여부 limits apply to PSpice and Probe: Analog display in Probe 400 traces, or 2 times the number of sections, whichever is greater Digital display in Probe 400 traces, or 2 times the number of sections, whichever is greater Size of a. DAT file 2 GB Number of analog nodes that can be stored in a. DAT file 2**31 (~2, 147 K) Number of digital nodes that can be stored in a. DAT file 2**15 (~32 K) Monte Carlo analysis Slide 121 10, 000 runs ITN ㈜아이티앤

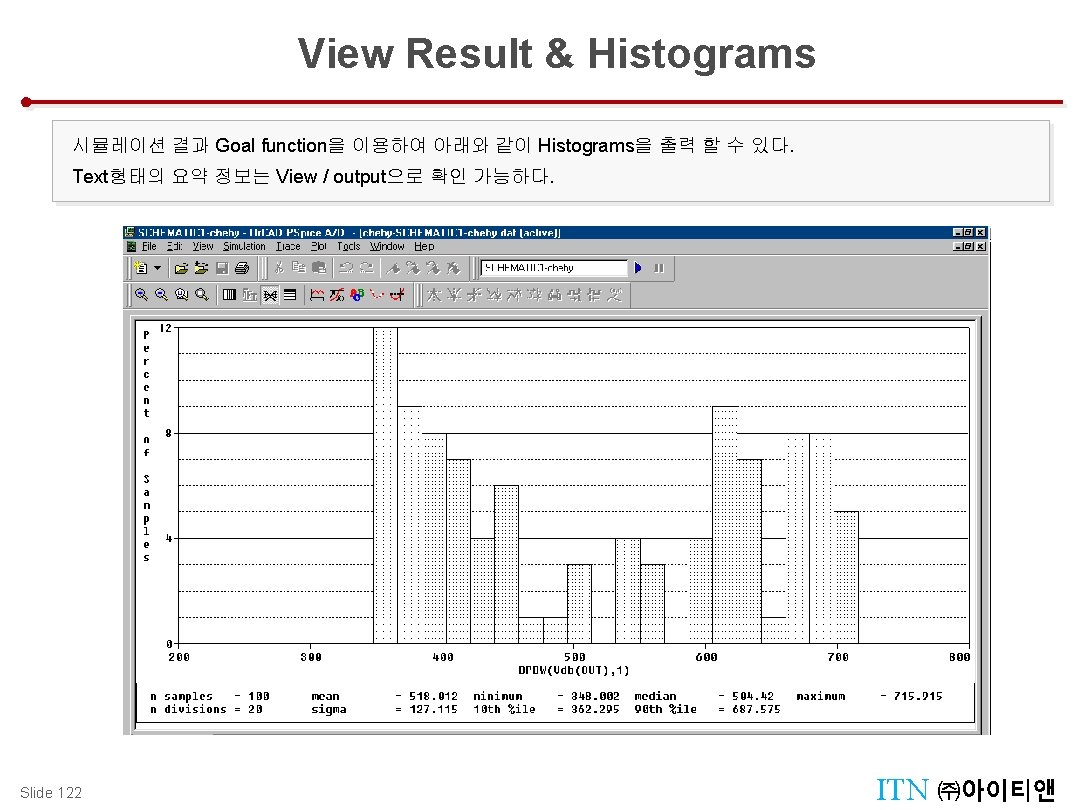

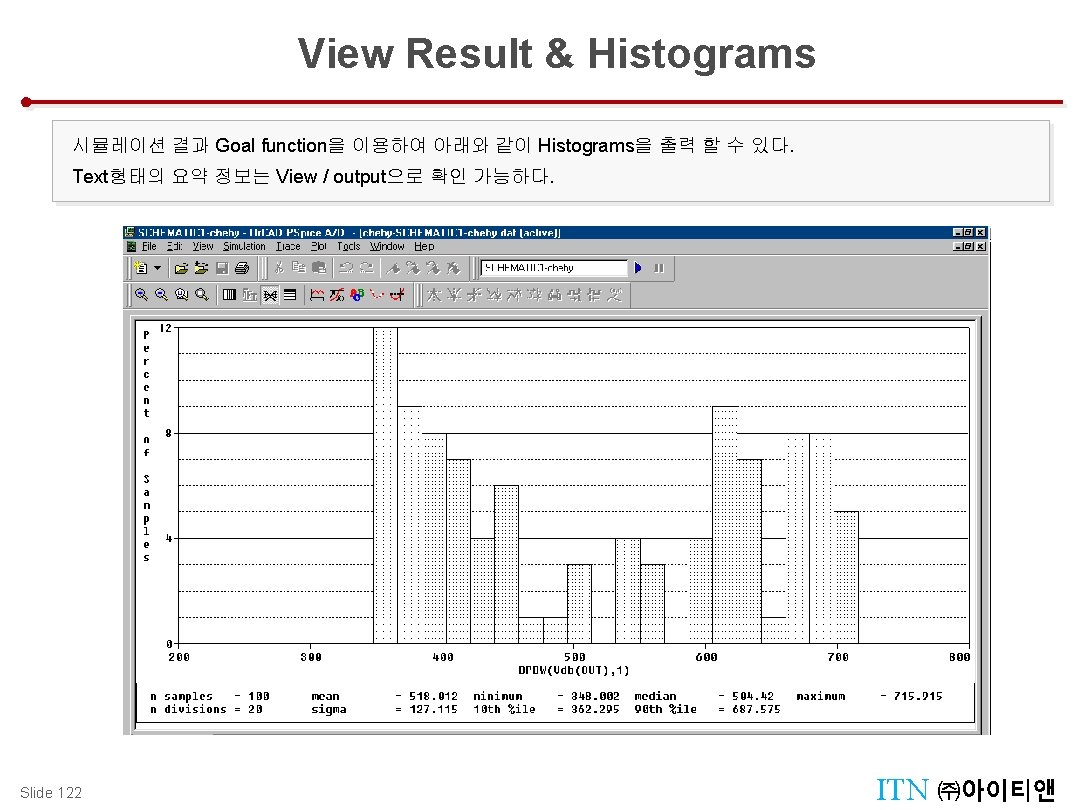

View Result & Histograms Parametric Analysis (Temperature Sweep) 시뮬레이션 결과 Goal function을 이용하여 아래와 같이 Histograms을 출력 할 수 있다. Text형태의 요약 정보는 View / output으로 확인 가능하다. Slide 122 ITN ㈜아이티앤

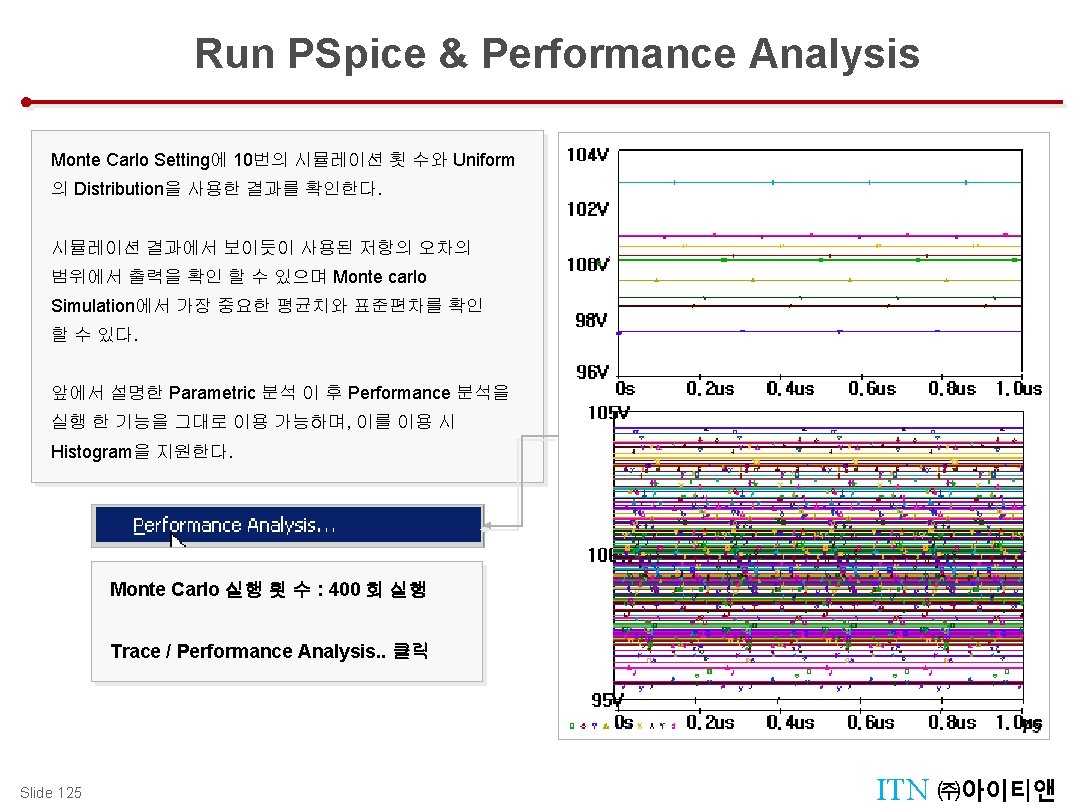

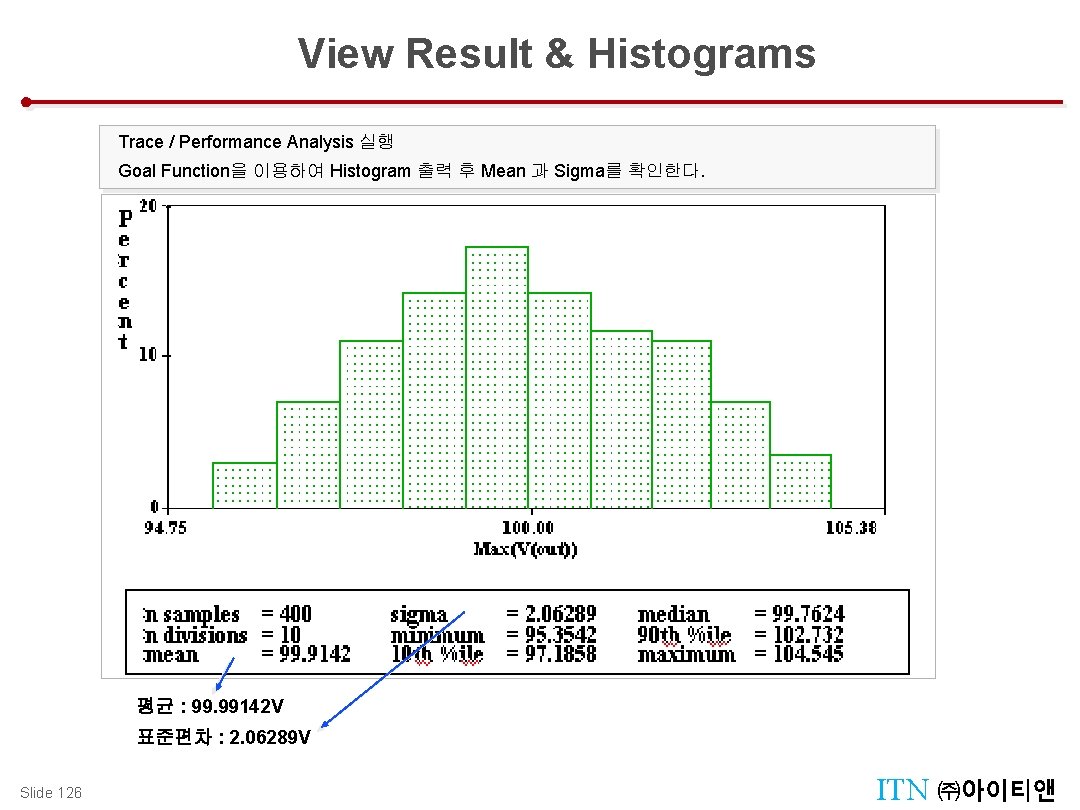

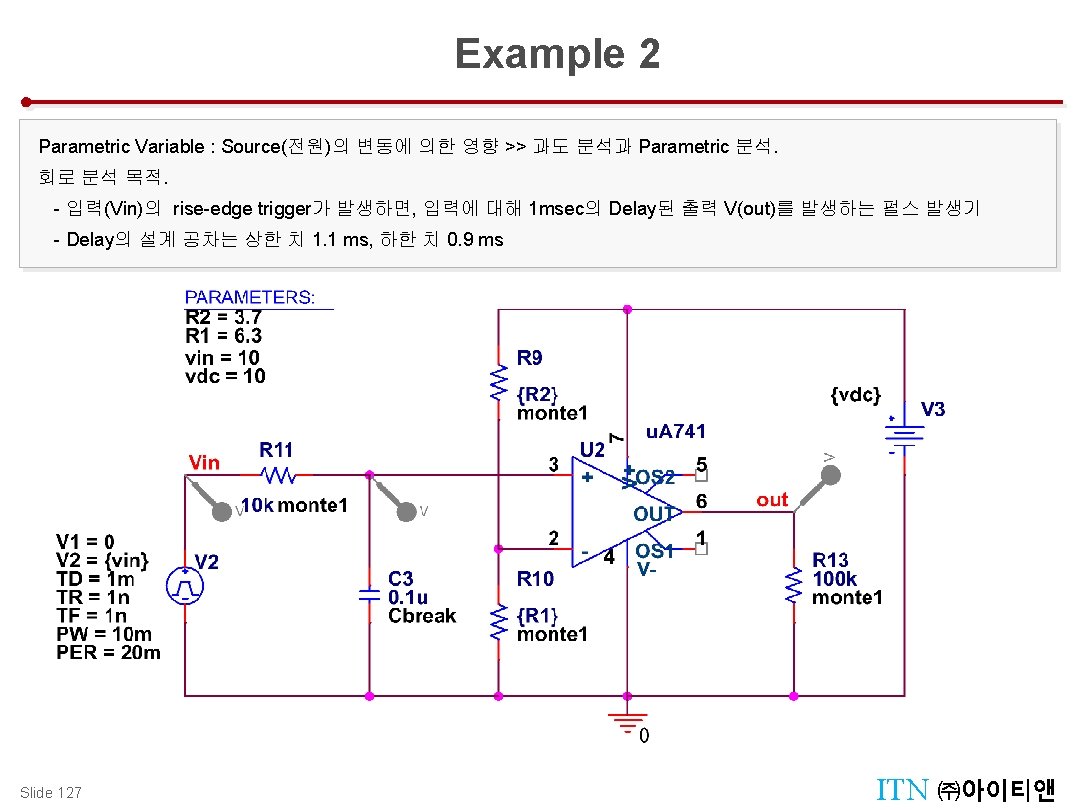

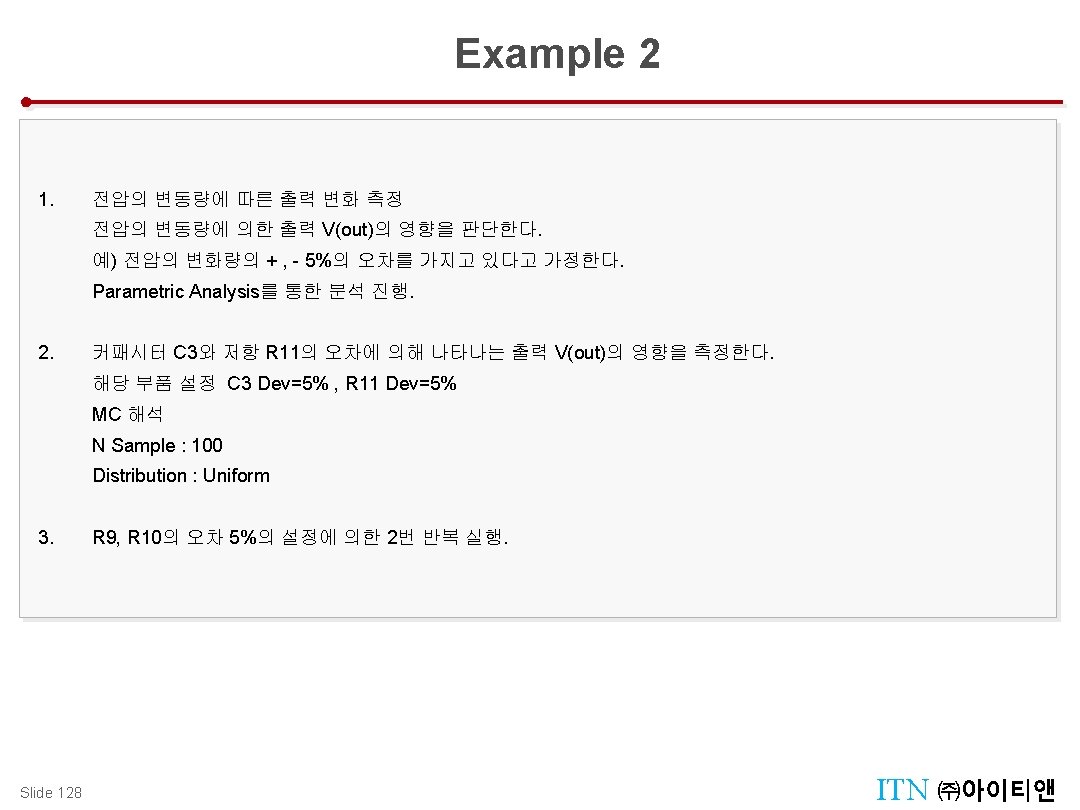

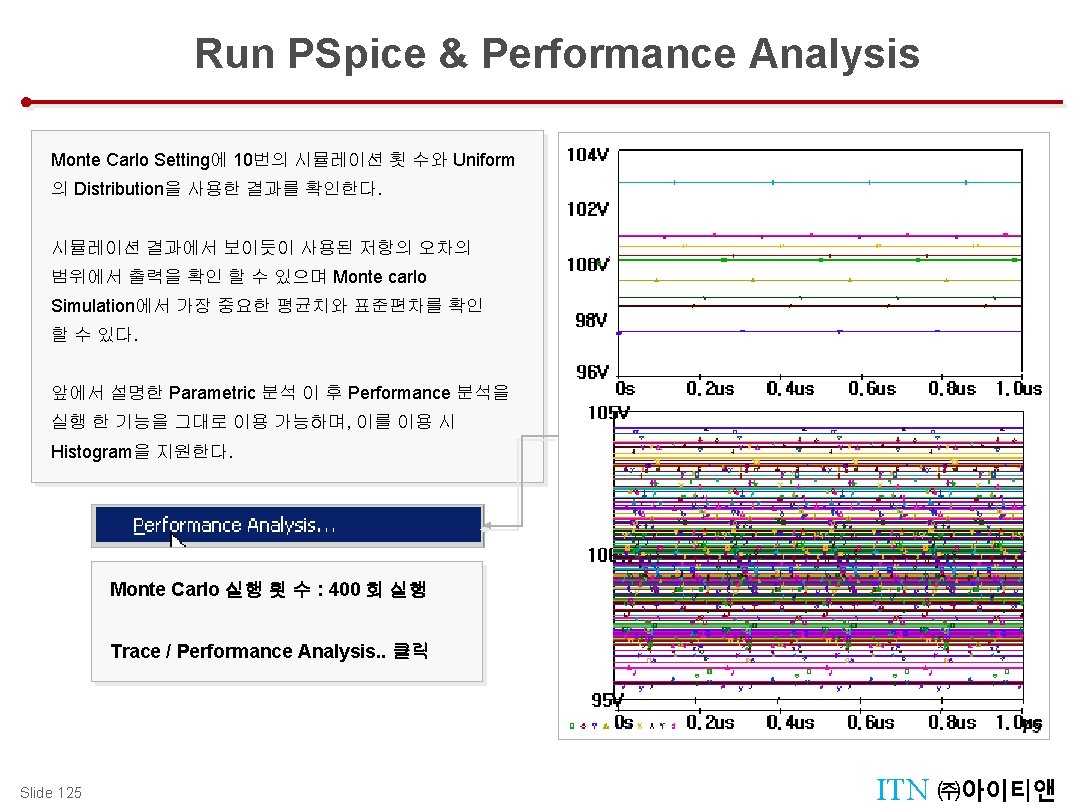

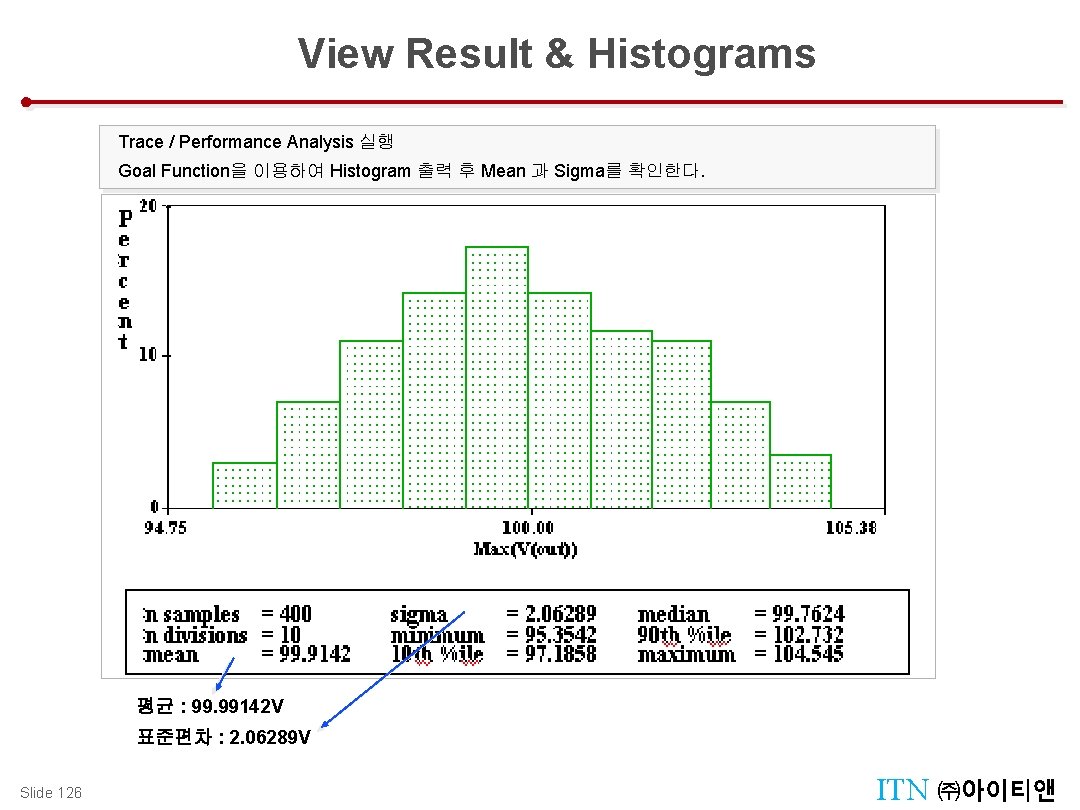

View Result & Histograms Monte Carlo Exam 1 (Simulation Result) Trace / Performance Analysis 실행 Goal Function을 이용하여 Histogram 출력 후 Mean 과 Sigma를 확인한다. 평균 : 99. 99142 V 표준편차 : 2. 06289 V Slide 126 ITN ㈜아이티앤

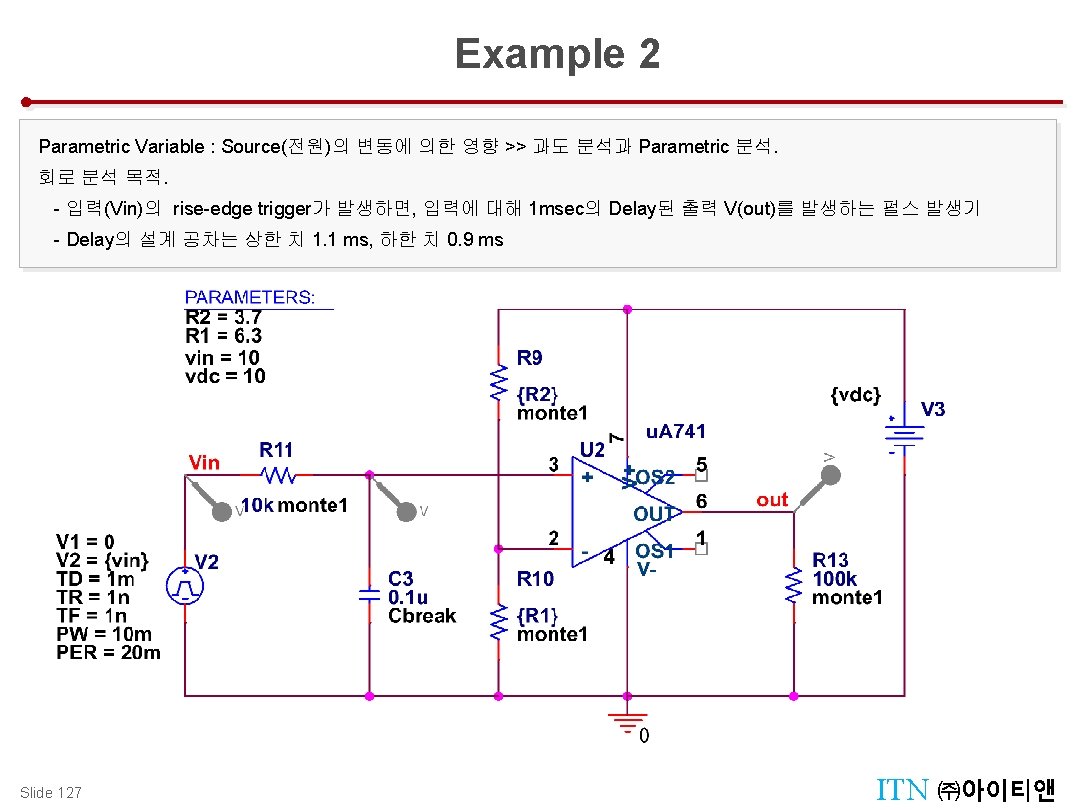

Creating Subcircuit from a schematic Design Management : Manager Tool Types of Simulation Models Create subcircuit from a schematic Create and configuring subcircuit Example (Slide 75 ; Transient Analysis) Slide 129 ITN ㈜아이티앤

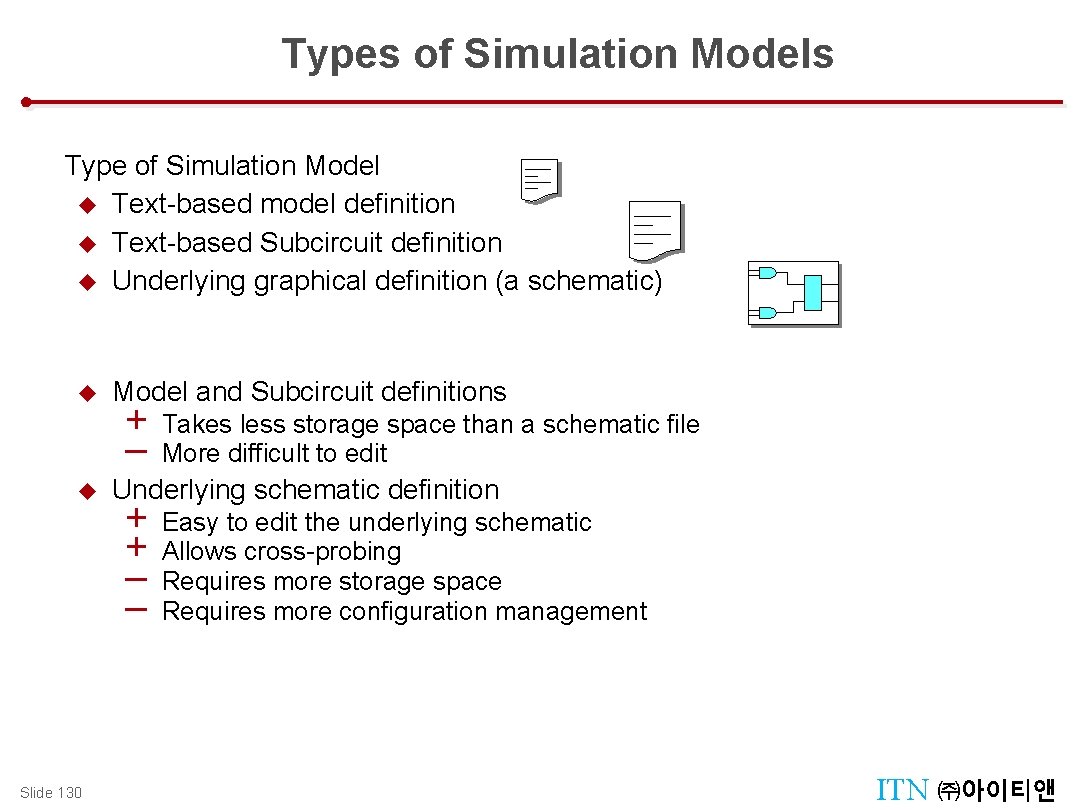

Types of Simulation Models Type of Simulation Model u Text-based model definition u Text-based Subcircuit definition u Underlying graphical definition (a schematic) u u Slide 130 Model and Subcircuit definitions + – Takes less storage space than a schematic file More difficult to edit Underlying schematic definition + + – – Easy to edit the underlying schematic Allows cross-probing Requires more storage space Requires more configuration management ITN ㈜아이티앤

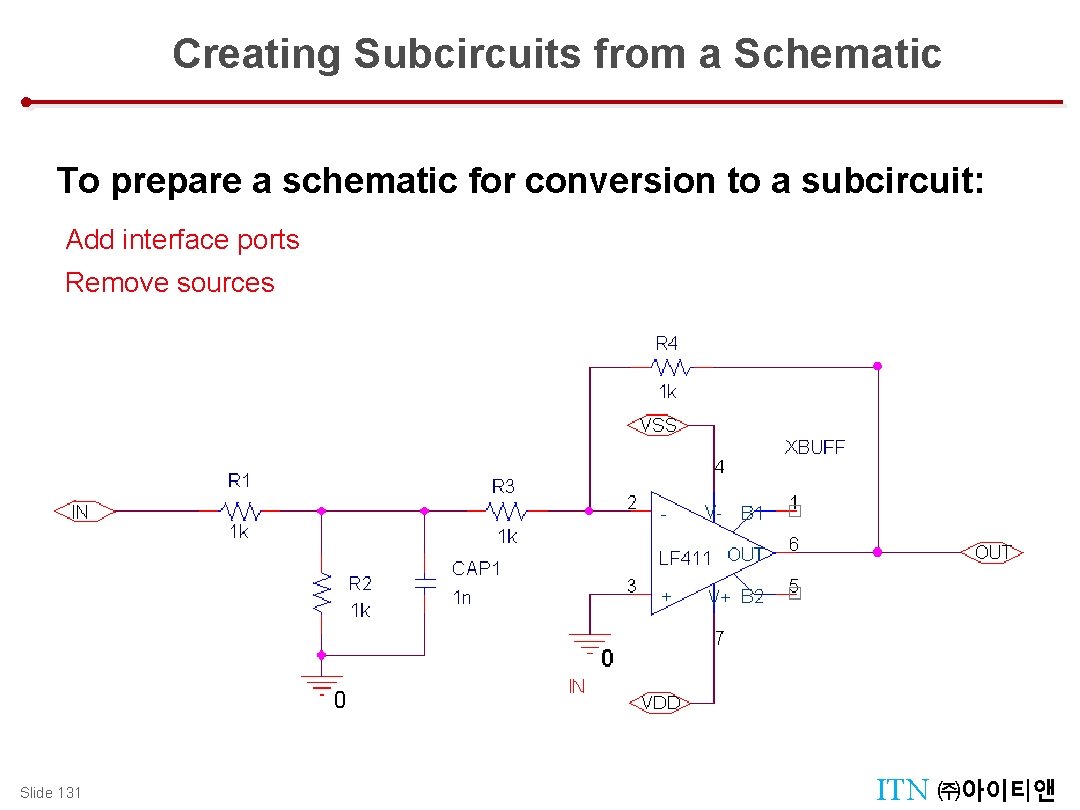

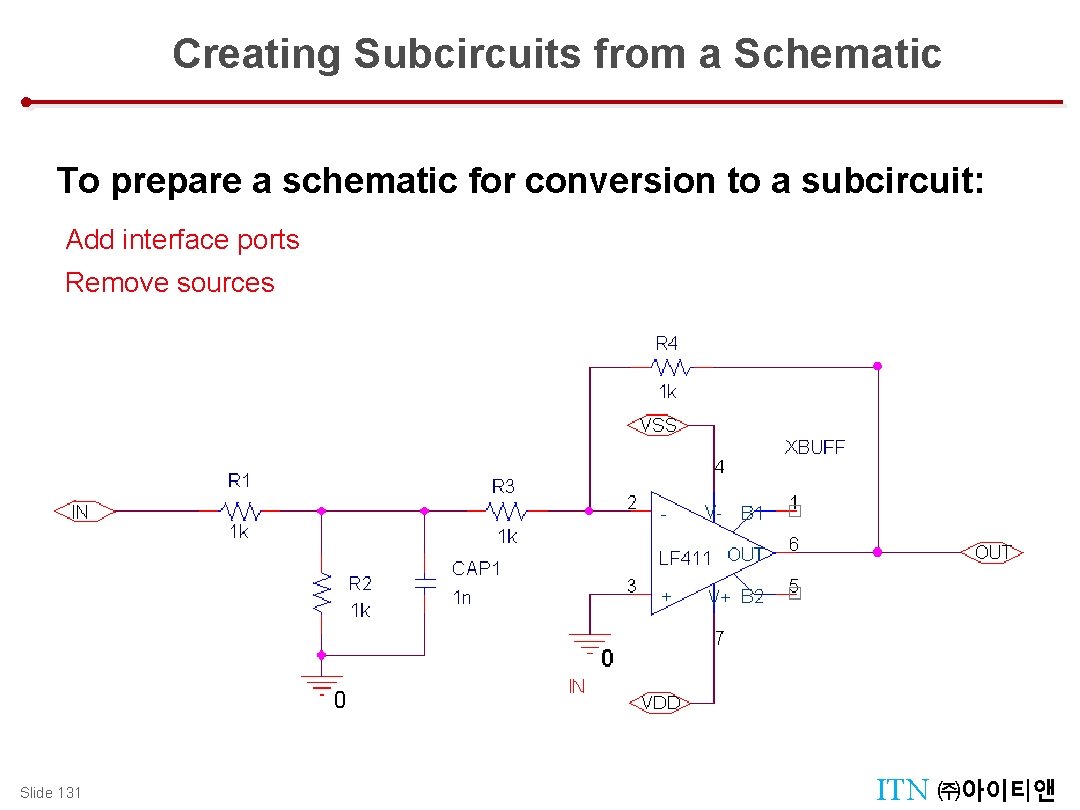

Creating Subcircuits from a Schematic To prepare a schematic for conversion to a subcircuit: Add interface ports Remove sources Slide 131 ITN ㈜아이티앤

Creating and Configuring the Subcircuit 1 From Project Manager 활성화 후 Tools > Create Netlist. 2 PSpice tab 선택. 3 Subcircuit Format Netlist 체크 후 Netlist 생성 Slide 132 ITN ㈜아이티앤

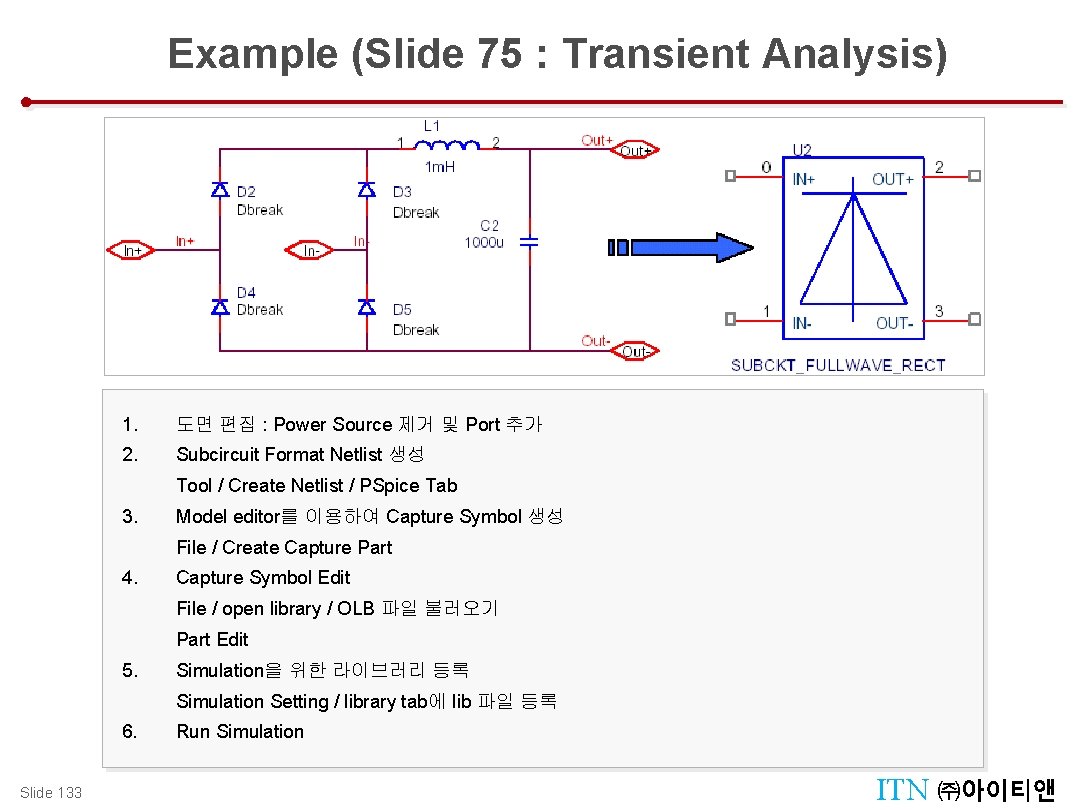

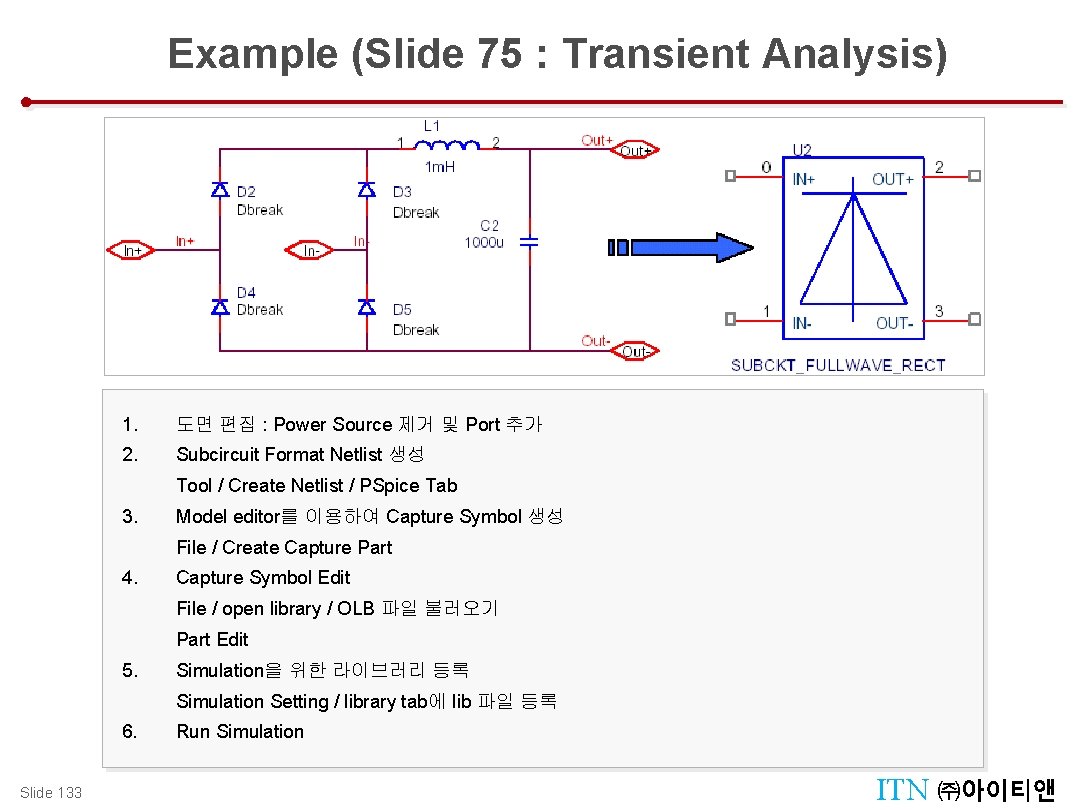

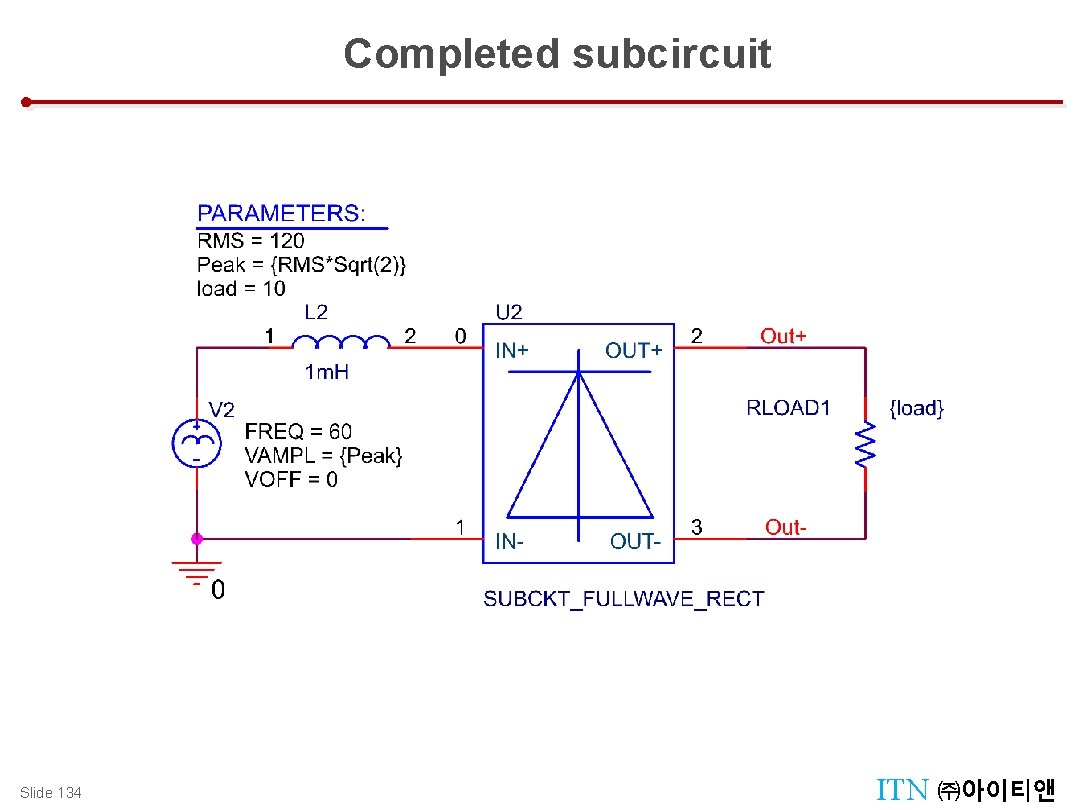

Example (Slide 75 : Transient Analysis) 1. 도면 편집 : Power Source 제거 및 Port 추가 2. Subcircuit Format Netlist 생성 Tool / Create Netlist / PSpice Tab 3. Model editor를 이용하여 Capture Symbol 생성 File / Create Capture Part 4. Capture Symbol Edit File / open library / OLB 파일 불러오기 Part Edit 5. Simulation을 위한 라이브러리 등록 Simulation Setting / library tab에 lib 파일 등록 6. Slide 133 Run Simulation ITN ㈜아이티앤

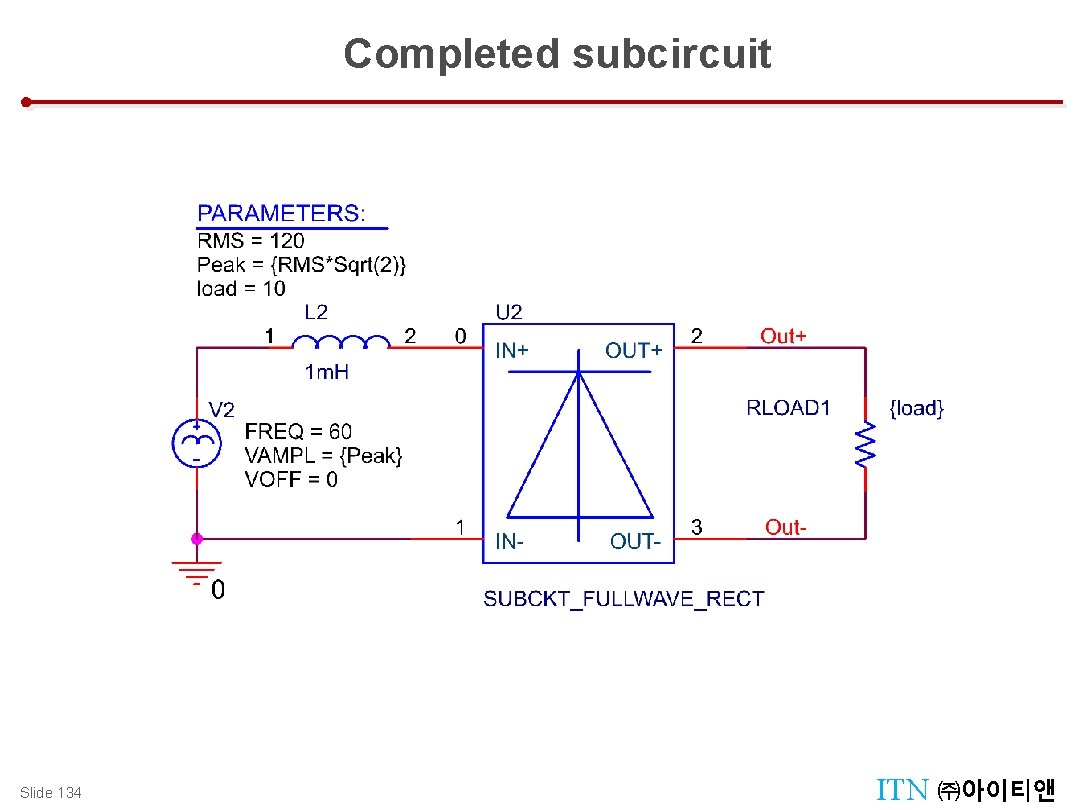

Completed subcircuit Slide 134 ITN ㈜아이티앤

Creating a PSpice Part Design Management : Manager Tool Drawing Tools Creating a Part Required properties for Simulation Use to Model Editor Slide 135 ITN ㈜아이티앤

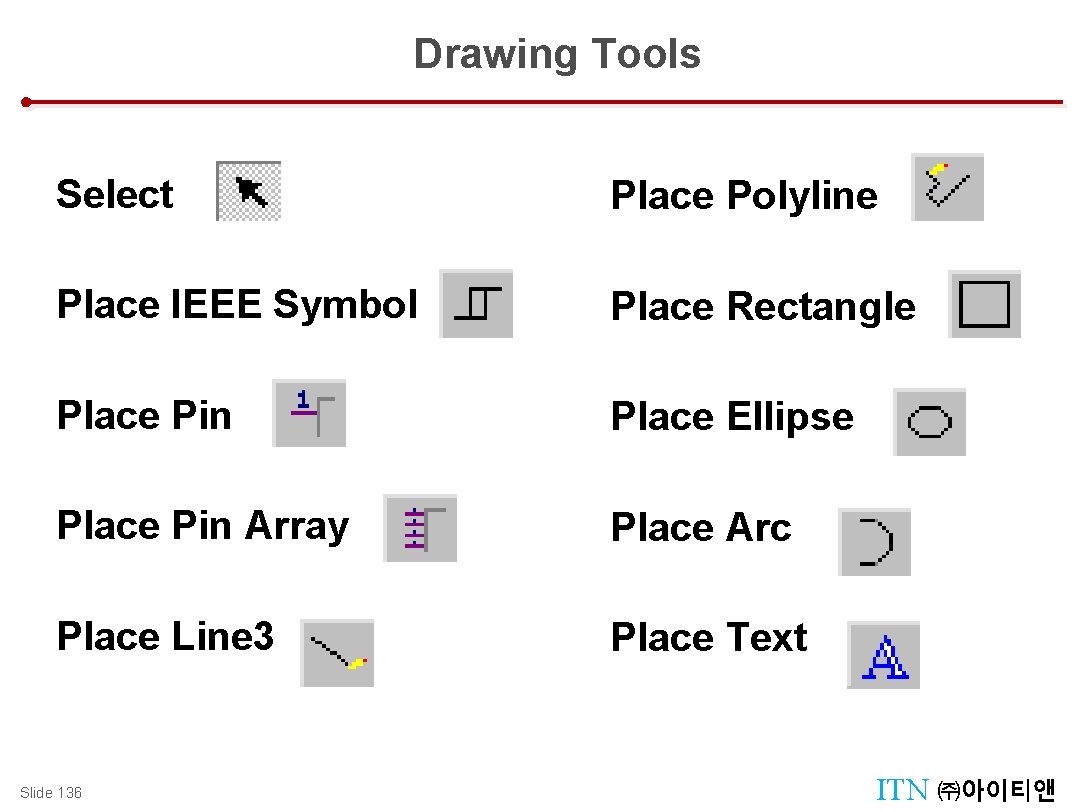

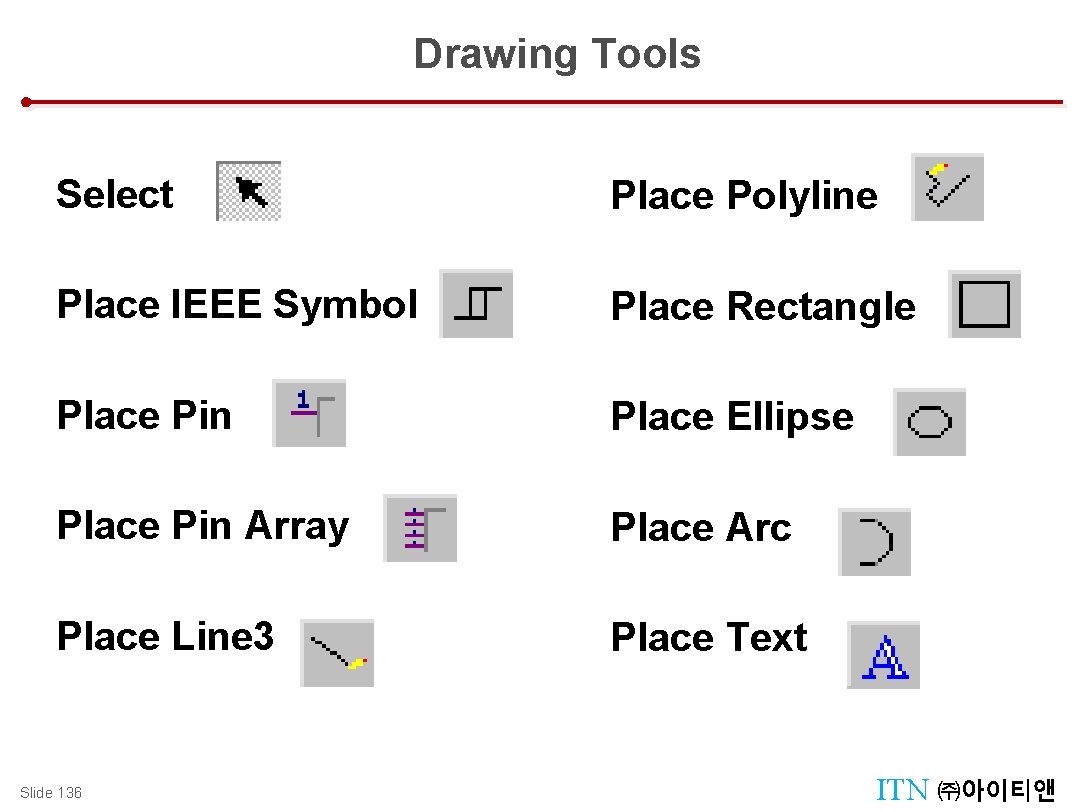

Subcircuit Create Drawing Tools Select Place Polyline Place IEEE Symbol Place Rectangle Place Pin Place Ellipse Place Pin Array Place Arc Place Line 3 Place Text Slide 136 ITN ㈜아이티앤

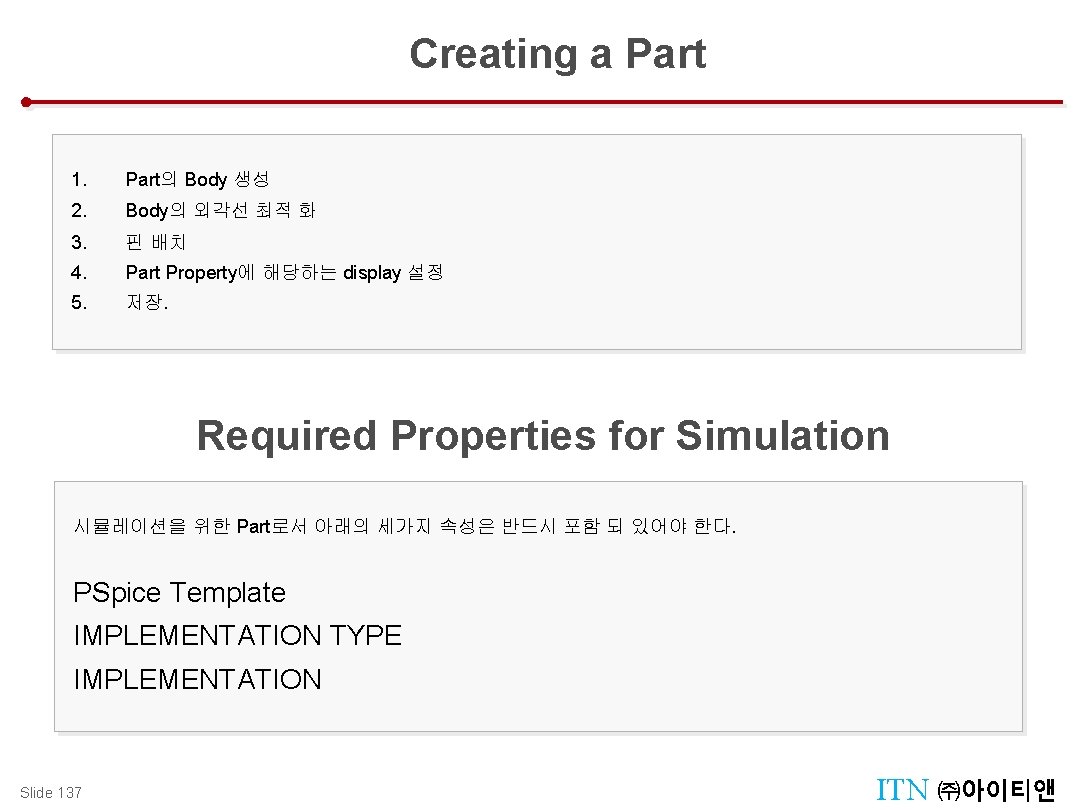

Subcircuit Create Creating a Part 1. Part의 Body 생성 2. Body의 외각선 최적 화 3. 핀 배치 4. Part Property에 해당하는 display 설정 5. 저장. Required Properties for Simulation 시뮬레이션을 위한 Part로서 아래의 세가지 속성은 반드시 포함 되 있어야 한다. PSpice Template IMPLEMENTATION TYPE IMPLEMENTATION Slide 137 ITN ㈜아이티앤

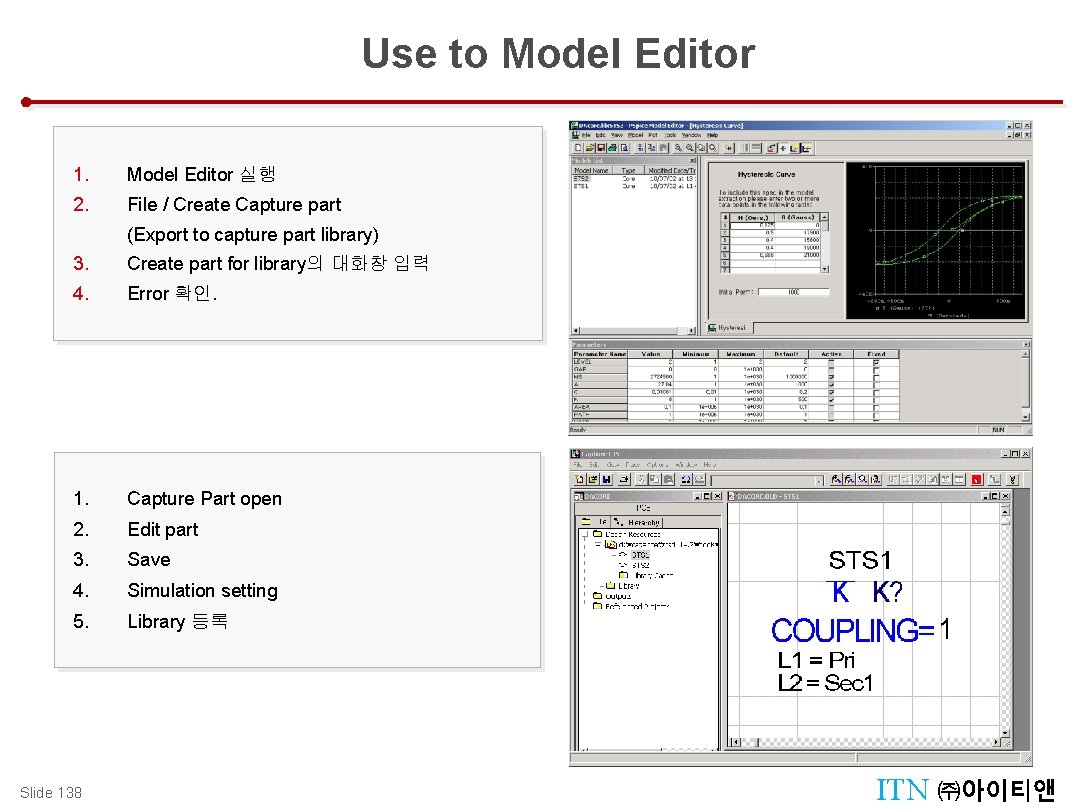

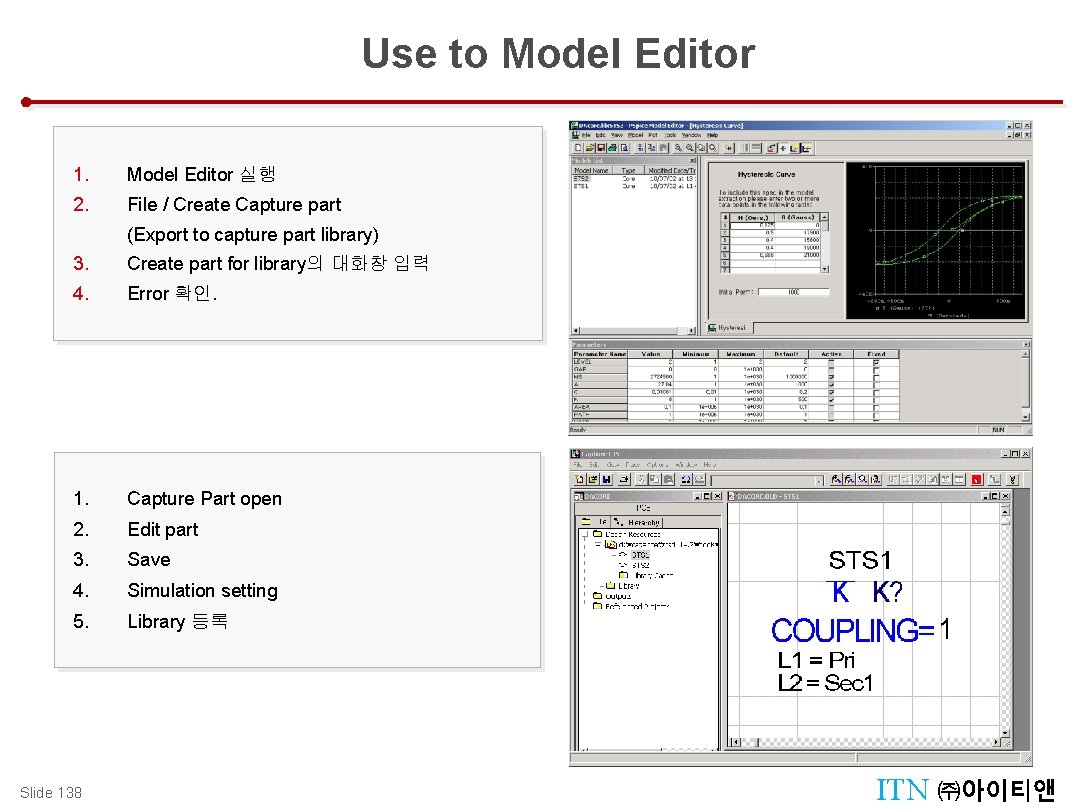

Subcircuit Create 1. Model Editor 실행 2. File / Create Capture part Use to Model Editor (Export to capture part library) 3. Create part for library의 대화창 입력 4. Error 확인. 1. Capture Part open 2. Edit part 3. Save 4. Simulation setting 5. Library 등록 Slide 138 ITN ㈜아이티앤

PSpice Template Design Management : Manager Tool Part Properties User Properties PSpice Template Edit PSpice Template Slide 139 ITN ㈜아이티앤

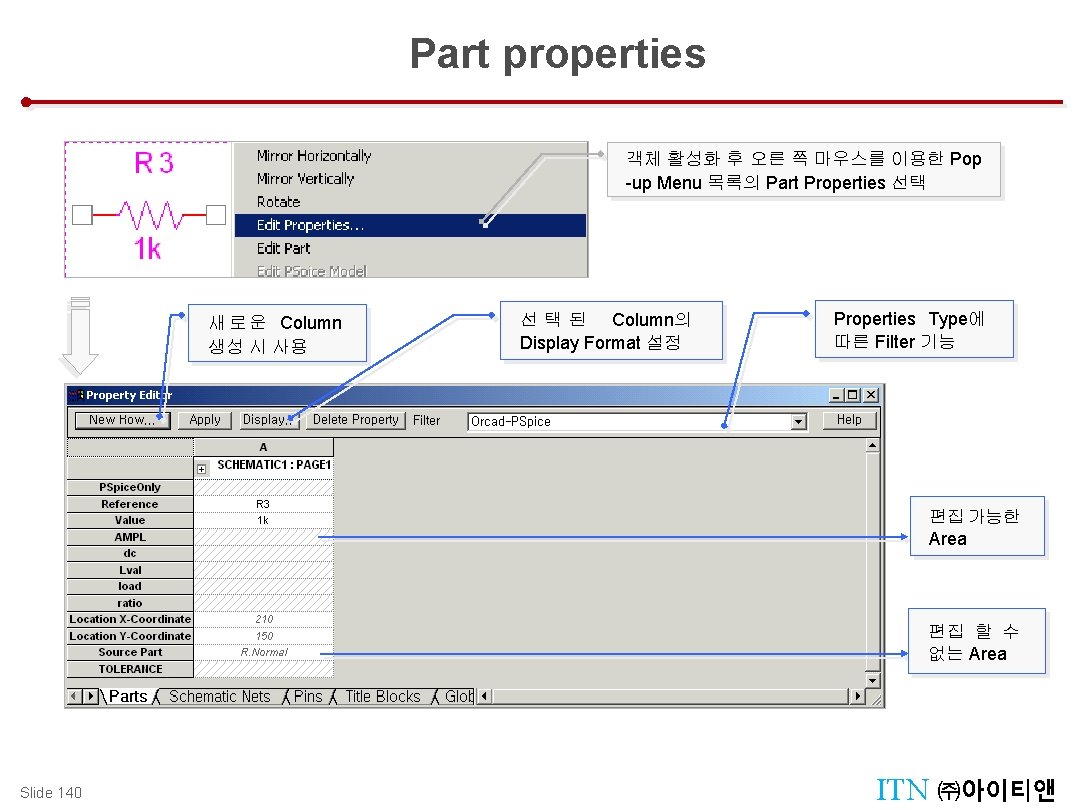

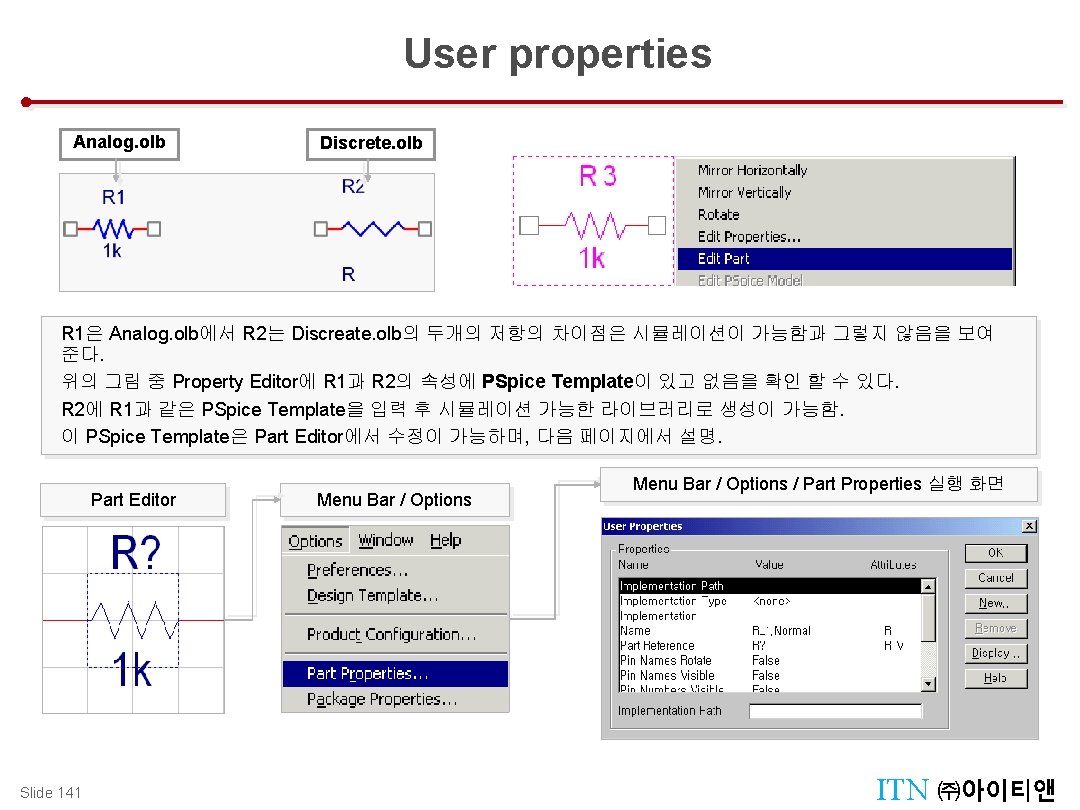

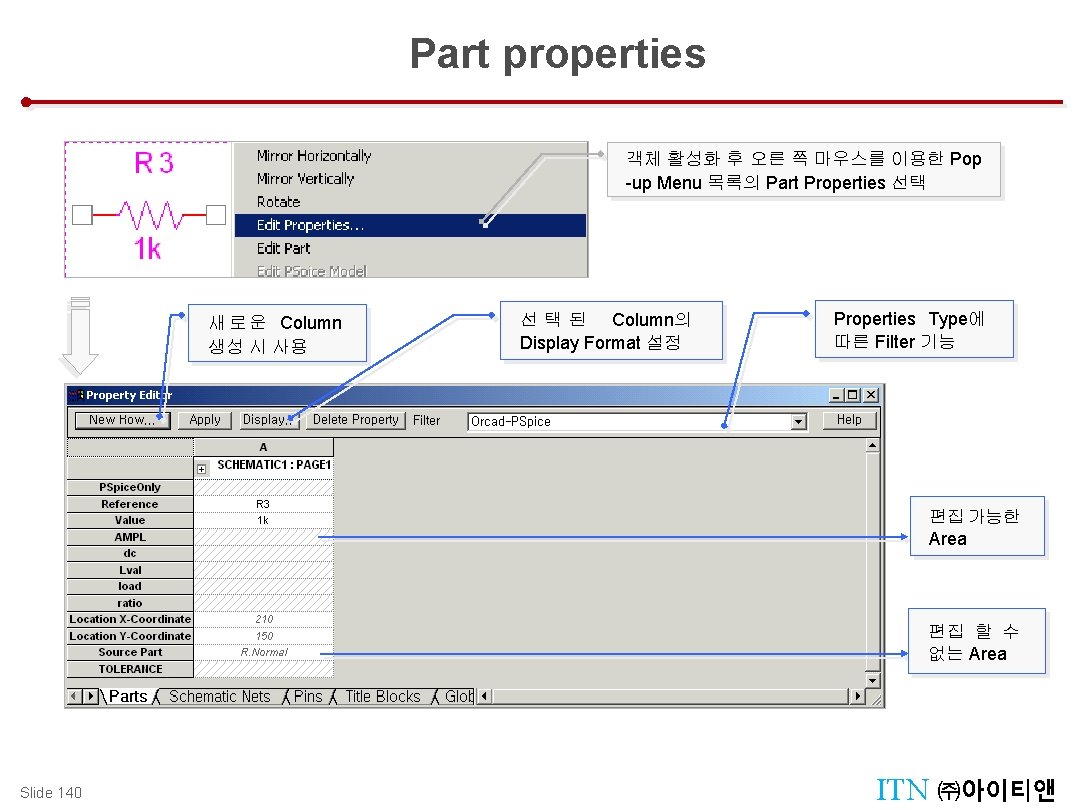

Part Properties Part properties 객체 활성화 후 오른 쪽 마우스를 이용한 Pop -up Menu 목록의 Part Properties 선택 새 로 운 Column 생성 시 사용 선 택 된 Column의 Display Format 설정 Properties Type에 따른 Filter 기능 편집 가능한 Area 편집 할 수 없는 Area Slide 140 ITN ㈜아이티앤

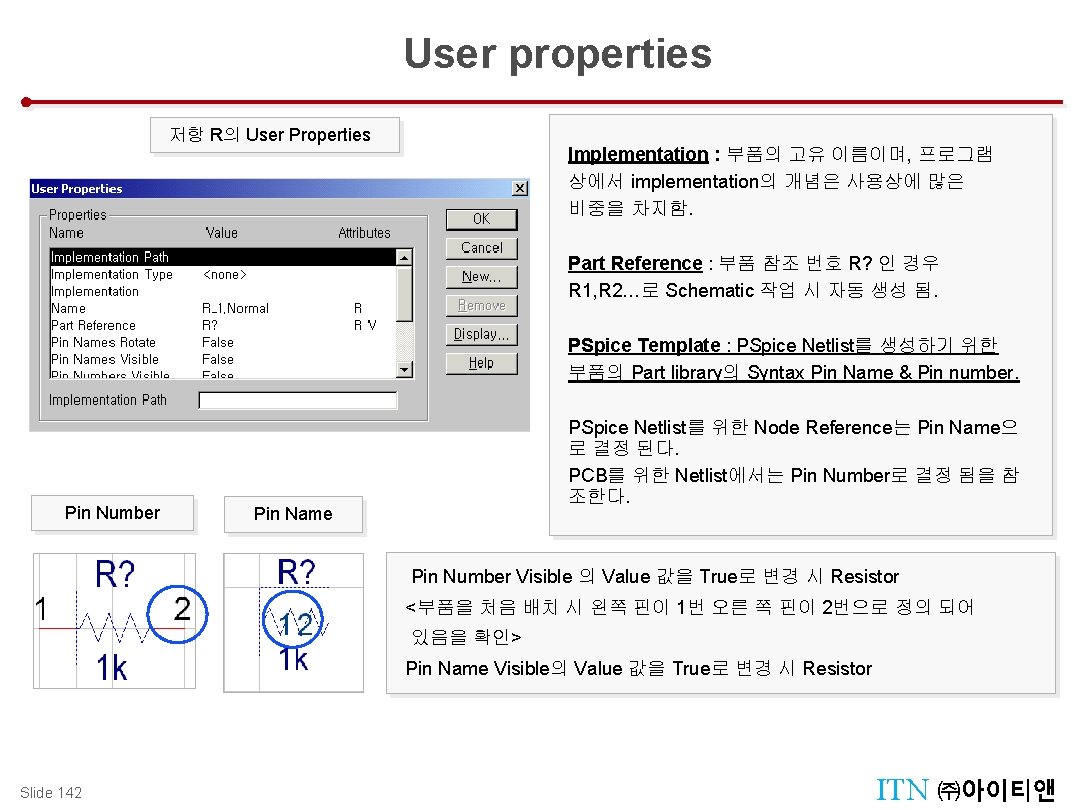

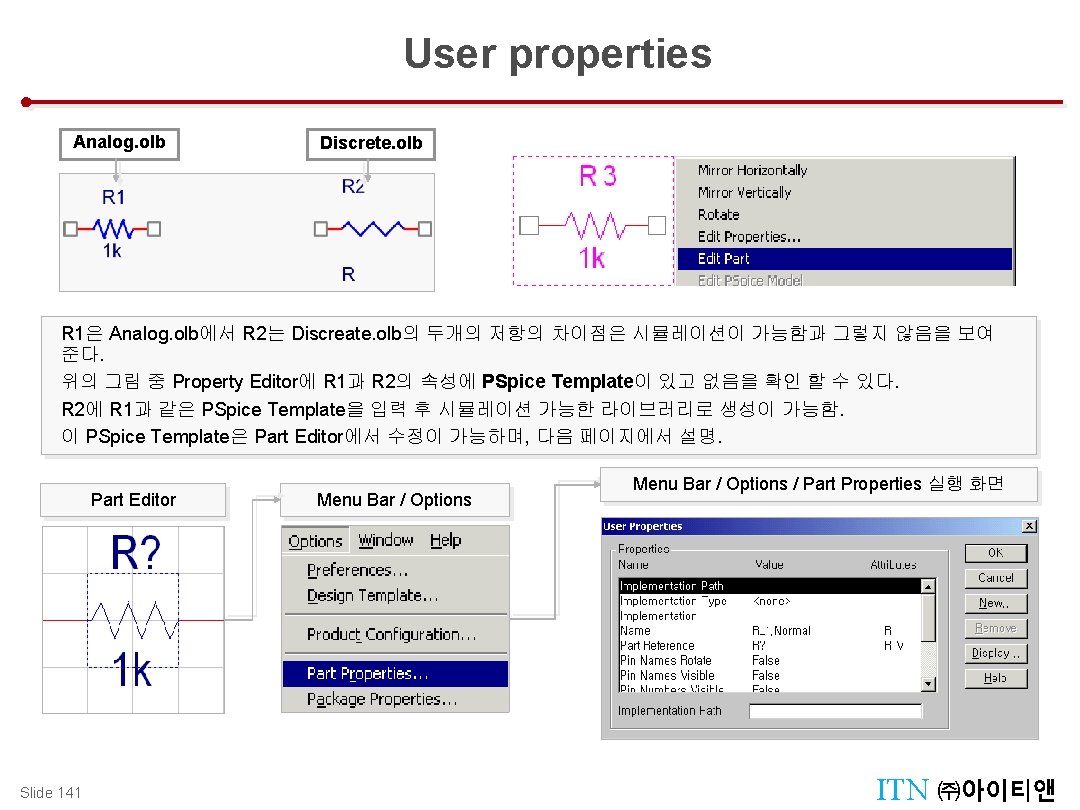

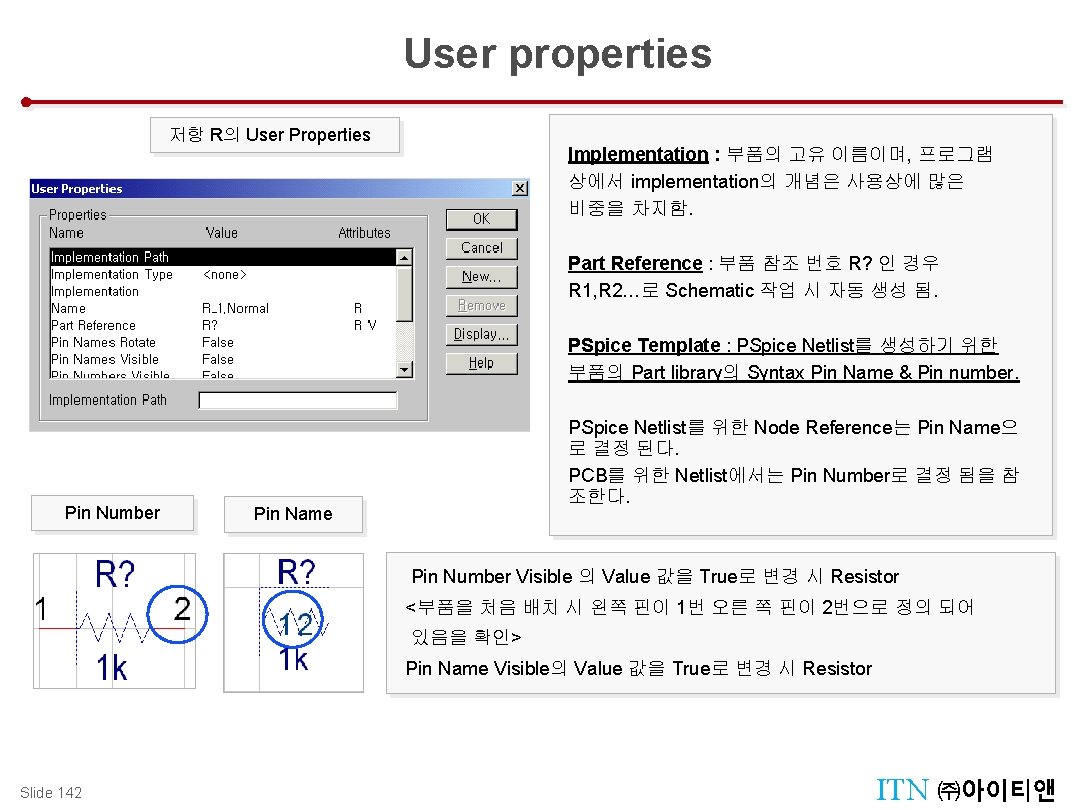

Part User Properties User properties 저항 R의 User Properties Implementation : 부품의 고유 이름이며, 프로그램 상에서 implementation의 개념은 사용상에 많은 비중을 차지함. Part Reference : 부품 참조 번호 R? 인 경우 R 1, R 2…로 Schematic 작업 시 자동 생성 됨. PSpice Template : PSpice Netlist를 생성하기 위한 부품의 Part library의 Syntax Pin Name & Pin number. Pin Number PSpice Netlist를 위한 Node Reference는 Pin Name으 로 결정 된다. PCB를 위한 Netlist에서는 Pin Number로 결정 됨을 참 조한다. Pin Name Pin Number Visible 의 Value 값을 True로 변경 시 Resistor <부품을 처음 배치 시 왼쪽 핀이 1번 오른 쪽 핀이 2번으로 정의 되어 있음을 확인> Pin Name Visible의 Value 값을 True로 변경 시 Resistor Slide 142 ITN ㈜아이티앤

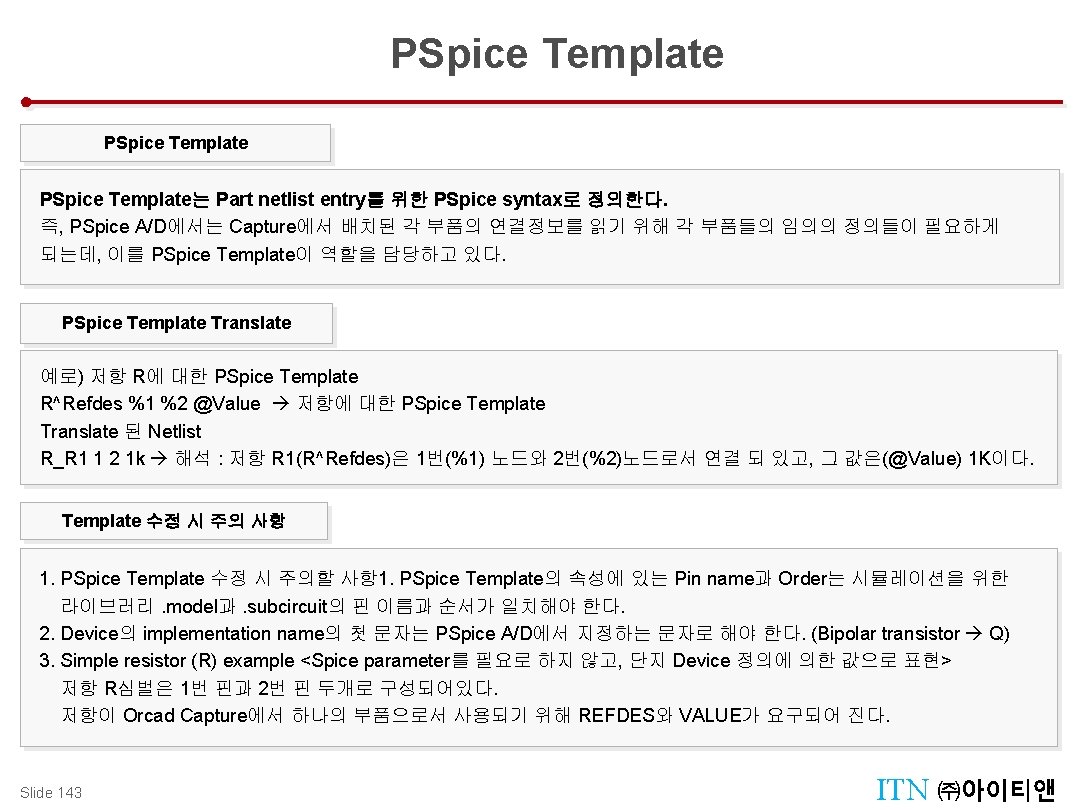

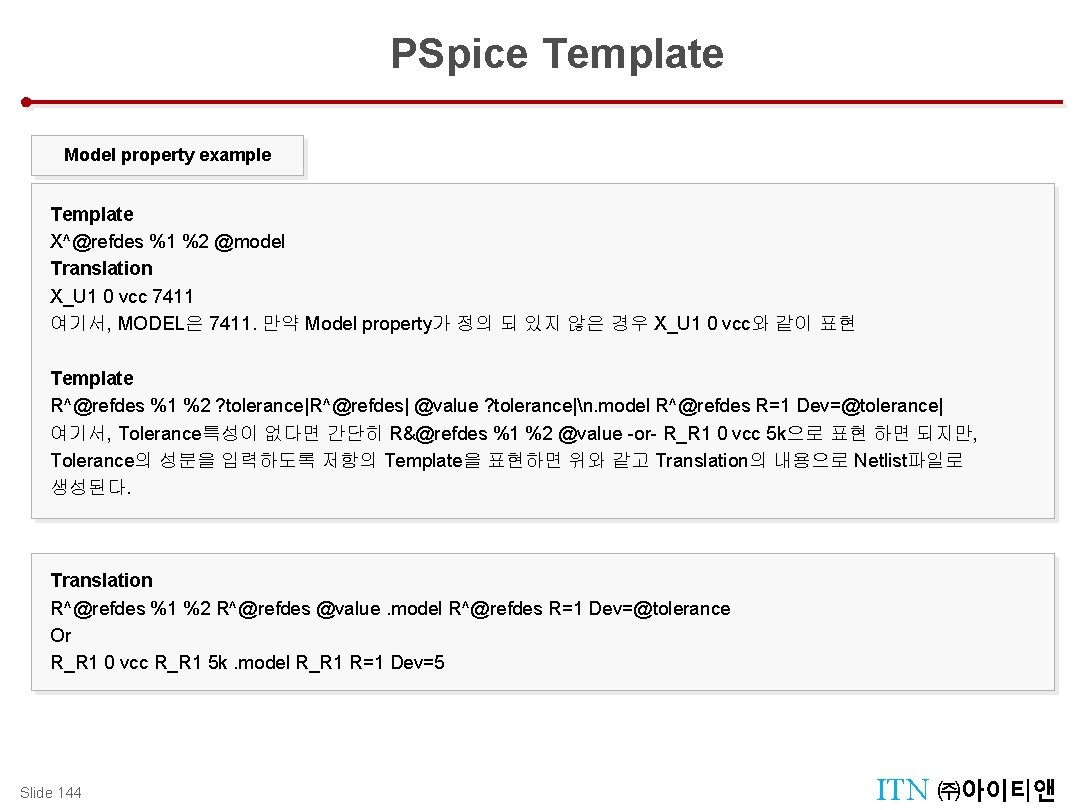

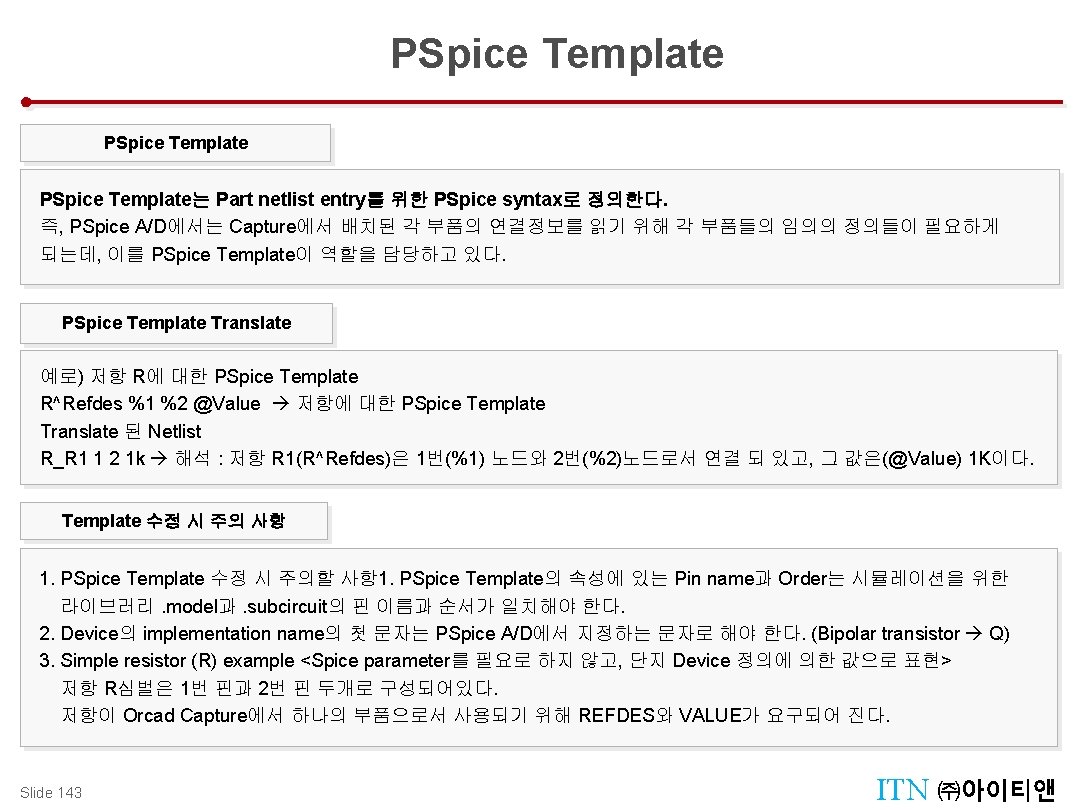

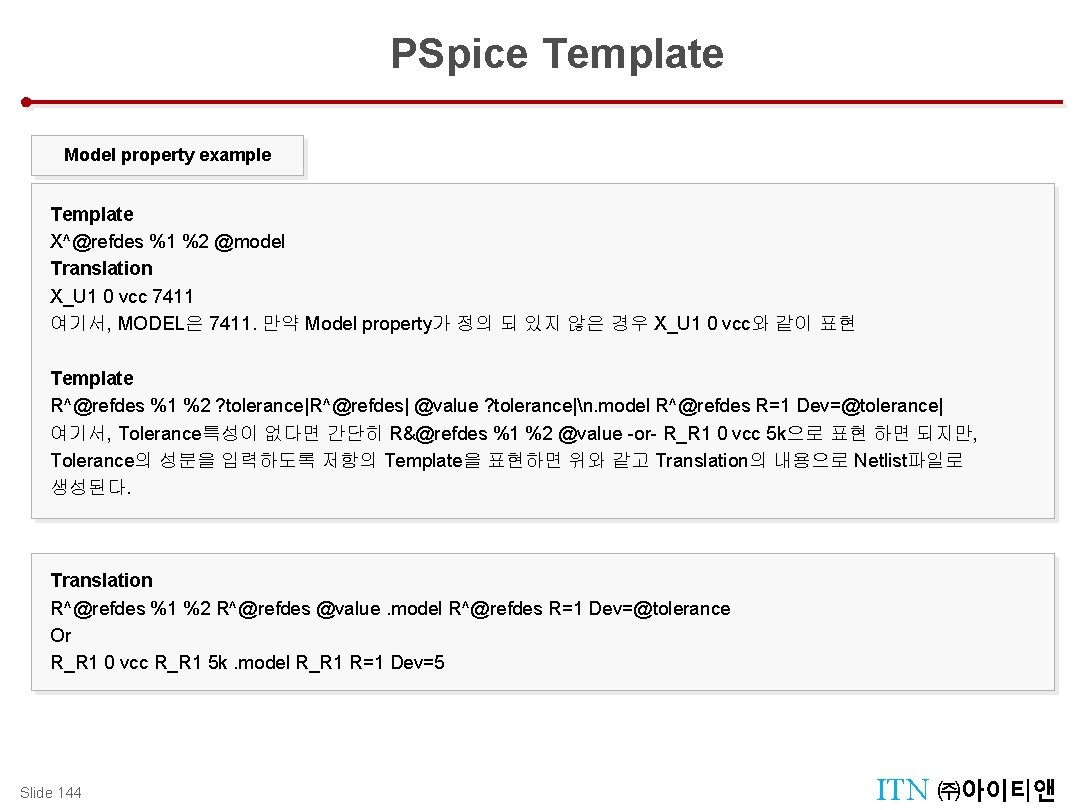

PSpice Template Model property example Template X^@refdes %1 %2 @model Translation X_U 1 0 vcc 7411 여기서, MODEL은 7411. 만약 Model property가 정의 되 있지 않은 경우 X_U 1 0 vcc와 같이 표현 Template R^@refdes %1 %2 ? tolerance|R^@refdes| @value ? tolerance|n. model R^@refdes R=1 Dev=@tolerance| 여기서, Tolerance특성이 없다면 간단히 R&@refdes %1 %2 @value -or- R_R 1 0 vcc 5 k으로 표현 하면 되지만, Tolerance의 성분을 입력하도록 저항의 Template을 표현하면 위와 같고 Translation의 내용으로 Netlist파일로 생성된다. Translation R^@refdes %1 %2 R^@refdes @value. model R^@refdes R=1 Dev=@tolerance Or R_R 1 0 vcc R_R 1 5 k. model R_R 1 R=1 Dev=5 Slide 144 ITN ㈜아이티앤

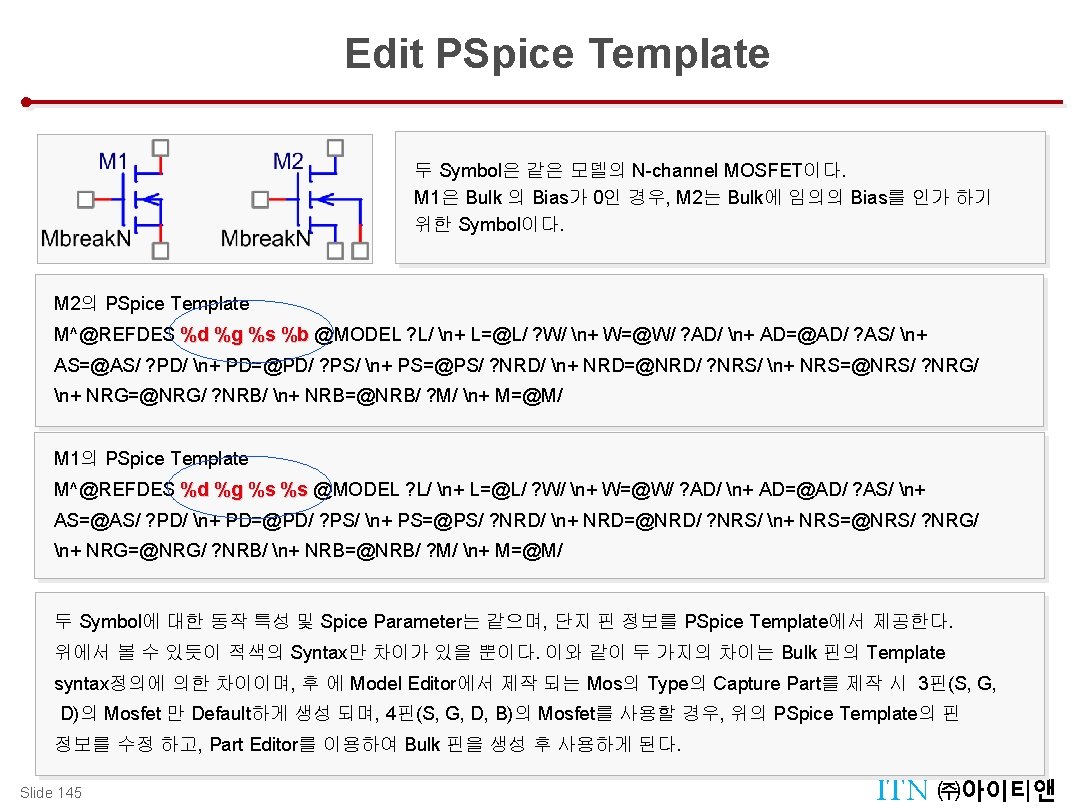

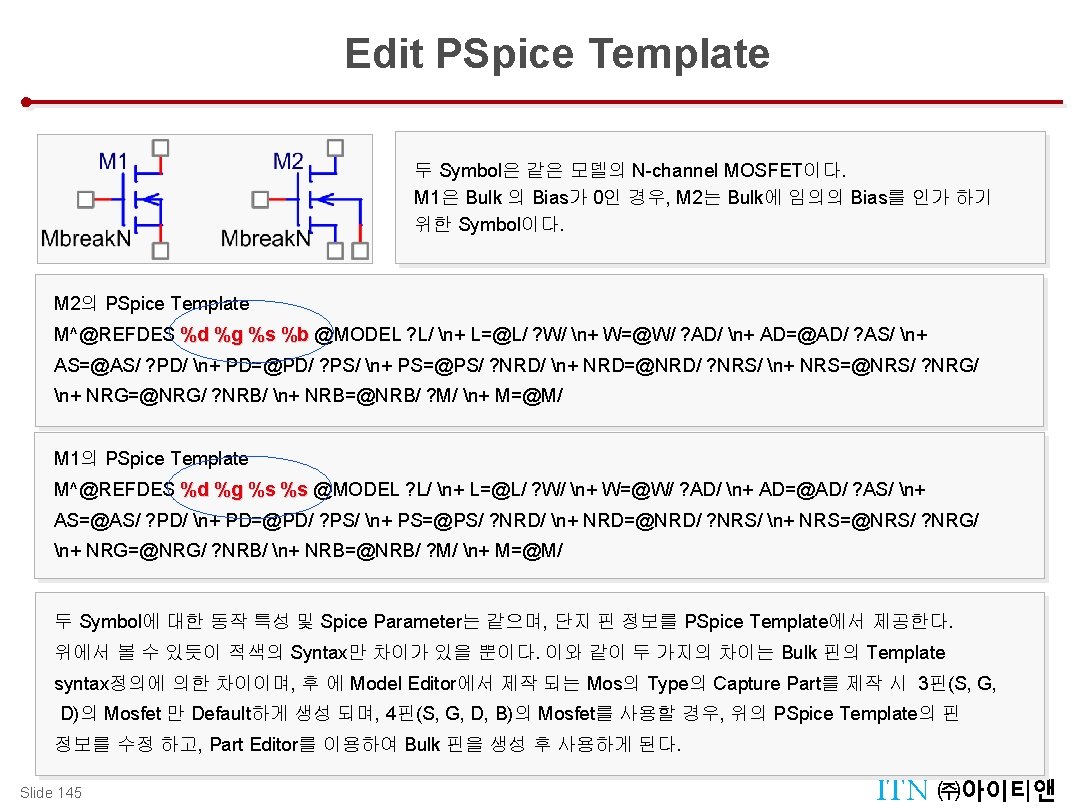

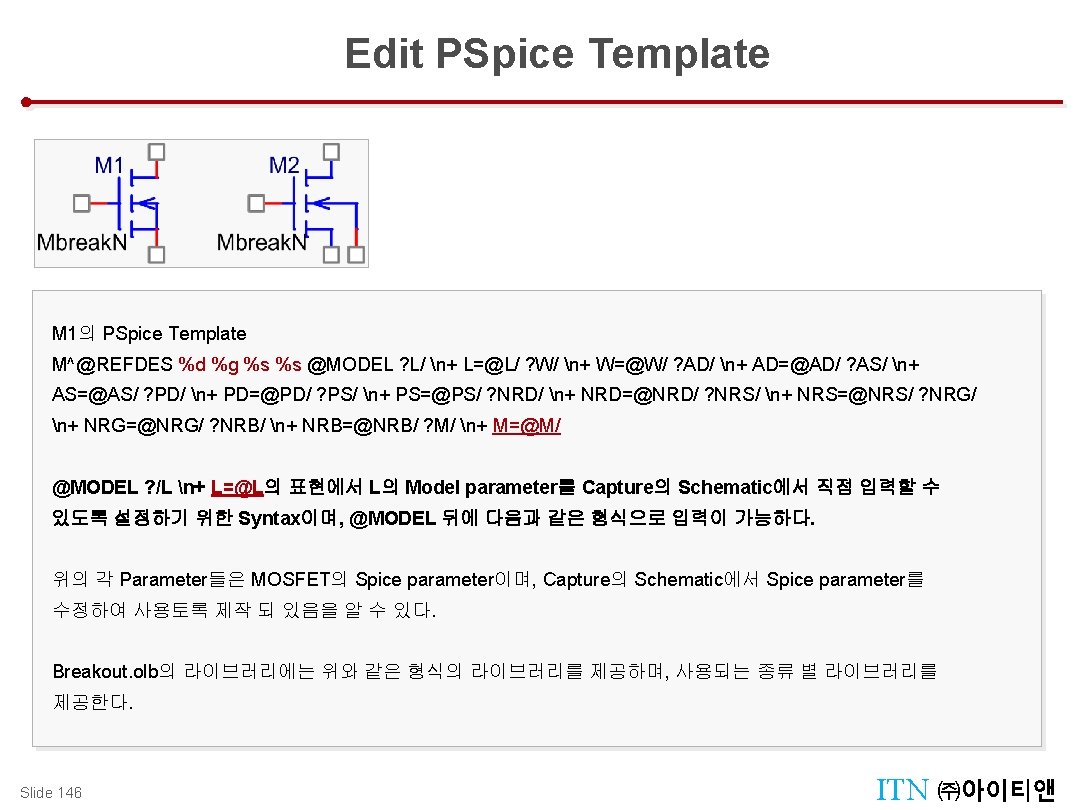

PSpice Template Example Edit PSpice Template 두 Symbol은 같은 모델의 N-channel MOSFET이다. M 1은 Bulk 의 Bias가 0인 경우, M 2는 Bulk에 임의의 Bias를 인가 하기 위한 Symbol이다. M 2의 PSpice Template M^@REFDES %d %g %s %b @MODEL ? L/ n+ L=@L/ ? W/ n+ W=@W/ ? AD/ n+ AD=@AD/ ? AS/ n+ %b AS=@AS/ ? PD/ n+ PD=@PD/ ? PS/ n+ PS=@PS/ ? NRD/ n+ NRD=@NRD/ ? NRS/ n+ NRS=@NRS/ ? NRG/ n+ NRG=@NRG/ ? NRB/ n+ NRB=@NRB/ ? M/ n+ M=@M/ M 1의 PSpice Template M^@REFDES %d %g %s %s @MODEL ? L/ n+ L=@L/ ? W/ n+ W=@W/ ? AD/ n+ AD=@AD/ ? AS/ n+ %s AS=@AS/ ? PD/ n+ PD=@PD/ ? PS/ n+ PS=@PS/ ? NRD/ n+ NRD=@NRD/ ? NRS/ n+ NRS=@NRS/ ? NRG/ n+ NRG=@NRG/ ? NRB/ n+ NRB=@NRB/ ? M/ n+ M=@M/ 두 Symbol에 대한 동작 특성 및 Spice Parameter는 같으며, 단지 핀 정보를 PSpice Template에서 제공한다. 위에서 볼 수 있듯이 적색의 Syntax만 차이가 있을 뿐이다. 이와 같이 두 가지의 차이는 Bulk 핀의 Template syntax정의에 의한 차이이며, 후 에 Model Editor에서 제작 되는 Mos의 Type의 Capture Part를 제작 시 3핀(S, G, D)의 Mosfet 만 Default하게 생성 되며, 4핀(S, G, D, B)의 Mosfet를 사용할 경우, 위의 PSpice Template의 핀 정보를 수정 하고, Part Editor를 이용하여 Bulk 핀을 생성 후 사용하게 된다. Slide 145 ITN ㈜아이티앤

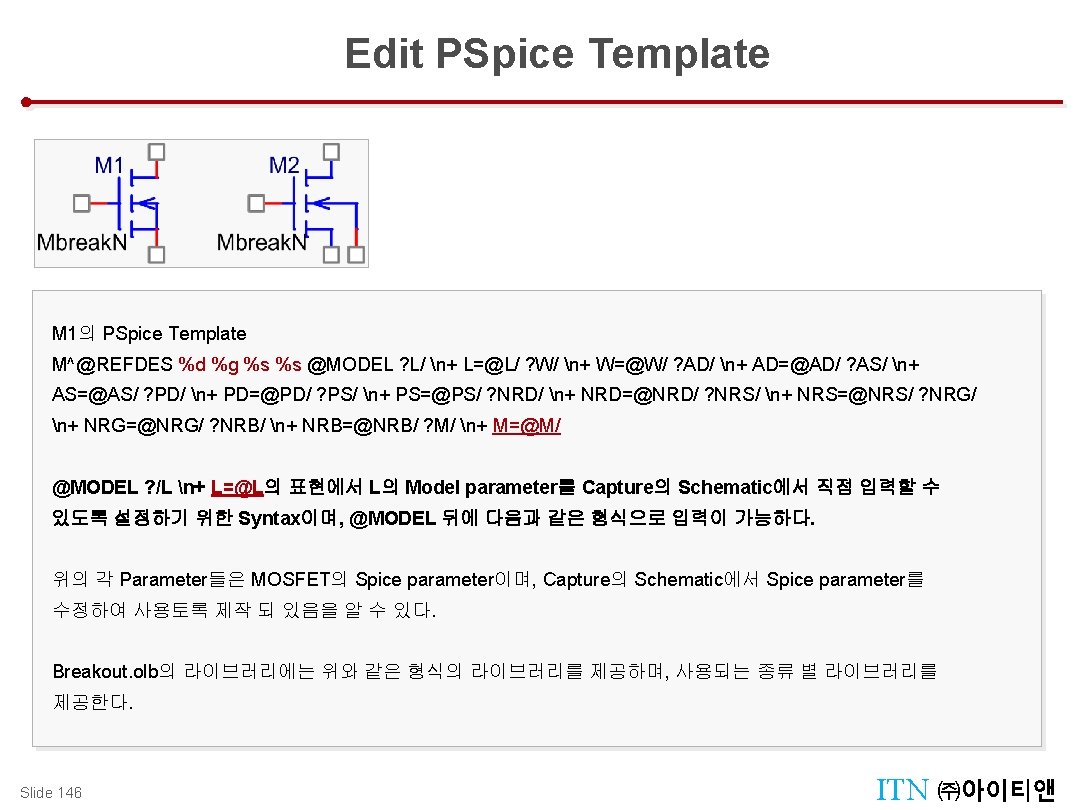

PSpice Template Example Edit PSpice Template M 1의 PSpice Template M^@REFDES %d %g %s %s @MODEL ? L/ n+ L=@L/ ? W/ n+ W=@W/ ? AD/ n+ AD=@AD/ ? AS/ n+ AS=@AS/ ? PD/ n+ PD=@PD/ ? PS/ n+ PS=@PS/ ? NRD/ n+ NRD=@NRD/ ? NRS/ n+ NRS=@NRS/ ? NRG/ n+ NRG=@NRG/ ? NRB/ n+ NRB=@NRB/ ? M/ n+ M=@M/ @MODEL ? /L n+ L=@L의 표현에서 L의 Model parameter를 Capture의 Schematic에서 직접 입력할 수 있도록 설정하기 위한 Syntax이며, @MODEL 뒤에 다음과 같은 형식으로 입력이 가능하다. 위의 각 Parameter들은 MOSFET의 Spice parameter이며, Capture의 Schematic에서 Spice parameter를 수정하여 사용토록 제작 되 있음을 알 수 있다. Breakout. olb의 라이브러리에는 위와 같은 형식의 라이브러리를 제공하며, 사용되는 종류 별 라이브러리를 제공한다. Slide 146 ITN ㈜아이티앤

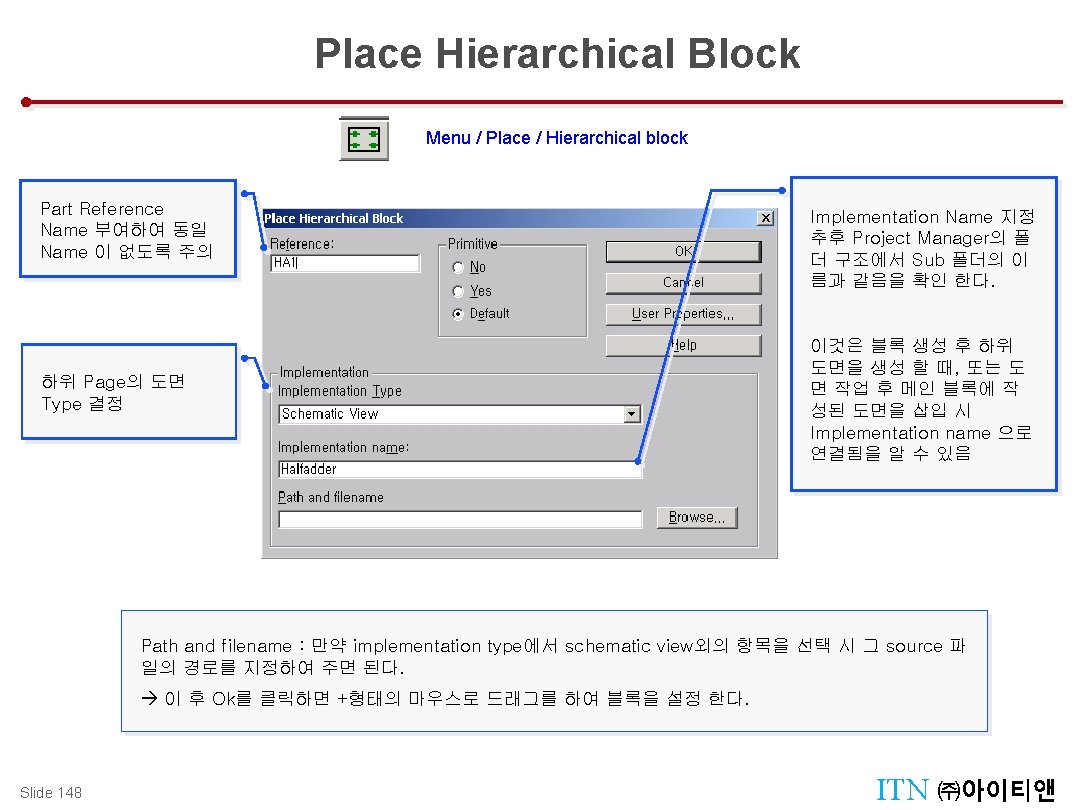

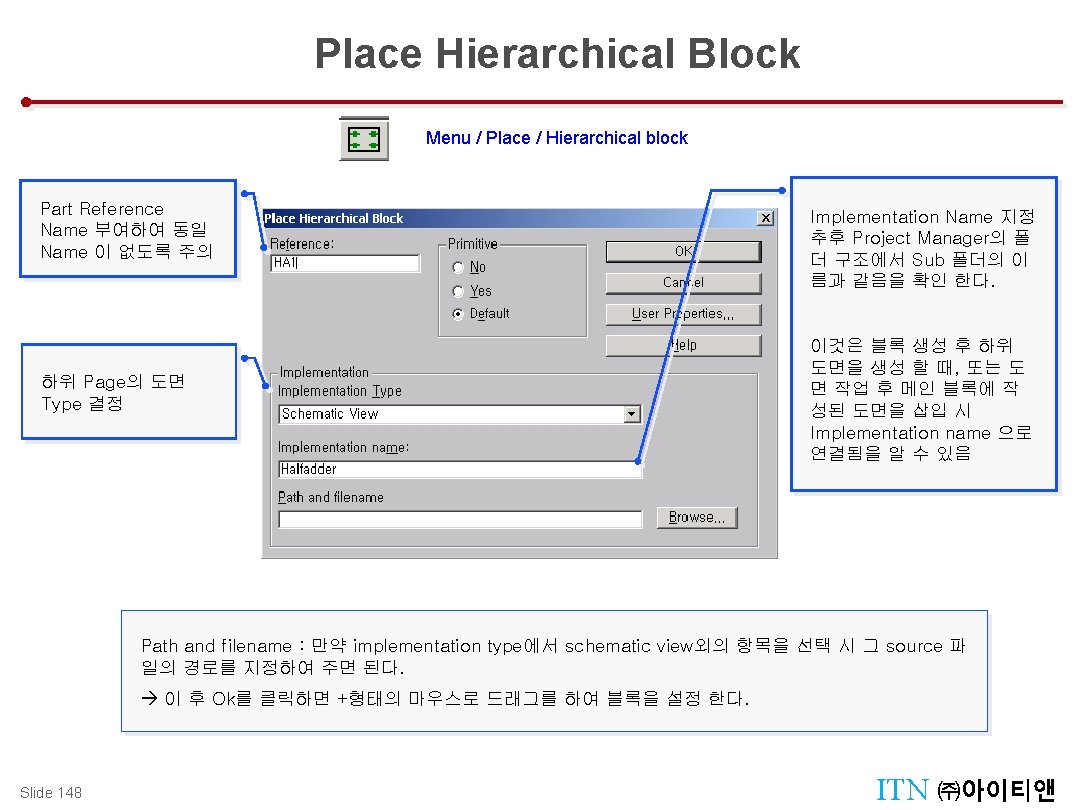

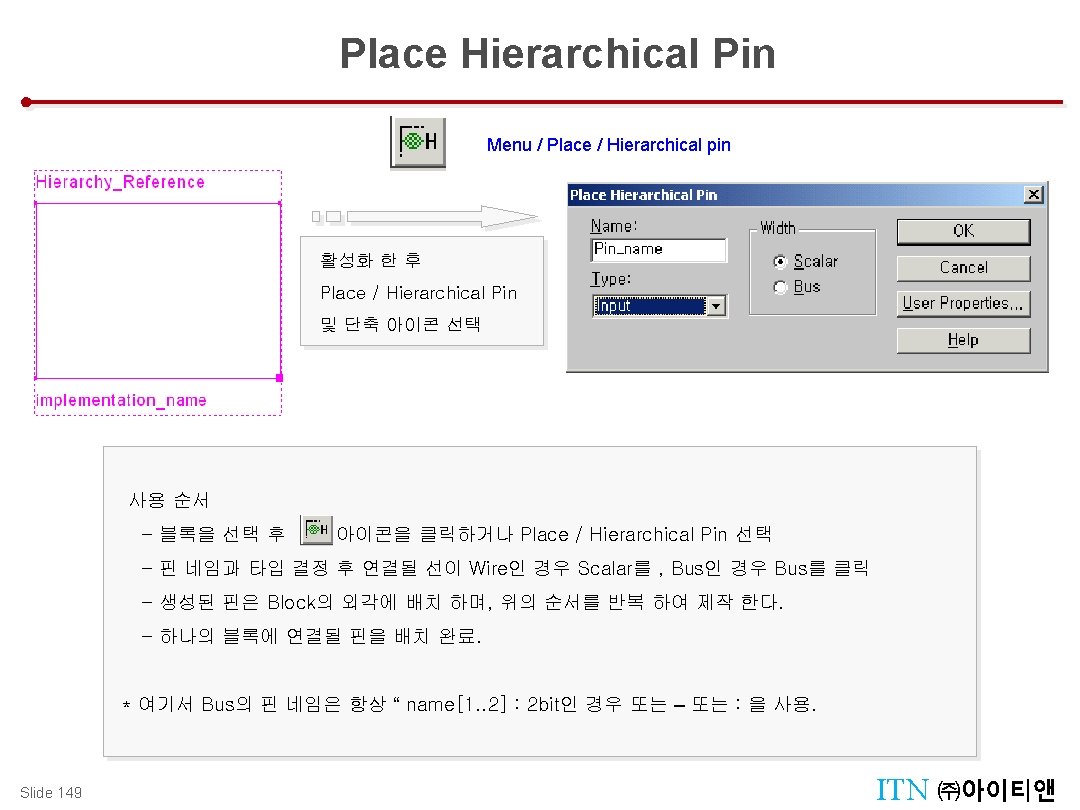

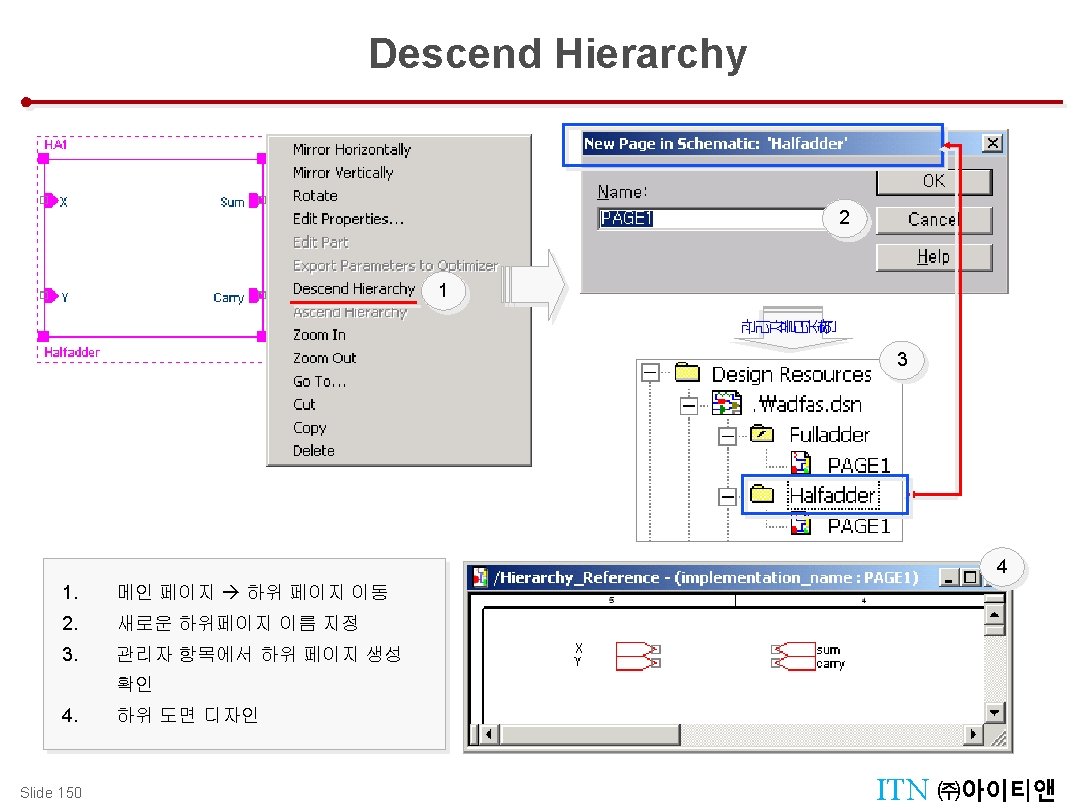

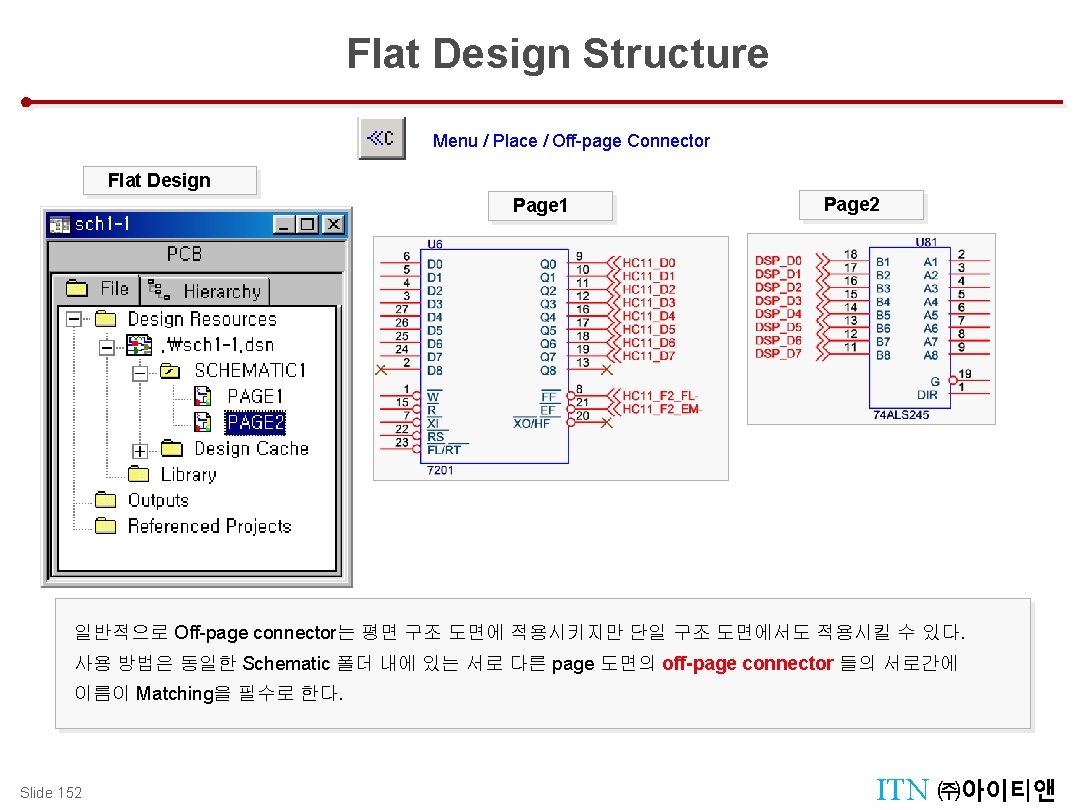

Design Structure (Hierarchy , Flat Design) Design Management : Manager Tool Place hierarchical block Place hierarchical pin Hierarchical design structure Flat Design structure review Capture Symbol Slide 147 ITN ㈜아이티앤

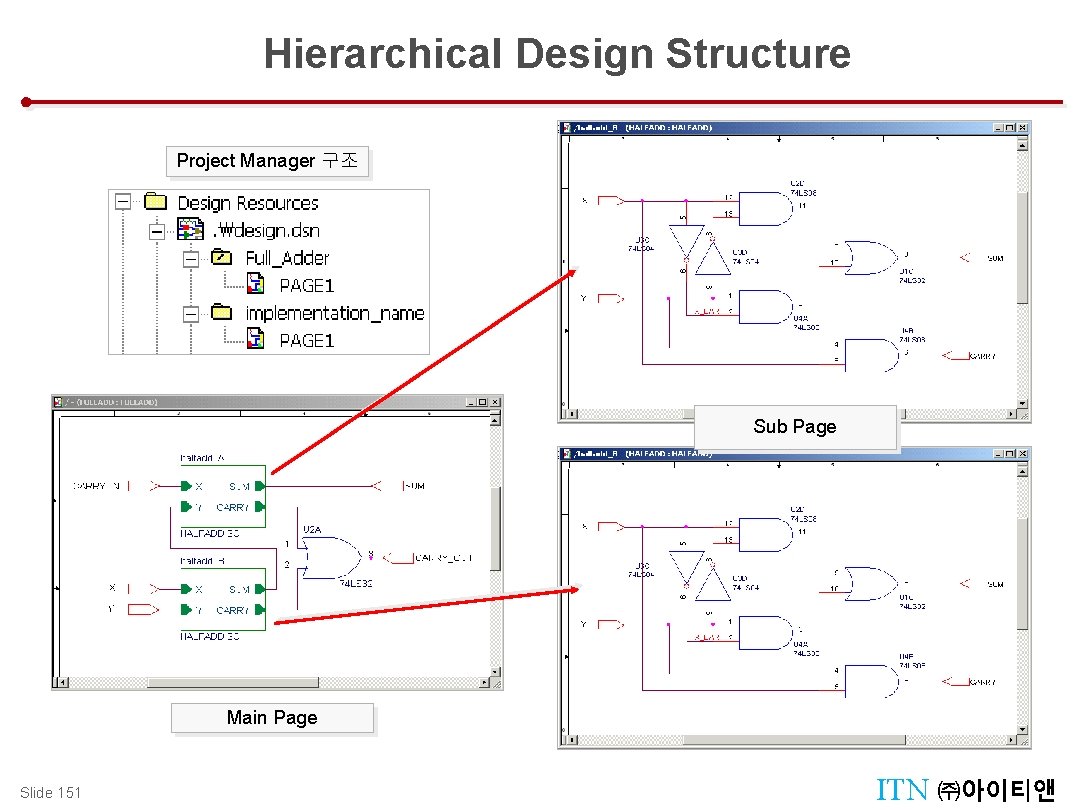

Hierarchical Design Structure Project Manager 구조 Sub Page Main Page Slide 151 ITN ㈜아이티앤

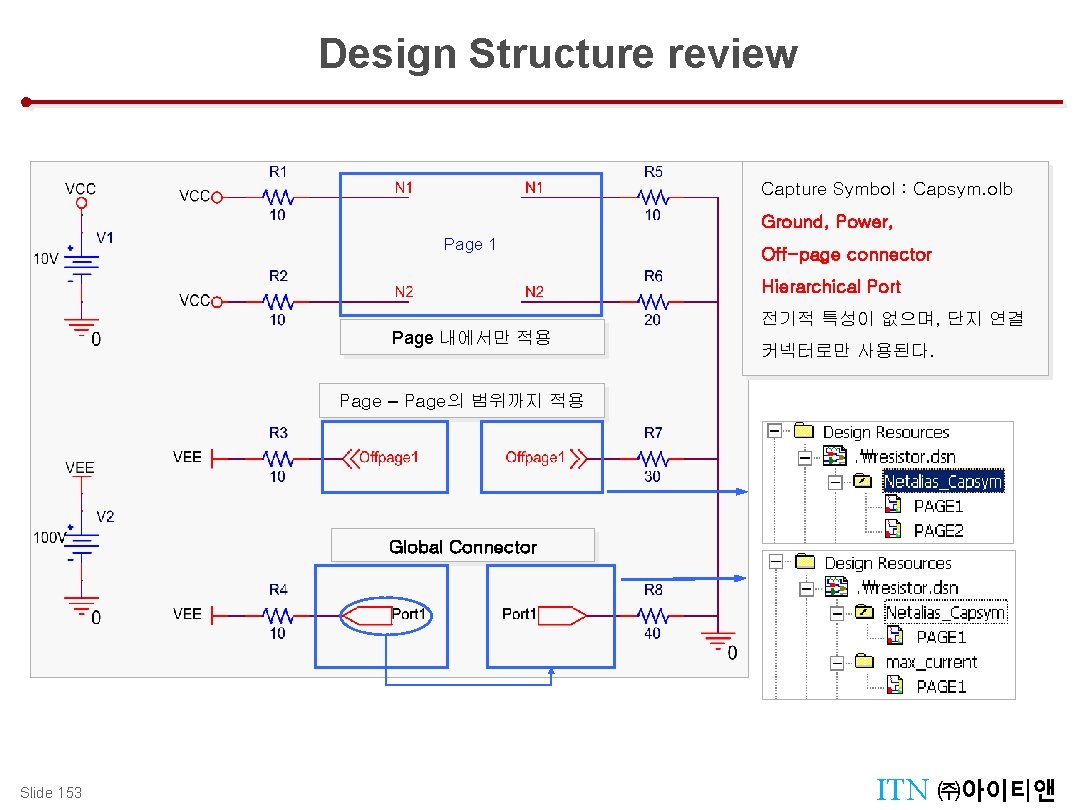

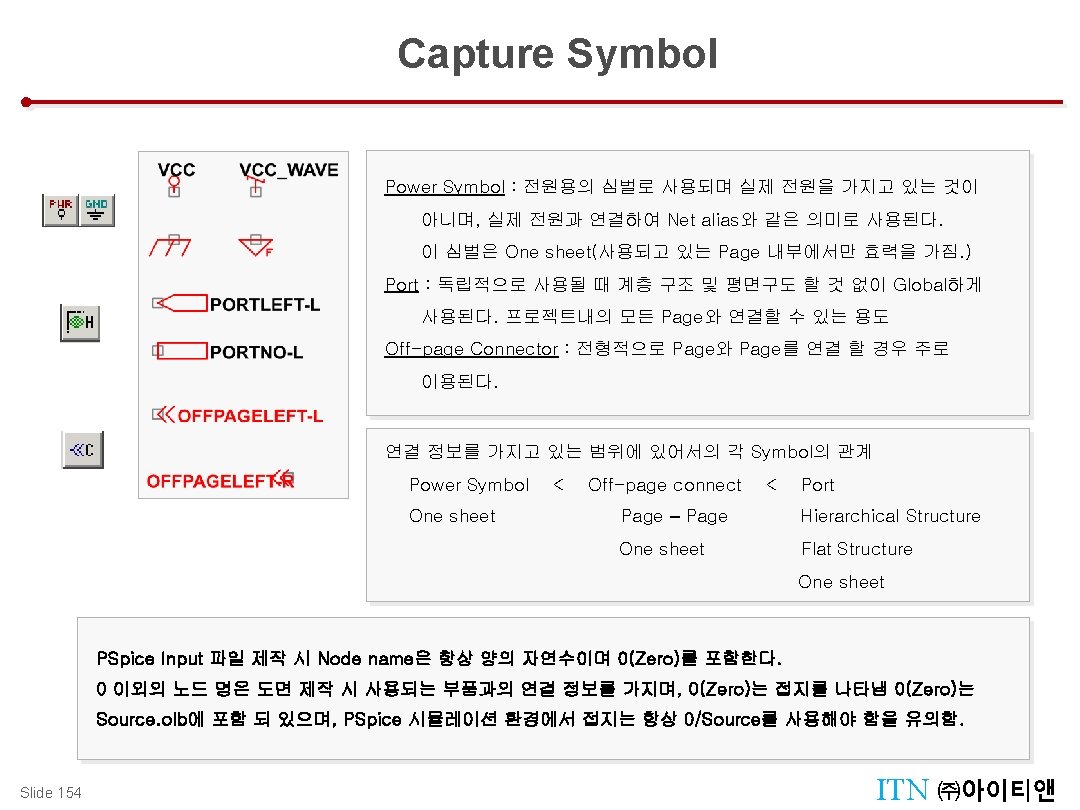

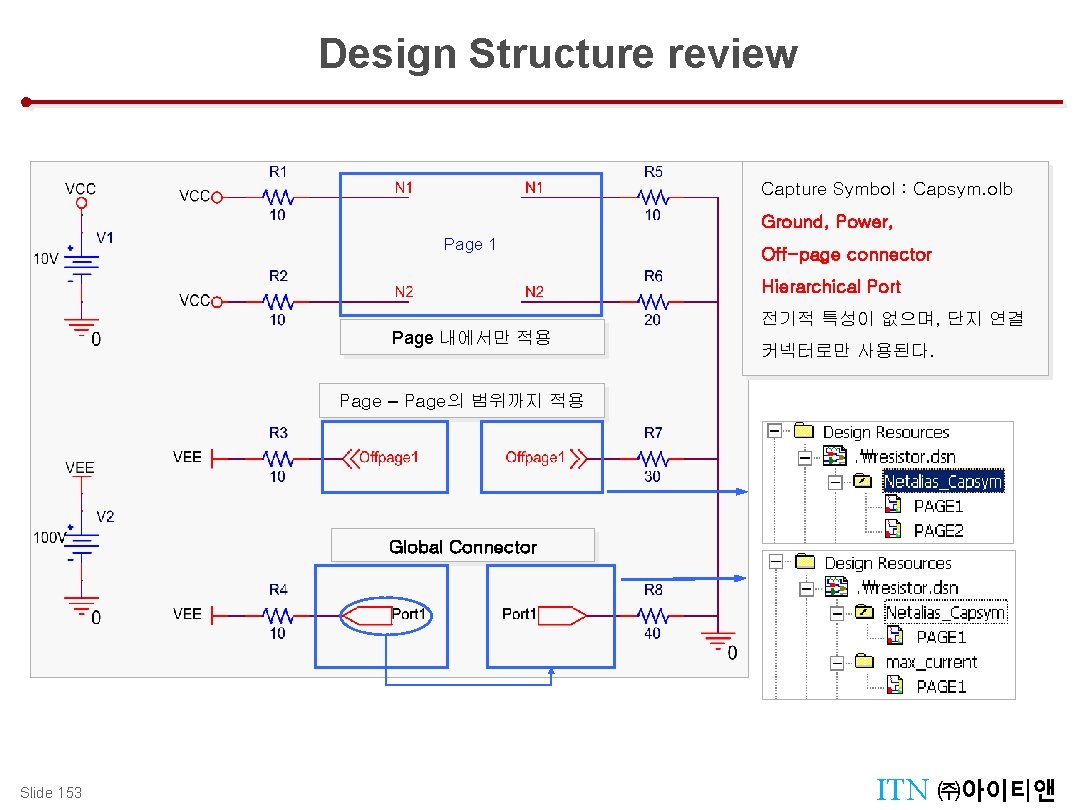

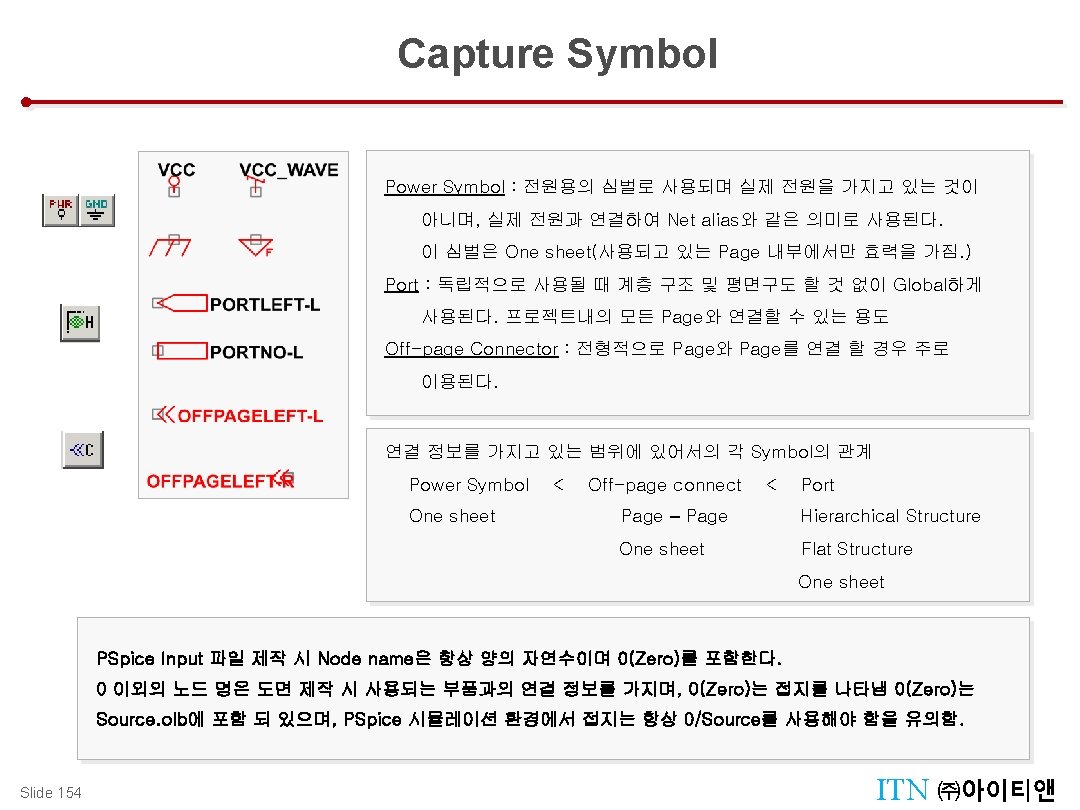

Design Structure review Capture Symbol : Capsym. olb Ground, Power, Page 1 Off-page connector Hierarchical Port Page 내에서만 적용 전기적 특성이 없으며, 단지 연결 커넥터로만 사용된다. Page – Page의 범위까지 적용 Global Connector Slide 153 ITN ㈜아이티앤

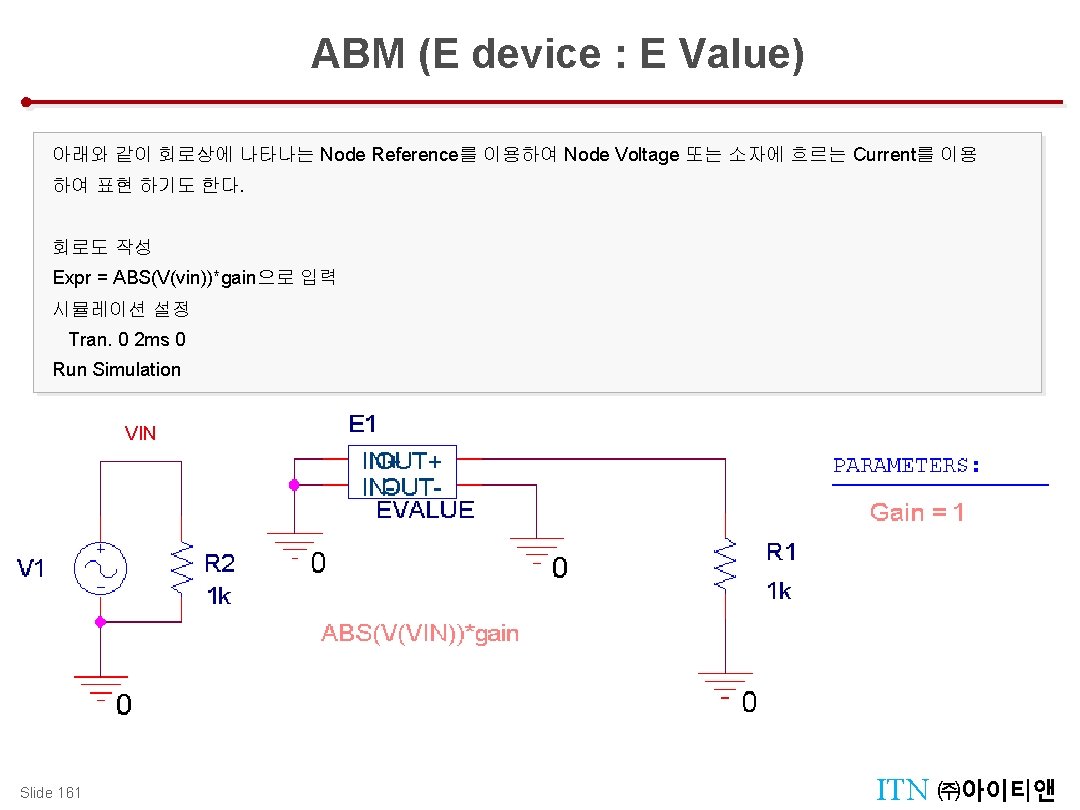

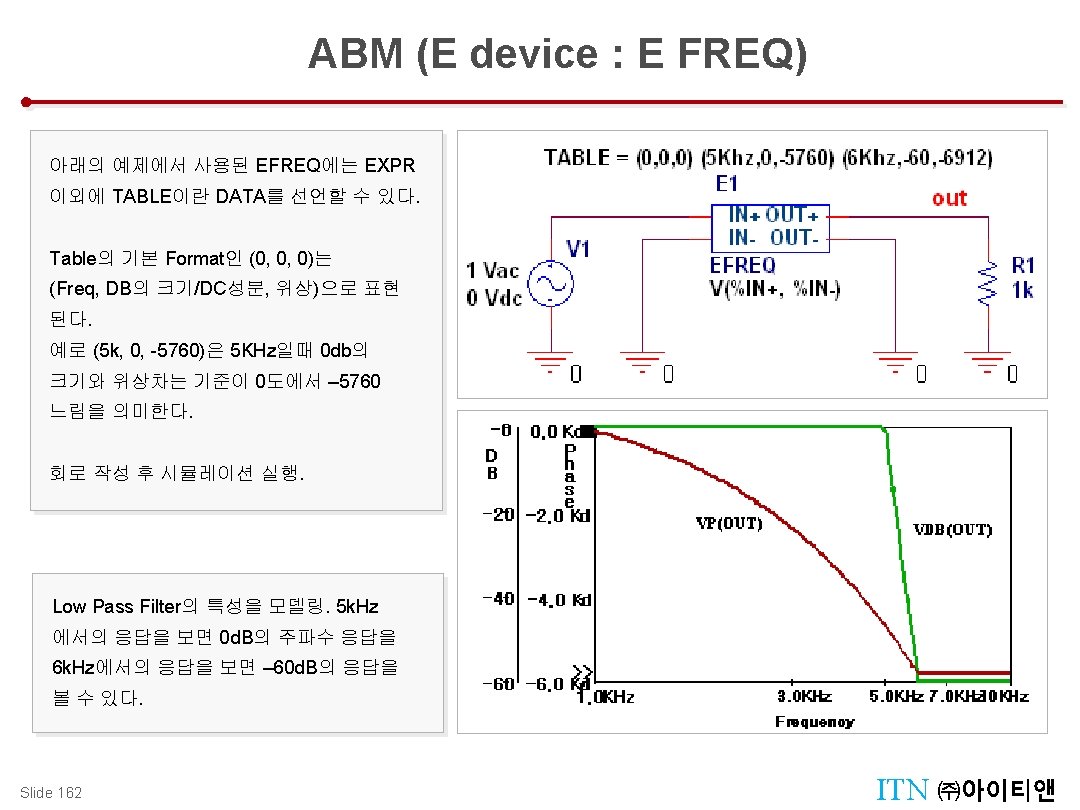

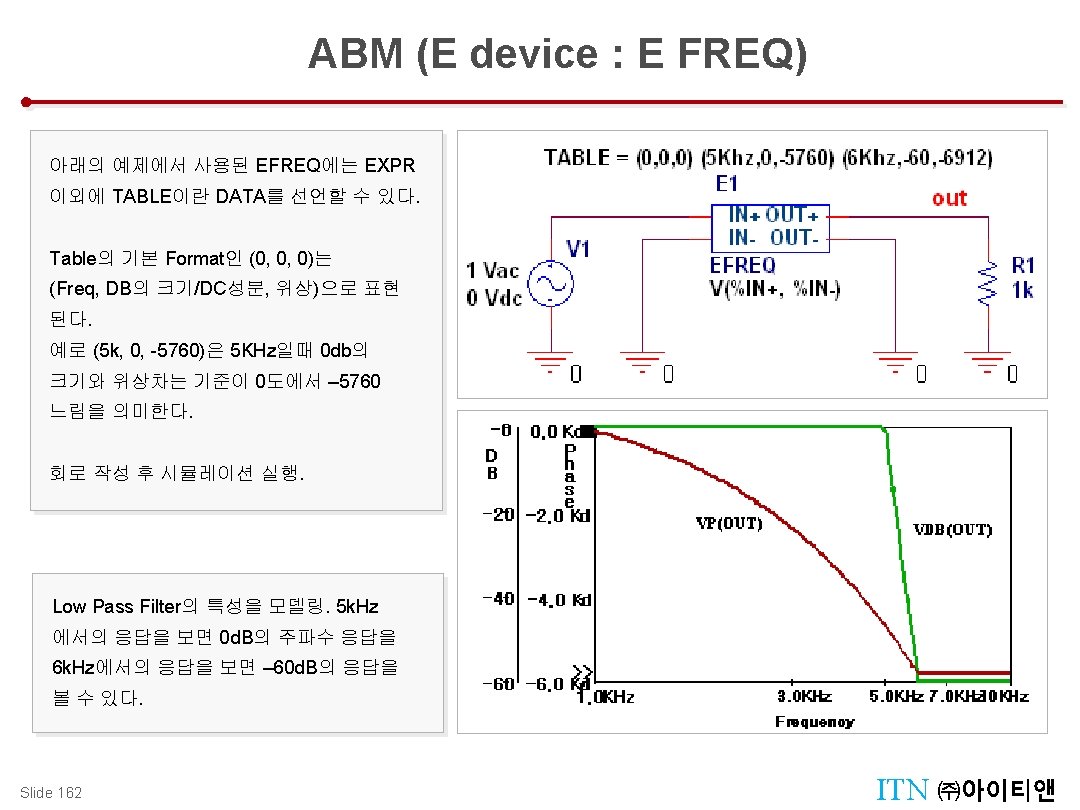

Analog Behavioral Models Design Management : Manager Tool Analog Behavior Modeling library Expression ABM (E device : E Value) ABM (E device : E FREQ) Slide 155 ITN ㈜아이티앤

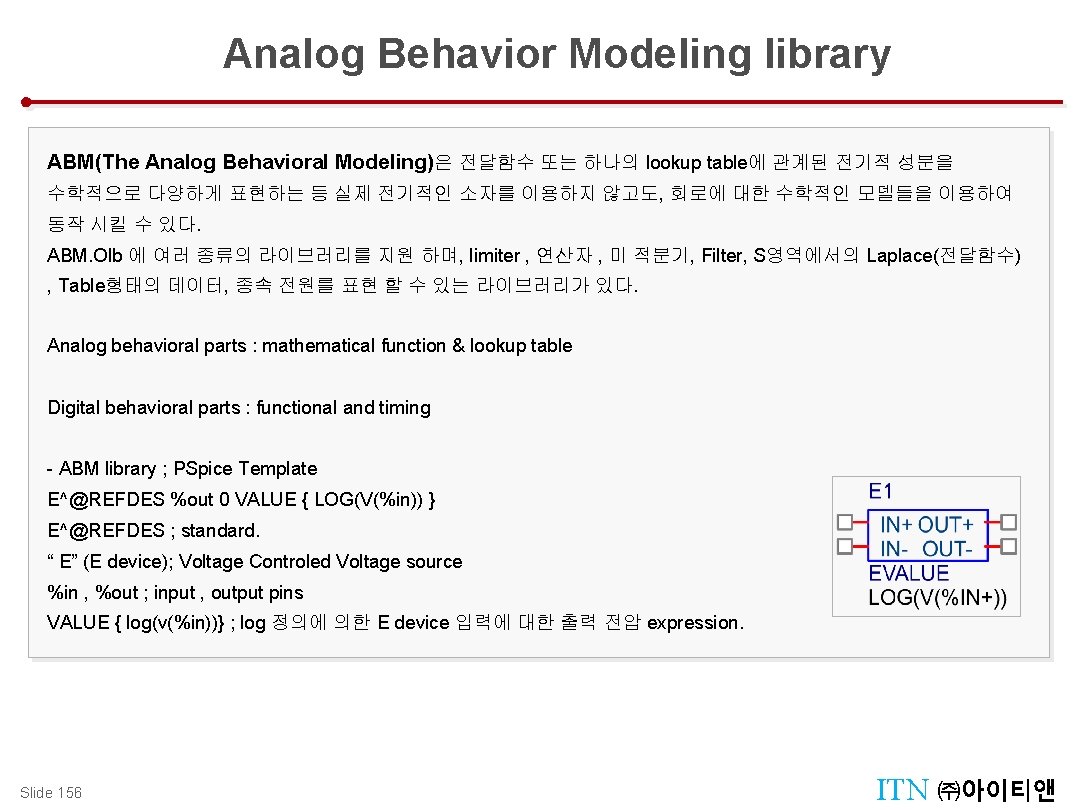

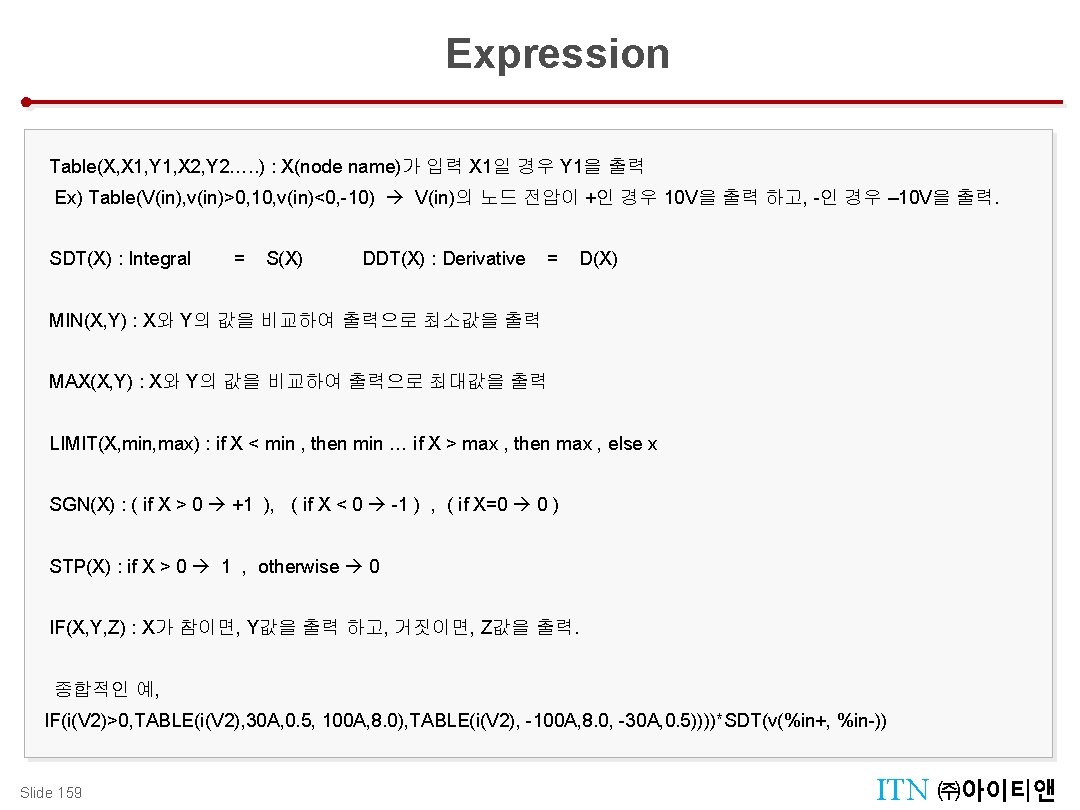

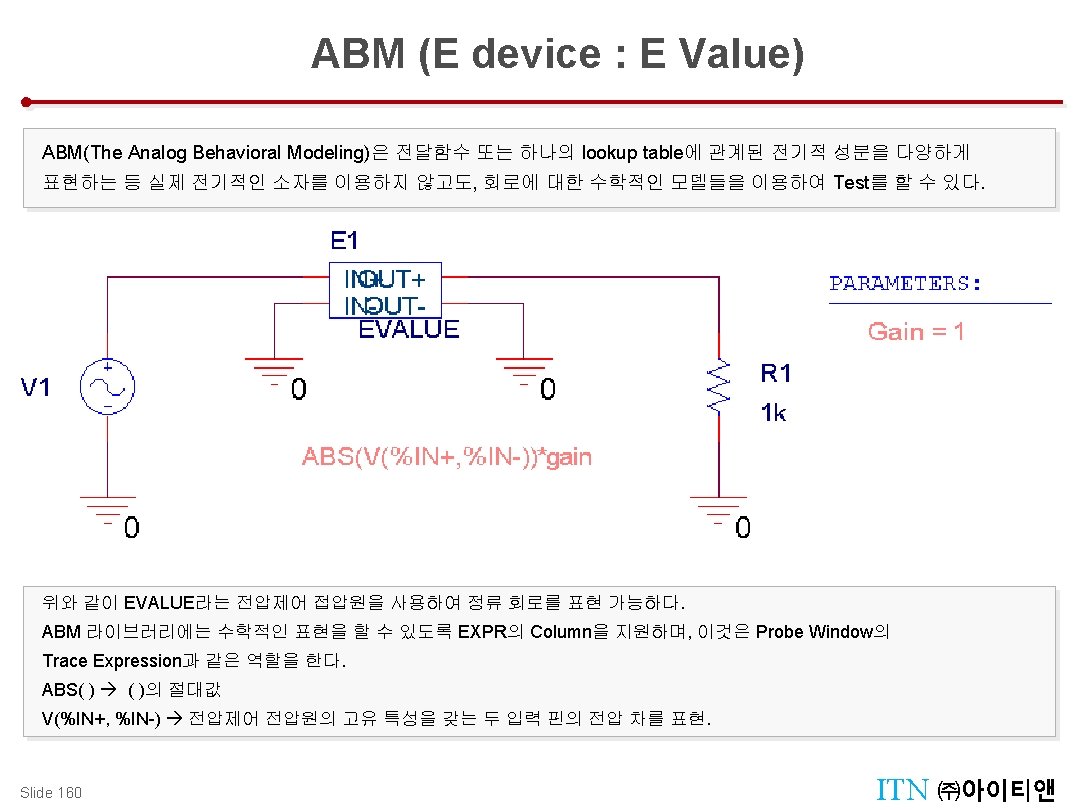

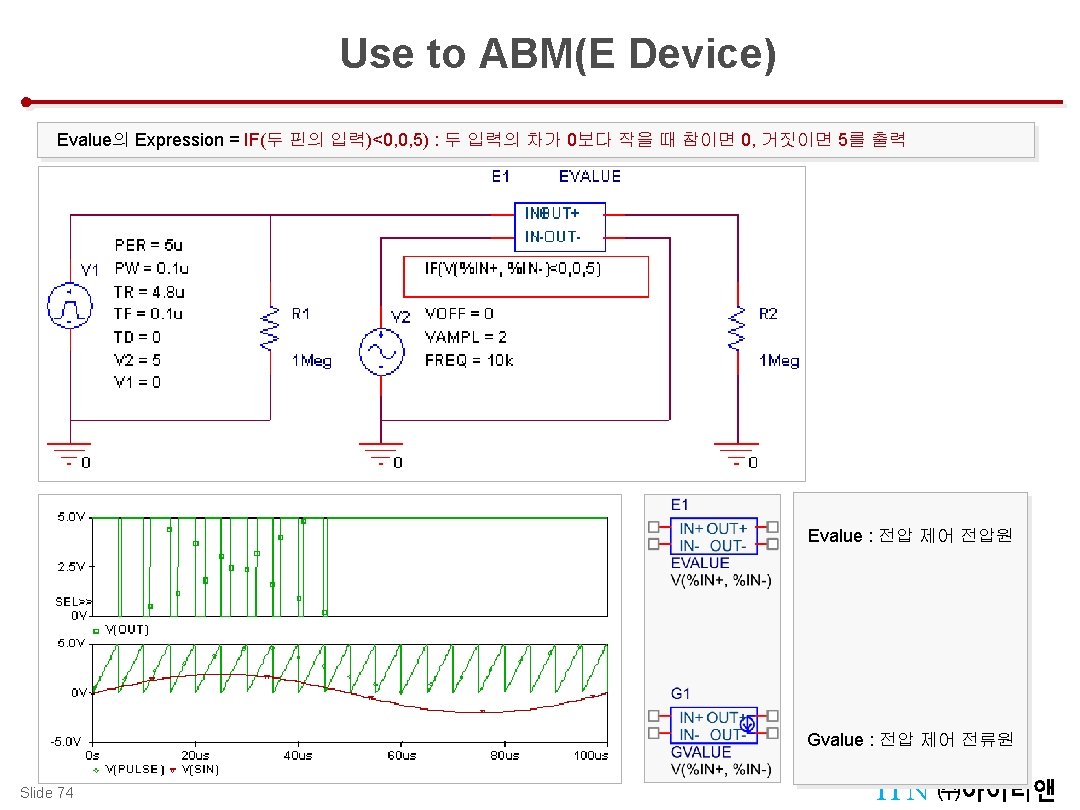

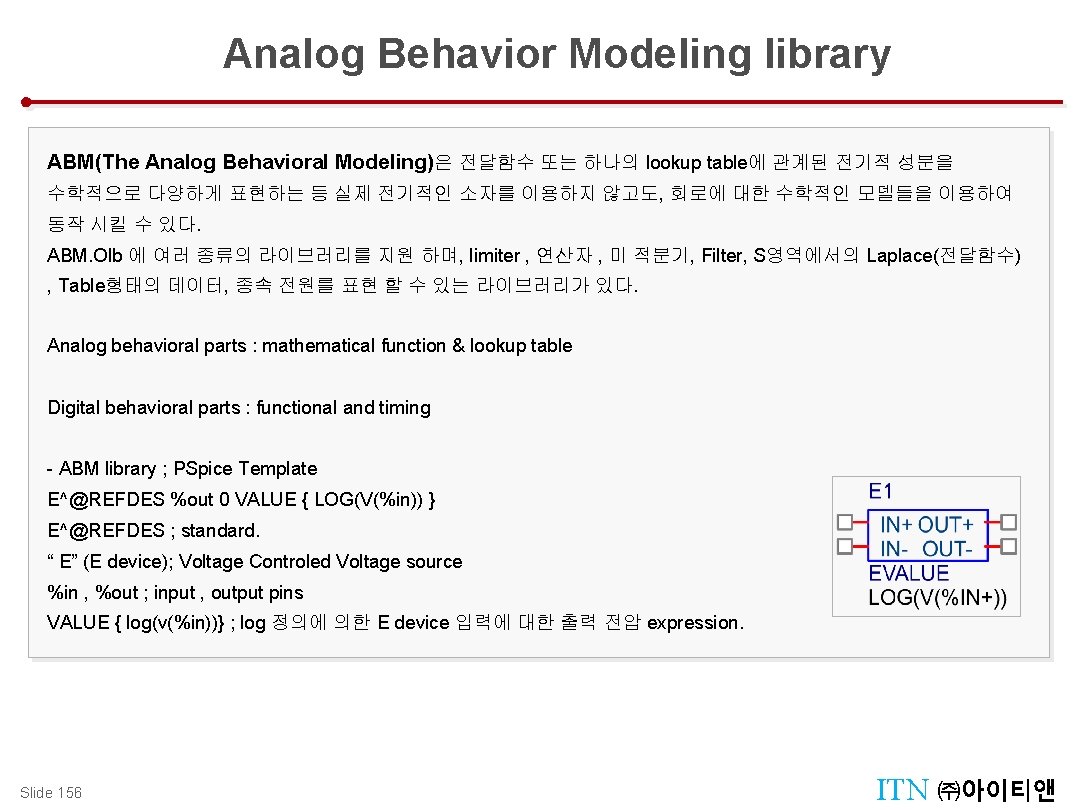

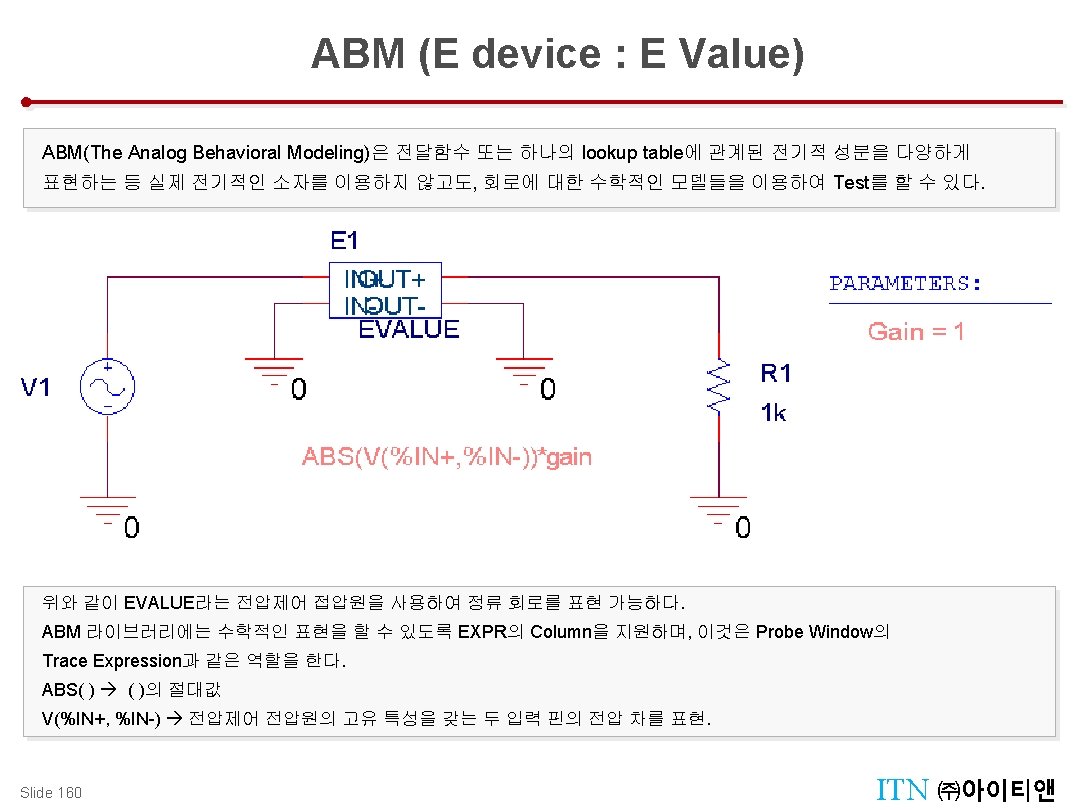

Analog Behavior Modeling library ABM (Analog Behavior Modeling) ABM(The Analog Behavioral Modeling)은 전달함수 또는 하나의 lookup table에 관계된 전기적 성분을 수학적으로 다양하게 표현하는 등 실제 전기적인 소자를 이용하지 않고도, 회로에 대한 수학적인 모델들을 이용하여 동작 시킬 수 있다. ABM. Olb 에 여러 종류의 라이브러리를 지원 하며, limiter , 연산자 , 미 적분기, Filter, S영역에서의 Laplace(전달함수) , Table형태의 데이터, 종속 전원를 표현 할 수 있는 라이브러리가 있다. Analog behavioral parts : mathematical function & lookup table Digital behavioral parts : functional and timing - ABM library ; PSpice Template E^@REFDES %out 0 VALUE { LOG(V(%in)) } E^@REFDES ; standard. “ E” (E device); Voltage Controled Voltage source %in , %out ; input , output pins VALUE { log(v(%in))} ; log 정의에 의한 E device 입력에 대한 출력 전압 expression. Slide 156 ITN ㈜아이티앤

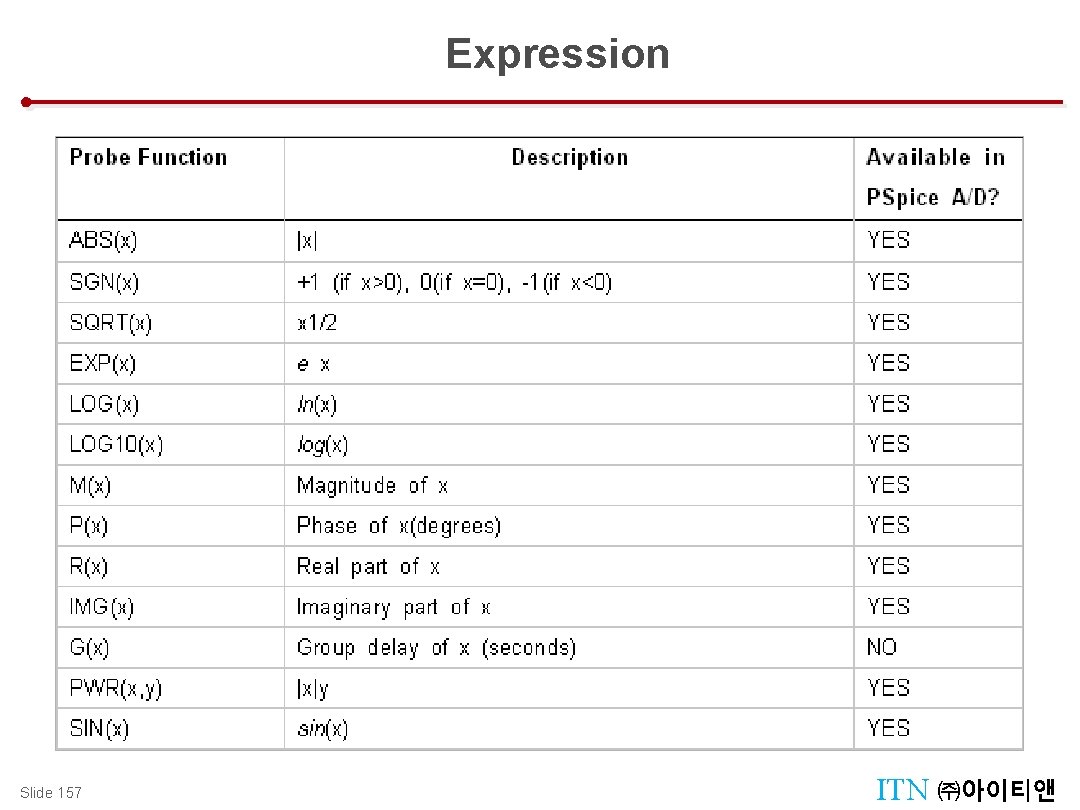

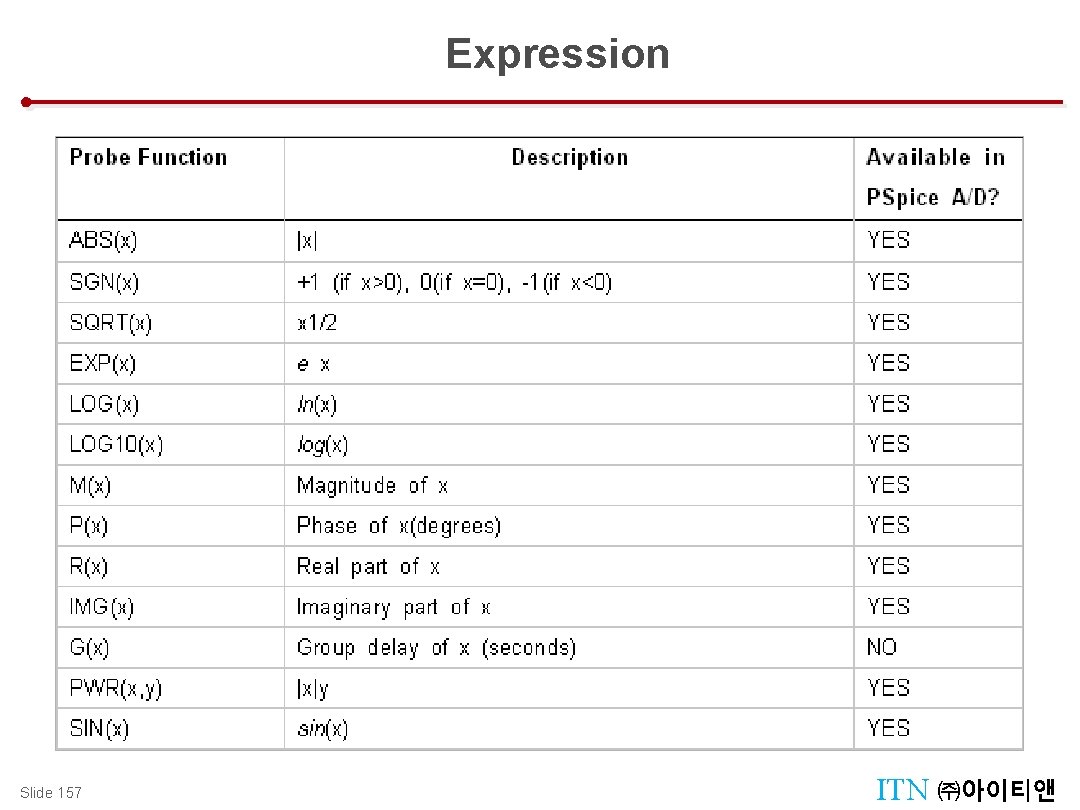

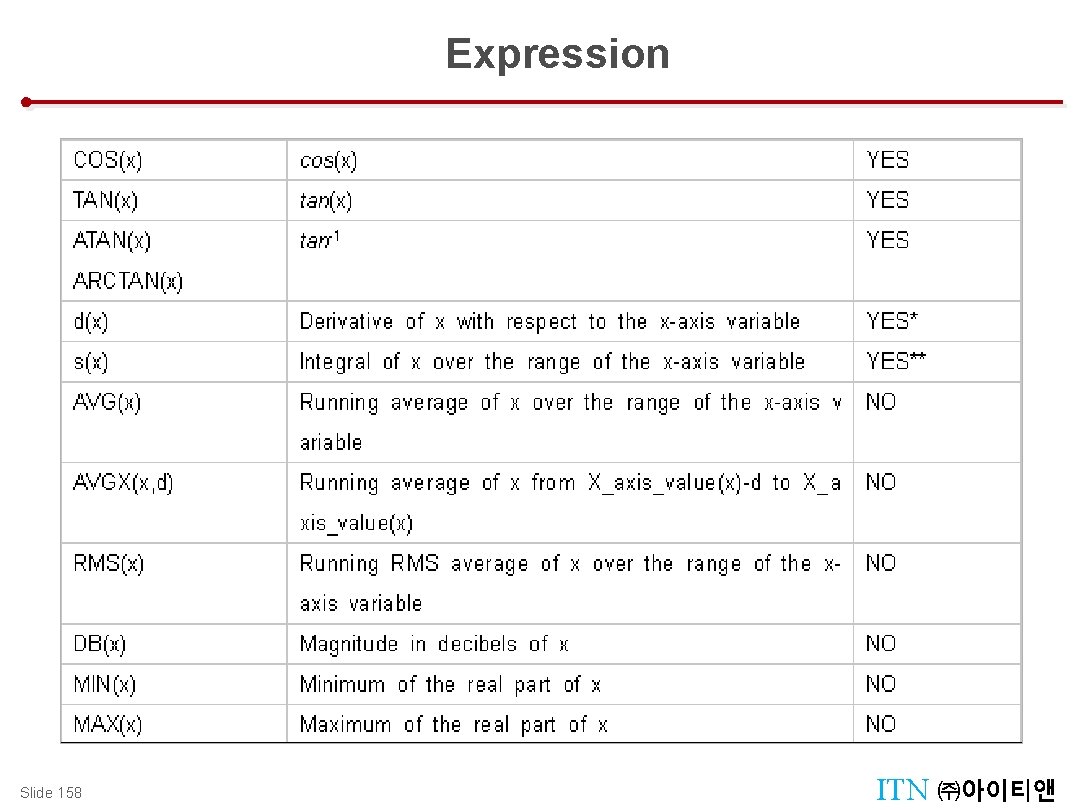

Expression Slide 157 ITN ㈜아이티앤

ABM (Expression) Slide 158 Expression ITN ㈜아이티앤

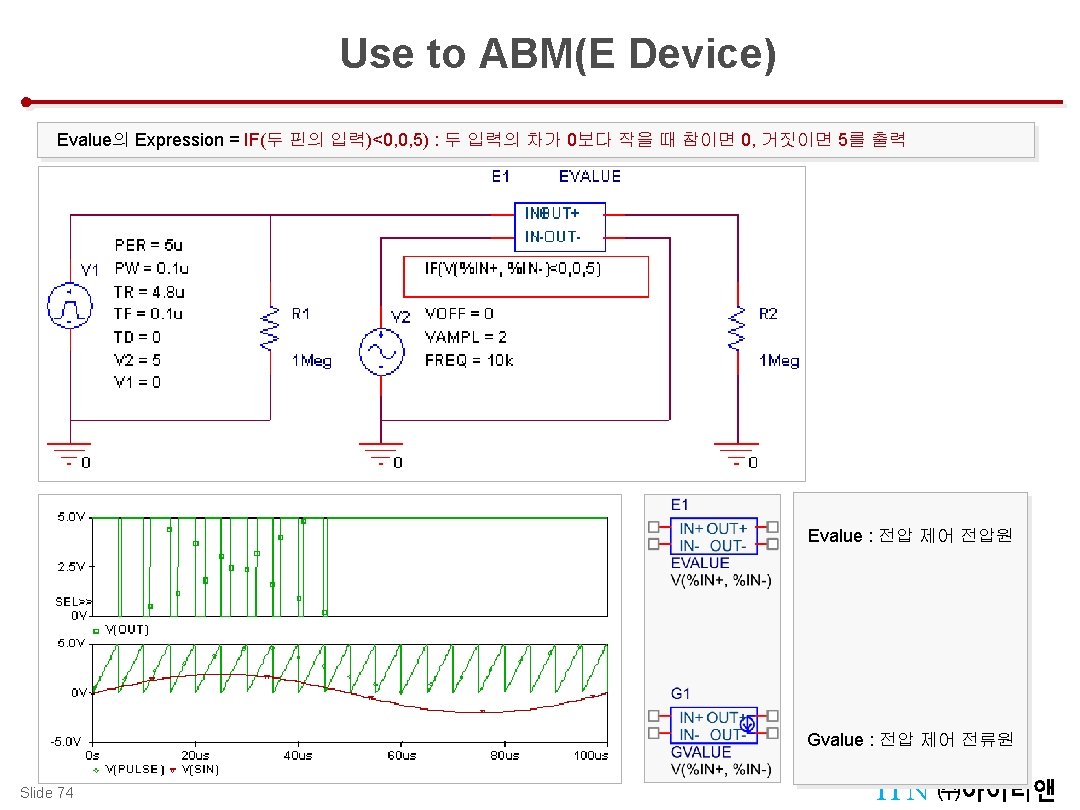

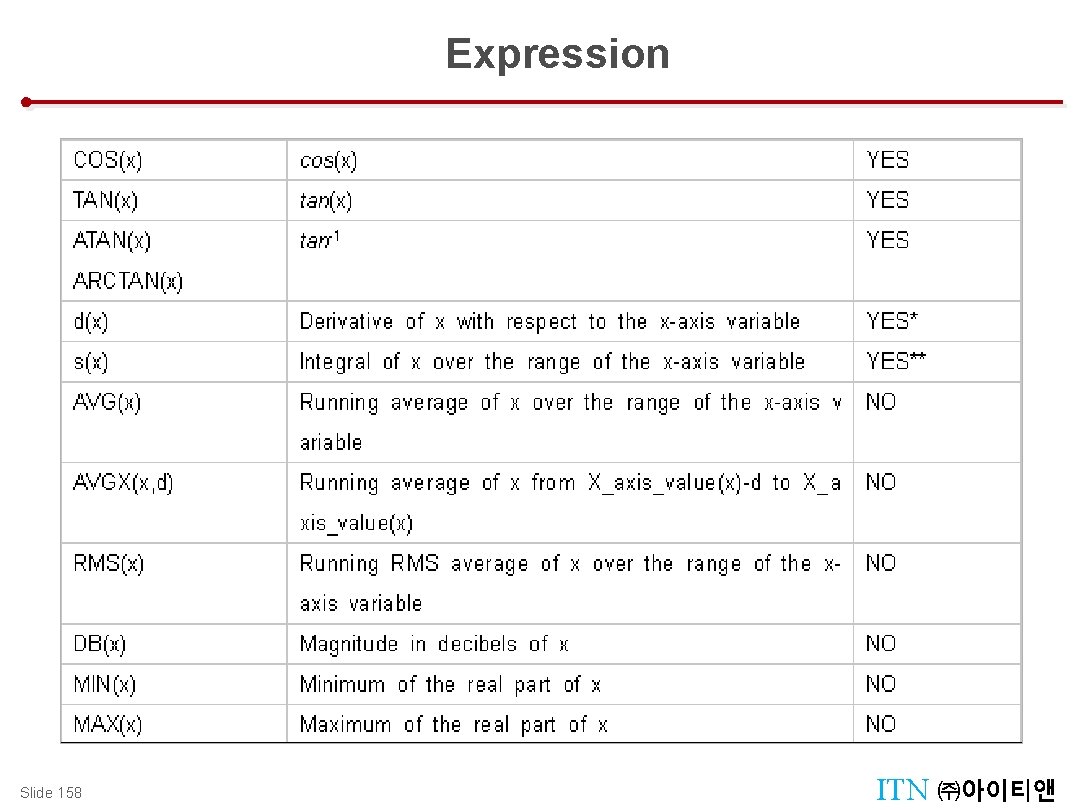

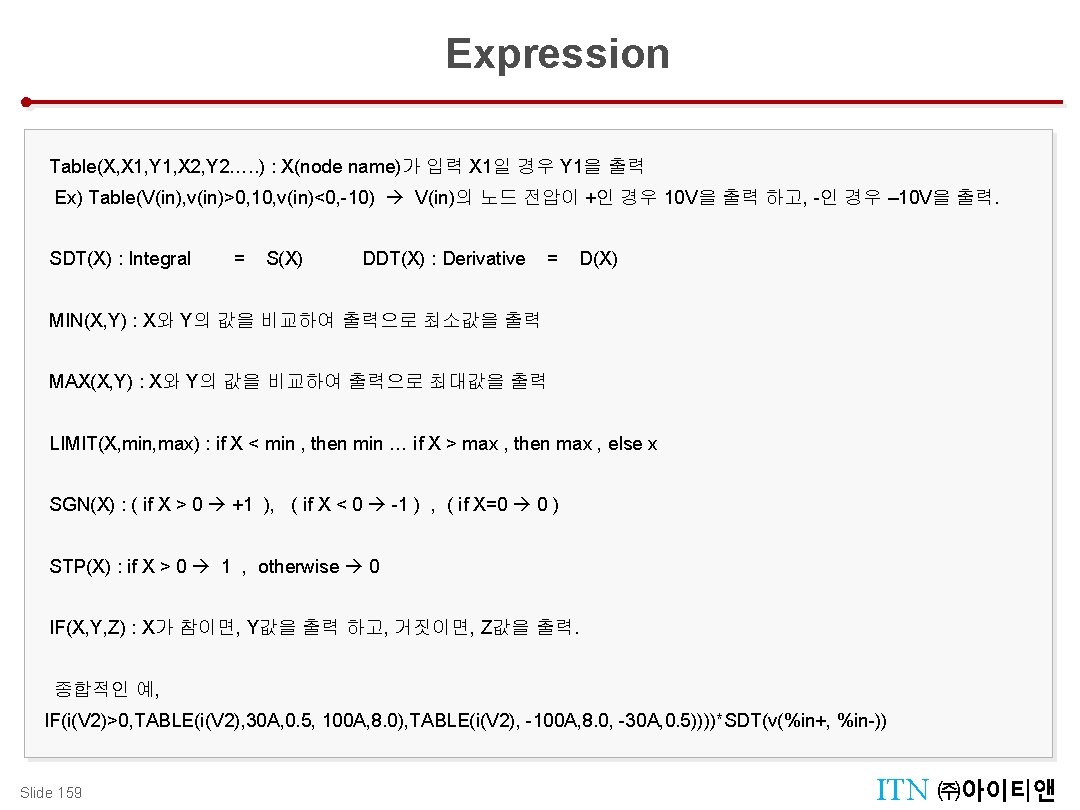

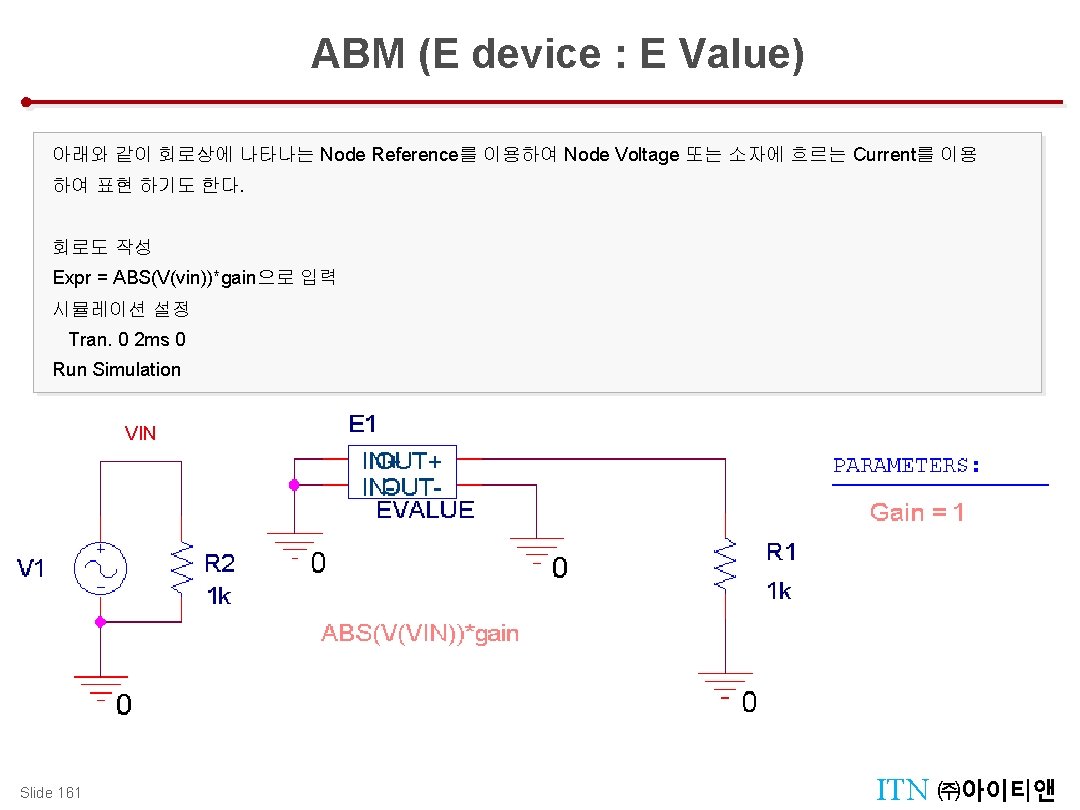

ABM (Other Function) Expression Table(X, X 1, Y 1, X 2, Y 2…. . ) : X(node name)가 입력 X 1일 경우 Y 1을 출력 Ex) Table(V(in), v(in)>0, 10, v(in)<0, -10) V(in)의 노드 전압이 +인 경우 10 V을 출력 하고, -인 경우 – 10 V을 출력. SDT(X) : Integral = S(X) DDT(X) : Derivative = D(X) MIN(X, Y) : X와 Y의 값을 비교하여 출력으로 최소값을 출력 MAX(X, Y) : X와 Y의 값을 비교하여 출력으로 최대값을 출력 LIMIT(X, min, max) : if X < min , then min … if X > max , then max , else x SGN(X) : ( if X > 0 +1 ), ( if X < 0 -1 ) , ( if X=0 0 ) STP(X) : if X > 0 1 , otherwise 0 IF(X, Y, Z) : X가 참이면, Y값을 출력 하고, 거짓이면, Z값을 출력. 종합적인 예, IF(i(V 2)>0, TABLE(i(V 2), 30 A, 0. 5, 100 A, 8. 0), TABLE(i(V 2), -100 A, 8. 0, -30 A, 0. 5))))*SDT(v(%in+, %in-)) Slide 159 ITN ㈜아이티앤

PSpice Training Guide Slide 163 ITN ㈜아이티앤