PSI 3441 Arquitetura de Sistemas Embarcados Registradores Memria

PSI 3441 – Arquitetura de Sistemas Embarcados - Registradores, Memória - Instruções de Desvio Escola Politécnica da Universidade de São Paulo Prof. Gustavo Rehder – grehder@lme. usp. br Prof. Sergio Takeo – kofuji@usp. br Prof. Antonio Seabra – acseabra@lsi. usp. br 2017

PSI 3441 – Arquitetura de Sistemas Embarcados - Registradores

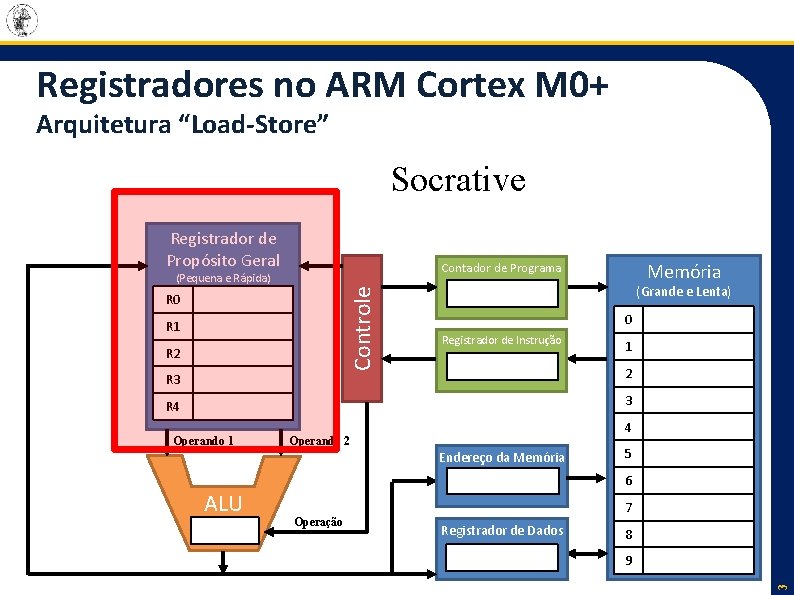

Registradores no ARM Cortex M 0+ Arquitetura “Load-Store” Socrative Registrador de Propósito Geral Memória Contador de Programa Controle (Pequena e Rápida) R 0 R 1 R 2 (Grande e Lenta) 0 Registrador de Instrução 1 R 3 2 R 4 3 Operando 2 Endereço da Memória ALU 5 6 7 Operação Registrador de Dados 8 9 3 Operando 1 4

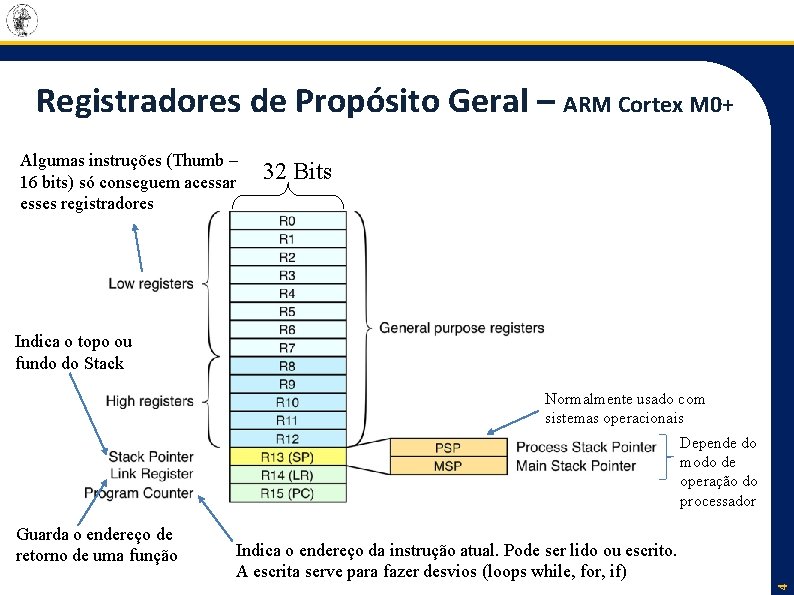

Registradores de Propósito Geral – ARM Cortex M 0+ Algumas instruções (Thumb – 16 bits) só conseguem acessar esses registradores 32 Bits Indica o topo ou fundo do Stack Normalmente usado com sistemas operacionais Depende do modo de operação do processador Indica o endereço da instrução atual. Pode ser lido ou escrito. A escrita serve para fazer desvios (loops while, for, if) 4 Guarda o endereço de retorno de uma função

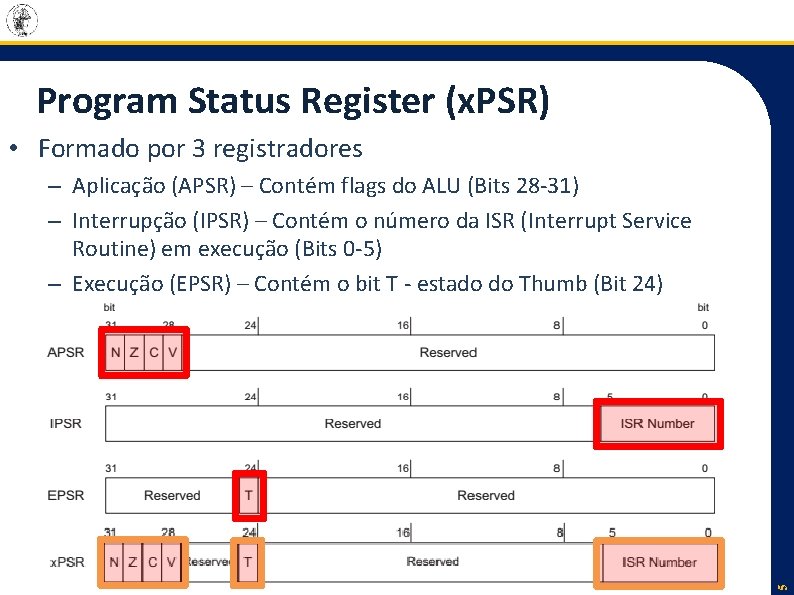

Program Status Register (x. PSR) • Formado por 3 registradores 5 – Aplicação (APSR) – Contém flags do ALU (Bits 28 -31) – Interrupção (IPSR) – Contém o número da ISR (Interrupt Service Routine) em execução (Bits 0 -5) – Execução (EPSR) – Contém o bit T - estado do Thumb (Bit 24)

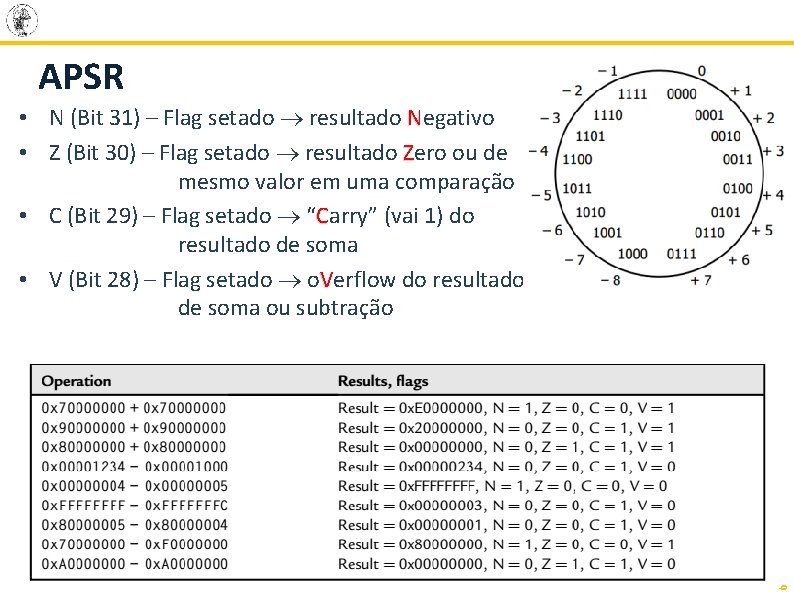

APSR 6 • N (Bit 31) – Flag setado resultado N egativo • Z (Bit 30) – Flag setado resultado Z ero ou de mesmo valor em uma comparação • C (Bit 29) – Flag setado “Carry” (vai 1) do resultado de soma • V (Bit 28) – Flag setado o. V erflow do resultado de soma ou subtração

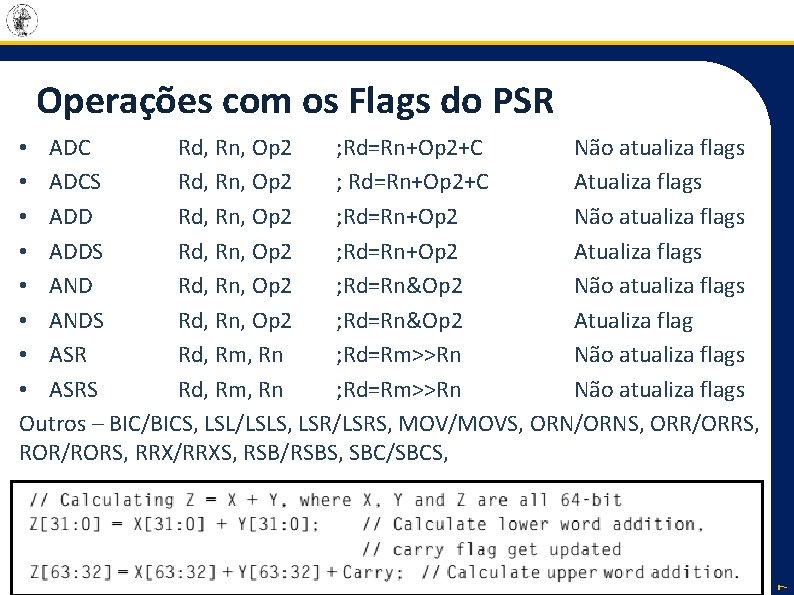

Operações com os Flags do PSR 7 • ADC Rd, Rn, Op 2 ; Rd=Rn+Op 2+C Não atualiza flags • ADCS Rd, Rn, Op 2 ; Rd=Rn+Op 2+C Atualiza flags • ADD Rd, Rn, Op 2 ; Rd=Rn+Op 2 Não atualiza flags • ADDS Rd, Rn, Op 2 ; Rd=Rn+Op 2 Atualiza flags • AND Rd, Rn, Op 2 ; Rd=Rn&Op 2 Não atualiza flags • ANDS Rd, Rn, Op 2 ; Rd=Rn&Op 2 Atualiza flag • ASR Rd, Rm, Rn ; Rd=Rm>>Rn Não atualiza flags • ASRS Rd, Rm, Rn ; Rd=Rm>>Rn Não atualiza flags Outros – BIC/BICS, LSL/LSLS, LSR/LSRS, MOV/MOVS, ORN/ORNS, ORR/ORRS, ROR/RORS, RRX/RRXS, RSB/RSBS, SBC/SBCS,

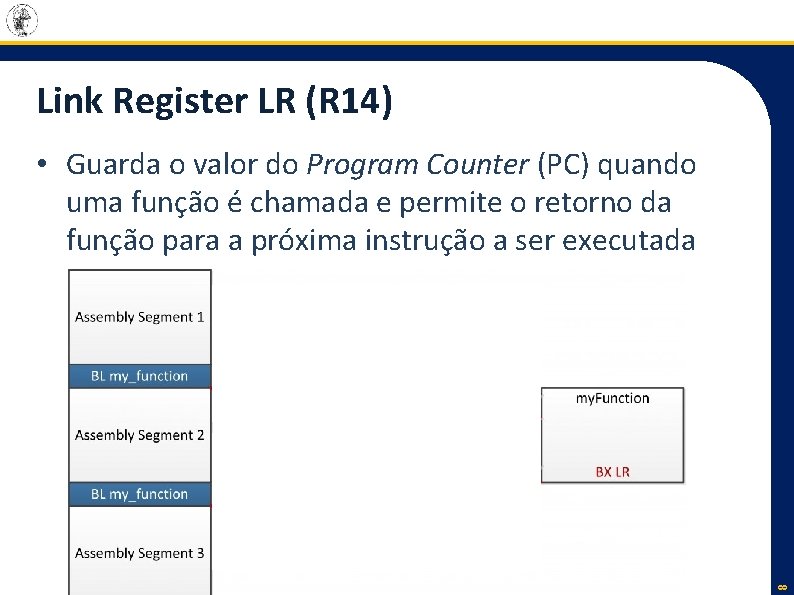

Link Register LR (R 14) 8 • Guarda o valor do Program Counter (PC) quando uma função é chamada e permite o retorno da função para a próxima instrução a ser executada

PSI 3441 – Arquitetura de Sistemas Embarcados - Memória – RAM (Stack e Heap) e Flash (instruções/código, tabelas)

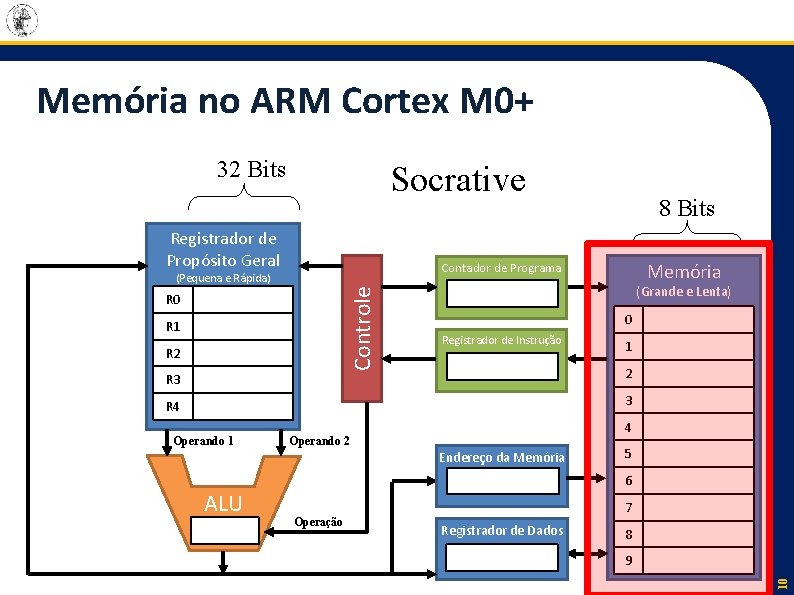

Memória no ARM Cortex M 0+ 32 Bits Socrative Registrador de Propósito Geral 8 Bits Memória Contador de Programa Controle (Pequena e Rápida) R 0 R 1 R 2 (Grande e Lenta) 0 Registrador de Instrução 1 R 3 2 R 4 3 Operando 2 Endereço da Memória ALU 5 6 7 Operação Registrador de Dados 8 9 10 Operando 1 4

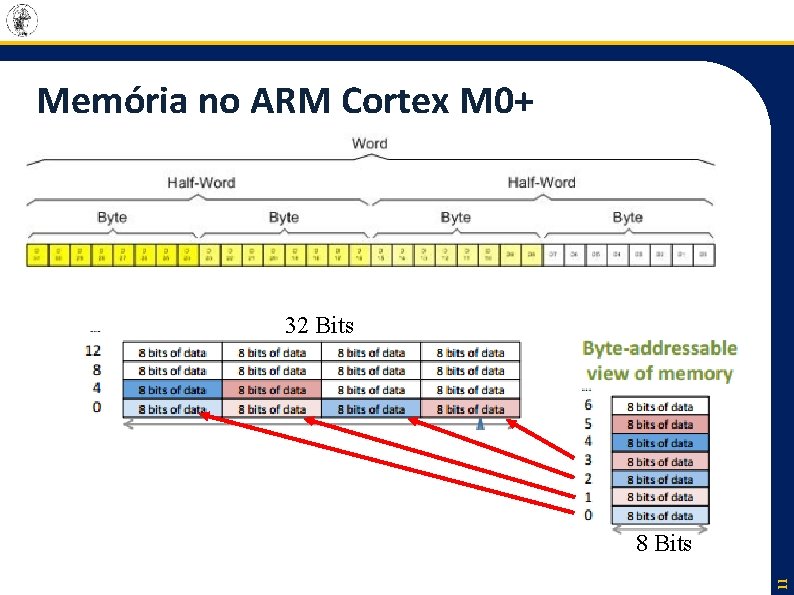

Memória no ARM Cortex M 0+ 32 Bits 11 8 Bits

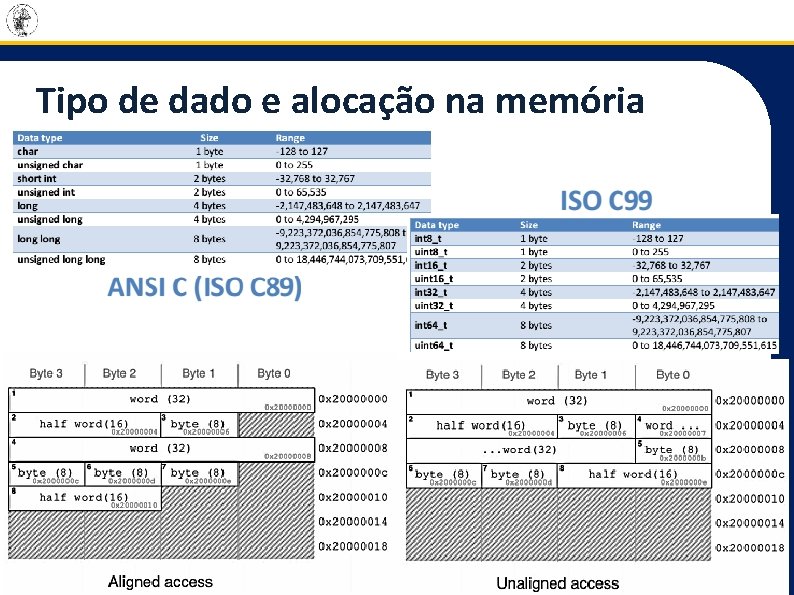

12 Tipo de dado e alocação na memória

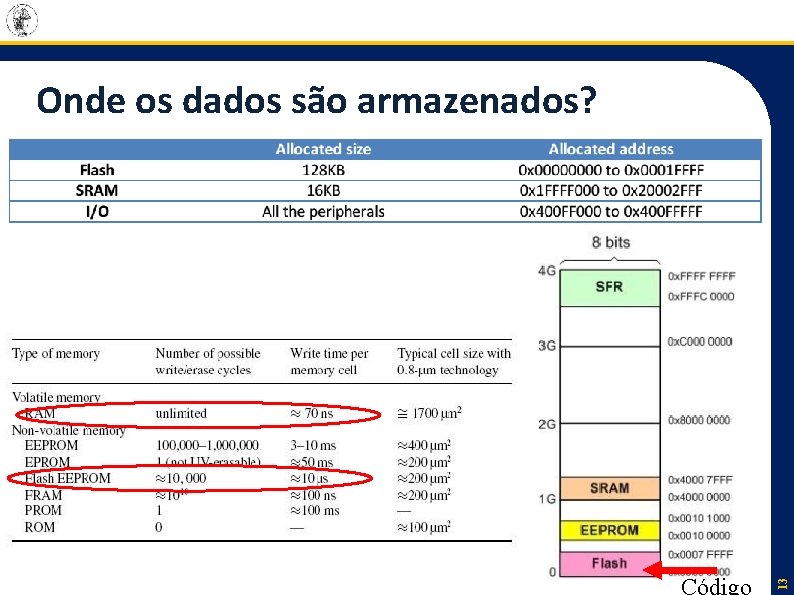

13 Onde os dados são armazenados?

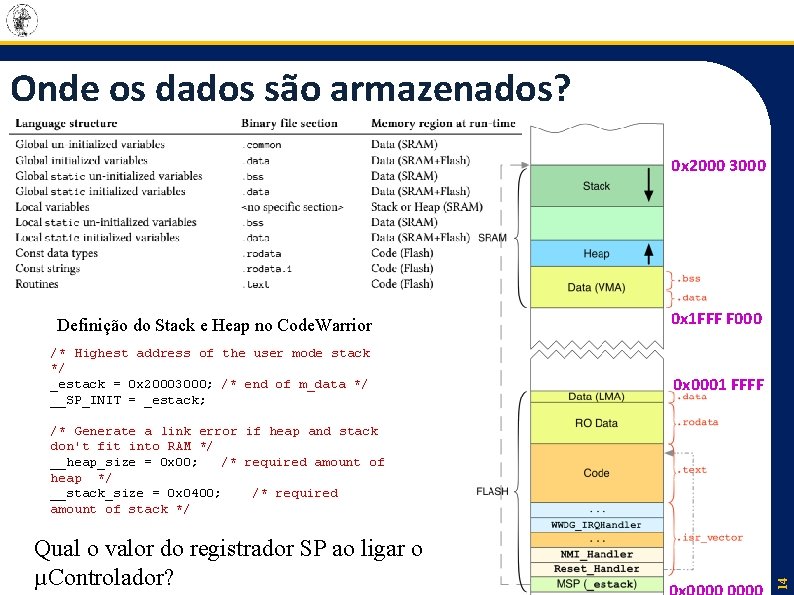

Onde os dados são armazenados? 0 x 2000 3000 Definição do Stack e Heap no Code. Warrior /* Highest address of the user mode stack */ _estack = 0 x 20003000; /* end of m_data */ __SP_INIT = _estack; 0 x 1 FFF F 000 0 x 0001 FFFF Qual o valor do registrador SP ao ligar o µControlador? 14 /* Generate a link error if heap and stack don't fit into RAM */ __heap_size = 0 x 00; /* required amount of heap */ __stack_size = 0 x 0400; /* required amount of stack */

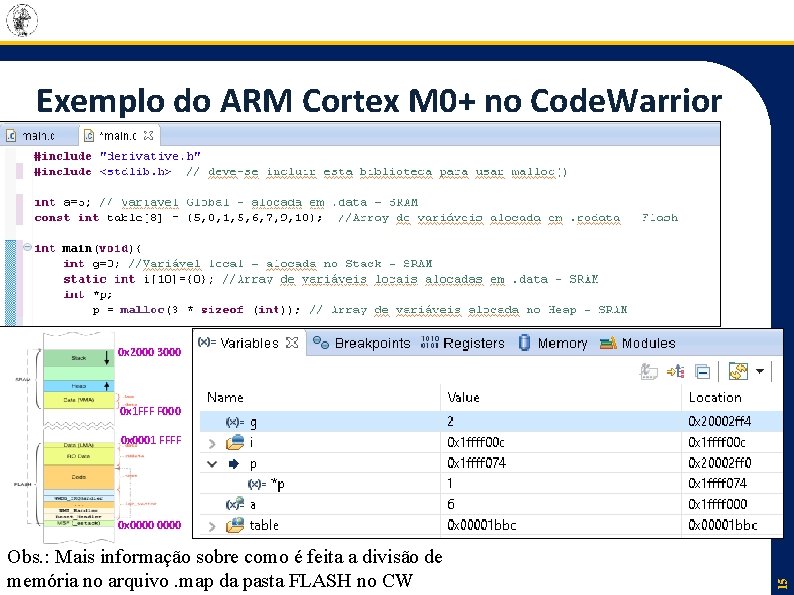

Exemplo do ARM Cortex M 0+ no Code. Warrior 0 x 2000 3000 0 x 1 FFF F 000 0 x 0001 FFFF Obs. : Mais informação sobre como é feita a divisão de memória no arquivo. map da pasta FLASH no CW 15 0 x 0000

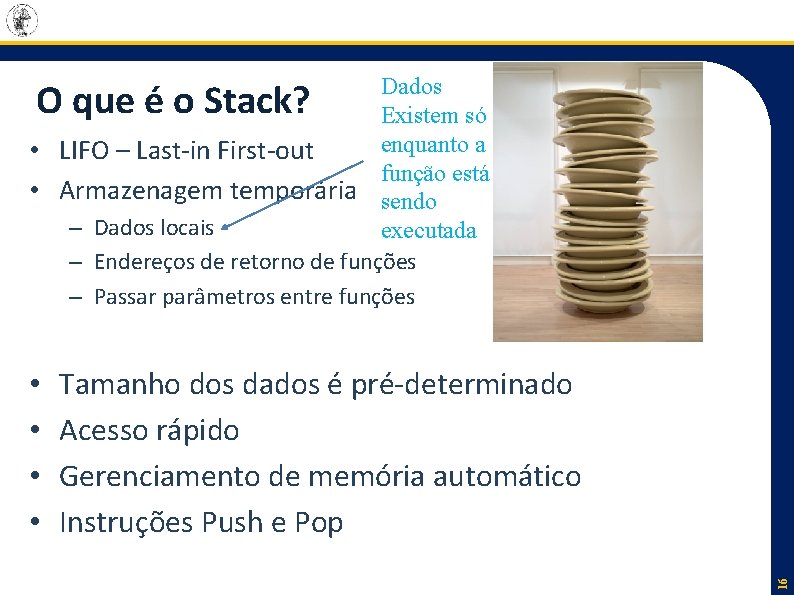

Dados Existem só enquanto a • LIFO – Last-in First-out função está • Armazenagem temporária sendo – Dados locais executada – Endereços de retorno de funções – Passar parâmetros entre funções O que é o Stack? Tamanho dos dados é pré-determinado Acesso rápido Gerenciamento de memória automático Instruções Push e Pop 16 • •

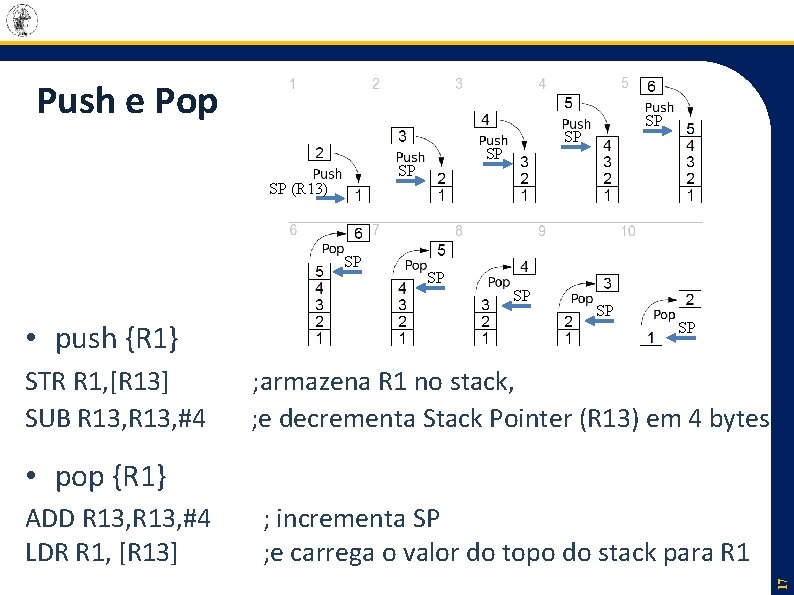

Push e Pop SP (R 13) SP SP SP • push {R 1} STR R 1, [R 13] SUB R 13, #4 SP SP SP ; armazena R 1 no stack, ; e decrementa Stack Pointer (R 13) em 4 bytes • pop {R 1} ; incrementa SP ; e carrega o valor do topo do stack para R 1 17 ADD R 13, #4 LDR R 1, [R 13]

![O que acontece? Declaração de vetores ou matrizes muito grandes char huge. Array[100000000]; Ou O que acontece? Declaração de vetores ou matrizes muito grandes char huge. Array[100000000]; Ou](http://slidetodoc.com/presentation_image_h2/6ad700ed1fe8da7cef1d63152564bedc/image-18.jpg)

O que acontece? Declaração de vetores ou matrizes muito grandes char huge. Array[100000000]; Ou 18 Operações Recursivas int foo(int x) { if (x <= 0) return x; return foo(x - 1); }

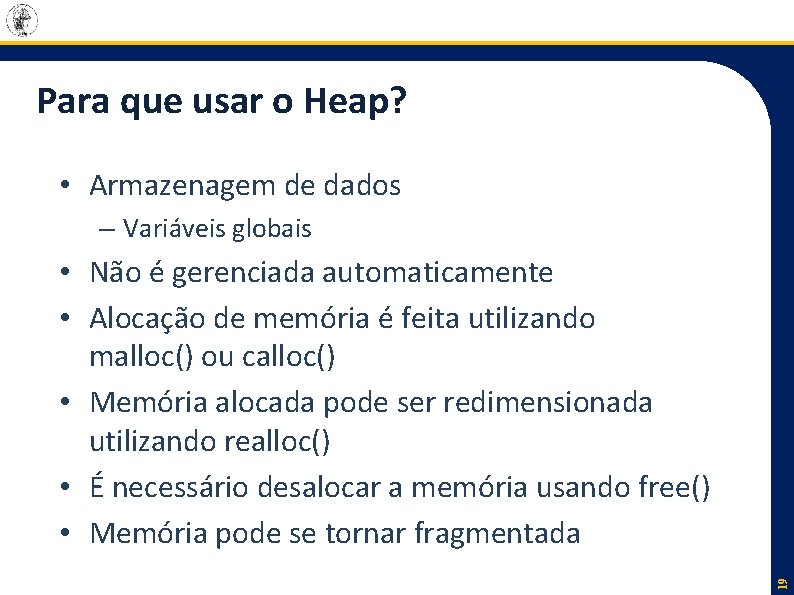

Para que usar o Heap? • Armazenagem de dados – Variáveis globais 19 • Não é gerenciada automaticamente • Alocação de memória é feita utilizando malloc() ou calloc() • Memória alocada pode ser redimensionada utilizando realloc() • É necessário desalocar a memória usando free() • Memória pode se tornar fragmentada

PSI 3441 – Arquitetura de Sistemas Embarcados - Instruções de Desvio 2017

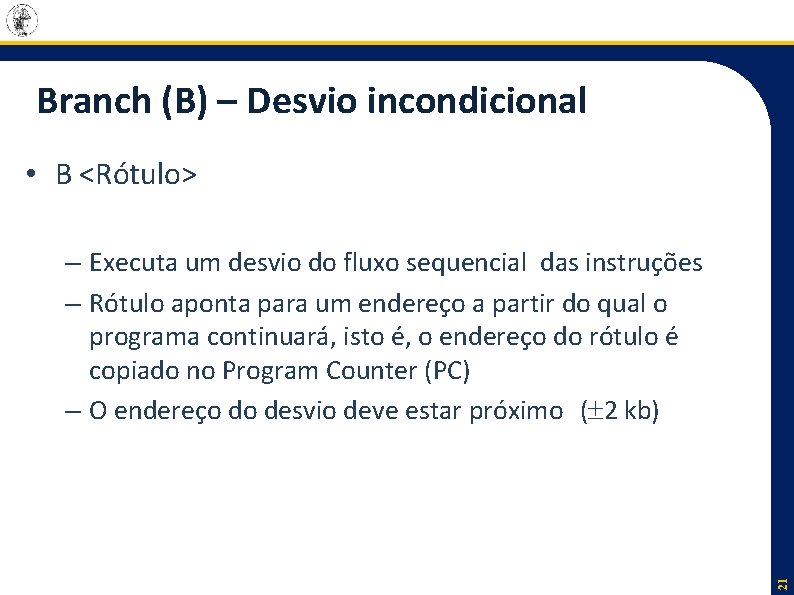

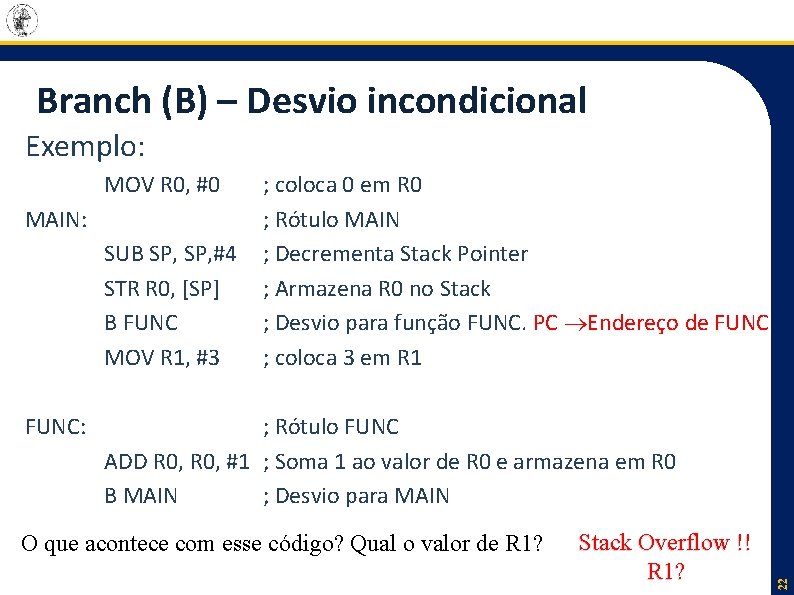

Branch (B) – Desvio incondicional • B <Rótulo> 21 – Executa um desvio do fluxo sequencial das instruções – Rótulo aponta para um endereço a partir do qual o programa continuará, isto é, o endereço do rótulo é copiado no Program Counter (PC) – O endereço do desvio deve estar próximo ( 2 kb)

Branch (B) – Desvio incondicional Exemplo: MOV R 0, #0 MAIN: SUB SP, #4 STR R 0, [SP] B FUNC MOV R 1, #3 ; Rótulo FUNC ADD R 0, #1 ; Soma 1 ao valor de R 0 e armazena em R 0 B MAIN ; Desvio para MAIN O que acontece com esse código? Qual o valor de R 1? Stack Overflow !! R 1? 22 FUNC: ; coloca 0 em R 0 ; Rótulo MAIN ; Decrementa Stack Pointer ; Armazena R 0 no Stack ; Desvio para função FUNC. PC Endereço de FUNC ; coloca 3 em R 1

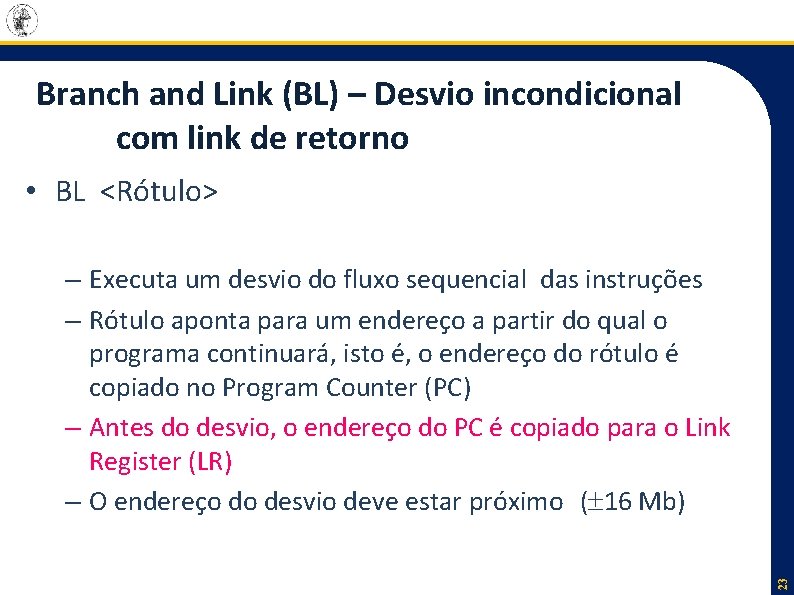

Branch and Link (BL) – Desvio incondicional com link de retorno • BL <Rótulo> 23 – Executa um desvio do fluxo sequencial das instruções – Rótulo aponta para um endereço a partir do qual o programa continuará, isto é, o endereço do rótulo é copiado no Program Counter (PC) – Antes do desvio, o endereço do PC é copiado para o Link Register (LR) – O endereço do desvio deve estar próximo ( 16 Mb)

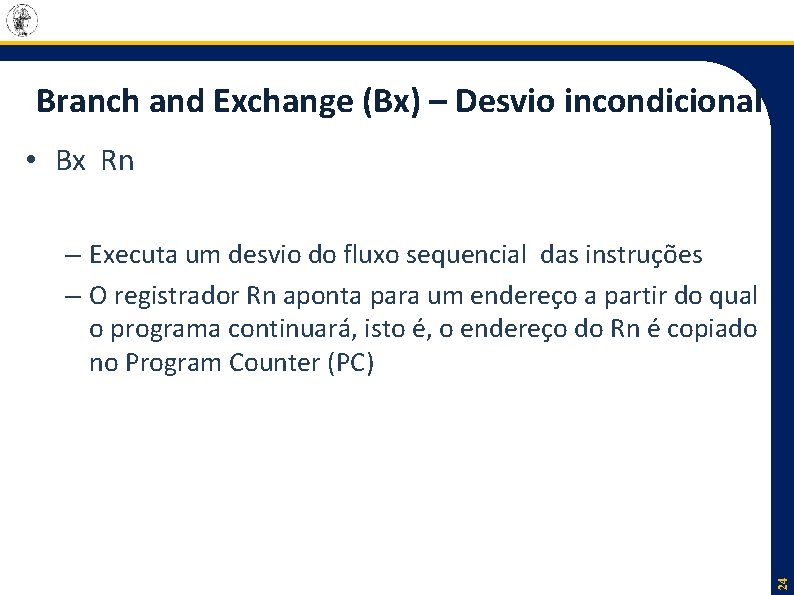

Branch and Exchange (Bx) – Desvio incondicional • Bx Rn 24 – Executa um desvio do fluxo sequencial das instruções – O registrador Rn aponta para um endereço a partir do qual o programa continuará, isto é, o endereço do Rn é copiado no Program Counter (PC)

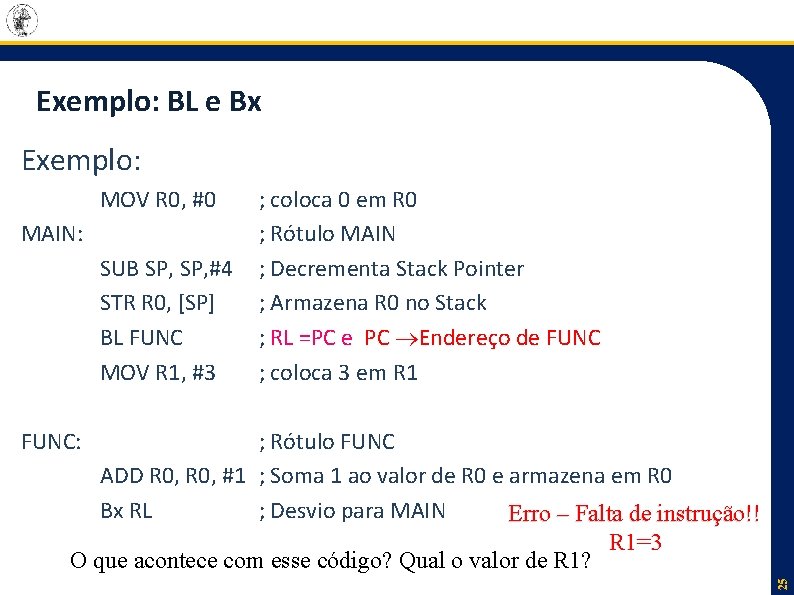

Exemplo: BL e Bx Exemplo: MOV R 0, #0 MAIN: SUB SP, #4 STR R 0, [SP] BL FUNC MOV R 1, #3 ; coloca 0 em R 0 ; Rótulo MAIN ; Decrementa Stack Pointer ; Armazena R 0 no Stack ; RL =PC e PC Endereço de FUNC ; coloca 3 em R 1 ; Rótulo FUNC ADD R 0, #1 ; Soma 1 ao valor de R 0 e armazena em R 0 Bx RL ; Desvio para MAIN Erro – Falta de instrução!! R 1=3 O que acontece com esse código? Qual o valor de R 1? 25 FUNC:

Exemplo: BL e Bx Exemplo: ; coloca 0 em R 0 MAIN: ; Rótulo MAIN SUB SP, #4 ; Decrementa Stack Pointer STR R 0, [SP] ; Armazena R 0 no Stack BL FUNC ; RL =PC e PC Endereço de FUNC MOV R 1, #3 ; coloca 3 em R 1 LOOP: ; Rótulo LOOP B LOOP ; Loop infinito FUNC: ; Rótulo FUNC ADD R 0, #1 ; Soma 1 ao valor de R 0 e armazena em R 0 Bx RL ; Desvio para MAIN 26 MOV R 0, #0

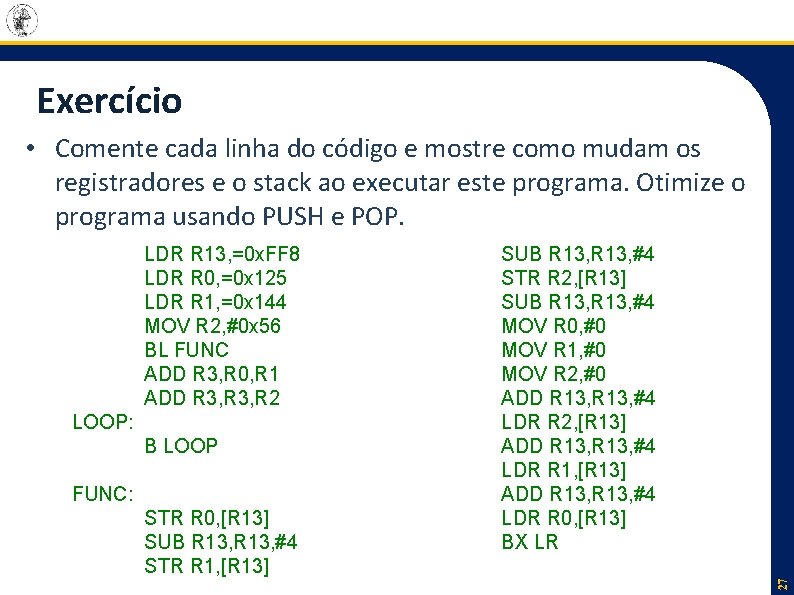

Exercício • Comente cada linha do código e mostre como mudam os registradores e o stack ao executar este programa. Otimize o programa usando PUSH e POP. LOOP: B LOOP FUNC: STR R 0, [R 13] SUB R 13, #4 STR R 1, [R 13] SUB R 13, #4 STR R 2, [R 13] SUB R 13, #4 MOV R 0, #0 MOV R 1, #0 MOV R 2, #0 ADD R 13, #4 LDR R 2, [R 13] ADD R 13, #4 LDR R 1, [R 13] ADD R 13, #4 LDR R 0, [R 13] BX LR 27 LDR R 13, =0 x. FF 8 LDR R 0, =0 x 125 LDR R 1, =0 x 144 MOV R 2, #0 x 56 BL FUNC ADD R 3, R 0, R 1 ADD R 3, R 2

Auxílio R 13 Stack Pointer (SP) R 14 Link Register (LR) BL Program Counter (PC) = LR antes do desvio Bx Rn Copia o valor de Rn para PC push {R 1} equivalente a: STR R 1, [R 13] SUB R 13, #4 • pop {R 1} equivalente a: ADD R 13, #4 LDR R 1, [R 13] 28 • • •

Push e Pop realmente otimizam o código? 29 • Quando ciclo de máquina cada instrução usa? • http: //infocenter. arm. com/help/index. jsp? topic=/c om. arm. doc. set. cortexm/index. html

- Slides: 29