PSI 3441 Arquitetura de Sistemas Embarcados Instrues de

PSI 3441 – Arquitetura de Sistemas Embarcados - Instruções de Desvio – Loop Ponto Flutuante Multiplicação e Divisão Pseudo-Instruções Processadores ARM Escola Politécnica da Universidade de São Paulo Prof. Gustavo Rehder – grehder@lme. usp. br Prof. Sergio Takeo – kofuji@usp. br Prof. Antonio Seabra – acseabra@lsi. usp. br 2017

Socrative 2 Sala: PSI 3441

PSI 3441 – Arquitetura de Sistemas Embarcados - Instruções de Desvio – Loop Escola Politécnica da Universidade de São Paulo 2017

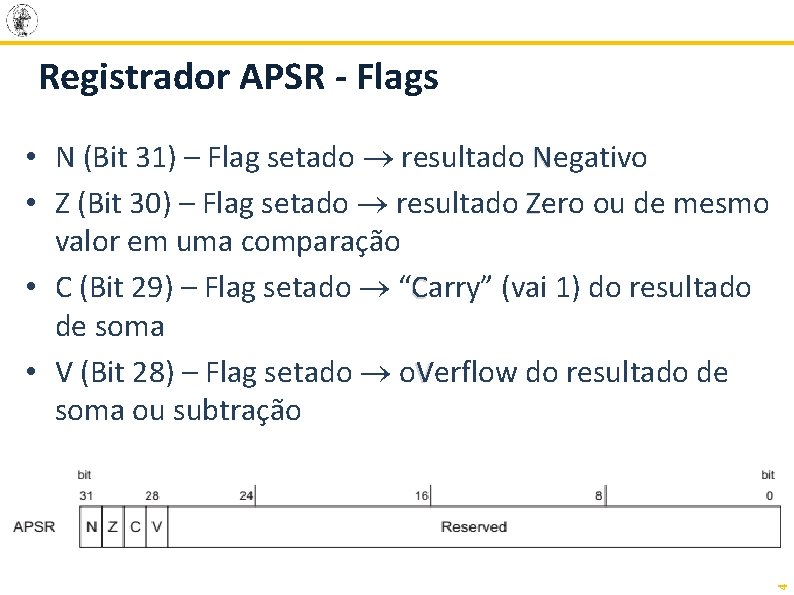

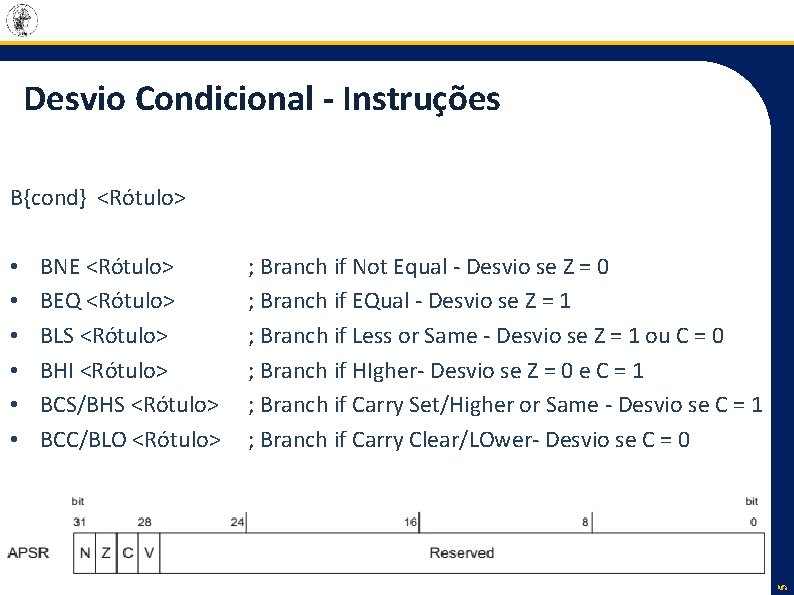

Registrador APSR - Flags 4 • N (Bit 31) – Flag setado resultado Negativo • Z (Bit 30) – Flag setado resultado Z ero ou de mesmo valor em uma comparação • C (Bit 29) – Flag setado “C arry” (vai 1) do resultado de soma • V (Bit 28) – Flag setado o. V erflow do resultado de soma ou subtração

Desvio Condicional - Instruções B{cond} <Rótulo> BNE <Rótulo> BEQ <Rótulo> BLS <Rótulo> BHI <Rótulo> BCS/BHS <Rótulo> BCC/BLO <Rótulo> ; Branch if Not Equal - Desvio se Z = 0 ; Branch if EQual - Desvio se Z = 1 ; Branch if Less or Same - Desvio se Z = 1 ou C = 0 ; Branch if HIgher- Desvio se Z = 0 e C = 1 ; Branch if Carry Set/Higher or Same - Desvio se C = 1 ; Branch if Carry Clear/LOwer- Desvio se C = 0 5 • • •

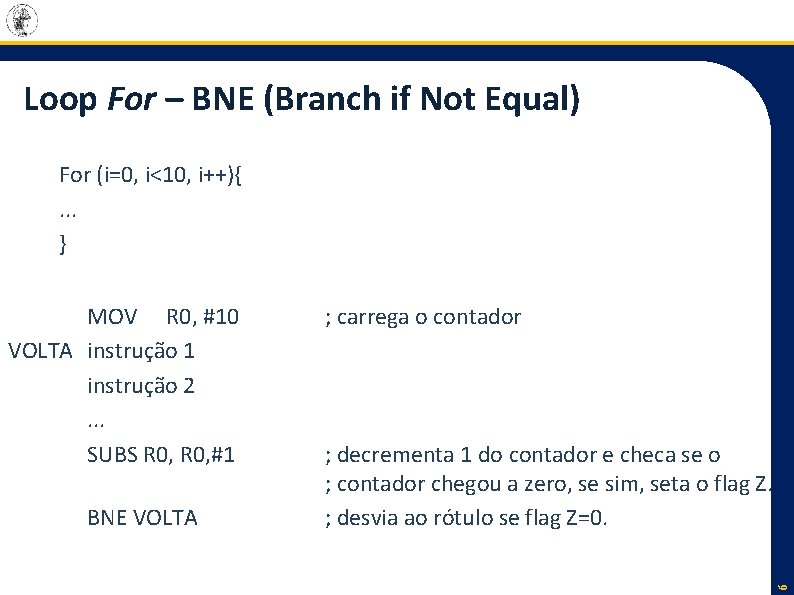

Loop For – BNE (Branch if Not Equal) For (i=0, i<10, i++){. . . } BNE VOLTA ; carrega o contador ; decrementa 1 do contador e checa se o ; contador chegou a zero, se sim, seta o flag Z. ; desvia ao rótulo se flag Z=0. 6 MOV R 0, #10 VOLTA instrução 1 instrução 2. . . SUBS R 0, #1

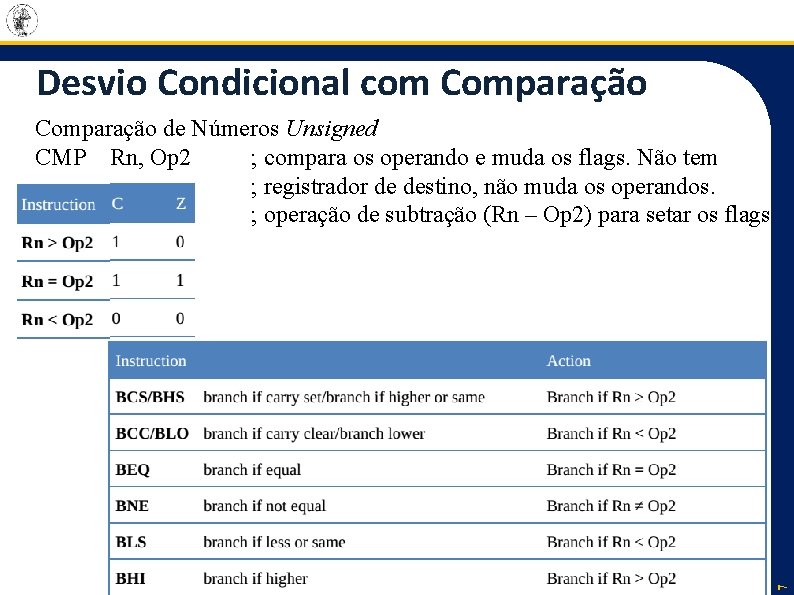

Desvio Condicional com Comparação 7 Comparação de Números Unsigned CMP Rn, Op 2 ; compara os operando e muda os flags. Não tem ; registrador de destino, não muda os operandos. ; operação de subtração (Rn – Op 2) para setar os flags

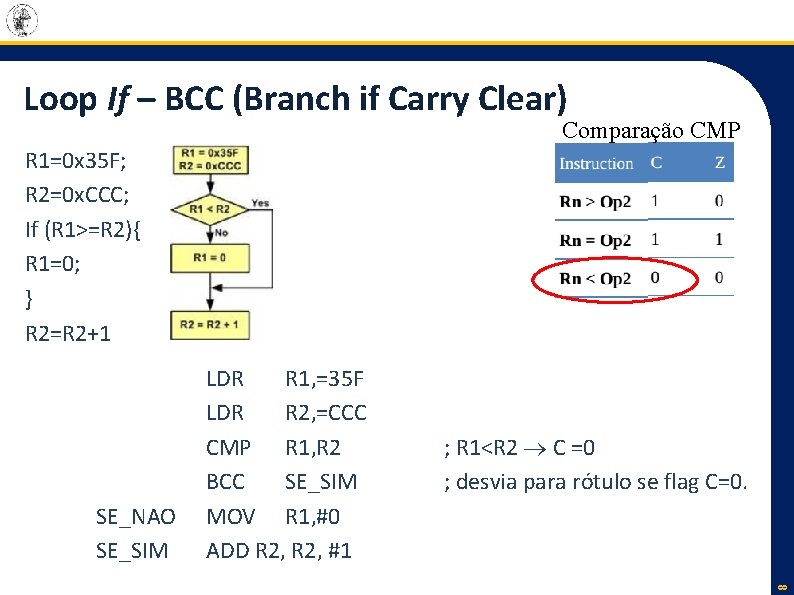

Loop If – BCC (Branch if Carry Clear) Comparação CMP R 1=0 x 35 F; R 2=0 x. CCC; If (R 1>=R 2){ R 1=0; } R 2=R 2+1 ; R 1<R 2 C =0 ; desvia para rótulo se flag C=0. 8 SE_NAO SE_SIM LDR R 1, =35 F LDR R 2, =CCC CMP R 1, R 2 BCC SE_SIM MOV R 1, #0 ADD R 2, #1

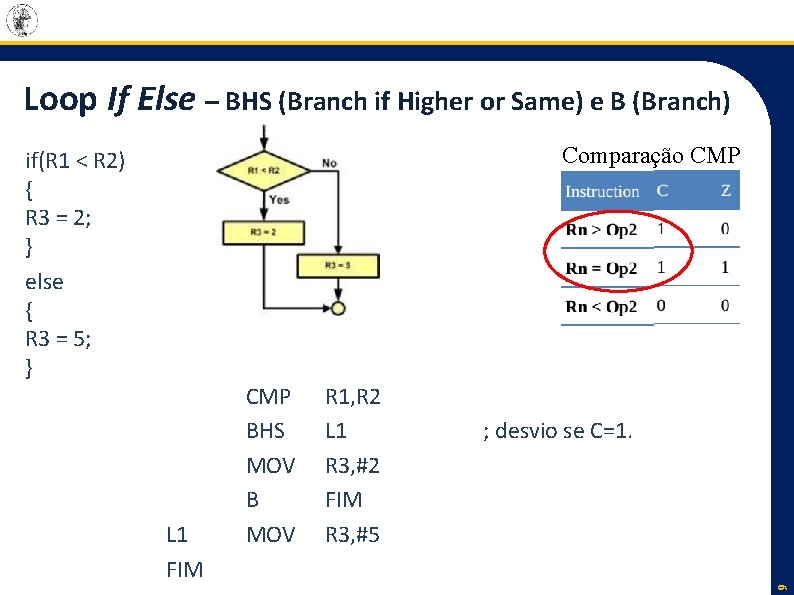

Loop If Else – BHS (Branch if Higher or Same) e B (Branch) Comparação CMP L 1 FIM CMP BHS MOV B MOV R 1, R 2 L 1 R 3, #2 FIM R 3, #5 ; desvio se C=1. 9 if(R 1 < R 2) { R 3 = 2; } else { R 3 = 5; }

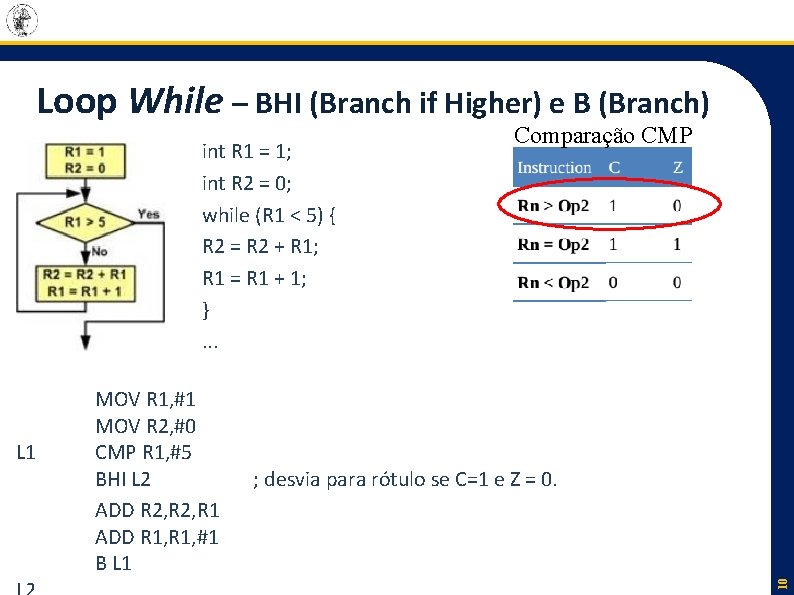

Loop While – BHI (Branch if Higher) e B (Branch) int R 1 = 1; int R 2 = 0; while (R 1 < 5) { R 2 = R 2 + R 1; R 1 = R 1 + 1; }. . . ; desvia para rótulo se C=1 e Z = 0. 10 L 1 MOV R 1, #1 MOV R 2, #0 CMP R 1, #5 BHI L 2 ADD R 2, R 1 ADD R 1, #1 B L 1 Comparação CMP

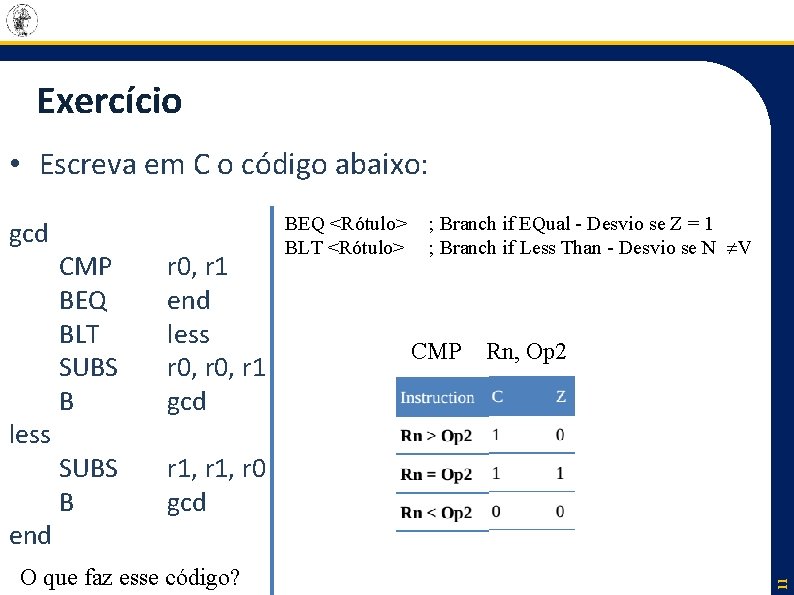

Exercício • Escreva em C o código abaixo: less end CMP BEQ BLT SUBS B r 0, r 1 end less r 0, r 1 gcd SUBS B r 1, r 0 gcd O que faz esse código? BEQ <Rótulo> BLT <Rótulo> ; Branch if EQual - Desvio se Z = 1 ; Branch if Less Than - Desvio se N V CMP Rn, Op 2 11 gcd

Socrative 13 Sala: PSI 3441

PSI 3441 – Arquitetura de Sistemas Embarcados - Ponto Flutuante Escola Politécnica da Universidade de São Paulo 2017

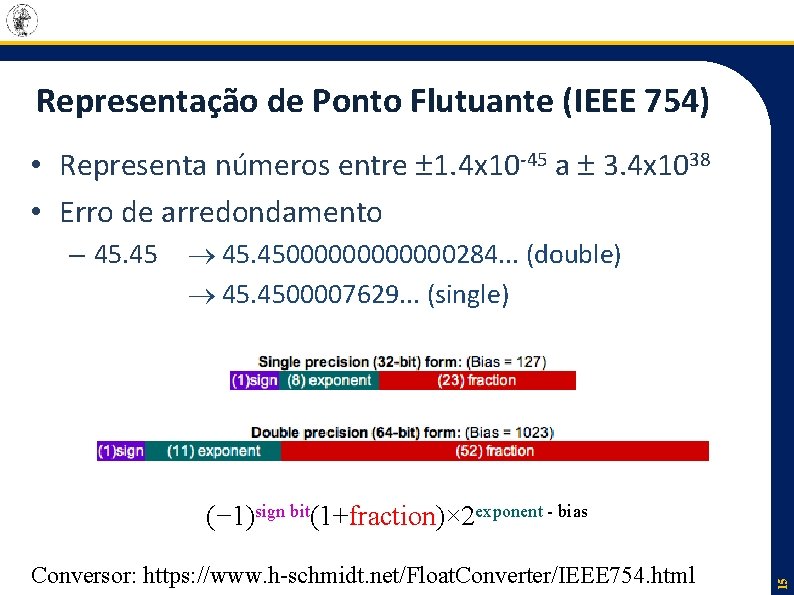

Representação de Ponto Flutuante (IEEE 754) • Representa números entre 1. 4 x 10 -45 a 3. 4 x 1038 • Erro de arredondamento – 45. 45000000284. . . (double) 45. 4500007629. . . (single) Conversor: https: //www. h-schmidt. net/Float. Converter/IEEE 754. html 15 (− 1)sign bit(1+fraction)× 2 exponent - bias

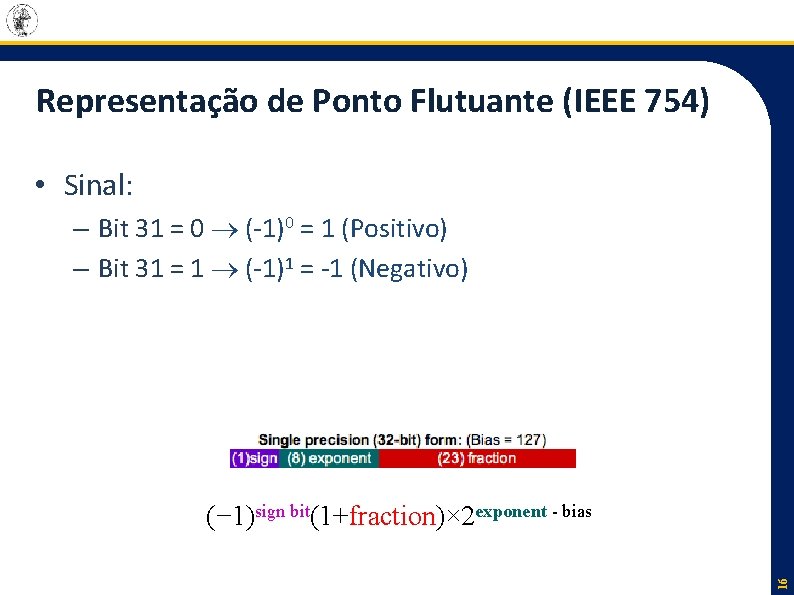

Representação de Ponto Flutuante (IEEE 754) • Sinal: – Bit 31 = 0 (-1)0 = 1 (Positivo) – Bit 31 = 1 (-1)1 = -1 (Negativo) 16 (− 1)sign bit(1+fraction)× 2 exponent - bias

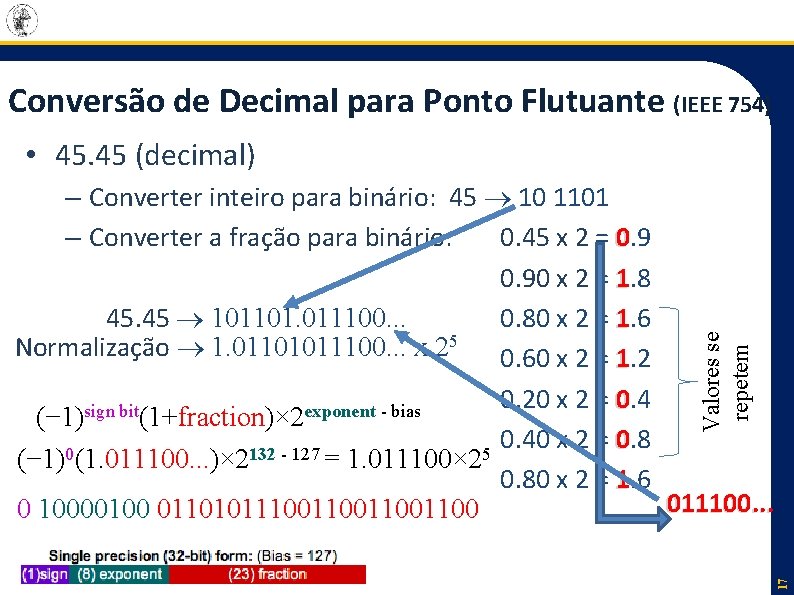

Conversão de Decimal para Ponto Flutuante (IEEE 754) • 45. 45 (decimal) 17 Valores se repetem – Converter inteiro para binário: 45 10 1101 – Converter a fração para binário: 0. 45 x 2 = 0. 90 x 2 = 1. 8 0. 80 x 2 = 1. 6 45. 45 101101. 011100. . . Normalização 1. 01101011100. . . x 25 0. 60 x 2 = 1. 2 0. 20 x 2 = 0. 4 sign bit exponent bias (− 1) (1+fraction)× 2 0. 40 x 2 = 0. 8 0 132 127 5 (− 1) (1. 011100. . . )× 2 = 1. 011100× 2 0. 80 x 2 = 1. 6 011100. . . 0 10000100 011010111001100

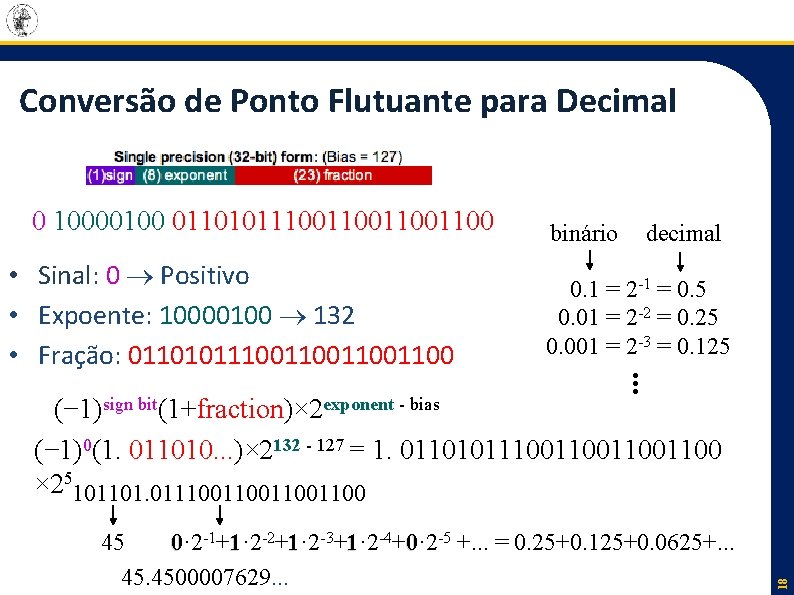

Conversão de Ponto Flutuante para Decimal 0 10000100 011010111001100 decimal 0. 1 = 2 -1 = 0. 5 0. 01 = 2 -2 = 0. 25 0. 001 = 2 -3 = 0. 125 . . . • Sinal: 0 Positivo • Expoente: 10000100 132 • Fração: 011010111001100 binário 45 0 · 2 -1+1 · 2 -2+1 · 2 -3+1 · 2 -4+0 · 2 -5 +. . . = 0. 25+0. 125+0. 0625+. . . 4500007629. . . 18 (− 1)sign bit(1+fraction)× 2 exponent - bias (− 1)0(1. 011010. . . )× 2132 - 127 = 1. 011010111001100 × 25101101. 0111001100

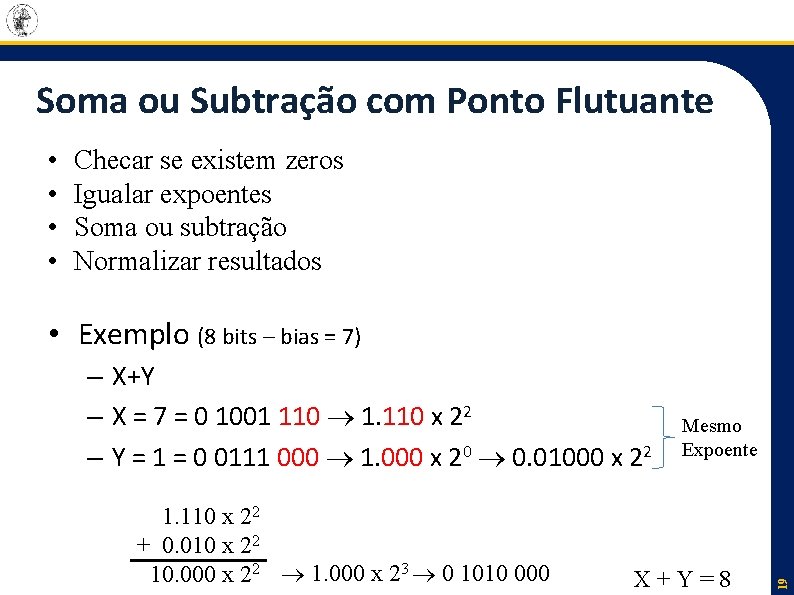

Soma ou Subtração com Ponto Flutuante • • Checar se existem zeros Igualar expoentes Soma ou subtração Normalizar resultados • Exemplo (8 bits – bias = 7) 1. 110 x 22 + 0. 010 x 22 10. 000 x 22 1. 000 x 23 0 1010 000 Mesmo Expoente X+Y=8 19 – X+Y – X = 7 = 0 1001 110 1. 110 x 22 – Y = 1 = 0 0111 000 1. 000 x 20 0. 01000 x 22

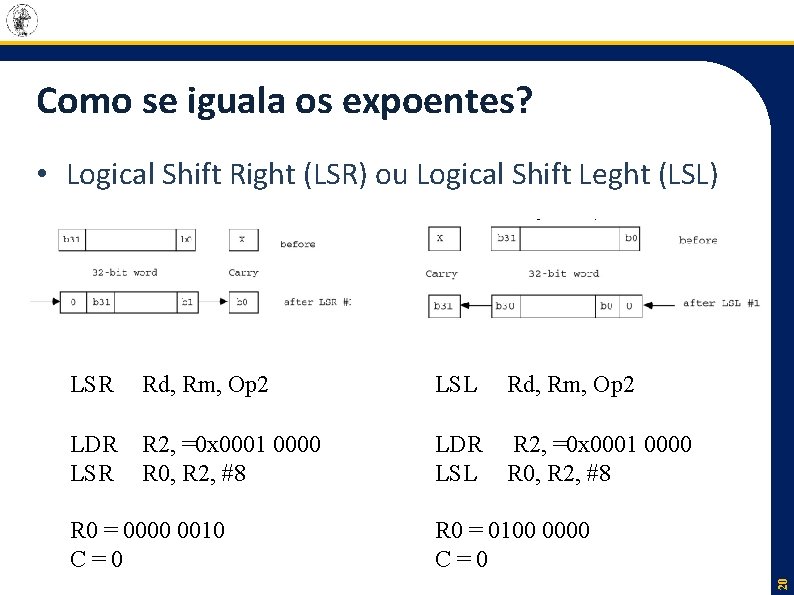

Como se iguala os expoentes? • Logical Shift Right (LSR) ou Logical Shift Leght (LSL) LSR Rd, Rm, Op 2 LSL Rd, Rm, Op 2 LDR LSR R 2, =0 x 0001 0000 R 0, R 2, #8 LDR LSL R 2, =0 x 0001 0000 R 0, R 2, #8 R 0 = 0100 0000 C=0 20 R 0 = 0000 0010 C=0

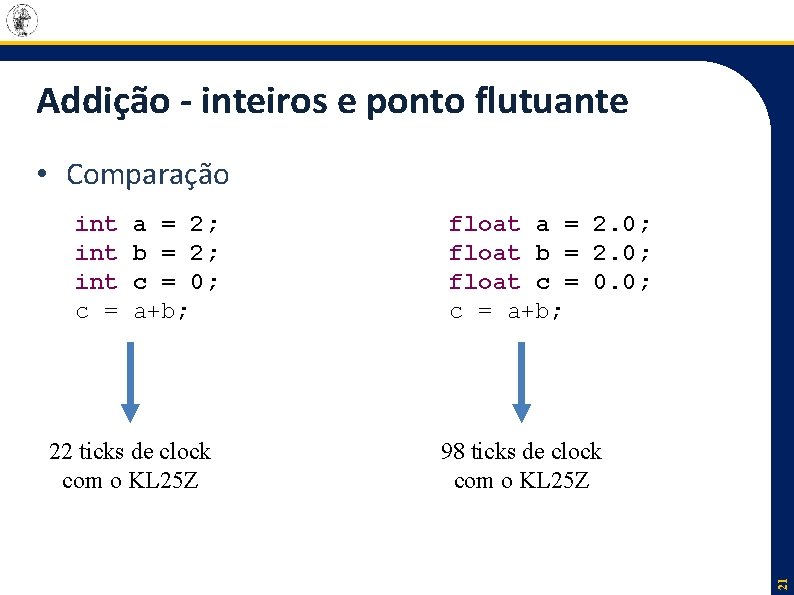

Addição - inteiros e ponto flutuante • Comparação a = 2; b = 2; c = 0; a+b; 22 ticks de clock com o KL 25 Z float a = 2. 0; float b = 2. 0; float c = 0. 0; c = a+b; 98 ticks de clock com o KL 25 Z 21 int int c =

PSI 3441 – Arquitetura de Sistemas Embarcados - Multiplicação e Divisão Escola Politécnica da Universidade de São Paulo 2017

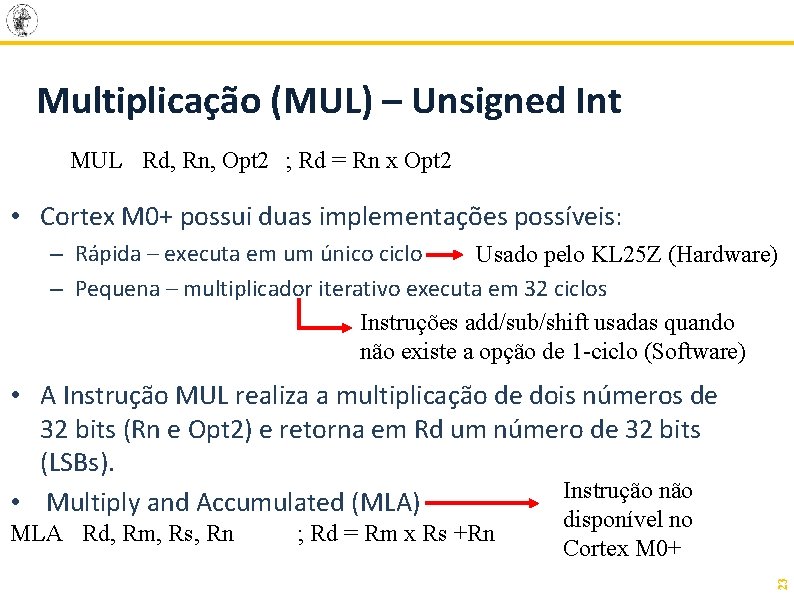

Multiplicação (MUL) – Unsigned Int MUL Rd, Rn, Opt 2 ; Rd = Rn x Opt 2 • Cortex M 0+ possui duas implementações possíveis: – Rápida – executa em um único ciclo Usado pelo KL 25 Z (Hardware) – Pequena – multiplicador iterativo executa em 32 ciclos Instruções add/sub/shift usadas quando não existe a opção de 1 -ciclo (Software) • A Instrução MUL realiza a multiplicação de dois números de 32 bits (Rn e Opt 2) e retorna em Rd um número de 32 bits (LSBs). Instrução não • Multiply and Accumulated (MLA) ; Rd = Rm x Rs +Rn 23 MLA Rd, Rm, Rs, Rn disponível no Cortex M 0+

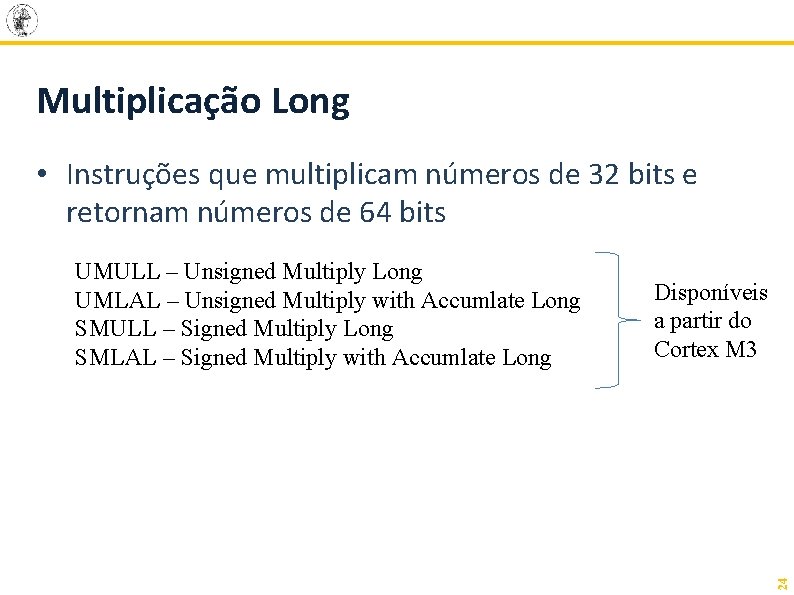

Multiplicação Long • Instruções que multiplicam números de 32 bits e retornam números de 64 bits Disponíveis a partir do Cortex M 3 24 UMULL – Unsigned Multiply Long UMLAL – Unsigned Multiply with Accumlate Long SMULL – Signed Multiply Long SMLAL – Signed Multiply with Accumlate Long

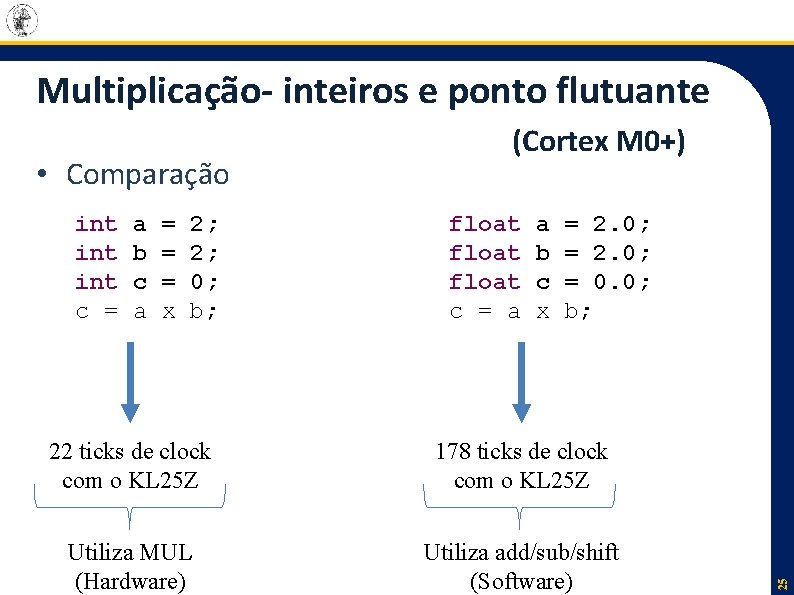

Multiplicação- inteiros e ponto flutuante int int c = a b c a = = = x 2; 2; 0; b; float c = a a b c x = 2. 0; = 0. 0; b; 22 ticks de clock com o KL 25 Z 178 ticks de clock com o KL 25 Z Utiliza MUL (Hardware) Utiliza add/sub/shift (Software) 25 • Comparação (Cortex M 0+)

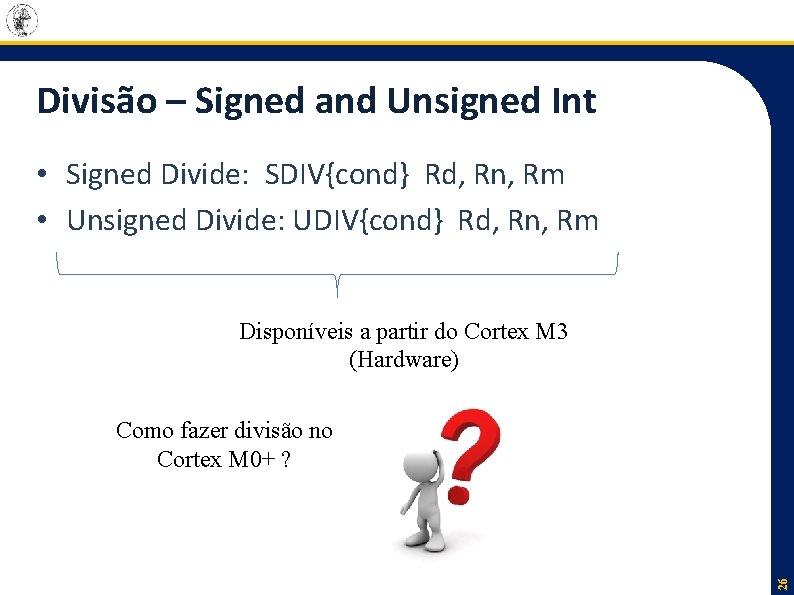

Divisão – Signed and Unsigned Int • Signed Divide: SDIV{cond} Rd, Rn, Rm • Unsigned Divide: UDIV{cond} Rd, Rn, Rm Disponíveis a partir do Cortex M 3 (Hardware) 26 Como fazer divisão no Cortex M 0+ ?

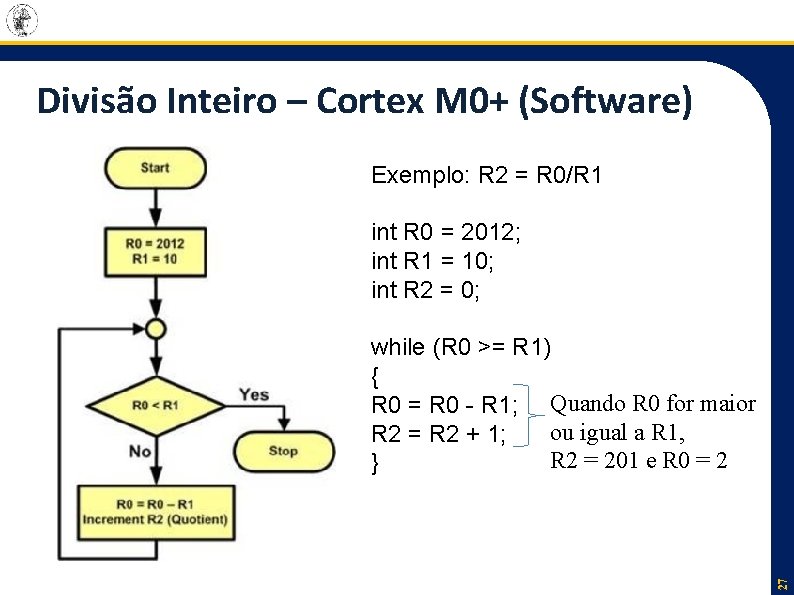

Divisão Inteiro – Cortex M 0+ (Software) Exemplo: R 2 = R 0/R 1 int R 0 = 2012; int R 1 = 10; int R 2 = 0; 27 while (R 0 >= R 1) { R 0 = R 0 - R 1; Quando R 0 for maior ou igual a R 1, R 2 = R 2 + 1; R 2 = 201 e R 0 = 2 }

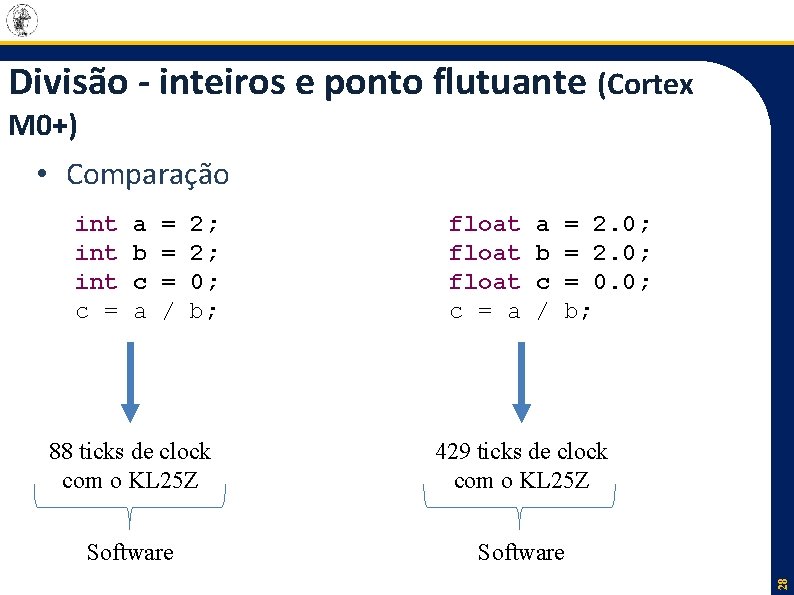

Divisão - inteiros e ponto flutuante (Cortex M 0+) • Comparação a b c a = = = / 2; 2; 0; b; float c = a a b c / = 2. 0; = 0. 0; b; 88 ticks de clock com o KL 25 Z 429 ticks de clock com o KL 25 Z Software 28 int int c =

PSI 3441 – Arquitetura de Sistemas Embarcados - Pseudo-Instruções Escola Politécnica da Universidade de São Paulo 2017

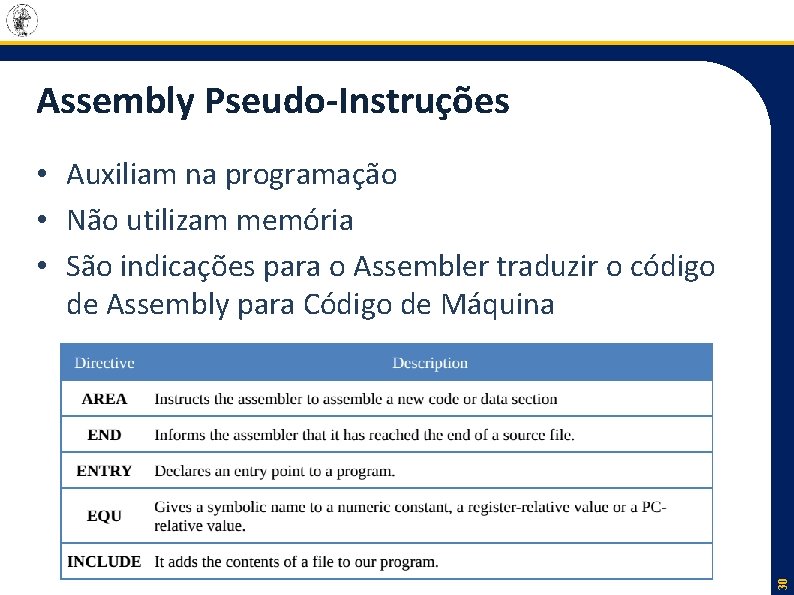

Assembly Pseudo-Instruções 30 • Auxiliam na programação • Não utilizam memória • São indicações para o Assembler traduzir o código de Assembly para Código de Máquina

PSI 3441 – Arquitetura de Sistemas Embarcados - Processadores ARM Escola Politécnica da Universidade de São Paulo 2017

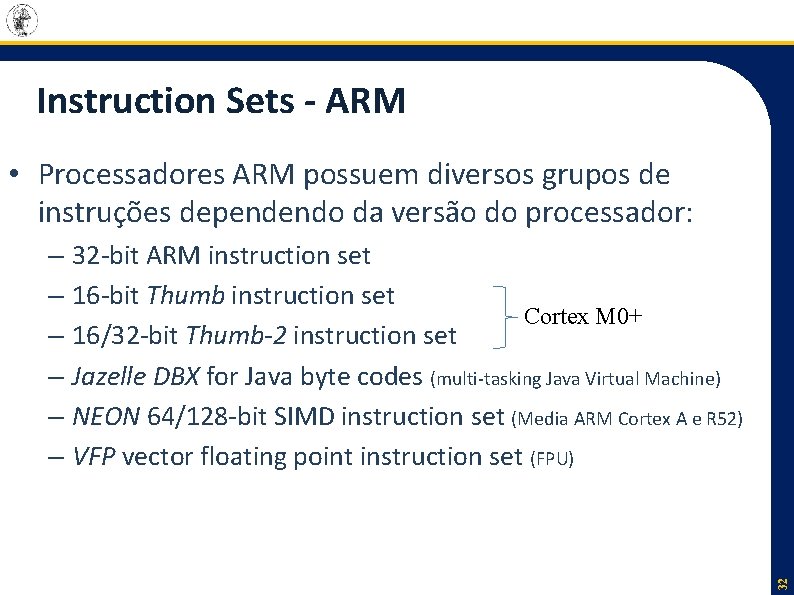

Instruction Sets - ARM • Processadores ARM possuem diversos grupos de instruções dependendo da versão do processador: 32 -bit ARM instruction set 16 -bit Thumb instruction set Cortex M 0+ 16/32 -bit Thumb-2 instruction set Jazelle DBX for Java byte codes (multi-tasking Java Virtual Machine) NEON 64/128 -bit SIMD instruction set (Media ARM Cortex A e R 52) VFP vector floating point instruction set (FPU) 32 – – –

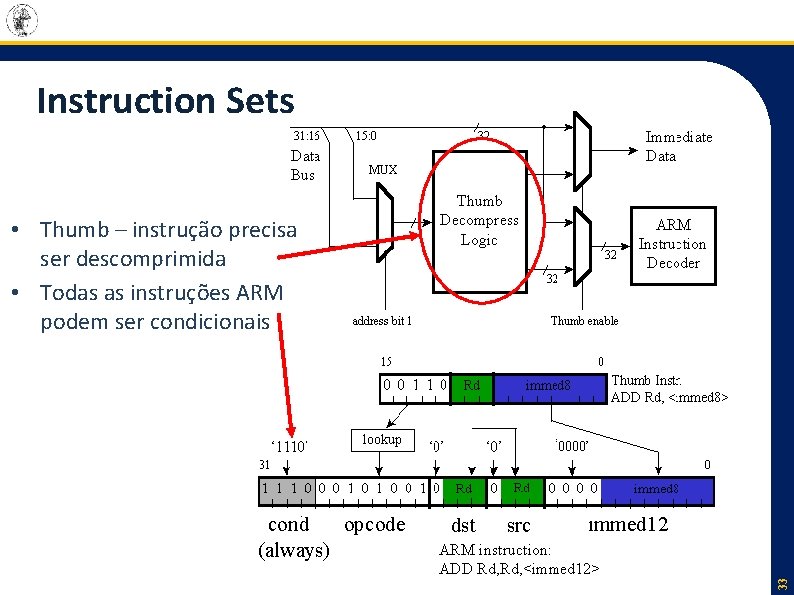

Instruction Sets 33 • Thumb – instrução precisa ser descomprimida • Todas as instruções ARM podem ser condicionais

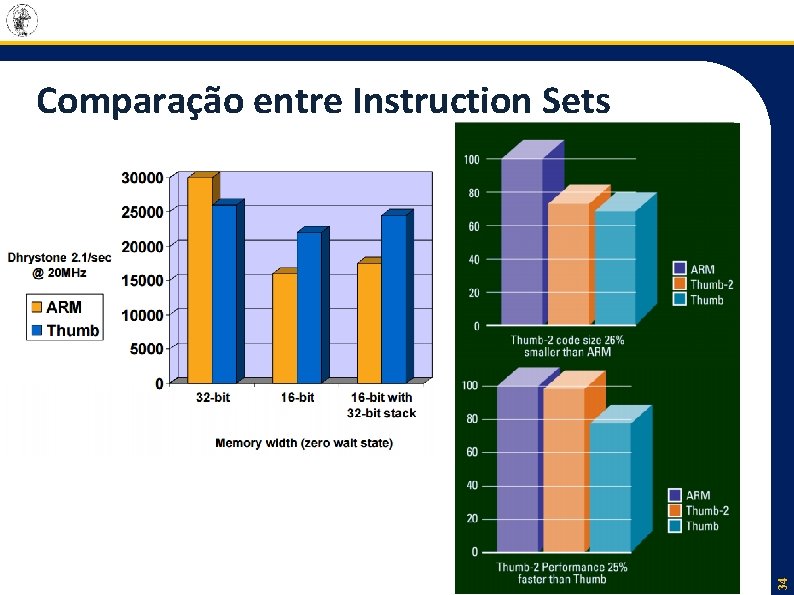

34 Comparação entre Instruction Sets

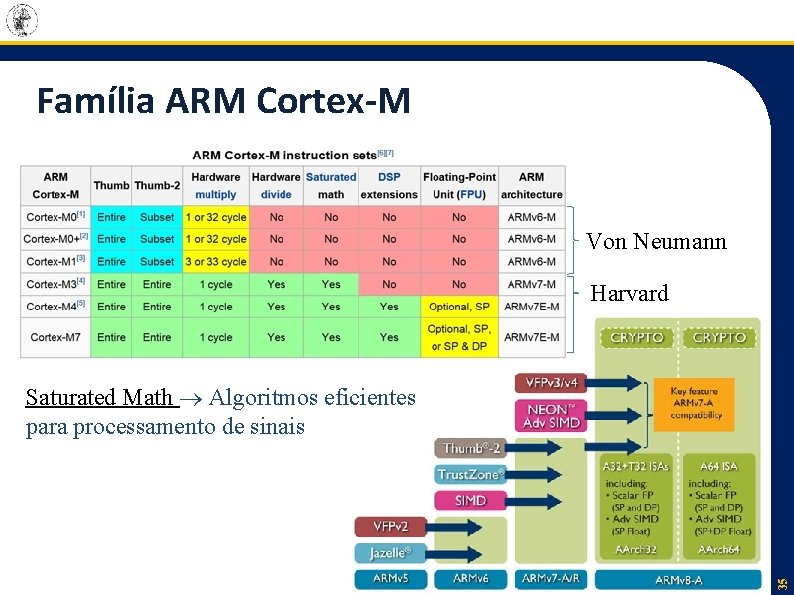

Família ARM Cortex-M Von Neumann Harvard 35 Saturated Math Algoritmos eficientes para processamento de sinais

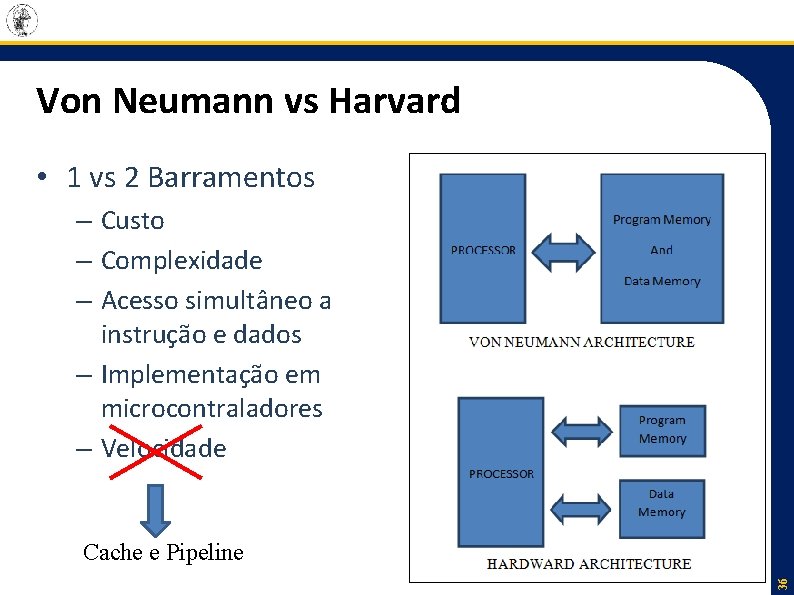

Von Neumann vs Harvard • 1 vs 2 Barramentos – Custo – Complexidade – Acesso simultâneo a instrução e dados – Implementação em microcontraladores – Velocidade 36 Cache e Pipeline

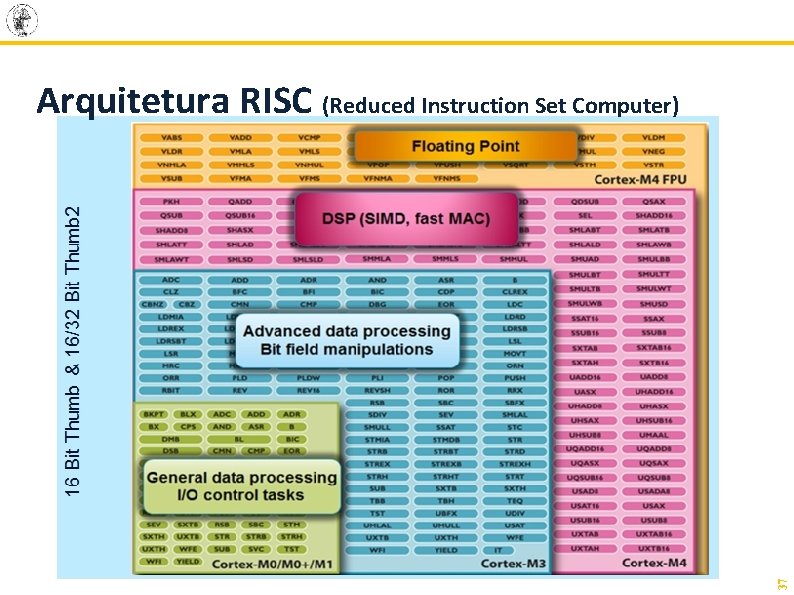

37 Arquitetura RISC (Reduced Instruction Set Computer)

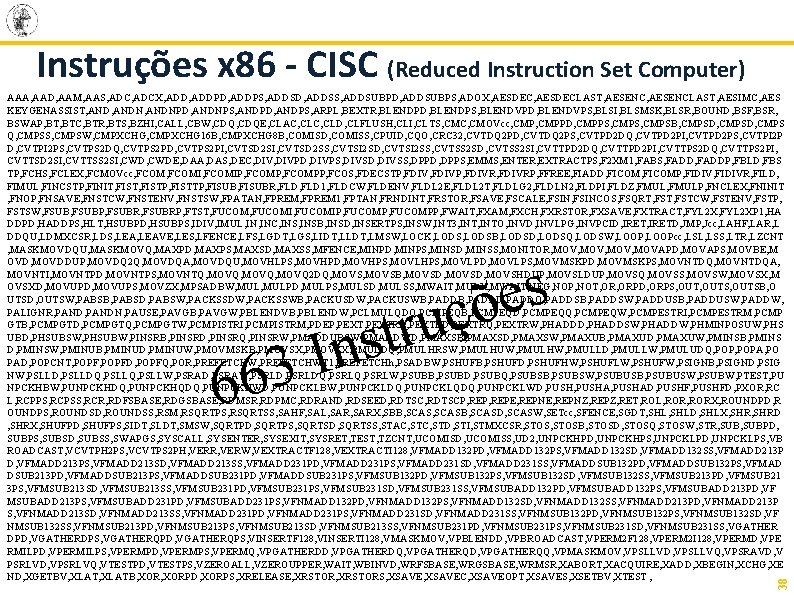

Instruções x 86 - CISC (Reduced Instruction Set Computer) AAA, AAD, AAM, AAS, ADCX, ADDPD, ADDPS, ADDSD, ADDSS, ADDSUBPD, ADDSUBPS, ADOX, AESDECLAST, AESENCLAST, AESIMC, AES KEYGENASSIST, ANDN, ANDNPD, ANDNPS, ANDPD, ANDPS, ARPL, BEXTR, BLENDPD, BLENDPS, BLENDVPD, BLENDVPS, BLSI, BLSMSK, BLSR, BOUND, BSF, BSR, BSWAP, BTC, BTR, BTS, BZHI, CALL, CBW, CDQE, CLAC, CLD, CLFLUSH, CLI, CLTS, CMC, CMOVcc, CMPPD, CMPPS, CMPSB, CMPSD, CMPS Q, CMPSS, CMPSW, CMPXCHG 16 B, CMPXCHG 8 B, COMISD, COMISS, CPUID, CQO, CRC 32, CVTDQ 2 PD, CVTDQ 2 PS, CVTPD 2 DQ, CVTPD 2 PI, CVTPD 2 PS, CVTPI 2 P D, CVTPI 2 PS, CVTPS 2 DQ, CVTPS 2 PD, CVTPS 2 PI, CVTSD 2 SS, CVTSI 2 SD, CVTSI 2 SS, CVTSS 2 SD, CVTSS 2 SI, CVTTPD 2 DQ, CVTTPD 2 PI, CVTTPS 2 DQ, CVTTPS 2 PI, CVTTSD 2 SI, CVTTSS 2 SI, CWDE, DAA, DAS, DEC, DIVPD, DIVPS, DIVSD, DIVSS, DPPD, DPPS, EMMS, ENTER, EXTRACTPS, F 2 XM 1, FABS, FADDP, FBLD, FBS TP, FCHS, FCLEX, FCMOVcc, FCOMI, FCOMIP, FCOMPP, FCOS, FDECSTP, FDIVP, FDIVRP, FFREE, FIADD, FICOMP, FIDIVR, FILD, FIMUL, FINCSTP, FINIT, FISTP, FISTTP, FISUBR, FLD 1, FLDCW, FLDENV, FLDL 2 E, FLDL 2 T, FLDLG 2, FLDLN 2, FLDPI, FLDZ, FMULP, FNCLEX, FNINIT , FNOP, FNSAVE, FNSTCW, FNSTENV, FNSTSW, FPATAN, FPREM 1, FPTAN, FRNDINT, FRSTOR, FSAVE, FSCALE, FSINCOS, FSQRT, FSTCW, FSTENV, FSTP, FSTSW, FSUBP, FSUBRP, FTST, FUCOMI, FUCOMIP, FUCOMPP, FWAIT, FXAM, FXCH, FXRSTOR, FXSAVE, FXTRACT, FYL 2 XP 1, HA DDPD, HADDPS, HLT, HSUBPD, HSUBPS, IDIV, IMUL, INC, INSB, INSD, INSERTPS, INSW, INT 3, INTO, INVD, INVLPG, INVPCID, IRETD, JMP, Jcc, LAHF, LAR, L DDQU, LDMXCSR, LDS, LEAVE, LES, LFENCE, LFS, LGDT, LGS, LIDT, LLDT, LMSW, LOCK, LODSB, LODSD, LODSQ, LODSW, LOOPcc, LSL, LSS, LTR, LZCNT , MASKMOVDQU, MASKMOVQ, MAXPD, MAXPS, MAXSD, MAXSS, MFENCE, MINPD, MINPS, MINSD, MINSS, MONITOR, MOV, MOVAPD, MOVAPS, MOVBE, M OVD, MOVDDUP, MOVDQ 2 Q, MOVDQA, MOVDQU, MOVHLPS, MOVHPD, MOVHPS, MOVLPD, MOVLPS, MOVMSKPD, MOVMSKPS, MOVNTDQA, MOVNTI, MOVNTPD, MOVNTPS, MOVNTQ, MOVQ, MOVQ 2 DQ, MOVSB, MOVSD, MOVSHDUP, MOVSLDUP, MOVSQ, MOVSS, MOVSW, MOVSX, M OVSXD, MOVUPS, MOVZX, MPSADBW, MULPD, MULPS, MULSD, MULSS, MWAIT, MULX, MWAIT, NEG, NOP, NOT, ORPD, ORPS, OUTS, OUTSB, O UTSD, OUTSW, PABSB, PABSD, PABSW, PACKSSDW, PACKSSWB, PACKUSDW, PACKUSWB, PADDD, PADDQ, PADDSB, PADDSW, PADDUSB, PADDUSW, PADDW, PALIGNR, PANDN, PAUSE, PAVGB, PAVGW, PBLENDVB, PBLENDW, PCLMULQDQ, PCMPEQB, PCMPEQD, PCMPEQQ, PCMPEQW, PCMPESTRI, PCMPESTRM, PCMP GTB, PCMPGTD, PCMPGTQ, PCMPGTW, PCMPISTRI, PCMPISTRM, PDEP, PEXTRB, PEXTRD, PEXTRQ, PEXTRW, PHADDD, PHADDSW, PHADDW, PHMINPOSUW, PHS UBD, PHSUBSW, PHSUBW, PINSRB, PINSRD, PINSRQ, PINSRW, PMADDUBSW, PMADDWD, PMAXSB, PMAXSD, PMAXSW, PMAXUB, PMAXUD, PMAXUW, PMINSB, PMINS D, PMINSW, PMINUB, PMINUD, PMINUW, PMOVMSKB, PMOVSX, PMOVZX, PMULDQ, PMULHRSW, PMULHUW, PMULHW, PMULLD, PMULLW, PMULUDQ, POPA, PO PAD, POPCNT, POPFD, POPFQ, POR, PREFETCHWT 1, PREFETCHh, PSADBW, PSHUFB, PSHUFD, PSHUFHW, PSHUFLW, PSHUFW, PSIGNB, PSIGND, PSIG NW, PSLLDQ, PSLLW, PSRAD, PSRAW, PSRLDQ, PSRLW, PSUBB, PSUBD, PSUBQ, PSUBSB, PSUBSW, PSUBUSB, PSUBUSW, PSUBW, PTEST, PU NPCKHBW, PUNPCKHDQ, PUNPCKHQDQ, PUNPCKHWD, PUNPCKLBW, PUNPCKLDQ, PUNPCKLQDQ, PUNPCKLWD, PUSHA, PUSHAD, PUSHFD, PXOR, RC L, RCPPS, RCPSS, RCR, RDFSBASE, RDGSBASE, RDMSR, RDPMC, RDRAND, RDSEED, RDTSCP, REPE, REPNZ, REPZ, RET, ROL, RORX, ROUNDPD, R OUNDPS, ROUNDSD, ROUNDSS, RSM, RSQRTPS, RSQRTSS, SAHF, SAL, SARX, SBB, SCASB, SCASD, SCASW, SETcc, SFENCE, SGDT, SHLD, SHLX, SHRD , SHRX, SHUFPD, SHUFPS, SIDT, SLDT, SMSW, SQRTPD, SQRTPS, SQRTSD, SQRTSS, STAC, STD, STI, STMXCSR, STOSB, STOSD, STOSQ, STOSW, STR, SUBPD, SUBPS, SUBSD, SUBSS, SWAPGS, SYSCALL, SYSENTER, SYSEXIT, SYSRET, TEST, TZCNT, UCOMISD, UCOMISS, UD 2, UNPCKHPD, UNPCKHPS, UNPCKLPD, UNPCKLPS, VB ROADCAST, VCVTPH 2 PS, VCVTPS 2 PH, VERR, VERW, VEXTRACTF 128, VEXTRACTI 128, VFMADD 132 PD, VFMADD 132 PS, VFMADD 132 SD, VFMADD 132 SS, VFMADD 213 P D, VFMADD 213 PS, VFMADD 213 SD, VFMADD 213 SS, VFMADD 231 PD, VFMADD 231 PS, VFMADD 231 SD, VFMADD 231 SS, VFMADDSUB 132 PD, VFMADDSUB 132 PS, VFMAD DSUB 213 PD, VFMADDSUB 213 PS, VFMADDSUB 231 PD, VFMADDSUB 231 PS, VFMSUB 132 PD, VFMSUB 132 PS, VFMSUB 132 SD, VFMSUB 132 SS, VFMSUB 213 PD, VFMSUB 21 3 PS, VFMSUB 213 SD, VFMSUB 213 SS, VFMSUB 231 PD, VFMSUB 231 PS, VFMSUB 231 SD, VFMSUB 231 SS, VFMSUBADD 132 PD, VFMSUBADD 132 PS, VFMSUBADD 213 PD, VF MSUBADD 213 PS, VFMSUBADD 231 PD, VFMSUBADD 231 PS, VFNMADD 132 PD, VFNMADD 132 PS, VFNMADD 132 SD, VFNMADD 132 SS, VFNMADD 213 PD, VFNMADD 213 P S, VFNMADD 213 SD, VFNMADD 213 SS, VFNMADD 231 PD, VFNMADD 231 PS, VFNMADD 231 SD, VFNMADD 231 SS, VFNMSUB 132 PD, VFNMSUB 132 PS, VFNMSUB 132 SD, VF NMSUB 132 SS, VFNMSUB 213 PD, VFNMSUB 213 PS, VFNMSUB 213 SD, VFNMSUB 213 SS, VFNMSUB 231 PD, VFNMSUB 231 PS, VFNMSUB 231 SD, VFNMSUB 231 SS, VGATHER DPD, VGATHERDPS, VGATHERQPD, VGATHERQPS, VINSERTF 128, VINSERTI 128, VMASKMOV, VPBLENDD, VPBROADCAST, VPERM 2 F 128, VPERM 2 I 128, VPERMD, VPE RMILPD, VPERMILPS, VPERMPD, VPERMPS, VPERMQ, VPGATHERDD, VPGATHERDQ, VPGATHERQD, VPGATHERQQ, VPMASKMOV, VPSLLVD, VPSLLVQ, VPSRAVD, V PSRLVD, VPSRLVQ, VTESTPD, VTESTPS, VZEROALL, VZEROUPPER, WAIT, WBINVD, WRFSBASE, WRGSBASE, WRMSR, XABORT, XACQUIRE, XADD, XBEGIN, XCHG, XE ND, XGETBV, XLATB, XORPD, XORPS, XRELEASE, XRSTORS, XSAVEC, XSAVEOPT, XSAVES, XSETBV, XTEST , 38 3 6 6 s e õ ç u r t Ins

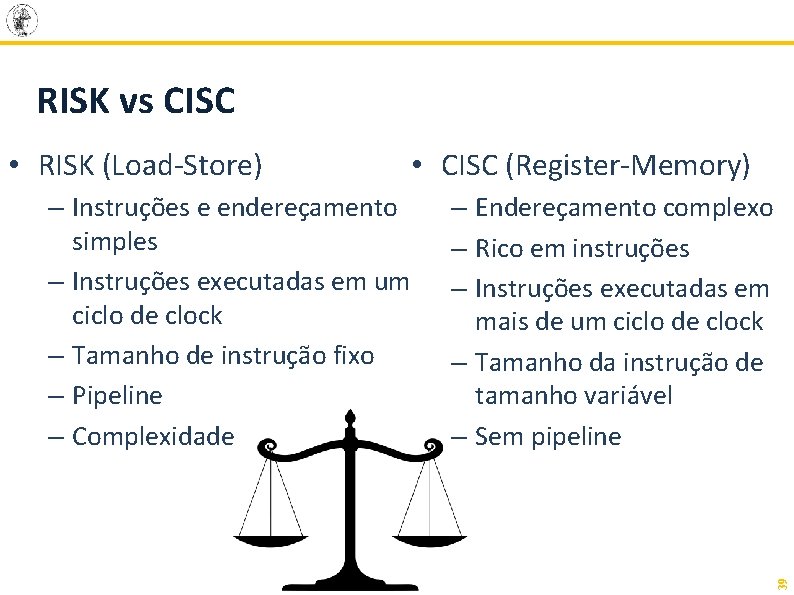

RISK vs CISC – Instruções e endereçamento simples – Instruções executadas em um ciclo de clock – Tamanho de instrução fixo – Pipeline – Complexidade • CISC (Register-Memory) – Endereçamento complexo – Rico em instruções – Instruções executadas em mais de um ciclo de clock – Tamanho da instrução de tamanho variável – Sem pipeline 39 • RISK (Load-Store)

- Slides: 38