PSI 3441 Arquitetura de Sistemas Embarcados Arquitetura do

PSI 3441 – Arquitetura de Sistemas Embarcados - Arquitetura do µProcessador Escola Politécnica da Universidade de São Paulo Prof. Gustavo Rehder – grehder@lme. usp. br Prof. Sergio Takeo – kofuji@usp. br Prof. Antonio Seabra – acseabra@lsi. usp. br

Objetivo do Vídeo • Entender como o processador executa um programa. • O que é o ciclo de máquina. • Entender a microarquitetura de processadores. (focado no Cortex M 0+ da ARM) 2 • Conhecer diferentes instruções executadas pelo processador.

Tarefa a ser executada pela CPU Programa (C, C++, Basic, Pascal, Python, Assembler, VLPs) Binário 2+2 4 Compilação 10 10 0 1 0 Código de máquina 3 Somador de 2 bits

Dentro da CPU – Ciclo de Máquina 2+2 1º Passo “FETCH” Busca as instruções na memória 2º Passo “DECODE” Decodifica as instruções Unidade de Controle Memória 3º Passo “EXECUTE” Executa as instruções ALU 4º Passo “STORE” Armazena os resultados na memória 4 ALU = Arithimetic and Logic Unit (ULA em português) 4

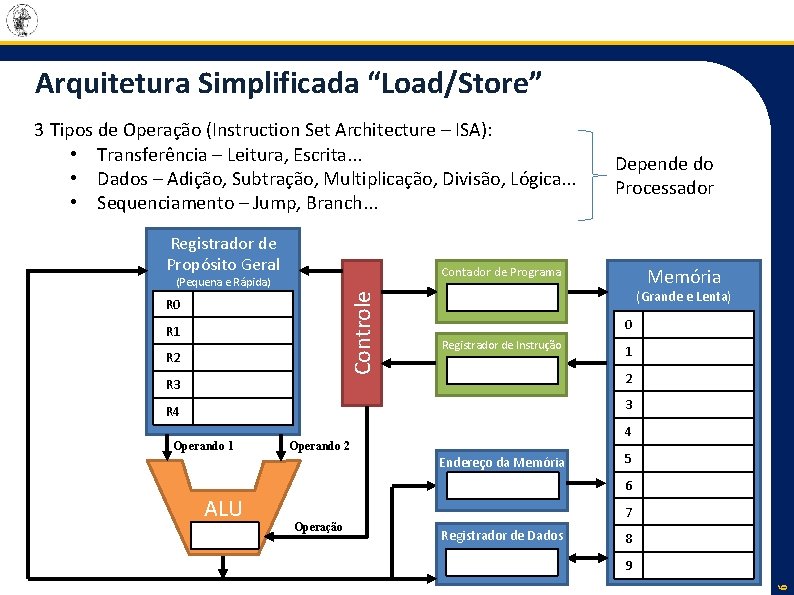

Arquitetura Simplificada “Load/Store” • A CPU não faz operações na Memória, todas as operações são realizadas pela ULA utilizando dados do Registrador • O programa e os dados são gravados na Memória • O programa é executado sequencialmente, uma instrução em cada linha da memória Registrador de Propósito Geral Memória Contador de Programa Controle (Pequena e Rápida) R 0 R 1 R 2 (Grande e Lenta) 0 Registrador de Instrução 1 R 3 2 R 4 3 4 Operando 2 Endereço da Memória ALU 5 6 7 Operação Registrador de Dados 8 9 5 Operando 1

Arquitetura Simplificada “Load/Store” 3 Tipos de Operação (Instruction Set Architecture – ISA): • Transferência – Leitura, Escrita. . . • Dados – Adição, Subtração, Multiplicação, Divisão, Lógica. . . • Sequenciamento – Jump, Branch. . . Registrador de Propósito Geral Depende do Processador Memória Contador de Programa Controle (Pequena e Rápida) R 0 R 1 R 2 (Grande e Lenta) 0 Registrador de Instrução 1 R 3 2 R 4 3 4 Operando 2 Endereço da Memória ALU 5 6 7 Operação Registrador de Dados 8 9 6 Operando 1

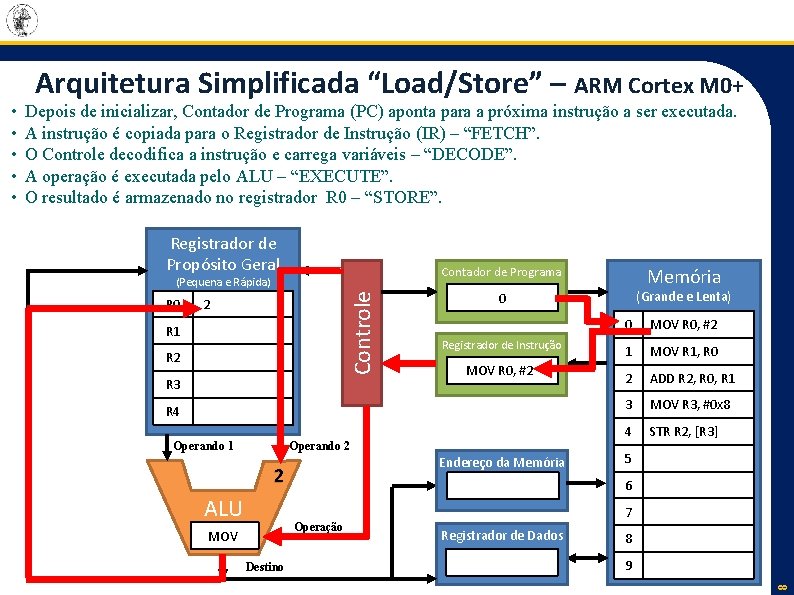

Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+ Instrução: MOVE – atribui o valor de Op 2 ao registrador Rn MOV Rn, Op 2 Dependendo da operação não é usado Op. Code Registrador de Propósito Geral Destino Constante de 8 bits Valor Memória Contador de Programa Controle (Pequena e Rápida) R 0 (Grande e Lenta) 0 MOV R 0, #2 1 MOV R 1, R 0 R 3 2 ADD R 2, R 0, R 1 R 4 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] R 1 R 2 Operando 2 Endereço da Memória ALU 5 6 7 Operação Registrador de Dados 8 9 7 Operando 1 Registrador de Instrução 2+2 Formato da Instrução: Operação Destino, Operando 1, Operando 2

Depois de inicializar, Contador de Programa (PC) aponta para a próxima instrução a ser executada. A instrução é copiada para o Registrador de Instrução (IR) – “FETCH”. O Controle decodifica a instrução e carrega variáveis – “DECODE”. A operação é executada pelo ALU – “EXECUTE”. O resultado é armazenado no registrador R 0 – “STORE”. Registrador de Propósito Geral 2 R 1 R 2 R 3 Registrador de Instrução MOV R 0, #2 R 4 Operando 1 Operando 2 Endereço da Memória 2 ALU (Grande e Lenta) 0 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 6 7 Operação MOV Destino Registrador de Dados 8 9 8 R 0 Memória Contador de Programa (Pequena e Rápida) Controle • • • Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+

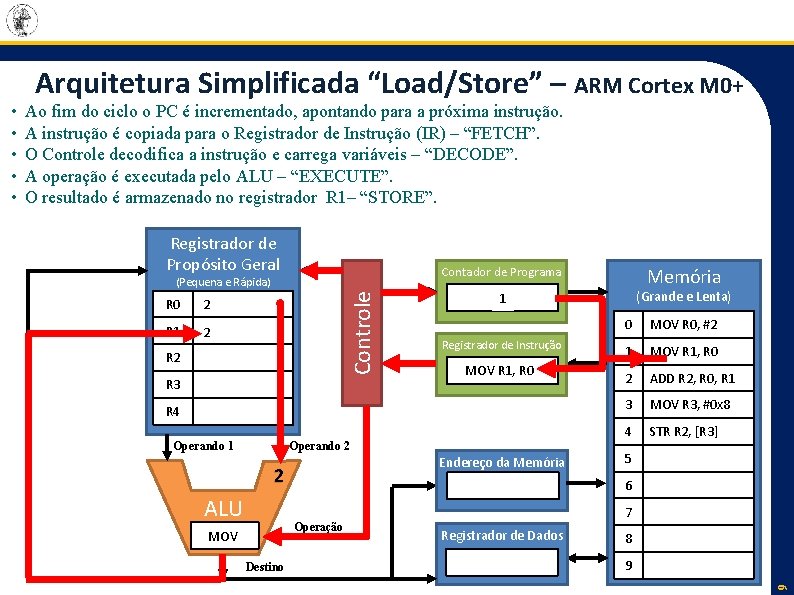

Ao fim do ciclo o PC é incrementado, apontando para a próxima instrução. A instrução é copiada para o Registrador de Instrução (IR) – “FETCH”. O Controle decodifica a instrução e carrega variáveis – “DECODE”. A operação é executada pelo ALU – “EXECUTE”. O resultado é armazenado no registrador R 1– “STORE”. Registrador de Propósito Geral 2 R 1 2 R 3 Registrador de Instrução MOV R 1, R 0 #2 R 4 Operando 1 Operando 2 Endereço da Memória 2 ALU (Grande e Lenta) 01 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 6 7 Operação MOV Destino Registrador de Dados 8 9 9 R 0 Memória Contador de Programa (Pequena e Rápida) Controle • • • Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+

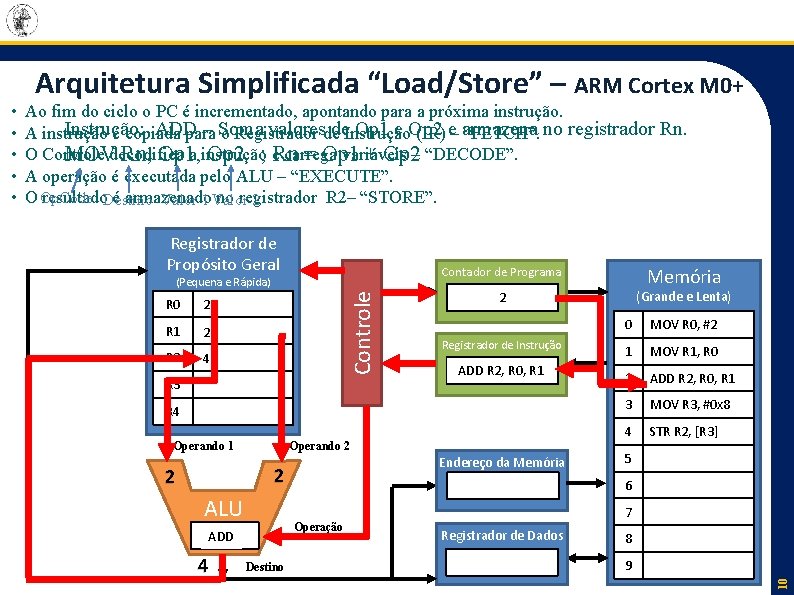

Ao fim do ciclo o PC é incrementado, apontando para a próxima instrução. Instrução: ADD – Soma valoresdede. Instrução Op 1 e Op 2 A instrução é copiada para o Registrador (IR) e– armazena “FETCH”. no registrador Rn. O Controle a instrução carrega variáveis MOVdecodifica Rn, Op 1, Op 2 ; e. Rn = Op 1 + Op 2– “DECODE”. A operação é executada pelo ALU – “EXECUTE”. O Op. Code resultado. Destino é armazenado no registrador R 2– “STORE”. 2 Valor 1 Valor Registrador de Propósito Geral 2 R 1 2 R 2 4 R 3 Registrador de Instrução ADD R 2, R 0, #2 R 1 MOV R 4 Operando 1 Operando 2 Endereço da Memória 2 2 ALU 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 6 7 Operação ADD MOV 4 (Grande e Lenta) 12 Destino Registrador de Dados 8 9 10 R 0 Memória Contador de Programa (Pequena e Rápida) Controle • • • Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+

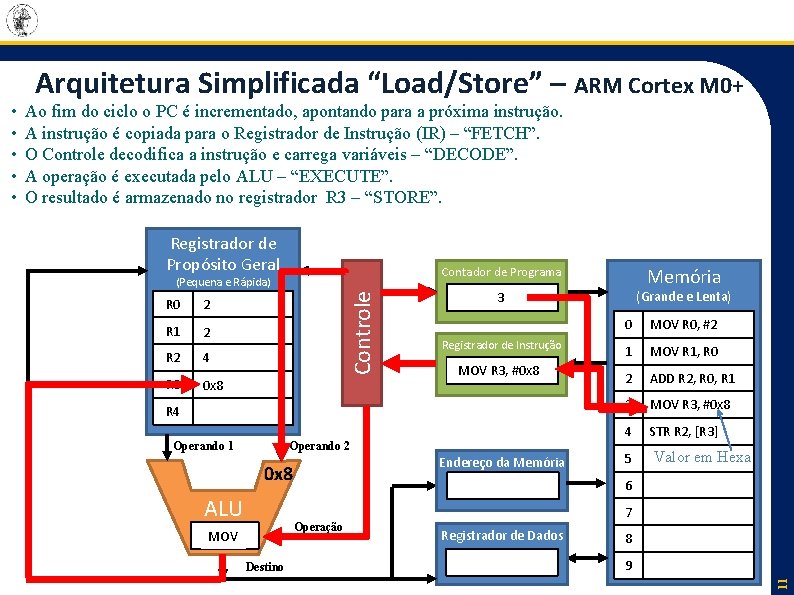

Ao fim do ciclo o PC é incrementado, apontando para a próxima instrução. A instrução é copiada para o Registrador de Instrução (IR) – “FETCH”. O Controle decodifica a instrução e carrega variáveis – “DECODE”. A operação é executada pelo ALU – “EXECUTE”. O resultado é armazenado no registrador R 3 – “STORE”. Registrador de Propósito Geral 2 R 1 2 R 2 4 R 3 0 x 8 Registrador de Instrução MOVR 3, R 0, #0 x 8 #2 R 4 Operando 1 Operando 2 Endereço da Memória 0 x 8 ALU (Grande e Lenta) 32 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 Valor em Hexa 6 7 Operação MOV Destino Registrador de Dados 8 9 11 R 0 Memória Contador de Programa (Pequena e Rápida) Controle • • • Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+

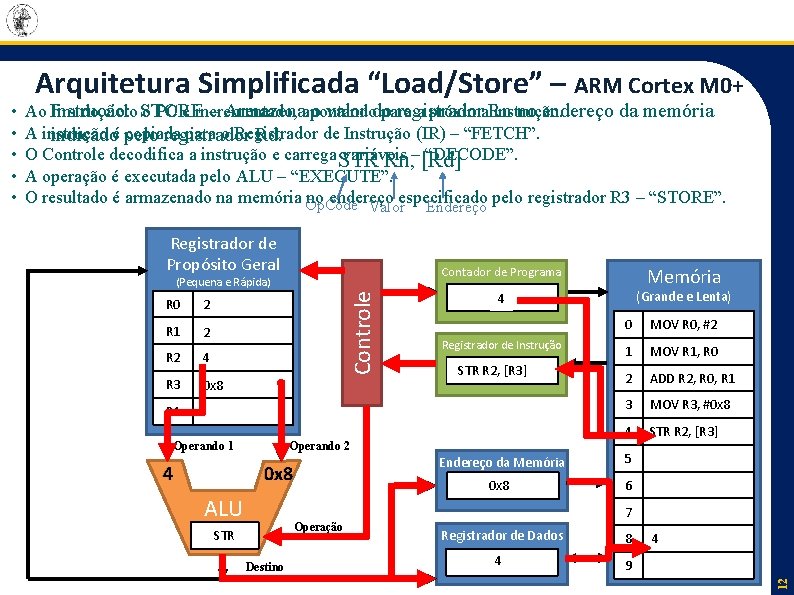

Ao Instrução: fim do ciclo STORE o PC é incrementado, para a próxima. Rn instrução. – Armazenaapontando o valor do registrador no endereço da memória A instrução copiada para o Registrador de Instrução (IR) – “FETCH”. indicadoé pelo registrador Rd. O Controle decodifica a instrução e carrega STR variáveis “DECODE”. Rn, –[Rd] A operação é executada pelo ALU – “EXECUTE”. O resultado é armazenado na memória Op. Code no endereço especificado pelo registrador R 3 – “STORE”. Valor Endereço Registrador de Propósito Geral 2 R 1 2 R 2 4 R 3 0 x 8 Registrador de Instrução STR R 2, R 0, [R 3] MOV #2 R 4 Operando 1 4 Operando 2 0 x 8 ALU (Grande e Lenta) 43 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] Endereço da Memória 5 0 x 8 6 7 Operação STR MOV Destino Registrador de Dados 8 4 9 4 12 R 0 Memória Contador de Programa (Pequena e Rápida) Controle • • • Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+

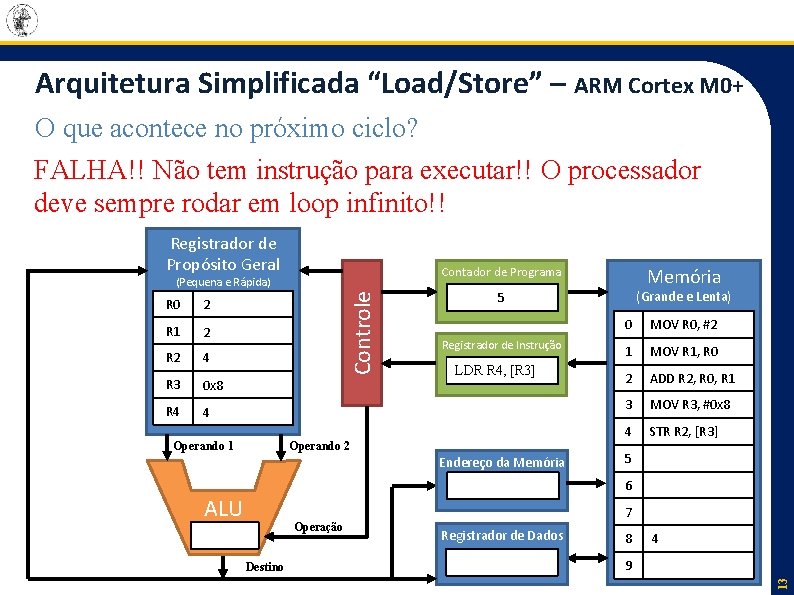

Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+ O que acontece no próximo ciclo? FALHA!! Não tem instrução para executar!! O processador deve sempre rodar em loop infinito!! Registrador de Propósito Geral R 1 2 R 2 4 R 3 0 x 8 R 4 4 Operando 1 (Grande e Lenta) 54 Registrador de Instrução LDR R 4, MOV R 0, [R 3] #2 Operando 2 Endereço da Memória 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 6 ALU 7 Operação Destino Registrador de Dados 8 4 9 13 2 Controle R 0 Memória Contador de Programa (Pequena e Rápida)

Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+ Instrução: LOAD – Carrega o registrador Rn com o valor do endereço da memória indicado pelo registrador Rd. Como colocar a posição 8 da memória no R 4? Qual é o fluxo? LDR Rn, [Rd] Op. Code Destino Endereço Registrador de Propósito Geral R 1 2 R 2 4 R 3 0 x 8 R 4 4 Operando 1 (Grande e Lenta) 54 Registrador de Instrução LDR R 4, MOV R 0, [R 3] #2 Operando 2 Endereço da Memória 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 LDR R 4, [R 3] 6 ALU 7 Operação Destino Registrador de Dados 8 4 9 14 2 Controle R 0 Memória Contador de Programa (Pequena e Rápida)

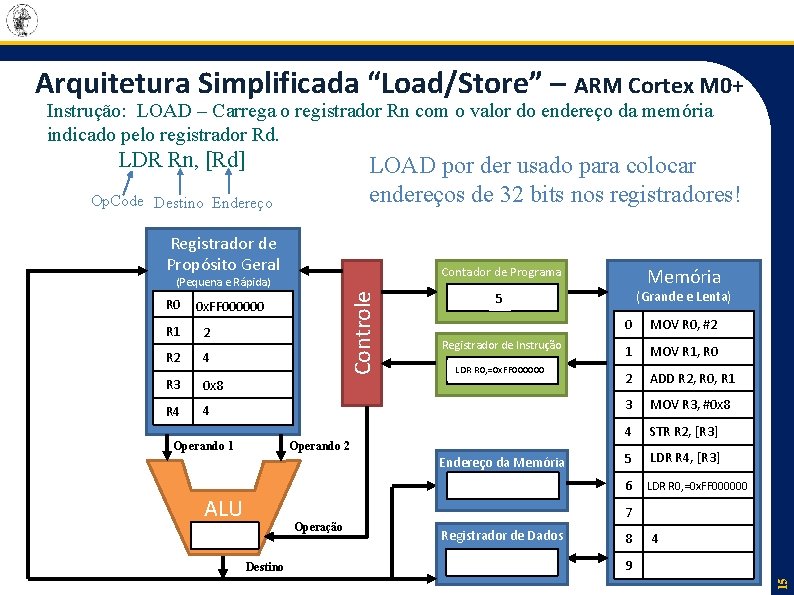

Arquitetura Simplificada “Load/Store” – ARM Cortex M 0+ Instrução: LOAD – Carrega o registrador Rn com o valor do endereço da memória indicado pelo registrador Rd. LDR Rn, [Rd] LOAD por der usado para colocar endereços de 32 bits nos registradores! Op. Code Destino Endereço Registrador de Propósito Geral Controle 2 0 x. FF 000000 R 1 2 R 2 4 R 3 0 x 8 R 4 4 Operando 1 Registrador de Instrução LDR R 0, =0 x. FF 000000 MOV R 0, #2 Operando 2 Endereço da Memória ALU (Grande e Lenta) 54 0 MOV R 0, #2 1 MOV R 1, R 0 2 ADD R 2, R 0, R 1 3 MOV R 3, #0 x 8 4 STR R 2, [R 3] 5 LDR R 4, [R 3] 6 LDR R 0, =0 x. FF 000000 7 Operação Destino Registrador de Dados 8 4 9 15 R 0 Memória Contador de Programa (Pequena e Rápida)

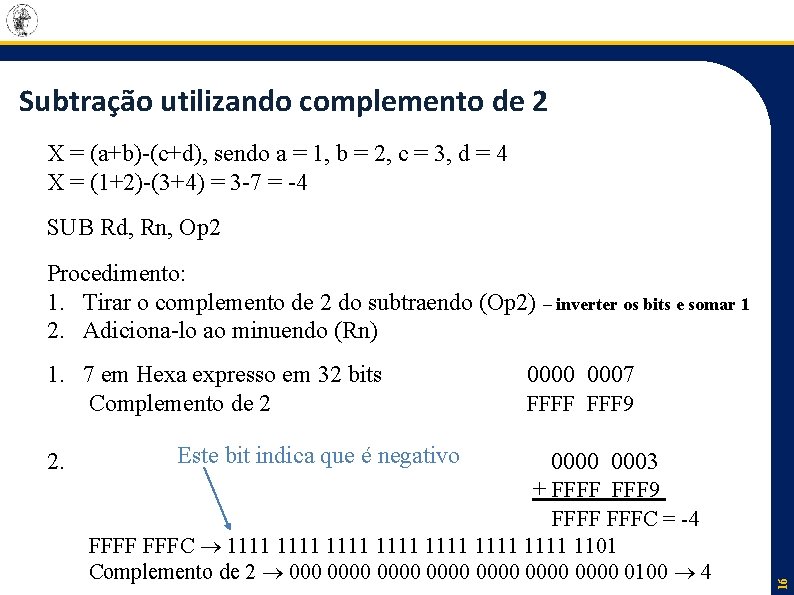

Subtração utilizando complemento de 2 X = (a+b)-(c+d), sendo a = 1, b = 2, c = 3, d = 4 X = (1+2)-(3+4) = 3 -7 = -4 SUB Rd, Rn, Op 2 Procedimento: 1. Tirar o complemento de 2 do subtraendo (Op 2) – inverter os bits e somar 1 2. Adiciona-lo ao minuendo (Rn) 1. 7 em Hexa expresso em 32 bits Complemento de 2 Este bit indica que é negativo FFFF 9 0000 0003 + FFFF 9 FFFF FFFC = -4 FFFF FFFC 1111 1111 1101 Complemento de 2 0000 0000 0100 4 16 2. 0000 0007

- Slides: 16