PS2 MouseKeyboard Port Discussion D 10 2 PS2

PS/2 Mouse/Keyboard Port Discussion D 10. 2

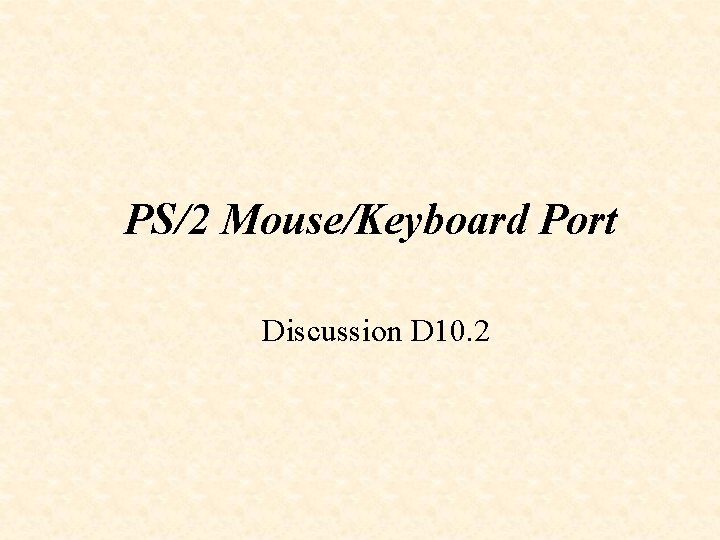

PS/2 Port

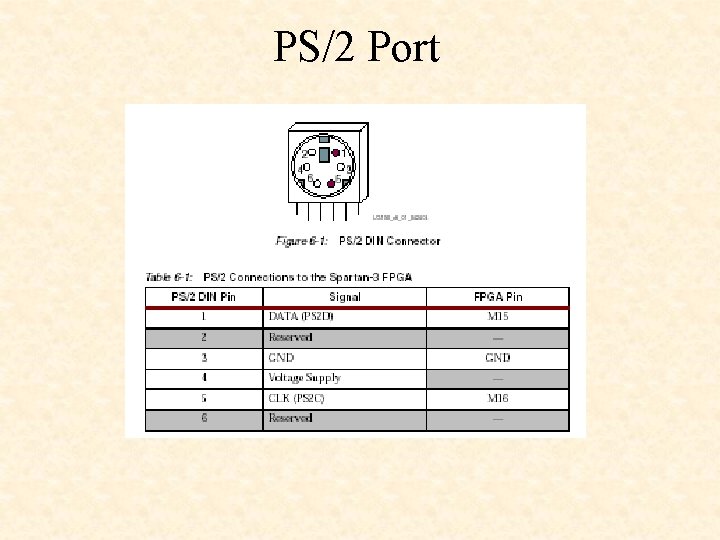

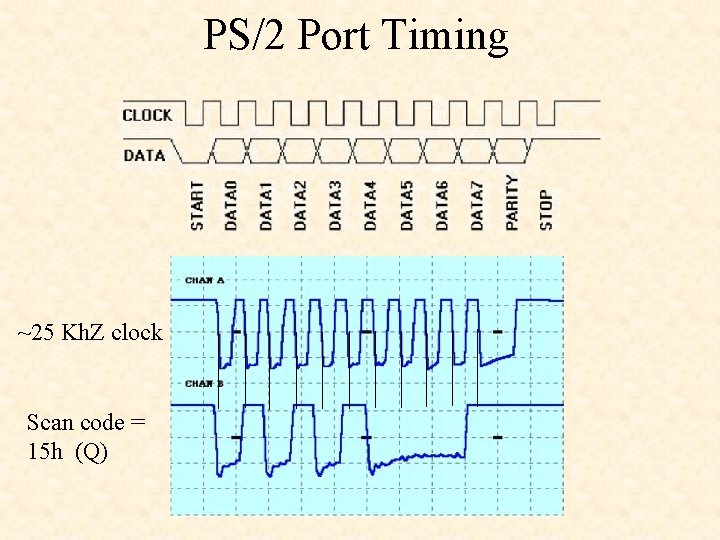

PS/2 Port Timing The clock frequency must be in the range 10 - 16. 7 k. Hz. Data sent from the device to the host is read on the falling edge of the clock signal. Data sent from the host to the device is read on the rising edge.

Summary: Bus States Data = high, Clock = high: Idle state. Data = high, Clock = low: Communication Inhibited. Data = low, Clock = high: Host Request-to-Send Device always generates the clock signal Data is transmitted one byte at a time Each byte is sent in a frame consisting of 11 -12 bits. 1 start bit. This is always 0. 8 data bits, least significant bit first. 1 parity bit (odd parity). 1 stop bit. This is always 1. 1 acknowledge bit (host-to-device communication only)

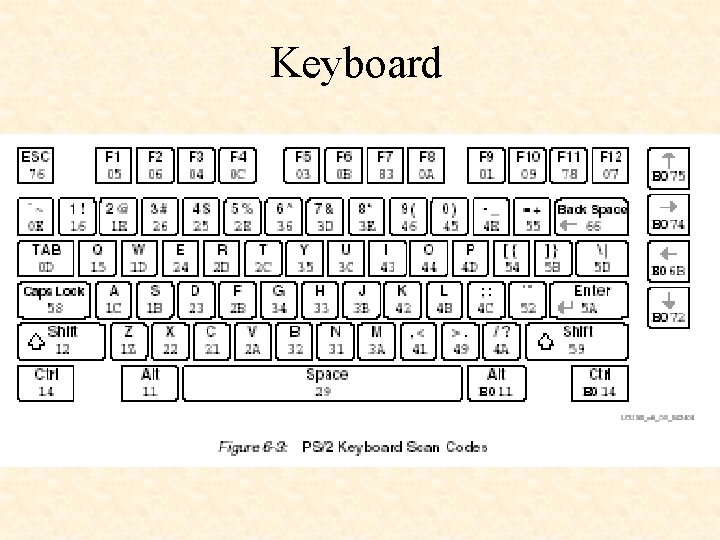

Keyboard

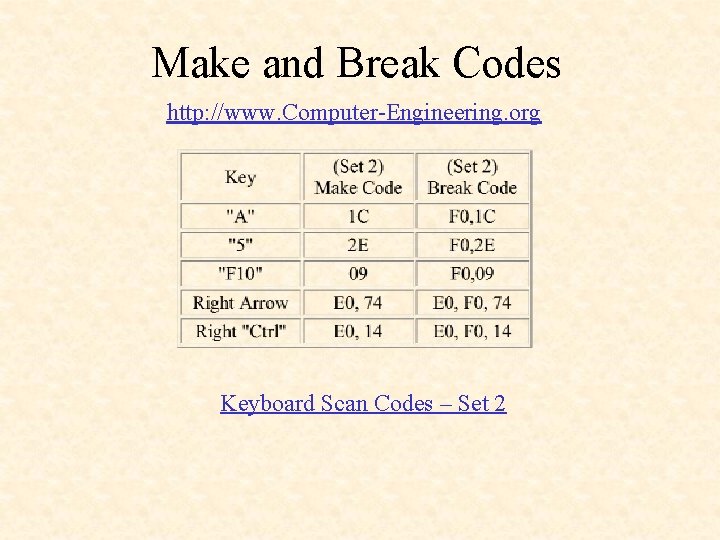

Make and Break Codes http: //www. Computer-Engineering. org Keyboard Scan Codes – Set 2

PS/2 Port Timing ~25 Kh. Z clock Scan code = 15 h (Q)

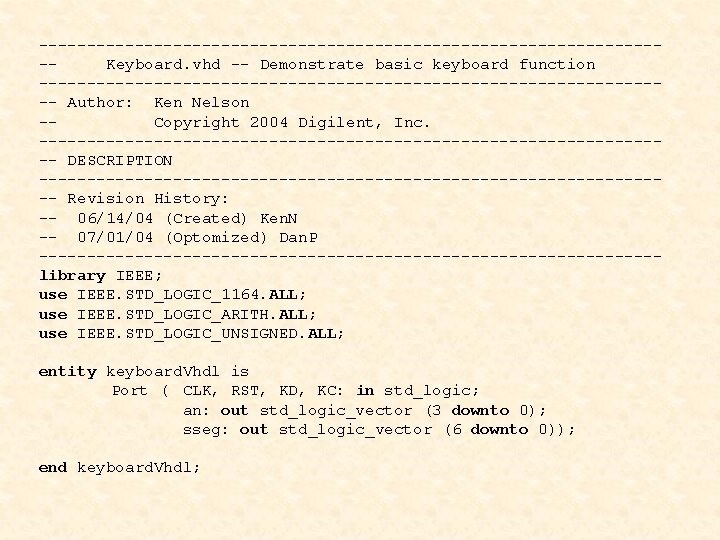

---------------------------------Keyboard. vhd -- Demonstrate basic keyboard function --------------------------------- Author: Ken Nelson -Copyright 2004 Digilent, Inc. --------------------------------- DESCRIPTION --------------------------------- Revision History: -- 06/14/04 (Created) Ken. N -- 07/01/04 (Optomized) Dan. P --------------------------------library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity keyboard. Vhdl is Port ( CLK, RST, KD, KC: in std_logic; an: out std_logic_vector (3 downto 0); sseg: out std_logic_vector (6 downto 0)); end keyboard. Vhdl;

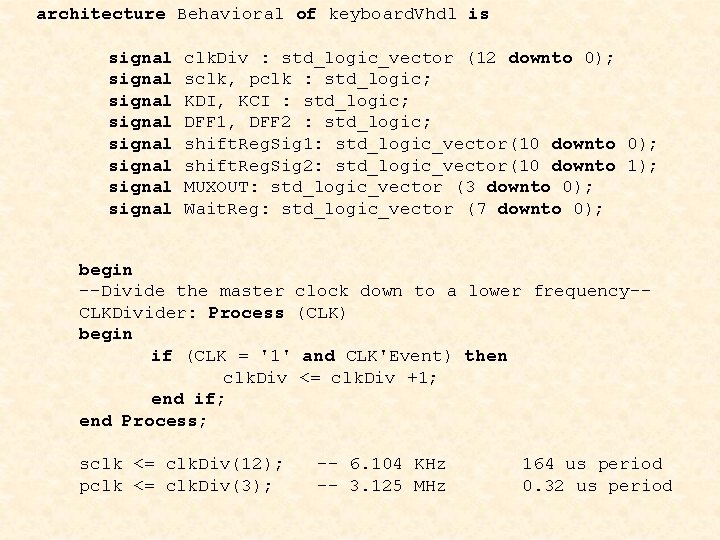

architecture Behavioral of keyboard. Vhdl is signal signal clk. Div : std_logic_vector (12 downto 0); sclk, pclk : std_logic; KDI, KCI : std_logic; DFF 1, DFF 2 : std_logic; shift. Reg. Sig 1: std_logic_vector(10 downto 0); shift. Reg. Sig 2: std_logic_vector(10 downto 1); MUXOUT: std_logic_vector (3 downto 0); Wait. Reg: std_logic_vector (7 downto 0); begin --Divide the master clock down to a lower frequency-CLKDivider: Process (CLK) begin if (CLK = '1' and CLK'Event) then clk. Div <= clk. Div +1; end if; end Process; sclk <= clk. Div(12); pclk <= clk. Div(3); -- 6. 104 KHz -- 3. 125 MHz 164 us period 0. 32 us period

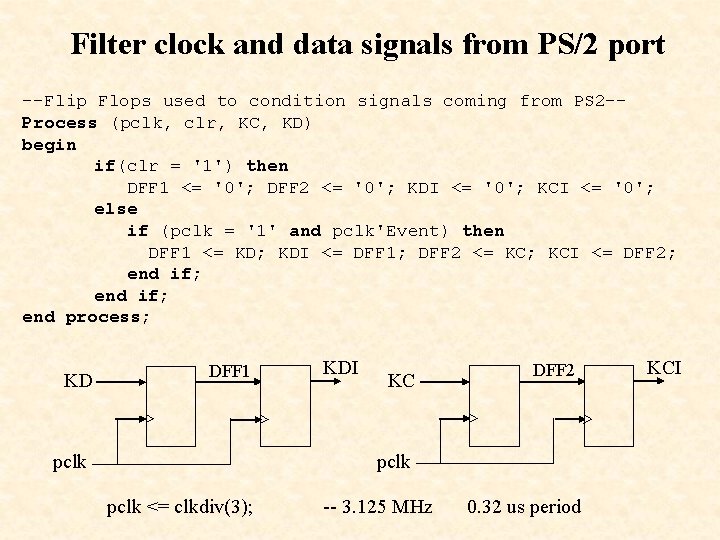

Filter clock and data signals from PS/2 port --Flip Flops used to condition signals coming from PS 2 -Process (pclk, clr, KC, KD) begin if(clr = '1') then DFF 1 <= '0'; DFF 2 <= '0'; KDI <= '0'; KCI <= '0'; else if (pclk = '1' and pclk'Event) then DFF 1 <= KD; KDI <= DFF 1; DFF 2 <= KC; KCI <= DFF 2; end if; end process; KD DFF 1 KDI KC DFF 2 pclk <= clkdiv(3); -- 3. 125 MHz 0. 32 us period KCI

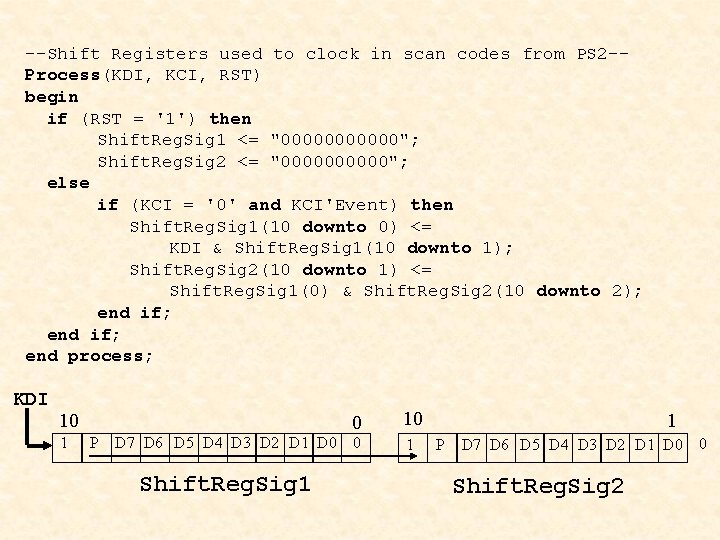

--Shift Registers used to clock in scan codes from PS 2 -Process(KDI, KCI, RST) begin if (RST = '1') then Shift. Reg. Sig 1 <= "000000"; Shift. Reg. Sig 2 <= "00000"; else if (KCI = '0' and KCI'Event) then Shift. Reg. Sig 1(10 downto 0) <= KDI & Shift. Reg. Sig 1(10 downto 1); Shift. Reg. Sig 2(10 downto 1) <= Shift. Reg. Sig 1(0) & Shift. Reg. Sig 2(10 downto 2); end if; end process; KDI 10 1 P D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 Shift. Reg. Sig 1 0 10 0 1 1 P D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 Shift. Reg. Sig 2 0

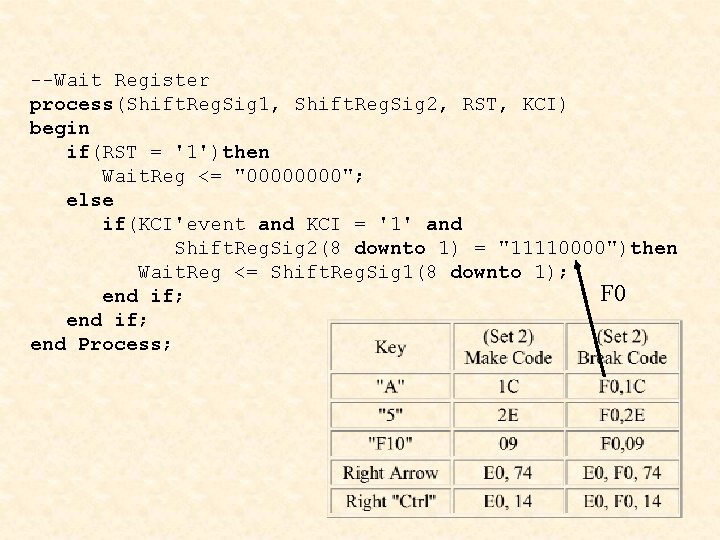

--Wait Register process(Shift. Reg. Sig 1, Shift. Reg. Sig 2, RST, KCI) begin if(RST = '1')then Wait. Reg <= "0000"; else if(KCI'event and KCI = '1' and Shift. Reg. Sig 2(8 downto 1) = "11110000")then Wait. Reg <= Shift. Reg. Sig 1(8 downto 1); F 0 end if; end Process;

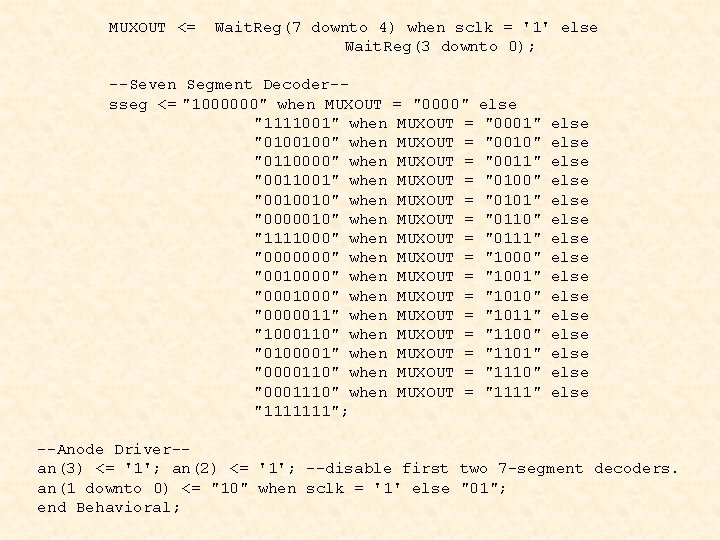

MUXOUT <= Wait. Reg(7 downto 4) when sclk = '1' else Wait. Reg(3 downto 0); --Seven Segment Decoder-sseg <= "1000000" when MUXOUT = "0000" else "1111001" when MUXOUT = "0001" "0100100" when MUXOUT = "0010" "0110000" when MUXOUT = "0011" "0011001" when MUXOUT = "0100" "0010010" when MUXOUT = "0101" "0000010" when MUXOUT = "0110" "1111000" when MUXOUT = "0111" "0000000" when MUXOUT = "1000" "0010000" when MUXOUT = "1001" "0001000" when MUXOUT = "1010" "0000011" when MUXOUT = "1011" "1000110" when MUXOUT = "1100" "0100001" when MUXOUT = "1101" "0000110" when MUXOUT = "1110" "0001110" when MUXOUT = "1111" "1111111"; else else else else --Anode Driver-an(3) <= '1'; an(2) <= '1'; --disable first two 7 -segment decoders. an(1 downto 0) <= "10" when sclk = '1' else "01"; end Behavioral;

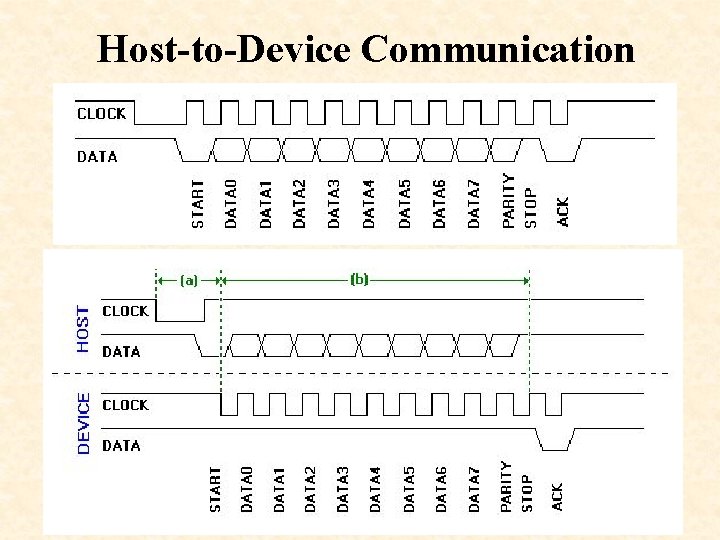

Host-to-Device Communication

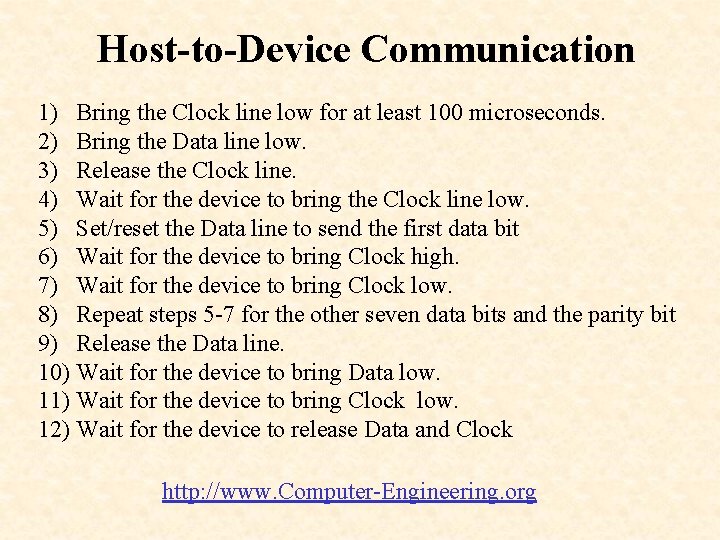

Host-to-Device Communication 1) Bring the Clock line low for at least 100 microseconds. 2) Bring the Data line low. 3) Release the Clock line. 4) Wait for the device to bring the Clock line low. 5) Set/reset the Data line to send the first data bit 6) Wait for the device to bring Clock high. 7) Wait for the device to bring Clock low. 8) Repeat steps 5 -7 for the other seven data bits and the parity bit 9) Release the Data line. 10) Wait for the device to bring Data low. 11) Wait for the device to bring Clock low. 12) Wait for the device to release Data and Clock http: //www. Computer-Engineering. org

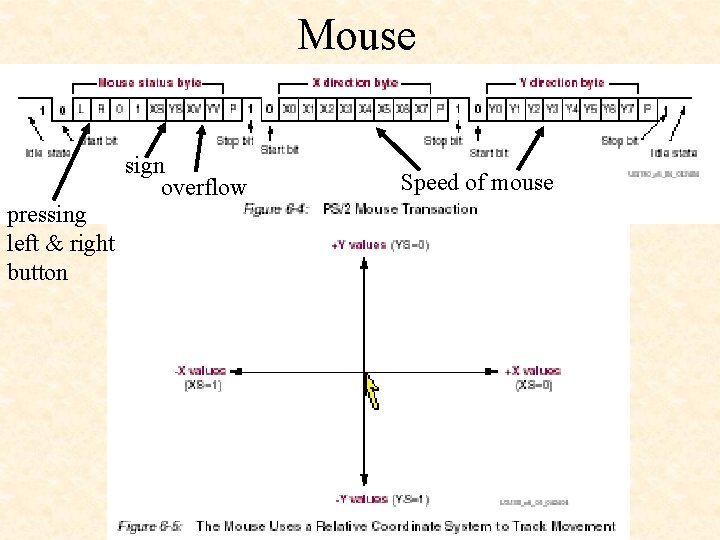

Mouse sign overflow pressing left & right button Speed of mouse

mouse. vhd source code http: //www. ece. gatech. edu/academic/courses/fpga/Xilinx/

- Slides: 17