Prototype Test of SPring8 FADC Module http www

- Slides: 12

Prototype Test of SPring-8 FADC Module http: //www. rcnp. osaka-u. ac. jp/~wchang/LEPS /Prototype. Test_FADC_SP 8. ppt

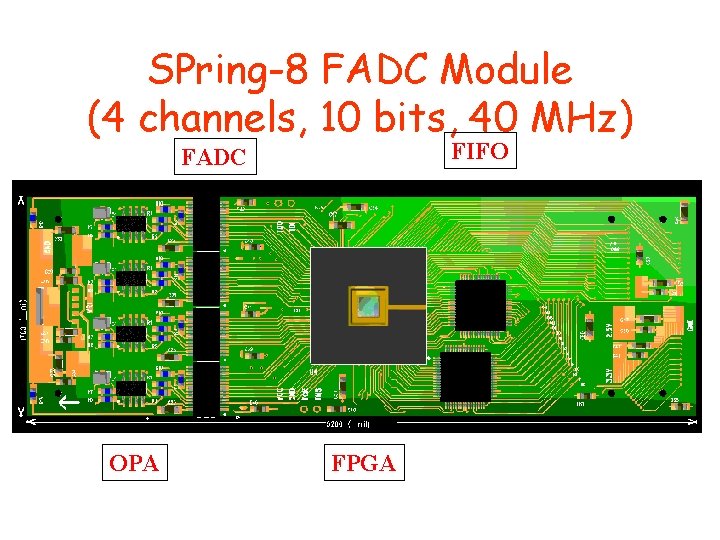

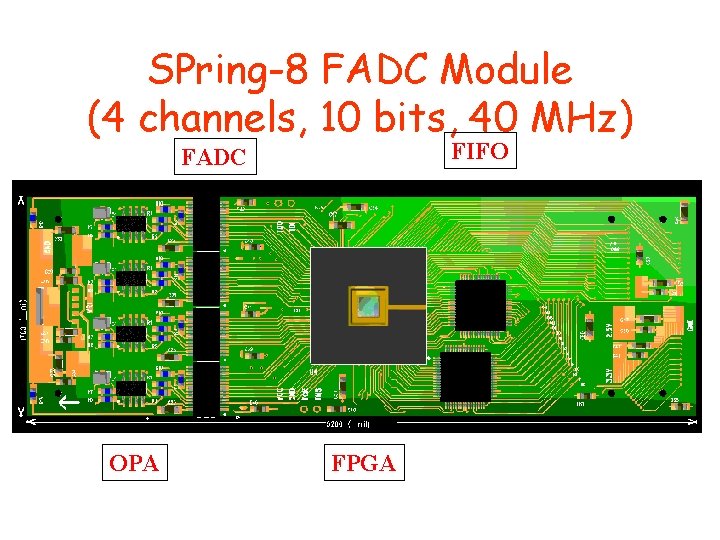

SPring-8 FADC Module (4 channels, 10 bits, 40 MHz) FIFO FADC OPA FPGA

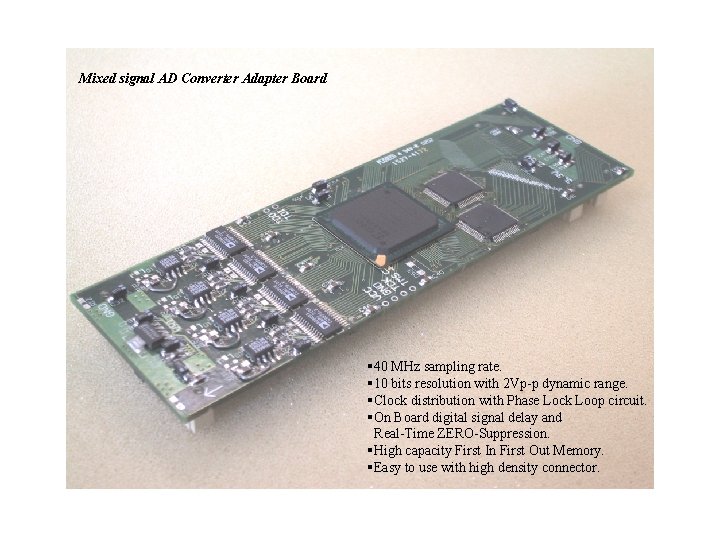

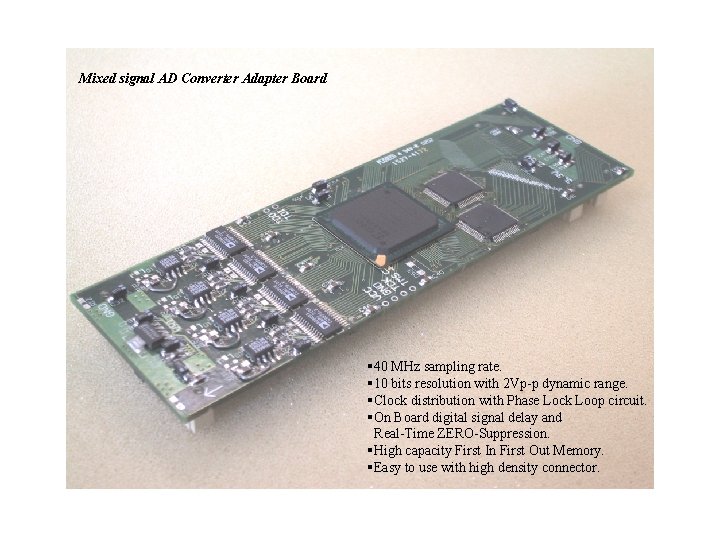

Mixed signal AD Converter Adapter Board § 40 MHz sampling rate. § 10 bits resolution with 2 Vp-p dynamic range. §Clock distribution with Phase Lock Loop circuit. §On Board digital signal delay and Real-Time ZERO-Suppression. §High capacity First In First Out Memory. §Easy to use with high density connector.

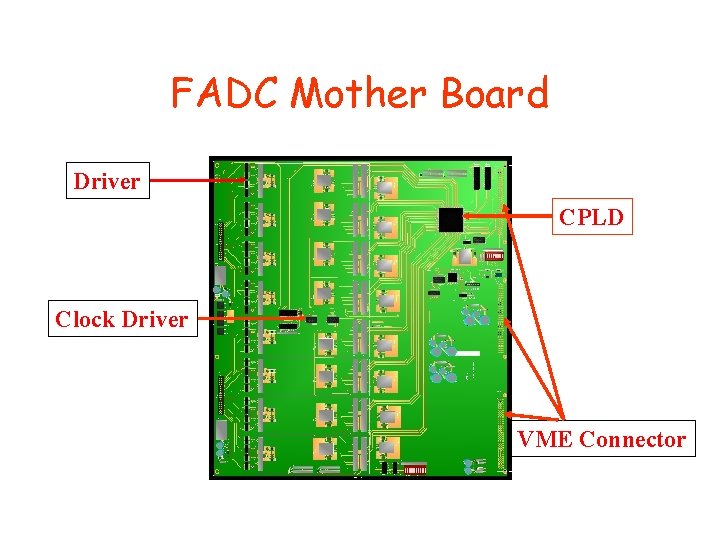

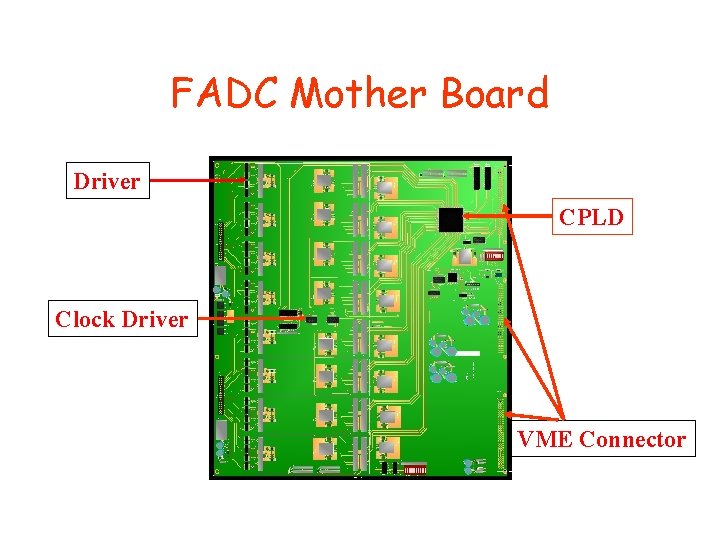

FADC Mother Board Driver CPLD Clock Driver VME Connector

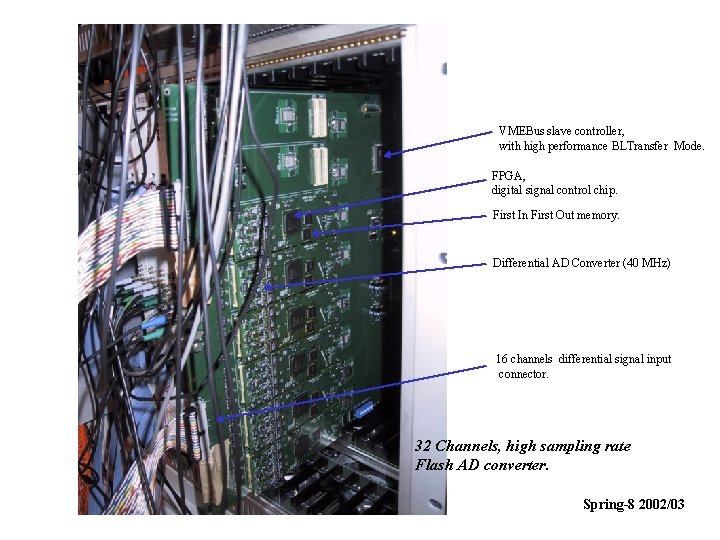

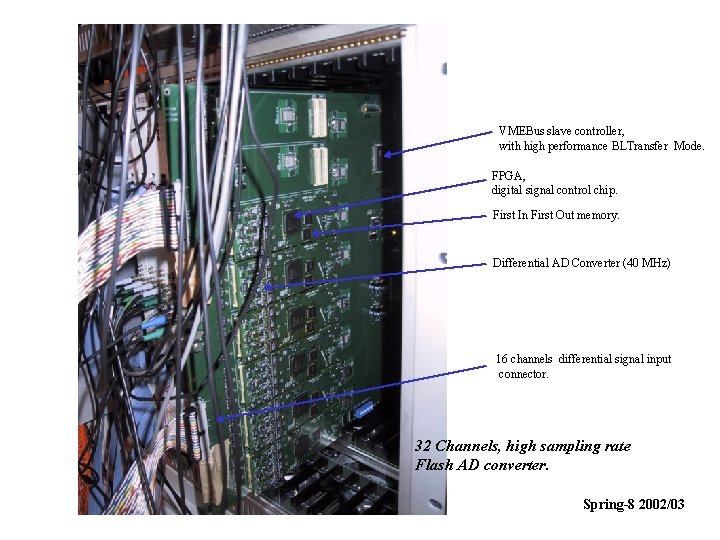

VMEBus slave controller, with high performance BLTransfer Mode. FPGA, digital signal control chip. First In First Out memory. Differential AD Converter (40 MHz) 16 channels differential signal input connector. 32 Channels, high sampling rate Flash AD converter. Spring-8 2002/03

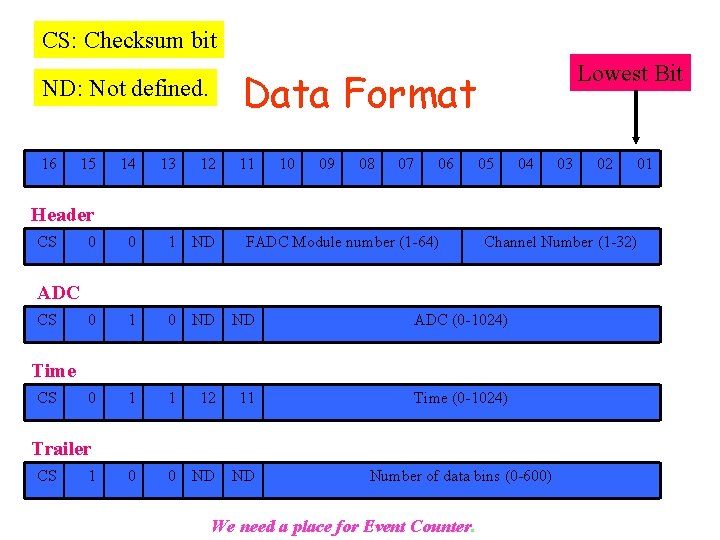

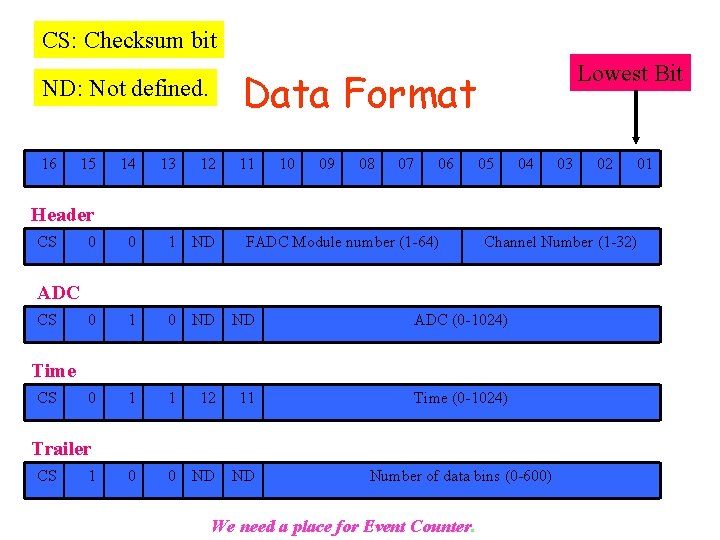

CS: Checksum bit ND: Not defined. Data Format 16 11 15 10 09 08 07 06 Lowest Bit 14 13 12 05 04 0 0 1 ND 0 1 0 ND ND ADC (0 -1024) 0 1 1 12 11 Time (0 -1024) 0 0 ND ND Number of data bins (0 -600) 03 02 01 Header CS FADC Module number (1 -64) Channel Number (1 -32) ADC CS Time CS Trailer CS 1 We need a place for Event Counter.

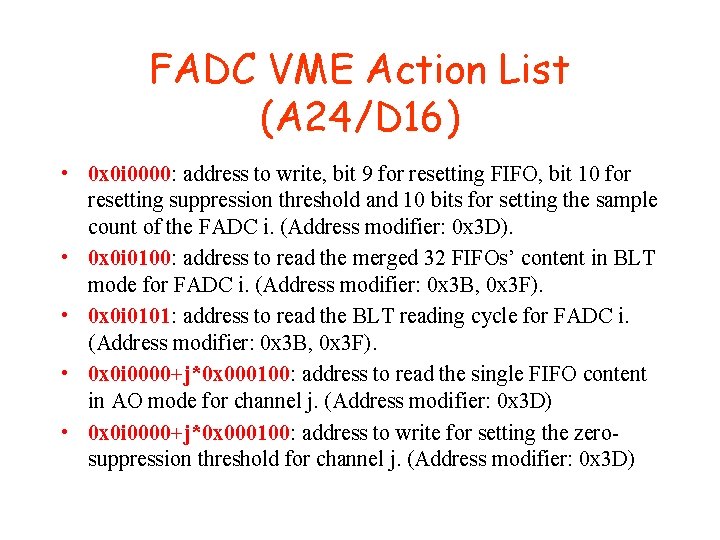

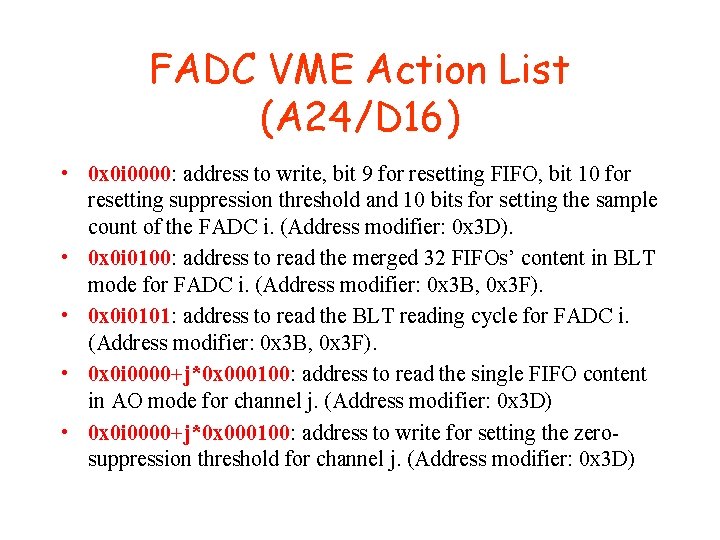

FADC VME Action List (A 24/D 16) • 0 x 0 i 0000: address to write, bit 9 for resetting FIFO, bit 10 for resetting suppression threshold and 10 bits for setting the sample count of the FADC i. (Address modifier: 0 x 3 D). • 0 x 0 i 0100: address to read the merged 32 FIFOs’ content in BLT mode for FADC i. (Address modifier: 0 x 3 B, 0 x 3 F). • 0 x 0 i 0101: address to read the BLT reading cycle for FADC i. (Address modifier: 0 x 3 B, 0 x 3 F). • 0 x 0 i 0000+j*0 x 000100: address to read the single FIFO content in AO mode for channel j. (Address modifier: 0 x 3 D) • 0 x 0 i 0000+j*0 x 000100: address to write for setting the zerosuppression threshold for channel j. (Address modifier: 0 x 3 D)

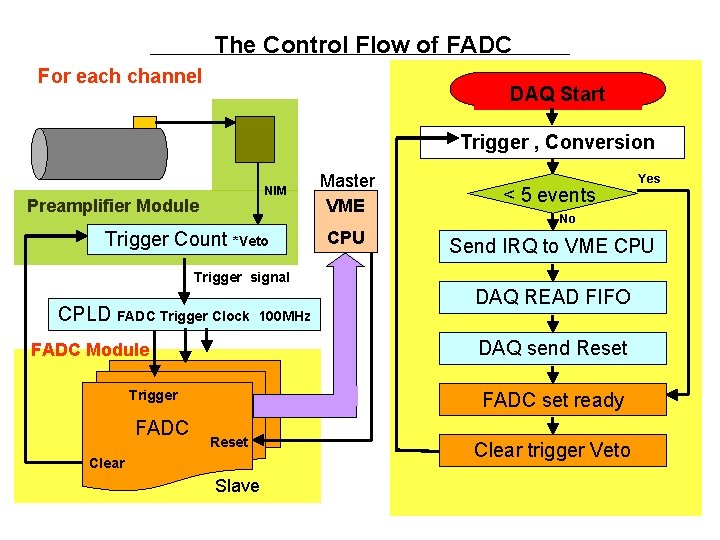

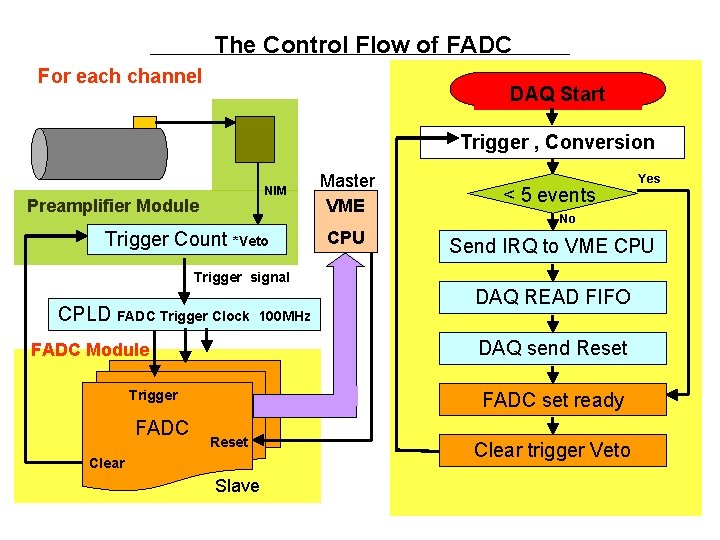

The Control Flow of FADC For each channel DAQ Start Trigger , Conversion NIM Preamplifier Module Trigger Count *Veto Master VME < 5 events CPU Send IRQ to VME CPU No Trigger signal CPLD FADC Trigger Clock 100 MHz Trigger FADC DAQ READ FIFO DAQ send Reset FADC Module FADC set ready Reset Clear Slave Yes Clear trigger Veto

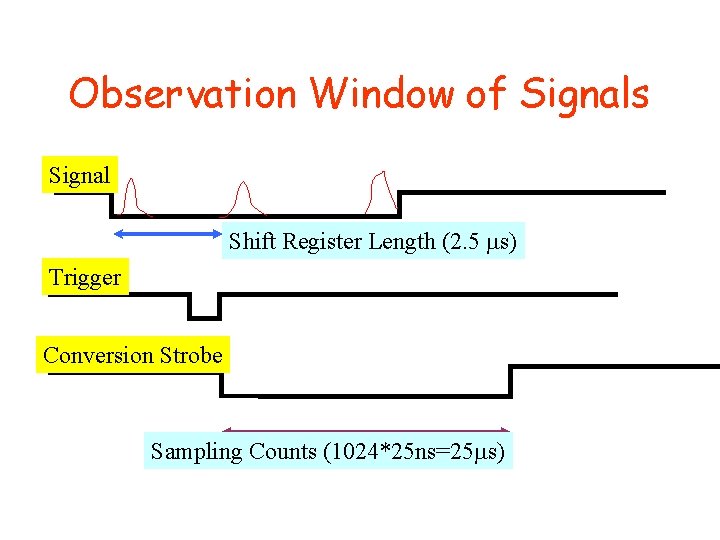

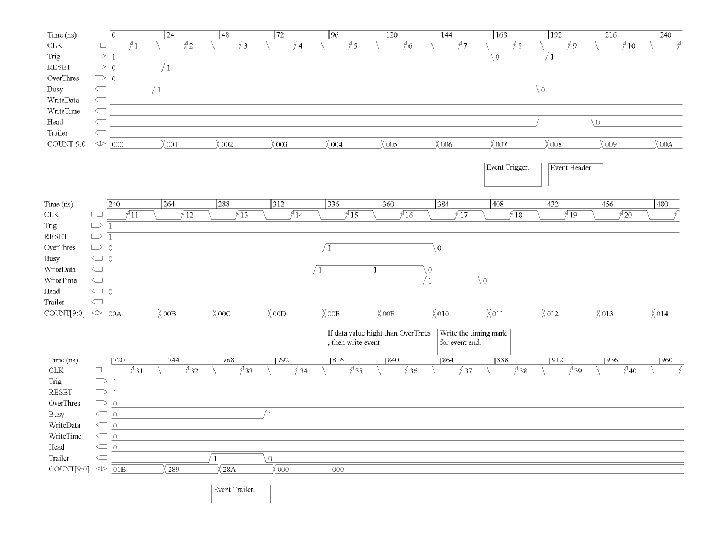

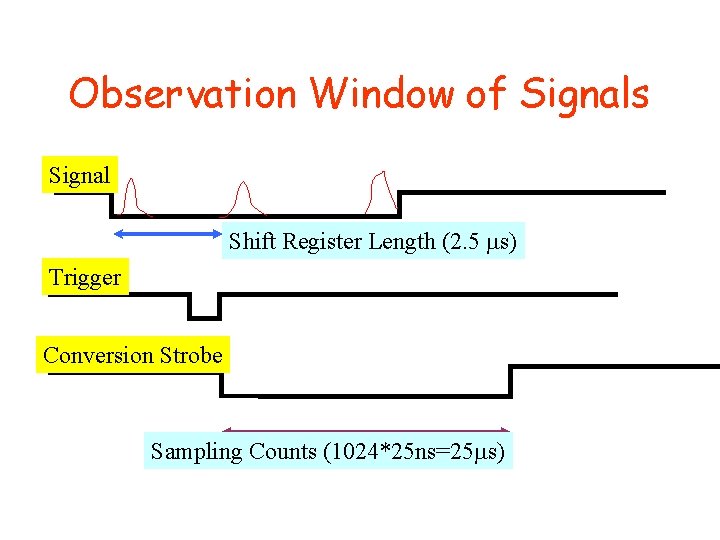

Observation Window of Signals Signal Shift Register Length (2. 5 s) Trigger Conversion Strobe Sampling Counts (1024*25 ns=25 s)

To-do Itmes During SPring-8 Visit • • Complete one full 32 -channel FADC module. TEXONO DAQ. Finalize and implement the VME action list. Determine and implement the default values for shift register length (1 -2 micro sec) and sampling count (about 600). • Implement the functions of “Reset” and “Busy” on the front-panel Lemo inputs and the definition of LED lights. • Fix up the gain range and signal coupling on the analog input. • Fix up the scheme of defining FADC reference voltage (pedestal) and zero suppression threshold.

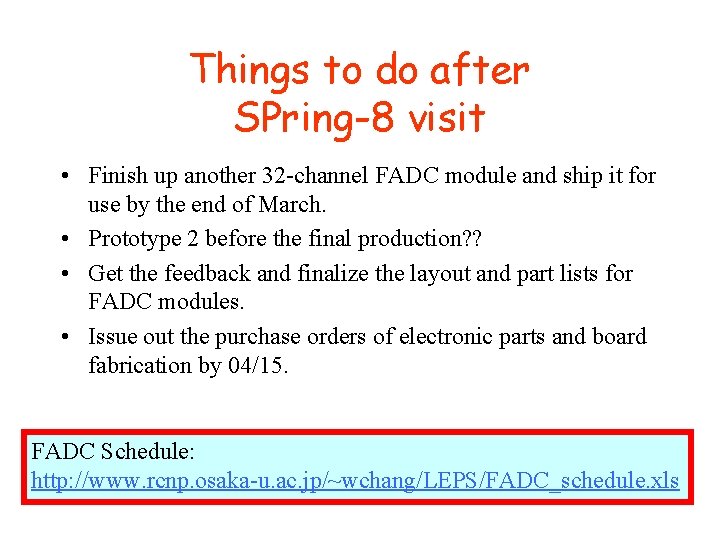

Things to do after SPring-8 visit • Finish up another 32 -channel FADC module and ship it for use by the end of March. • Prototype 2 before the final production? ? • Get the feedback and finalize the layout and part lists for FADC modules. • Issue out the purchase orders of electronic parts and board fabrication by 04/15. FADC Schedule: http: //www. rcnp. osaka-u. ac. jp/~wchang/LEPS/FADC_schedule. xls