Proto Dune Data Emulator using Front End LInk

- Slides: 16

Proto Dune Data Emulator using: Front. End LInk e. Xchange By: René Habraken

Introduction • Adjustments made to FELIX hardware • Data Emulator • Current status • Next steps 2

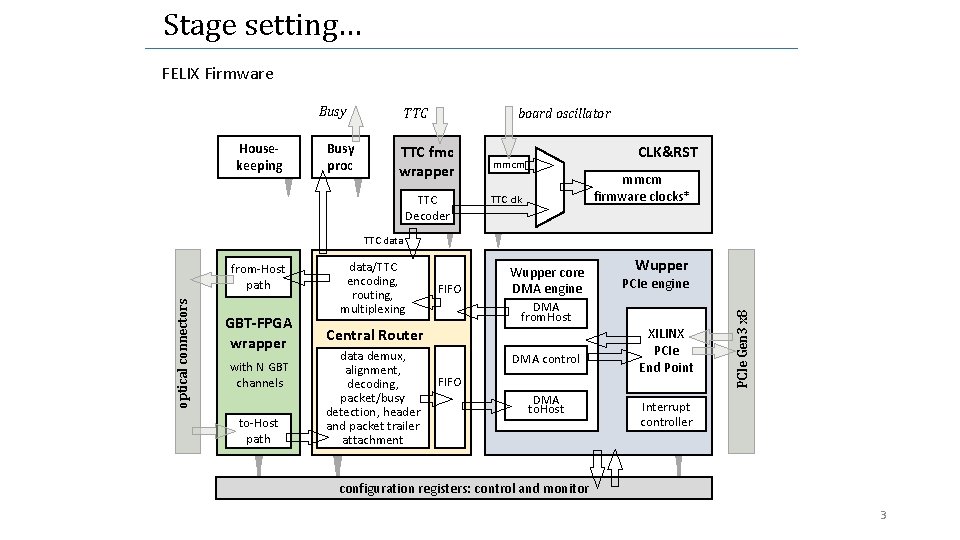

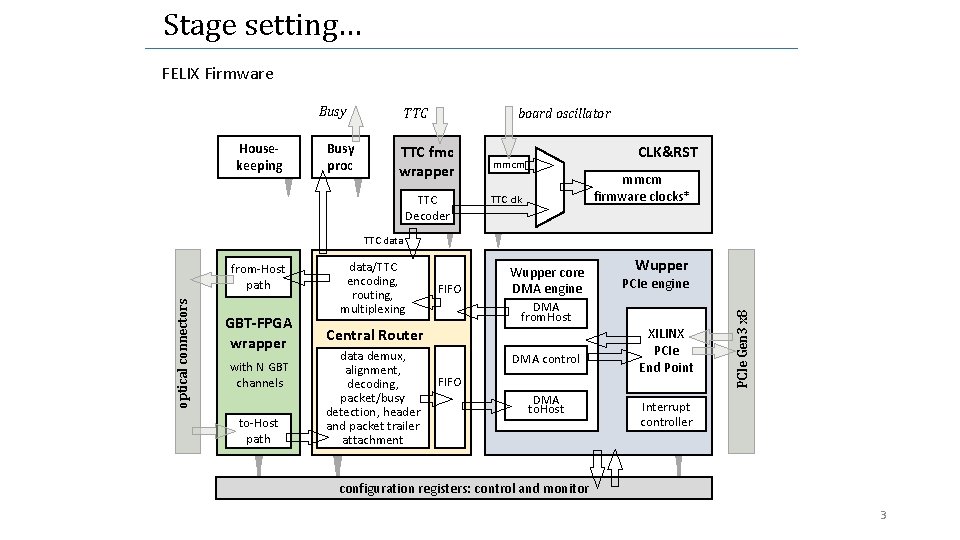

Stage setting… FELIX Firmware Busy Housekeeping Busy proc TTC board oscillator TTC fmc wrapper TTC Decoder CLK&RST mmcm firmware clocks* TTC clk TTC data GBT-FPGA wrapper with N GBT channels to-Host path data/TTC encoding, routing, multiplexing FIFO Wupper core DMA engine PCIe engine DMA from. Host Central Router data demux, alignment, decoding, packet/busy detection, header and packet trailer attachment Wupper DMA control FIFO DMA to. Host XILINX PCIe End Point PCIe Gen 3 x 8 optical connectors from-Host path Interrupt controller configuration registers: control and monitor 3

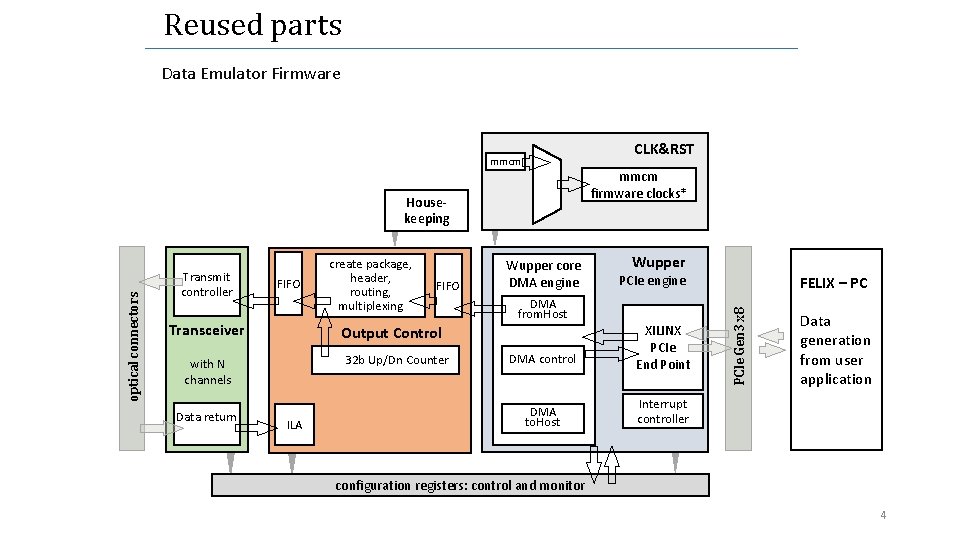

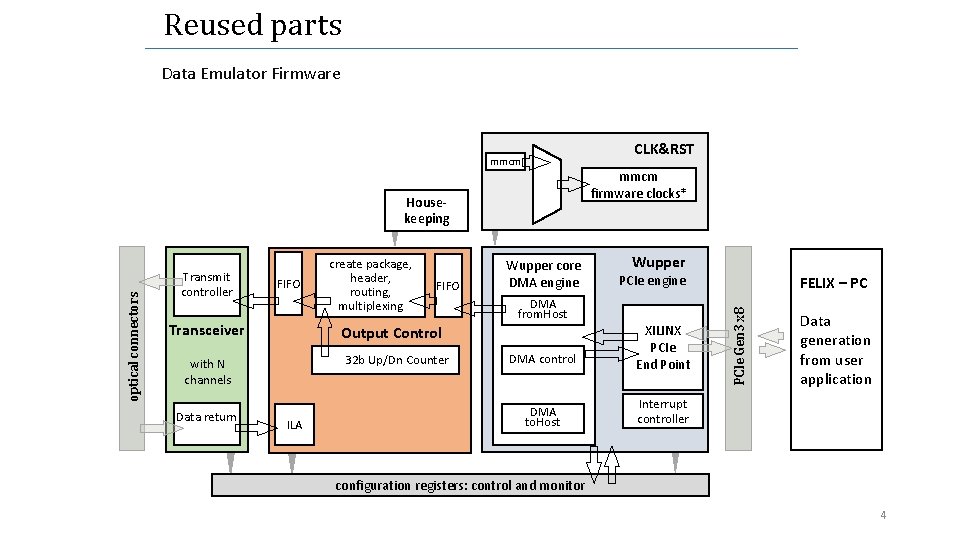

Reused parts Data Emulator Firmware CLK&RST mmcm firmware clocks* Transmit controller FIFO Transceiver FIFO Wupper core DMA engine 32 b Up/Dn Counter ILA Wupper PCIe engine DMA from. Host DMA control XILINX PCIe End Point DMA to. Host Interrupt controller Output Control with N channels Data return create package, header, routing, multiplexing FELIX – PC PCIe Gen 3 x 8 optical connectors Housekeeping Data generation from user application configuration registers: control and monitor 4

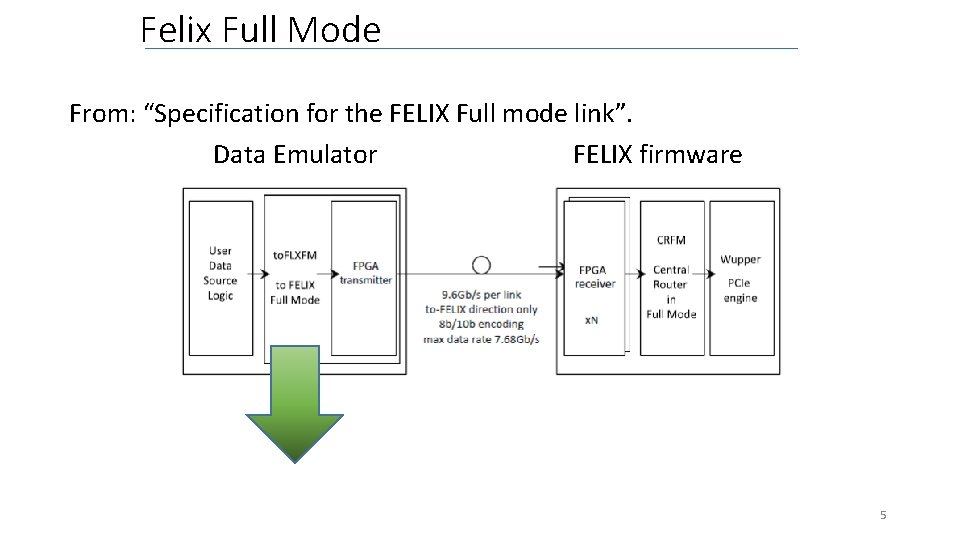

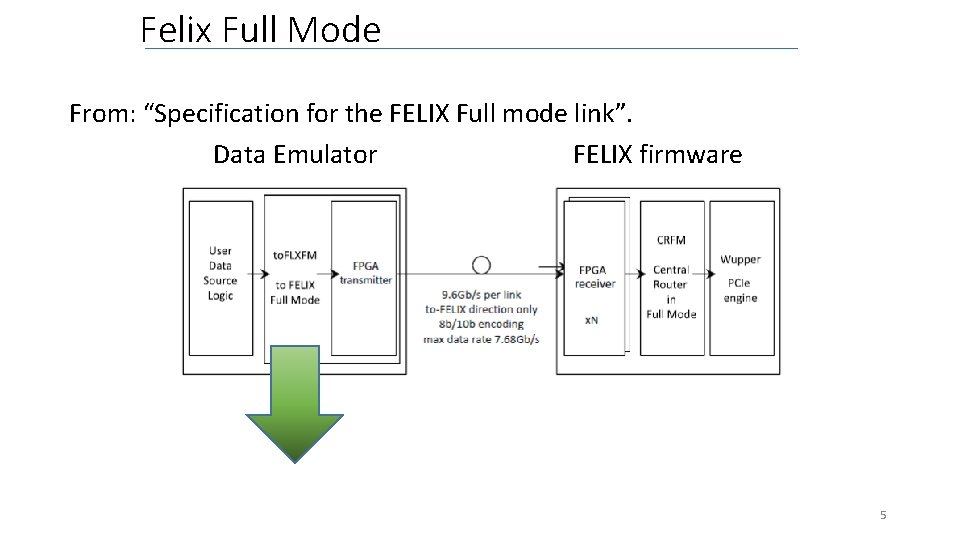

Felix Full Mode From: “Specification for the FELIX Full mode link”. Data Emulator FELIX firmware 5

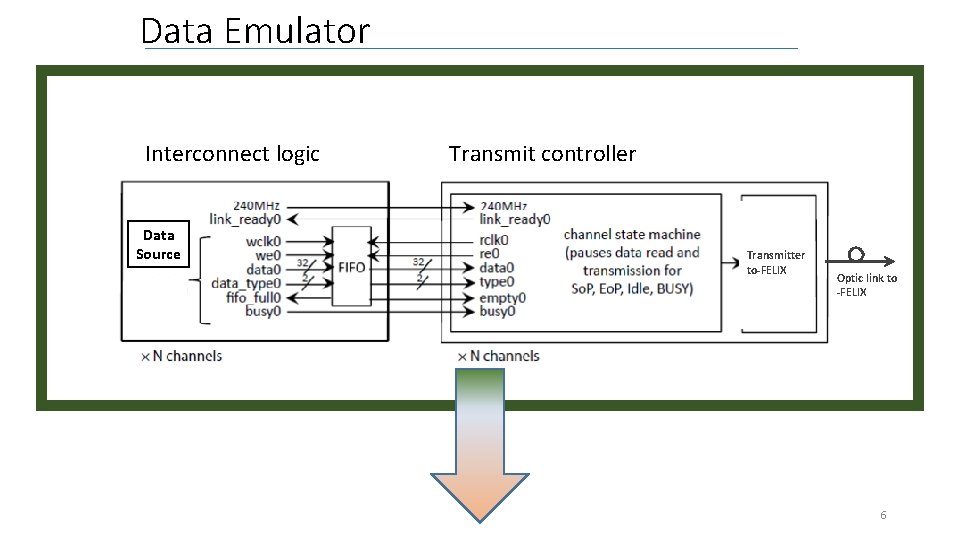

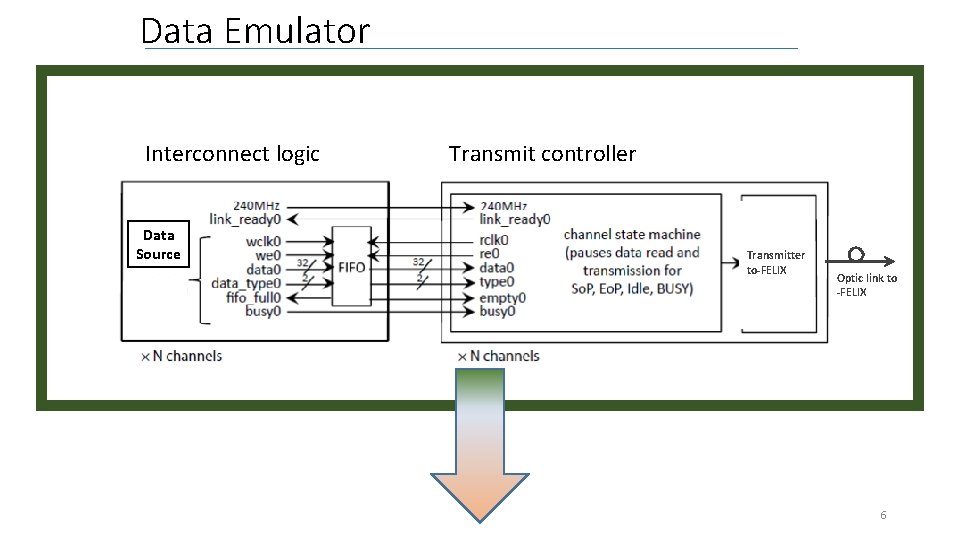

Data Emulator Interconnect logic Data Source Transmit controller Transmitter to-FELIX Optic link to -FELIX 6

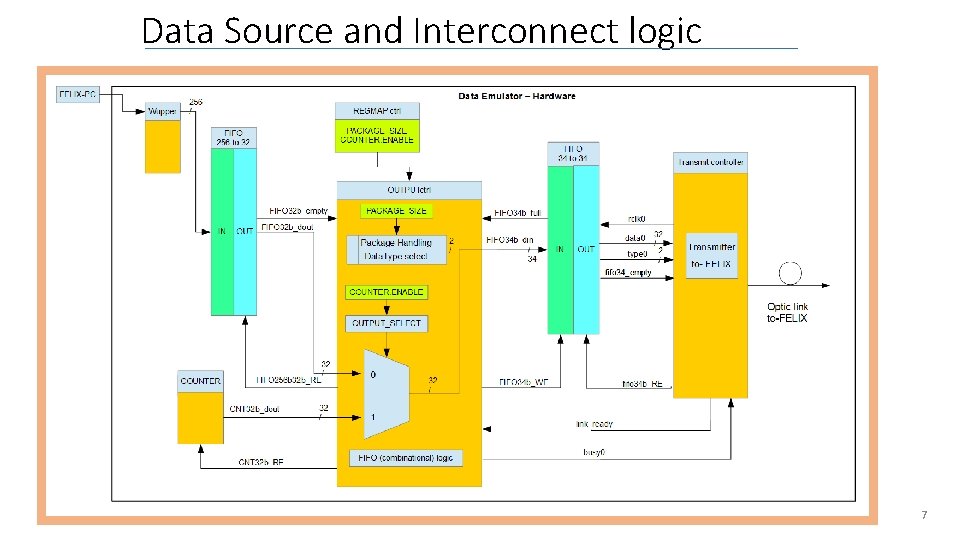

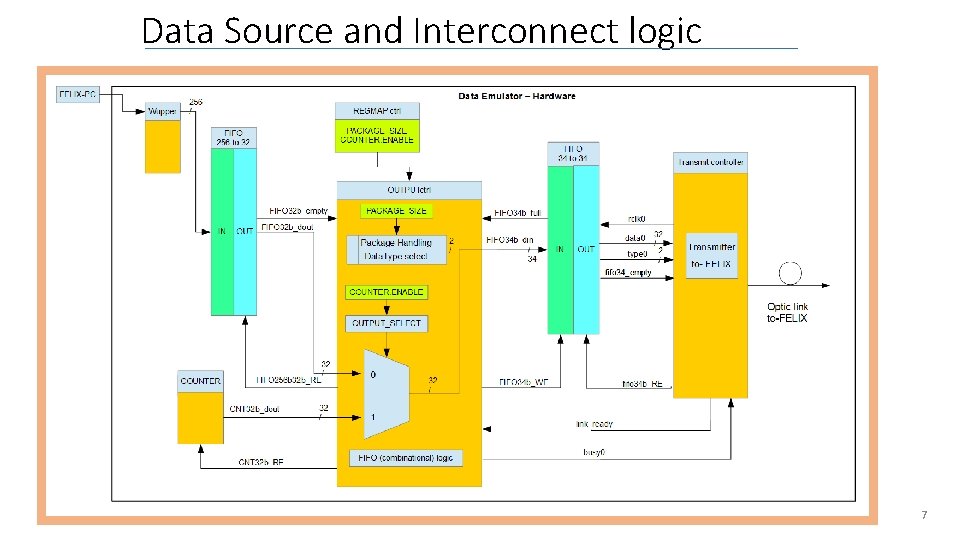

Data Source and Interconnect logic 7

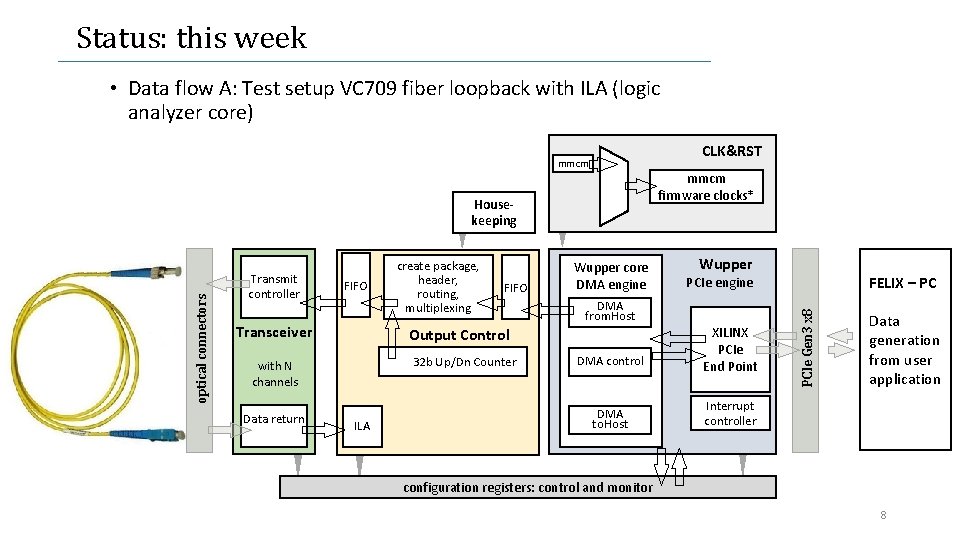

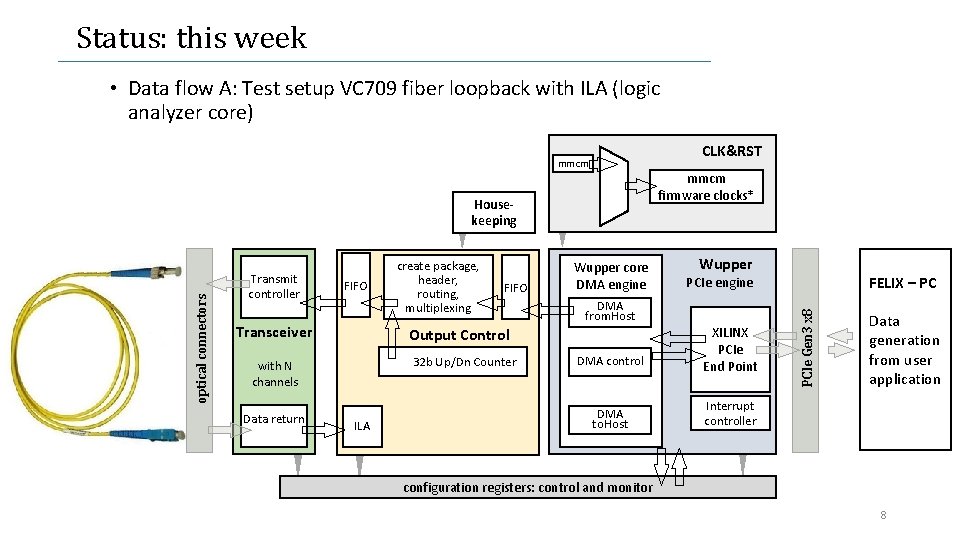

Status: this week • Data flow A: Test setup VC 709 fiber loopback with ILA (logic analyzer core) CLK&RST mmcm firmware clocks* Transmit controller FIFO Transceiver FIFO Wupper core DMA engine 32 b Up/Dn Counter ILA Wupper FELIX – PC PCIe engine DMA from. Host DMA control XILINX PCIe End Point DMA to. Host Interrupt controller Output Control with N channels Data return create package, header, routing, multiplexing PCIe Gen 3 x 8 optical connectors Housekeeping Data generation from user application configuration registers: control and monitor 8

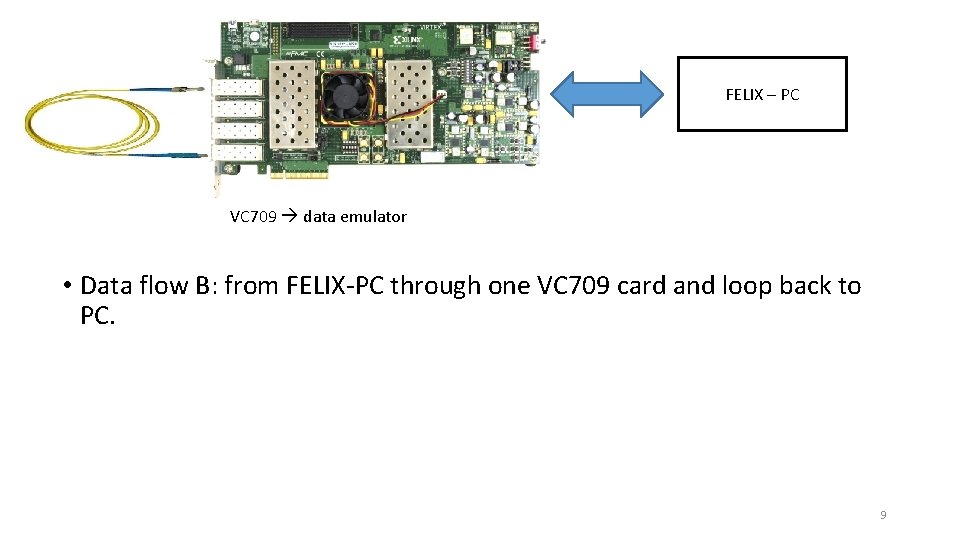

FELIX – PC VC 709 data emulator • Data flow B: from FELIX-PC through one VC 709 card and loop back to PC. 9

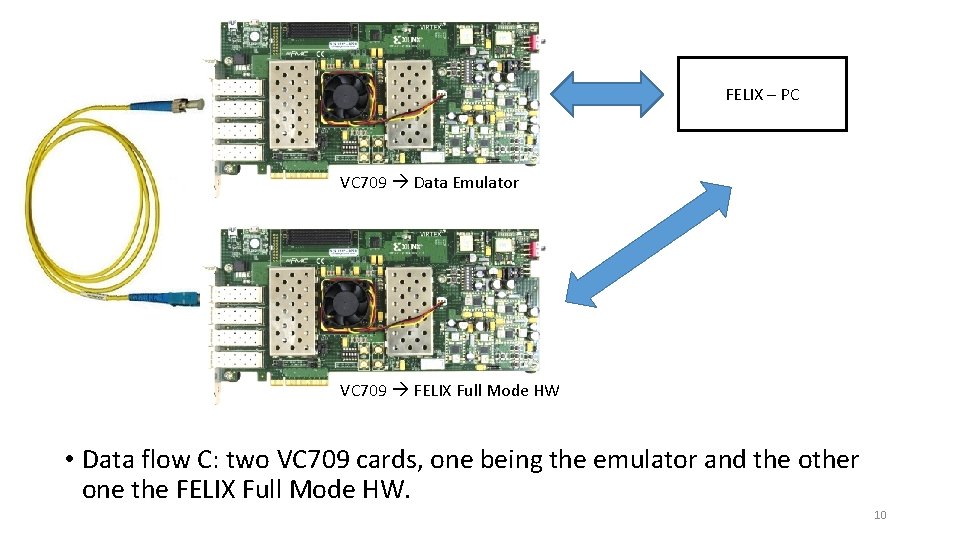

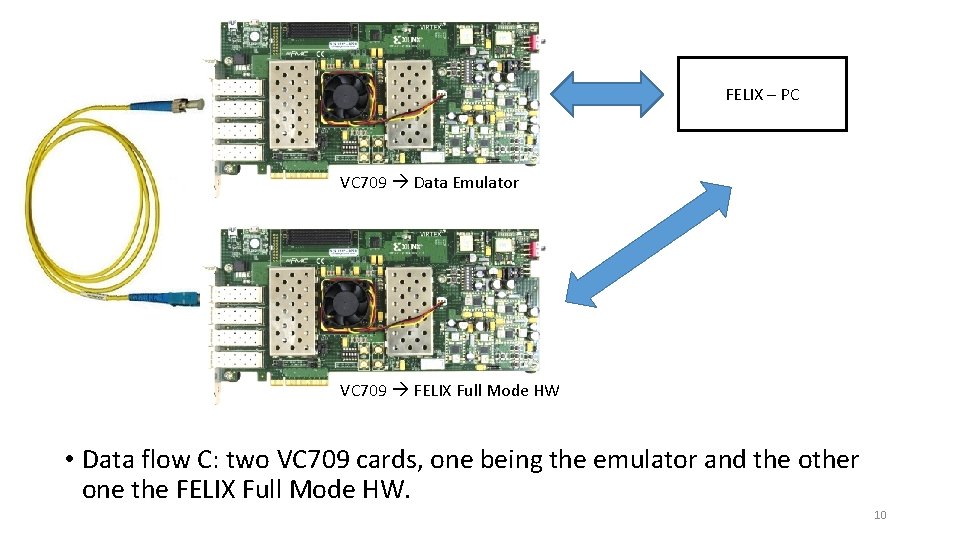

FELIX – PC VC 709 Data Emulator VC 709 FELIX Full Mode HW • Data flow C: two VC 709 cards, one being the emulator and the other one the FELIX Full Mode HW. 10

Next steps • Debug loopback with VC 709 card and the logic analyzer in FPGA • Backup the project in GIT • Adjust to multiple links and add timestamp • Data flow B: from FELIX-PC through one VC 709 card and loop back to PC. • Data flow C: two VC 709 cards, one being the emulator and one with the standard FELIX full mode HW. 11

12

• Backup sheets 13

Data type 14

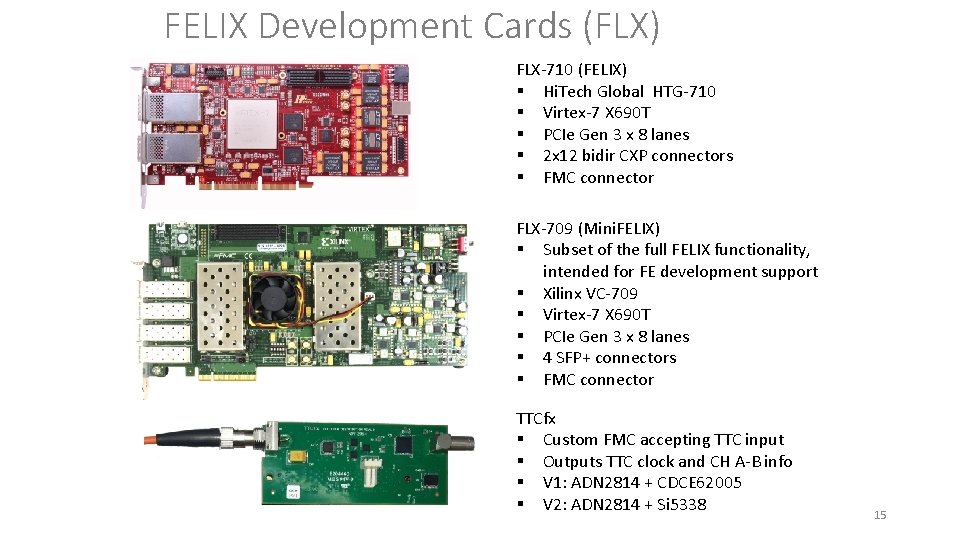

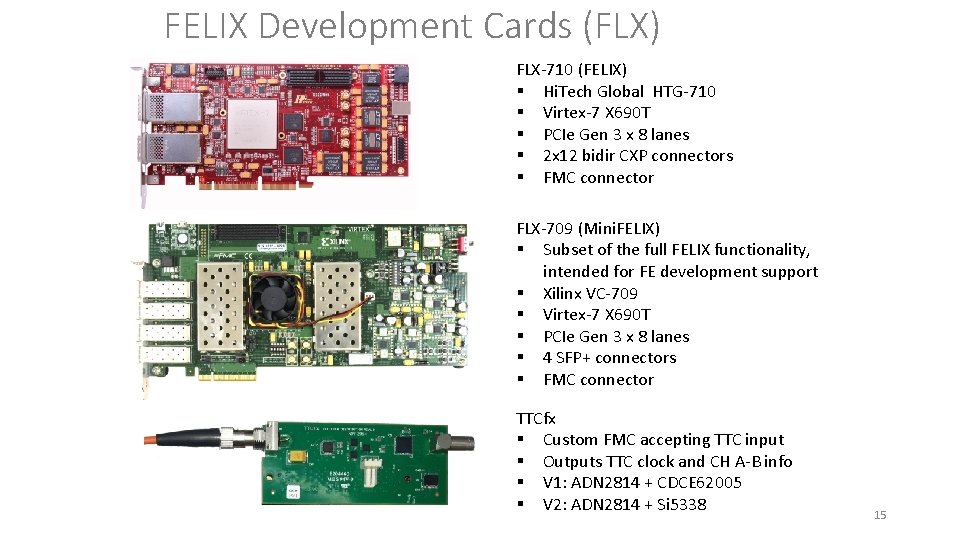

FELIX Development Cards (FLX) FLX-710 (FELIX) § Hi. Tech Global HTG-710 § Virtex-7 X 690 T § PCIe Gen 3 x 8 lanes § 2 x 12 bidir CXP connectors § FMC connector FLX-709 (Mini. FELIX) § Subset of the full FELIX functionality, intended for FE development support § Xilinx VC-709 § Virtex-7 X 690 T § PCIe Gen 3 x 8 lanes § 4 SFP+ connectors § FMC connector TTCfx § Custom FMC accepting TTC input § Outputs TTC clock and CH A-B info § V 1: ADN 2814 + CDCE 62005 § V 2: ADN 2814 + Si 5338 15

Data format Proto. Dune 16