PROSESOR SUPERSKALAR Organisasi Komputer STMIKAUB SURAKARTA What is

PROSESOR SUPERSKALAR Organisasi Komputer STMIK-AUB SURAKARTA

What is Superscalar? • Salah satu rancangan untuk meningkatkan kecepatan CPU • Instruksi umum (arithmetic, load/store, conditional branch) dapat dimulai dan dilaksanakan secara independen • Sebuah inti prosesor yang mengeksekusi dua kali/lebih operasi scalar dalam bentuk paralel. • Sebuah prosesor yang memungkinkan eksekusi yang bersamaan dari instruksi yang banyak pada tahap pipeline yang sama • Dapat diterapkan untuk RISC & CISC • Dalam praktek, biasanya RISC

Why Superscalar? • Kebanyakan operasi pada besaran skalar (satu instruksi dalam satu siklus waktu) sehingga superscalar meningkatkan operasi ini untuk mendapatkan peningkatan secara keseluruhan

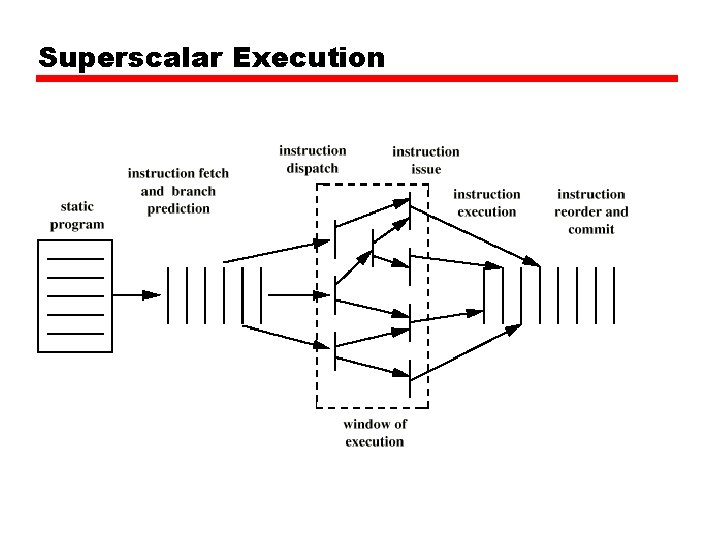

Superscalar Execution

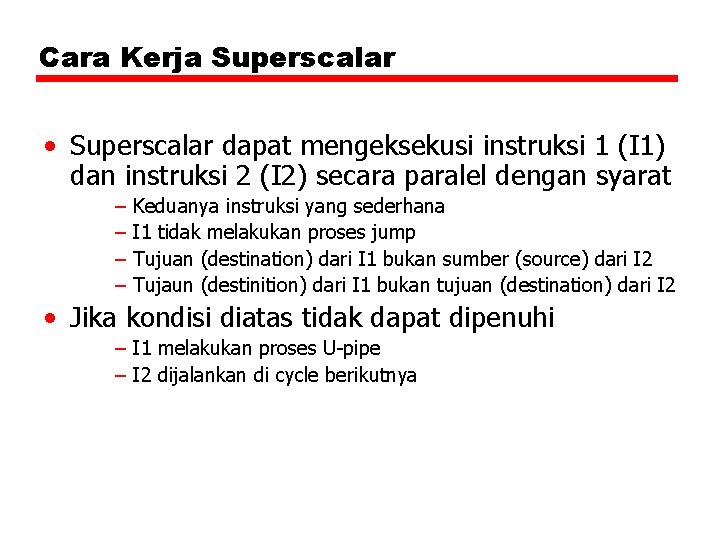

Cara Kerja Superscalar • Superscalar dapat mengeksekusi instruksi 1 (I 1) dan instruksi 2 (I 2) secara paralel dengan syarat – – Keduanya instruksi yang sederhana I 1 tidak melakukan proses jump Tujuan (destination) dari I 1 bukan sumber (source) dari I 2 Tujaun (destinition) dari I 1 bukan tujuan (destination) dari I 2 • Jika kondisi diatas tidak dapat dipenuhi – I 1 melakukan proses U-pipe – I 2 dijalankan di cycle berikutnya

Superscalar Processing • Memproses lebih dari satu instruksi per clock cycle • Sangat dimungkinkan untuk memisahkan siklus fetch and execute • Memiliki Buffers pada fase antara proses fetch and decode • Memiliki unit eksekusi yang Parallel

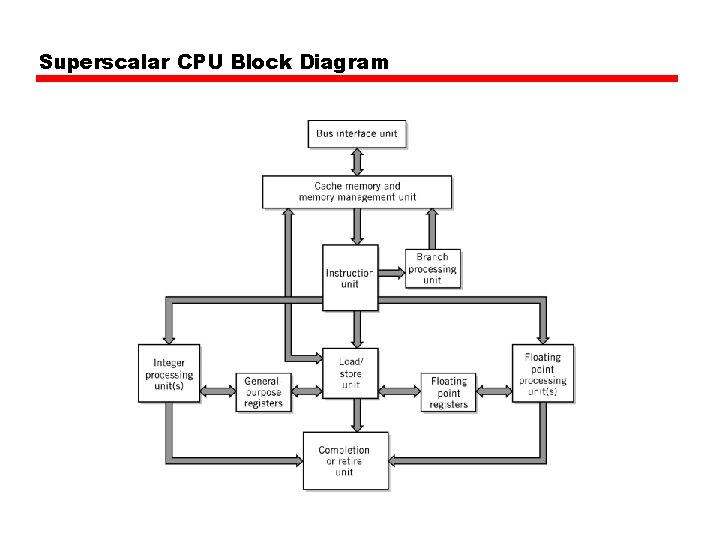

Superscalar CPU Block Diagram

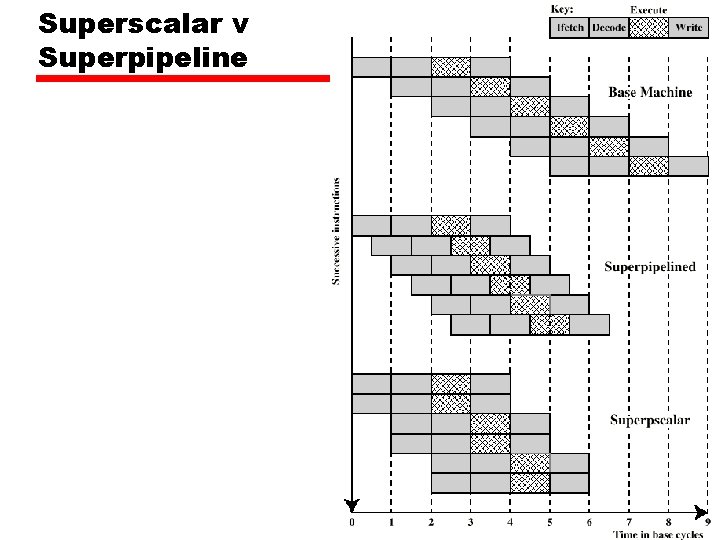

Superpipelined • Banyak tahap pipeline memerlukan waktu kurang dari setengah siklus clock • Kecepatan clock internal yang double bisa mengerjakan dua tugas per siklus clock eksternal • Superscalar memungkinkan mengambil eksekusi secara paralel

Superscalar v Superpipeline

Limitations • Instruction level parallelism (kemampuan mengeksekusi sejumlah instruksi secara paralel) • Compiler based optimisation • Hardware techniques • Dibatasi oleh —True data dependency (Ketergantungan Data Sebenarnya) —Procedural dependency (Ketergantungan Prosedural) —Resource conflicts (Konflik Sumber Daya) —Output dependency (Ketergantungan Output) —Antidependency (Antiketergantungan)

True Data Dependency • ADD r 1, r 2 (r 1 : = r 1+r 2; ) • MOVE r 3, r 1 (r 3 : = r 1; ) • Instruksi kedua dapat diambil dan didekode, namun tidak dapat dieksekusi apabila instruksi pertama belum dieksekusi. • Instruksi kedua membutuhkan data yang dihasilkan oleh instruksi pertama

Procedural Dependency • Instruksi-instruksi yang berada setelah percabangan (dilakukan ataupun tidak dilakukan) memiliki suatu ketergantungan prosedural pada percabangan dan tidak akan dieksekusi sampai percabangan tersebut dieksekusi.

Resource Conflict • Persaingan antara dua buah instruksi atau lebih untuk memperoleh sumber daya yang sama pada saat yang bersamaan. —e. g. two arithmetic instructions • Pada pipeline, dapat dilakukan duplikasi sumber daya —e. g. have two arithmetic units —Unit fungsional tertentu dipipelinekan juga

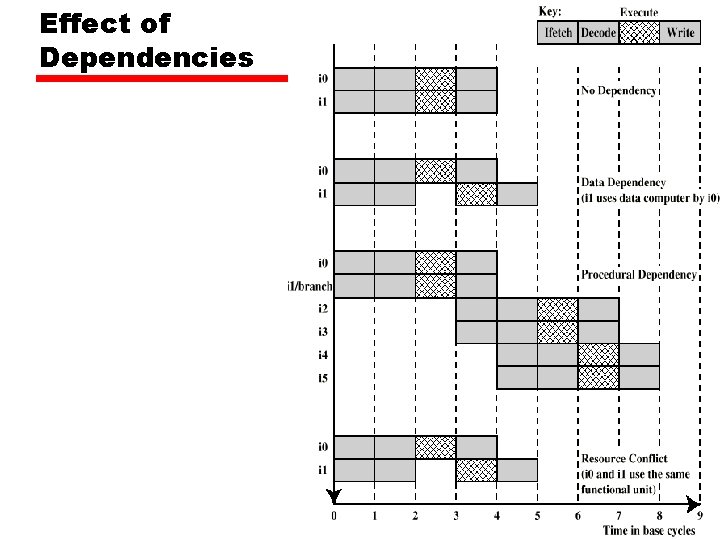

Effect of Dependencies

Persoalan Perancangan • Instruction level parallelism —Instruksi-instruksi yang terdapat pada rangkaian bersifat independen —Sehingga dapat dieksekusi secara paralel dengan cara overlapped (bertumpang tindih) —Ditentukan oleh ketergantungan data and procedural • Machine Parallelism —Kemampuan prosesor dalam memanfaatkan paralelisme tingkat instruksi —Ditentukan oleh jumlah instruksi yang dapat diambil dan dieksekusi secara bersamaan • Kedua hal di atas merupakan faktor yang penting untuk meningkatkan kinerja

Instruction Issue Policy • Bagaimana proses penginisiasian eksekusi instruksi di dalam unit-unit fungsional prosesor. • Prosesor mecoba mencari posisi di depan instruksi saat itu untuk mendapatkan instruksi yang dapat dibawa dan dapat dieksekusi. • Dalam hal ini, terdapat tiga pengurutan —Urutan diambilnya instruksi —Urutan dieksekusinya instruksi. —Urutan pertukaran register dan lokasi memori dari instruksi

In-Order Issue In-Order Completion • Menerbitkan instruksi dalam urutan pasti yang akan diperoleh eksekusi sekuensial (inorder-issue) dan dengan menuliskan hasilnya dengan urutan yang sama (in-order-completion) • Tidak begitu efisien • May fetch >1 instruction

In-Order Issue Out-of-Order Completion • Prosesor akan mendekode instruksi hingga dijumpai ketergantungan atau konflik. • Tidak akan ada instruksi lainnya yang akan didekode sampai konflik diatasi. • Output dependency —R 3: = R 3 + R 5; (I 1) —R 4: = R 3 + 1; (I 2) —R 3: = R 5 + 1; (I 3) —I 2 depends on result of I 1 - data dependency —If I 3 completes before I 1, the result from I 1 will be wrong - output (read-write) dependency

Out-of-Order Issue Out-of-Order Completion • Decouple tahapan-tahapan dekode dan eksekusi pipeline, dengan cara menggunakan buffer yang dianggap sebagai jendela instuksi. • Setelah prosesor menyelesaikan pendekodean instruksi, maka instruksi tersebut ditempatkan di dalam jendela instruksi. • Selama buffer belum penuh, prosesor dapat mengambil instruksi dan mendekode instruksi lainnya. • Apabila pada tahapan eksekusi tersedia unit fungsional, maka instruksi yang berasal dari jendela instruksi dapat dikirimkan ke tahapan eksekusi. • Sebuah instruksi dapat dikirimkan dengan syarat — Instruksi memerlukan unit fungsinal yang tersedia — Tidak terjadi konflik atau ketergantungan yang memblokir instuksi tersebut.

Antidependency • Contoh konflik penyimpanan • Write-write dependency —R 3: =R 3 + R 5; (I 1) —R 4: =R 3 + 1; (I 2) —R 3: =R 5 + 1; (I 3) —R 7: =R 3 + R 4; (I 4) —I 3 can not complete before I 2 starts as I 2 needs a value in R 3 and I 3 changes R 3 • Kebalikan dari Ketergantungan data sebenarnya(instruksi pertama menghasilkan nilai yang akan digunakan instruksi kedua), melainkan instruksi kedua memusnahkan nilai yang akan digunakan instruksi pertama

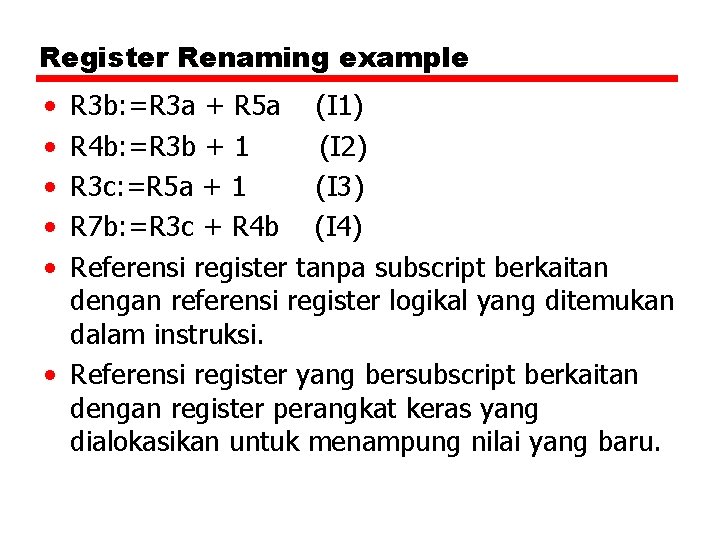

Register Renaming • Output dan antidepedency muncul karena nilai dalam register tidak dapat lagi merefleksikan nilai-nilai yang ditentukan oleh aliran program. • Registers allocated dynamically —registers are not specifically named, pada saat nilai register yang baru dibuat, maka sebuah register akan dialokasikan bagi nilai tersebut.

Register Renaming example • • • R 3 b: =R 3 a + R 5 a (I 1) R 4 b: =R 3 b + 1 (I 2) R 3 c: =R 5 a + 1 (I 3) R 7 b: =R 3 c + R 4 b (I 4) Referensi register tanpa subscript berkaitan dengan referensi register logikal yang ditemukan dalam instruksi. • Referensi register yang bersubscript berkaitan dengan register perangkat keras yang dialokasikan untuk menampung nilai yang baru.

Machine Parallelism • Tiga teknik perangkat keras untuk meningkatkan kinerja : —Duplication of Resources —Out of order issue —Renaming • Not worth duplication functions without register renaming • Need instruction window large enough (more than 8), apabila jendela instruksi terlalu kecil, maka ketergantungan data akan menghambat kerja unit-unit fungsional

Teknik dalam Superscalar • Teknik yang dapat dilakukan dengan metode superscalar ini adalah dalam hal memperkirakan pencabangan instruksi (brach prediction) serta perkiraan eksekusi perintah (speculative execution). • Peristiwa ini sangat menguntungkan untuk program yang membutuhkan pencabangan dari kelompok instruksi yang dijalankannya.

Branch Prediction • Program yang terdiri dari kelompok perintah bercabang sering digunakan dalam pemrograman. • Pada CPU yang mendukung perintah pencabangan, CPU membutuhkan cukup banyak clock cycle, mengingat CPU menempatkan semuanya pada pipeline dan menemukan perintah berikutnya yang akan dieksekusinya. • Sirkuit untuk branch prediction melakukan pekerjaan ini bekerja sama dengan pipeline, yang dilakukan sebelum proses di ALU dilaksanakan, dan memperkirakan hasil dari pencabangan tersebut. • Jika CPU berfikir bahwa branch akan menuju suatu cabang, biasanya berdasarkan pekerjaan sebelumnya, maka perintah berikutnya sudah dipersiapkan untuk dieksekusi berikut data -datanya, bahkan dengan adanya pipeline ini, bila tidak diperlukan suatu referensi dari instruksi terakhir, maka bisa dilaksanakan dengan segera, karena data dan instruksi yang dibutuhkan telah dipersiapkan sebelumnya. .

Speculative Execution • CPU akan menggunakan melakukan perhitungan pada pipeline yang berbeda berdasarkan kemungkinan yang diperkirakan oleh komputer. — Jika kemungkinan yang dilakukan oleh komputer tepat, maka hasilnya sudah bisa diambil langsung dan tinggal melanjutkan perintah berikutnya — Jika kemungkinan yang diperkirakan oleh komputer tidak tepat, maka akan dilaksanakan kemungkinan lain sesuai dengan logika instruksi tersebut.

Extra Transistor • Teknik yang digunakan pipeline dan superscalar untuk melakukan branch prediction dan speculative execution membutuhkan ekstra transistor untuk hal tersebut. • Sebagai perbandingan, — komputer yang membangkitkan pemrosesan pada PC pertama yang dikeluarkan oleh IBM pada mesin 8088 memiliki sekitar 29. 000 transistor. — Sedangkan pada mesin Pentium III, dengan teknologi superscalar dan superpipeline, mendukung branch prediction, speculative execution serta berbagai kemampuan lainnya memiliki sekitar 7, 5 juta transistor. Beberapa CPU lainnya seperti HP 8500 memiliki sekitar 140 juta transistor.

Pengguna Superscalar • Prosesor Intel x 86 yang menggunakan arsitektur superskalar adalah keluarga Intel Pentium, Intel Pentium Pro, Intel Pentium III, Intel Itanium, Intel Xeon, Intel Pentium 4, Intel Pentium M, Intel Core dari Intel Corporation; • Keluarga AMD K 5, AMD K 6, AMD Athlon 64, dan AMD Opteron.

Processor superscalar Processor board of a CRAY T 3 e parallel computer with four superscalar Alpha processors

- Slides: 29