Proposal of CSP based Network Design and Construction

Proposal of CSP based Network Design and Construction Kazuto Tanaka , Satoshi Iwanami , Takeshi Yamakawa, Chikara Fukunaga(Tokyo Metropolitan University) Kazuto Matsui(Prominent Network inc. ) Takashi Yoshida(Smart Scape inc. ) 5. nov. 2008 k. tanaka Sp. W Conf. at Nara 1

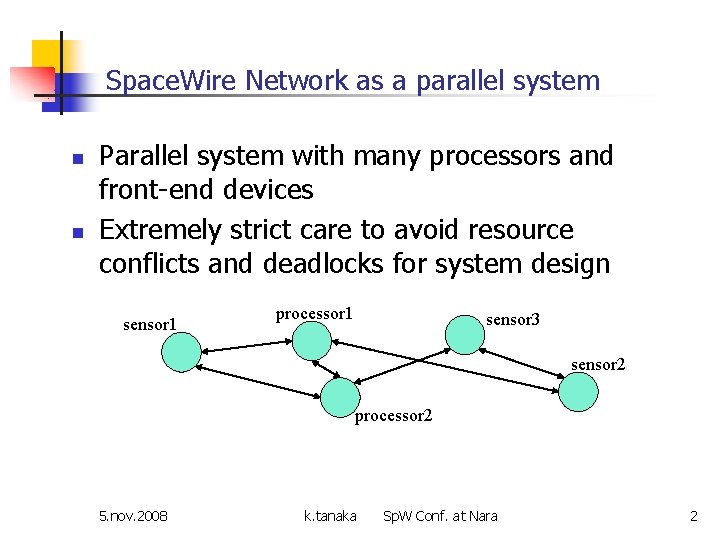

Space. Wire Network as a parallel system n n Parallel system with many processors and front-end devices Extremely strict care to avoid resource conflicts and deadlocks for system design sensor 1 processor 1 sensor 3 sensor 2 processor 2 5. nov. 2008 k. tanaka Sp. W Conf. at Nara 2

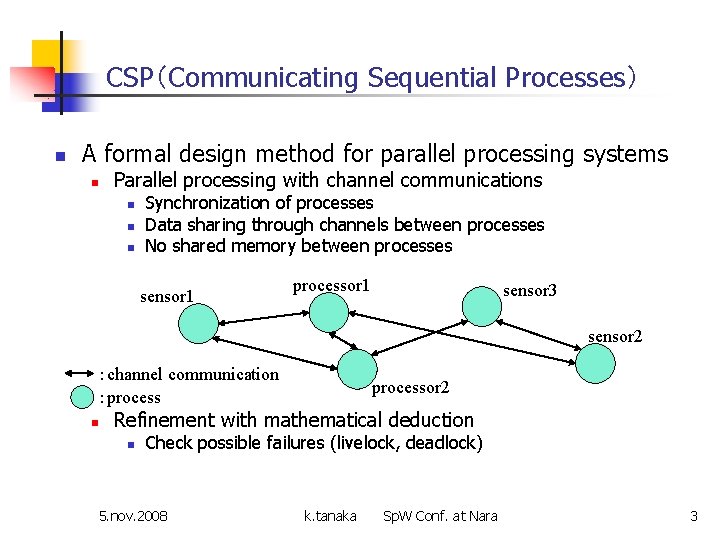

CSP(Communicating Sequential Processes) n A formal design method for parallel processing systems n Parallel processing with channel communications n n n Synchronization of processes Data sharing through channels between processes No shared memory between processes sensor 1 processor 1 sensor 3 sensor 2 :channel communication :process n processor 2 Refinement with mathematical deduction n Check possible failures (livelock, deadlock) 5. nov. 2008 k. tanaka Sp. W Conf. at Nara 3

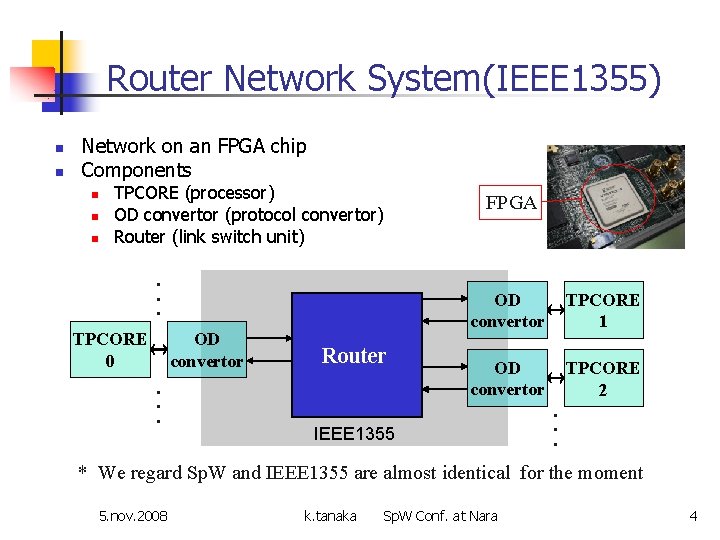

Router Network System(IEEE 1355) n n Network on an FPGA chip Components n n n TPCORE (processor) OD convertor (protocol convertor) Router (link switch unit) ・ ・ ・ OD convertor TPCORE 0 ・ ・ ・ Router FPGA OD convertor TPCORE 1 OD convertor TPCORE 2 IEEE 1355 ・ ・ ・ * We regard Sp. W and IEEE 1355 are almost identical for the moment 5. nov. 2008 k. tanaka Sp. W Conf. at Nara 4

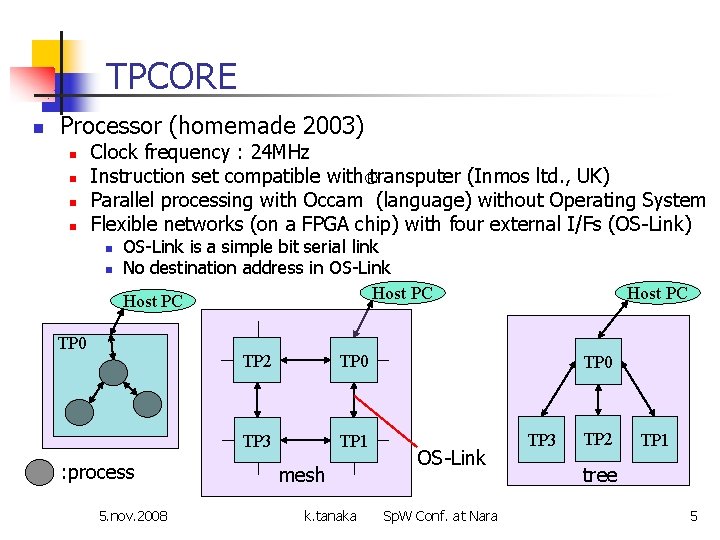

TPCORE n Processor (homemade 2003) n n Clock frequency : 24 MHz Instruction set compatible with Rtransputer (Inmos ltd. , UK) Parallel processing with Occam (language) without Operating System Flexible networks (on a FPGA chip) with four external I/Fs (OS-Link) n n OS-Link is a simple bit serial link No destination address in OS-Link Host PC TP 0 : process 5. nov. 2008 TP 2 TP 0 TP 3 TP 1 mesh k. tanaka Host PC TP 0 OS-Link Sp. W Conf. at Nara TP 3 TP 2 TP 1 tree 5

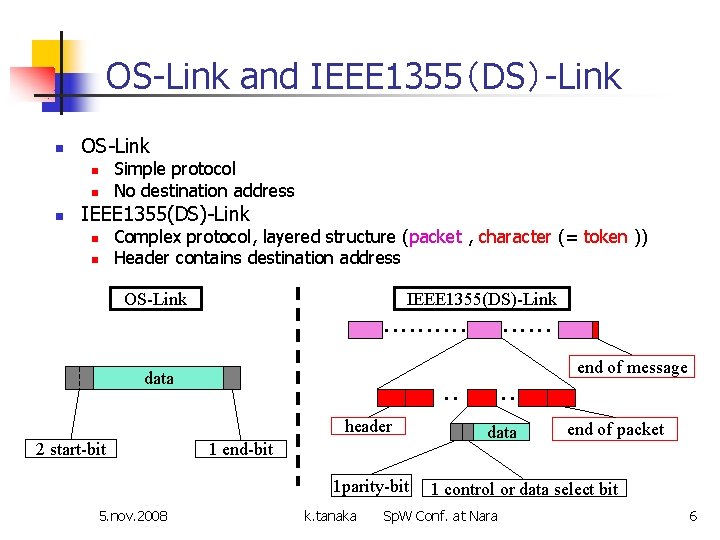

OS-Link and IEEE 1355(DS)-Link n OS-Link n n n Simple protocol No destination address IEEE 1355(DS)-Link n n Complex protocol, layered structure (packet , character (= token )) Header contains destination address IEEE 1355(DS)-Link OS-Link ・・・・・・ end of message data ・・ header 2 start-bit 1 end-bit 1 parity-bit 5. nov. 2008 k. tanaka ・・ data end of packet 1 control or data select bit Sp. W Conf. at Nara 6

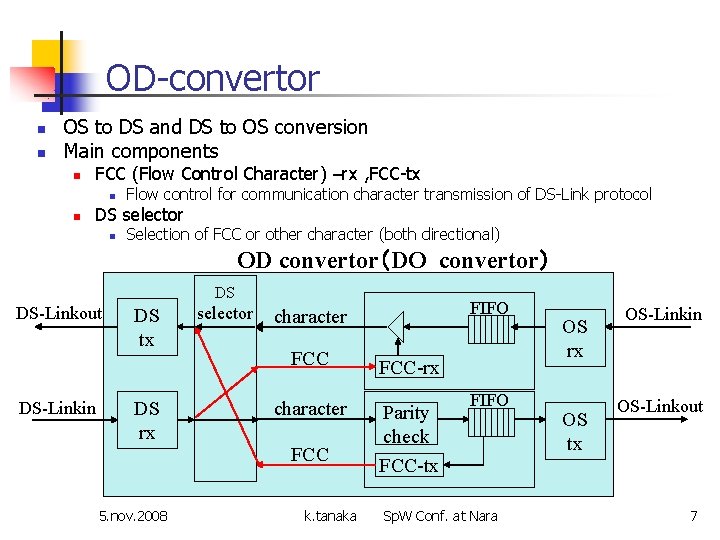

OD-convertor n n OS to DS and DS to OS conversion Main components n FCC (Flow Control Character) –rx , FCC-tx n n Flow control for communication character transmission of DS-Link protocol DS selector n Selection of FCC or other character (both directional) OD convertor(DO convertor) DS DS-Linkout DS-Linkin DS tx DS rx 5. nov. 2008 selector FIFO character FCC-rx character Parity check FCC-tx FCC k. tanaka FIFO Sp. W Conf. at Nara OS rx OS tx OS-Linkin OS-Linkout 7

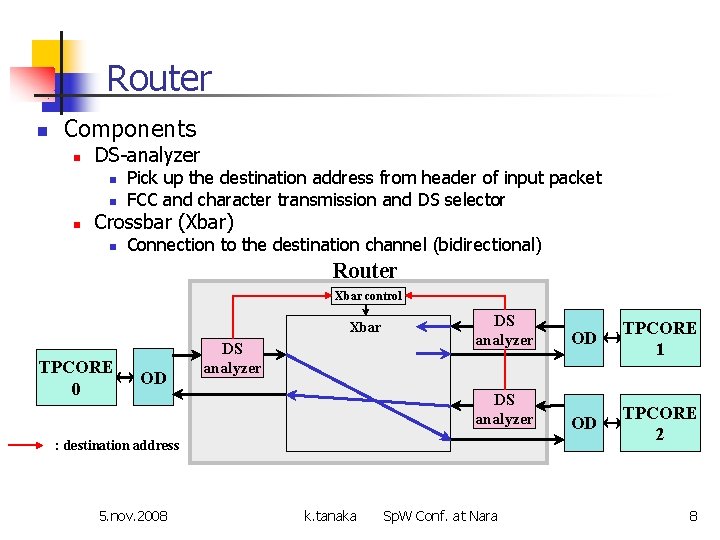

Router n Components n DS-analyzer n n n Pick up the destination address from header of input packet FCC and character transmission and DS selector Crossbar (Xbar) n Connection to the destination channel (bidirectional) Router Xbar control Xbar TPCORE 0 OD DS analyzer OD TPCORE 1 DS analyzer OD TPCORE 2 : destination address 5. nov. 2008 k. tanaka Sp. W Conf. at Nara 8

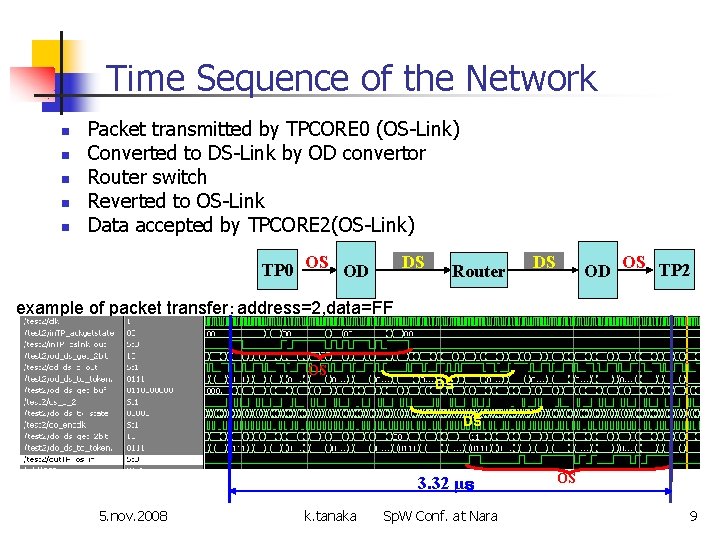

Time Sequence of the Network n n n Packet transmitted by TPCORE 0 (OS-Link) Converted to DS-Link by OD convertor Router switch Reverted to OS-Link Data accepted by TPCORE 2(OS-Link) TP 0 OS OD DS Router OD OS TP 2 DS example of packet transfer:address=2, data=FF OS DS DS 3. 32 μs 5. nov. 2008 k. tanaka Sp. W Conf. at Nara OS 9

Summary n Network-Router and OD convertor (IEEE 1355) have been designed based on CSP. n n n By refinement checking , We find no deadlock , no livelock in these devices as a parallel system. Detailed discussion of CSP will be found in our another presentation (Poster). Correct data communication has been confirmed using TPCOREs. We measured DS-Link transfer rate. It is 20. 29 Mbps. Theoretical value is 20. 28 Mbps. n The difference is less than a clock width (48 MHz). n The good agreement has been achieved. From this study, we found CSP as a good design method for parallel systems. Thank you for your attention !! 5. nov. 2008 k. tanaka Sp. W Conf. at Nara 10

- Slides: 10