Proposal for the Bit Grouping Scheme for Convoluational

Proposal for the Bit Grouping Scheme for Convoluational Turbo Code Document Number: IEEE C 802. 16 m-09/0992 Date Submitted: 2009 -04 -27 Source: Ciou. Ping Wu (ciouping. wu@mediatek. com), Peikai Liao (pk. liao@mediatek. com), Yu-Hao Chang (yuhao. chang@mediatek. com), Yih-Shen Chen (yihshen. chen@mediatek. com) and Paul Cheng (paul. cheng@mediatek. com) Media. Tek Inc. No. 1 Dusing Rd. 1 Hsinchu Science Park Hsinchu City 300 Taiwan. Venue: Category: AWD comments / Area: Chapter 15. 3. 12 (Channel coding HARQ-PHY) “Comments on AWD 15. 3. 12 Channel Coding and HARQ” Base Contribution: This is base contribution. Purpose: Propose to be discussed and adopted by TGm for the use in Project 802. 16 m. Notice: This document does not represent the agreed views of the IEEE 802. 16 Working Group or any of its subgroups. It represents only the views of the participants listed in the “Source(s)” field above. It is offered as a basis for discussion. It is not binding on the contributor(s), who reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor grants a free, irrevocable license to the IEEE to incorporate material contained in this contribution, and any modifications thereof, in the creation of an IEEE Standards publication; to copyright in the IEEE’s name any IEEE Standards publication even though it may include portions of this contribution; and at the IEEE’s sole discretion to permit others to reproduce in whole or in part the resulting IEEE Standards publication. The contributor also acknowledges and accepts that this contribution may be made public by IEEE 802. 16. Patent Policy: The contributor is familiar with the IEEE-SA Patent Policy and Procedures: <http: //standards. ieee. org/guides/bylaws/sect 6 -7. html#6> and <http: //standards. ieee. org/guides/opman/sect 6. html#6. 3>. Further information is located at <http: //standards. ieee. org/board/pat-material. html> and <http: //standards. ieee. org/board/pat >.

Introduction • • Issues with IEEE 802. 16 e subblock interleaver for CTC: – Since the subblocks are interleaved by the same interleaving equation, the input bits of the CTC decoder may be mapped onto the same bit level at each decoding stage. è Coding performance loss Circular shift bit grouping is applied to avoid mapping the coded bits with the same index onto the same bit level in 16 QAM and 64 QAM.

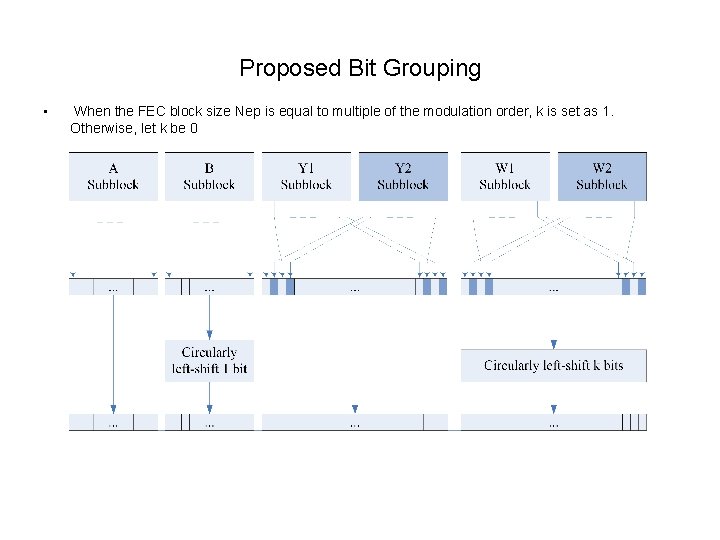

Proposed Bit Grouping • When the FEC block size Nep is equal to multiple of the modulation order, k is set as 1. Otherwise, let k be 0

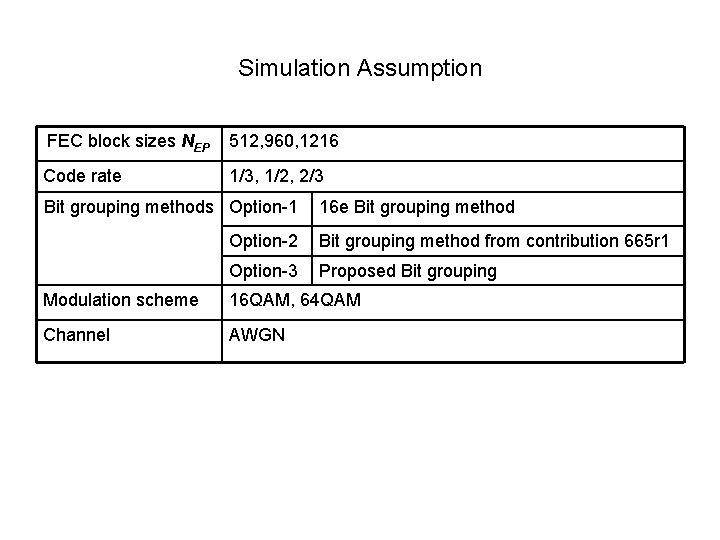

Simulation Assumption FEC block sizes NEP 512, 960, 1216 Code rate 1/3, 1/2, 2/3 Bit grouping methods Option-1 16 e Bit grouping method Option-2 Bit grouping method from contribution 665 r 1 Option-3 Proposed Bit grouping Modulation scheme 16 QAM, 64 QAM Channel AWGN

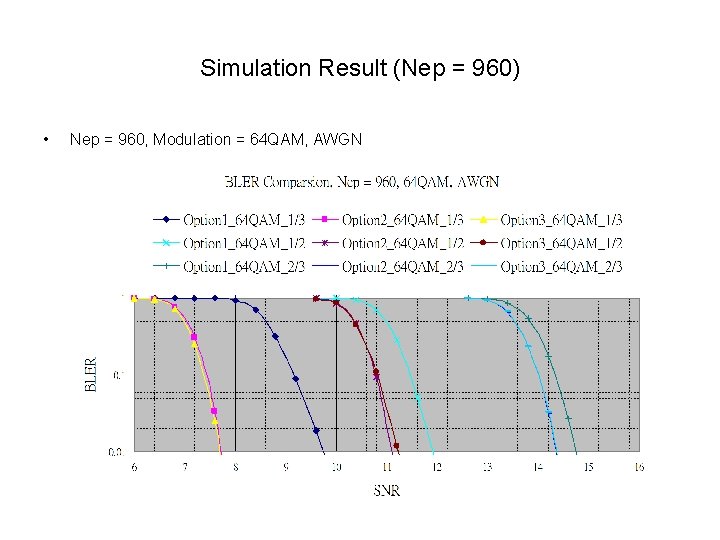

Simulation Result (Nep = 960) • Nep = 960, Modulation = 64 QAM, AWGN

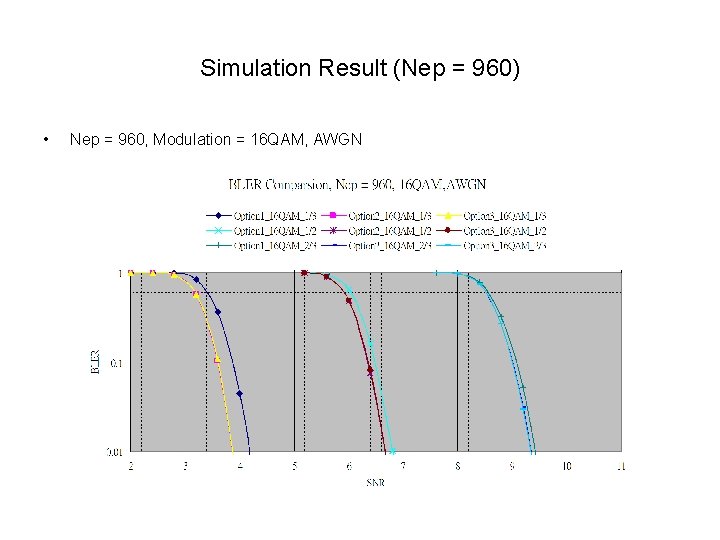

Simulation Result (Nep = 960) • Nep = 960, Modulation = 16 QAM, AWGN

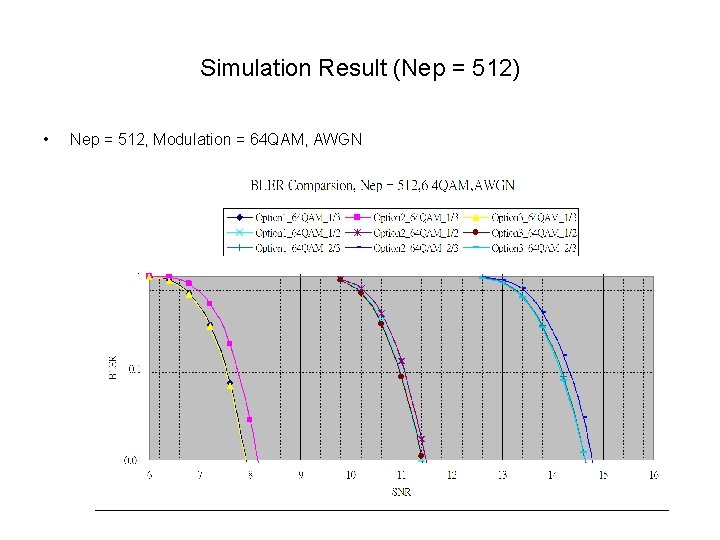

Simulation Result (Nep = 512) • Nep = 512, Modulation = 64 QAM, AWGN

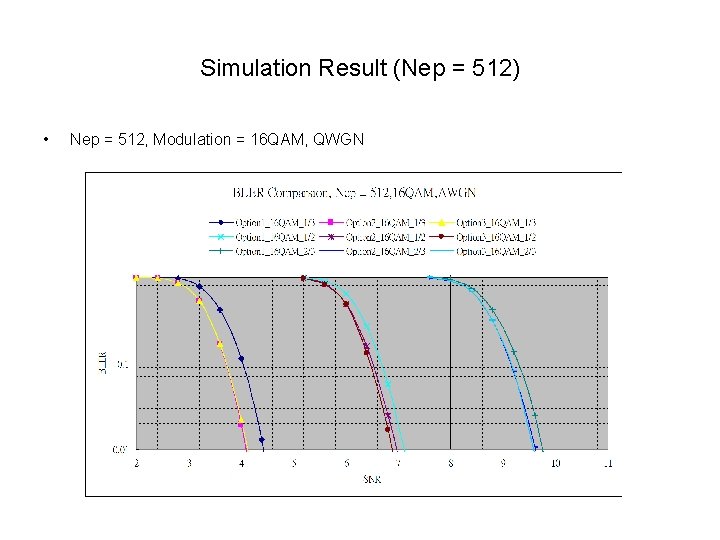

Simulation Result (Nep = 512) • Nep = 512, Modulation = 16 QAM, QWGN

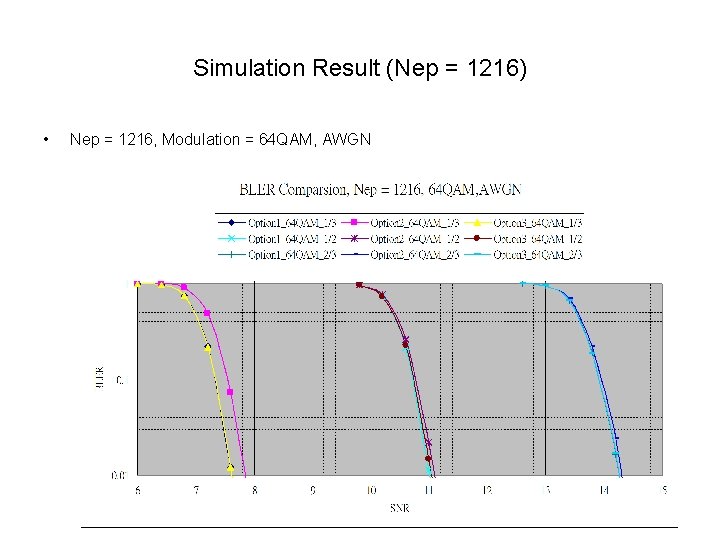

Simulation Result (Nep = 1216) • Nep = 1216, Modulation = 64 QAM, AWGN

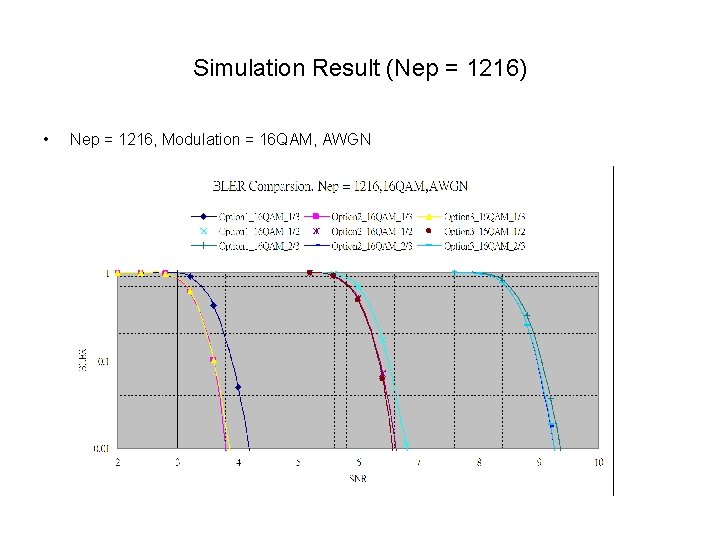

Simulation Result (Nep = 1216) • Nep = 1216, Modulation = 16 QAM, AWGN

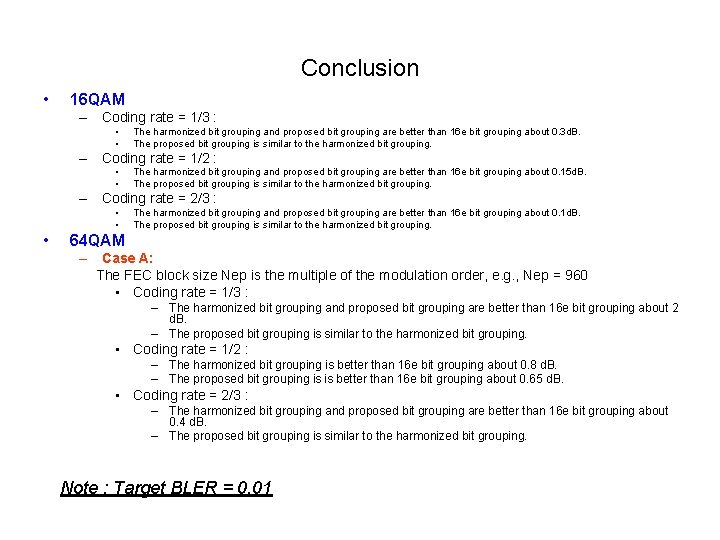

Conclusion • 16 QAM – Coding rate = 1/3 : • • The harmonized bit grouping and proposed bit grouping are better than 16 e bit grouping about 0. 3 d. B. The proposed bit grouping is similar to the harmonized bit grouping. – Coding rate = 1/2 : • • The harmonized bit grouping and proposed bit grouping are better than 16 e bit grouping about 0. 15 d. B. The proposed bit grouping is similar to the harmonized bit grouping. – Coding rate = 2/3 : • • • The harmonized bit grouping and proposed bit grouping are better than 16 e bit grouping about 0. 1 d. B. The proposed bit grouping is similar to the harmonized bit grouping. 64 QAM – Case A: The FEC block size Nep is the multiple of the modulation order, e. g. , Nep = 960 • Coding rate = 1/3 : – The harmonized bit grouping and proposed bit grouping are better than 16 e bit grouping about 2 d. B. – The proposed bit grouping is similar to the harmonized bit grouping. • Coding rate = 1/2 : – The harmonized bit grouping is better than 16 e bit grouping about 0. 8 d. B. – The proposed bit grouping is is better than 16 e bit grouping about 0. 65 d. B. • Coding rate = 2/3 : – The harmonized bit grouping and proposed bit grouping are better than 16 e bit grouping about 0. 4 d. B. – The proposed bit grouping is similar to the harmonized bit grouping. Note : Target BLER = 0. 01

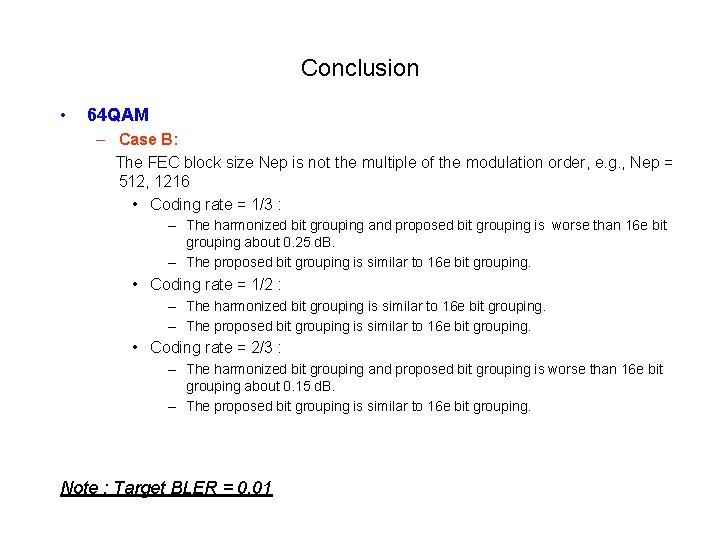

Conclusion • 64 QAM – Case B: The FEC block size Nep is not the multiple of the modulation order, e. g. , Nep = 512, 1216 • Coding rate = 1/3 : – The harmonized bit grouping and proposed bit grouping is worse than 16 e bit grouping about 0. 25 d. B. – The proposed bit grouping is similar to 16 e bit grouping. • Coding rate = 1/2 : – The harmonized bit grouping is similar to 16 e bit grouping. – The proposed bit grouping is similar to 16 e bit grouping. • Coding rate = 2/3 : – The harmonized bit grouping and proposed bit grouping is worse than 16 e bit grouping about 0. 15 d. B. – The proposed bit grouping is similar to 16 e bit grouping. Note : Target BLER = 0. 01

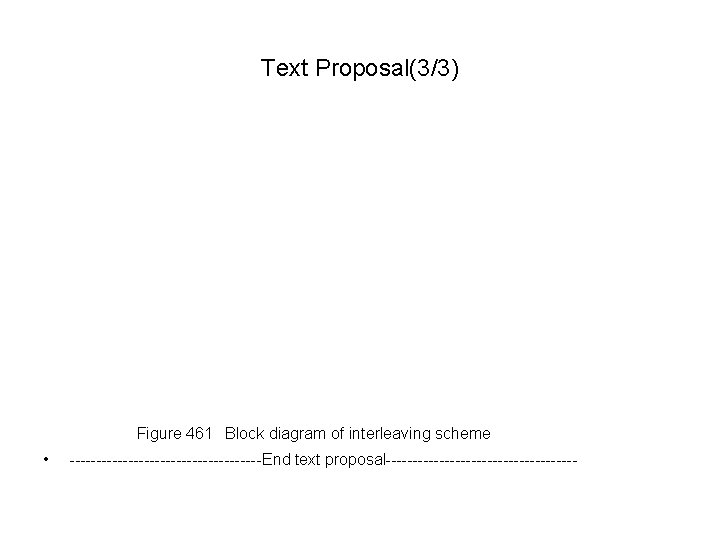

Text Proposal(1/3) • ------------------Start text proposal------------------ • Bit Grouping Corresponding to section <<8. 4. 9. 2. 3. 4. 3>> The interleaved subblocks shall be multiplexed into four blocks; those four blocks consist of an interleaved A subblock, an interleaved B subblock, a bit-by-bit multiplexed sequence of the interleaved Y 1 and Y 2 subblock sequences, which is referred to Y, and a bit-by-bit multiplexed sequence of the interleaved W 1 and W 2 subblock sequences, which is referred to W. Information subblocks, A and B, are bypassed while parity subblocks are multiplexed bit by bit. The bit-by-bit multiplexed sequence of interleaved Y 1 and Y 2 subblock sequences shall consist of the first output bit from the Y 1 subblock interleaver, the first output bit from the Y 2 subblock interleaver, the second output bit from the Y 1 subblock interleaver, the second output bit from the Y 2 subblock interleaver, etc. The bit-by-bit multiplexed sequence of interleaved W 1 and W 2 subblock sequences shall consist of the first output bit from the W 1 subblock interleaver, the first output bit from the W 2 subblock interleaver, the second output bit from the W 1 subblock interleaver, the second output bit from the W 2 subblock interleaver, etc.

Text Proposal(2/3) After multiplexing subblocks into four blocks, Subblock B is circularly left-shifted by 1 bit. The multiplexed subblock W is circularly left-shifted by k bits. When the FEC block size Nep is equal to multiple of the modulation order, k is set as 1. Otherwise, let k be 0. Figure 461 shows interleaving scheme as explained above.

Text Proposal(3/3) Figure 461 Block diagram of interleaving scheme • ------------------End text proposal------------------

- Slides: 15