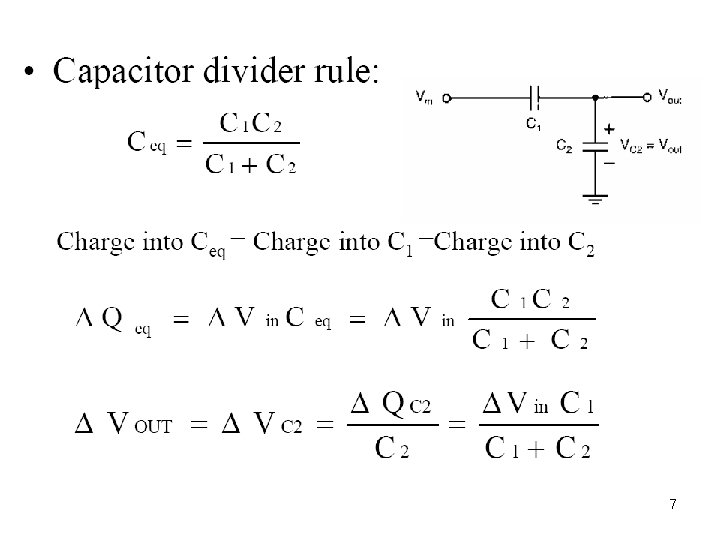

Propagation Time Delay Rising propagation delay time Propagation

- Slides: 26

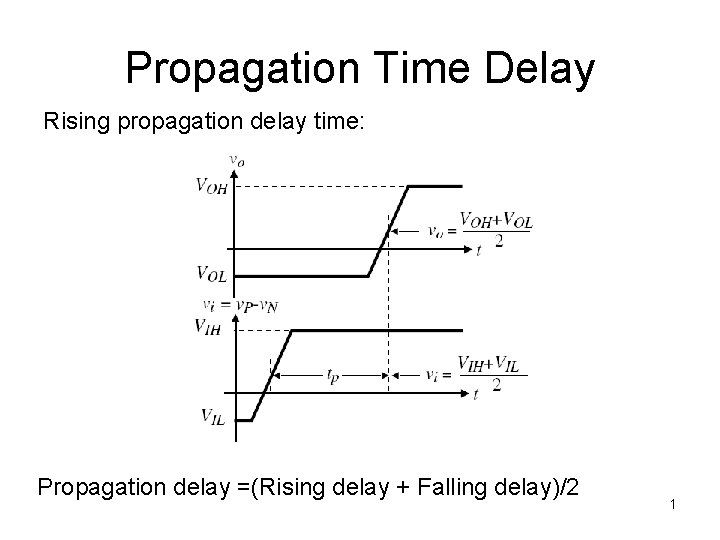

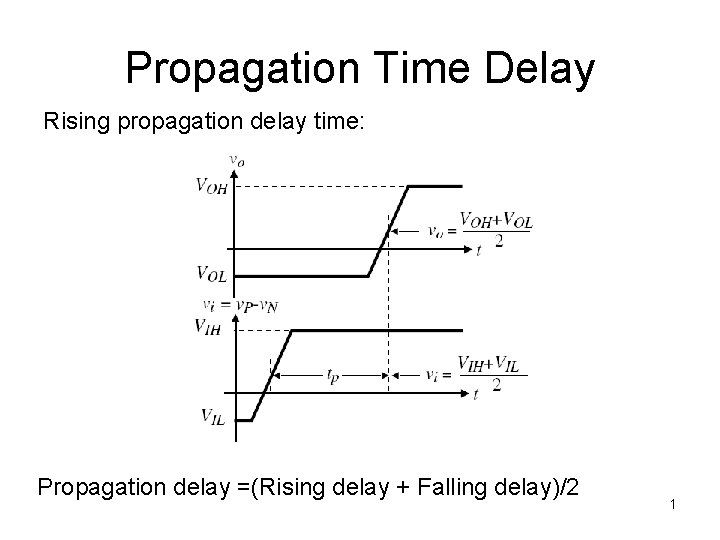

Propagation Time Delay Rising propagation delay time: Propagation delay =(Rising delay + Falling delay)/2 1

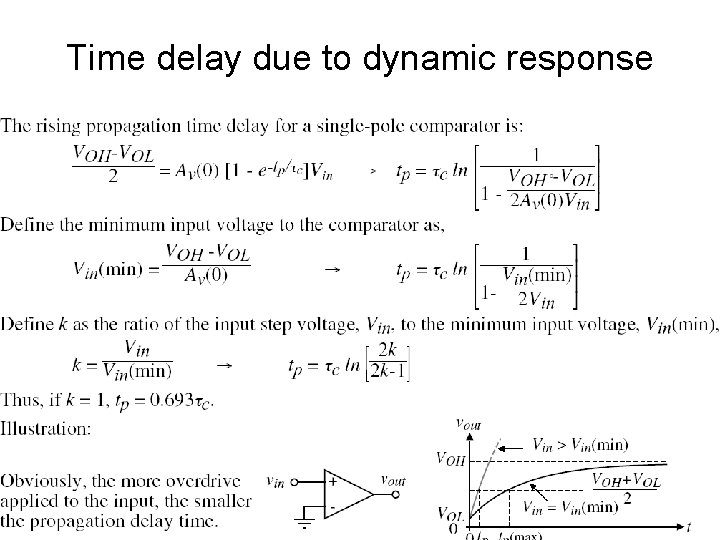

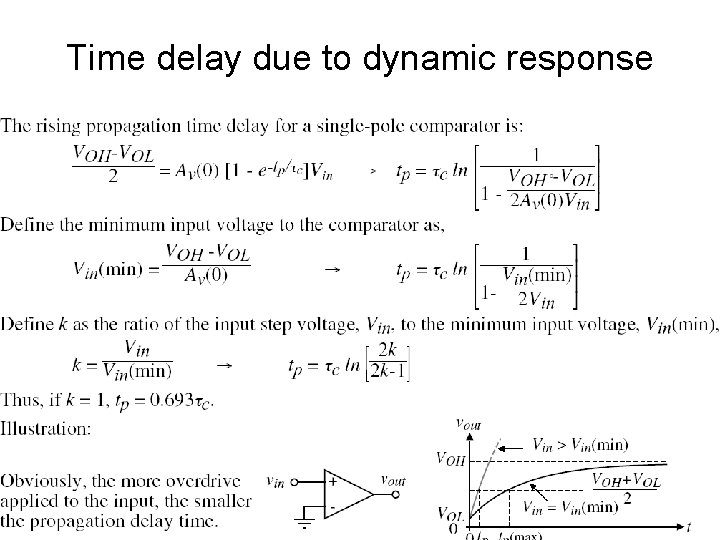

Time delay due to dynamic response 2

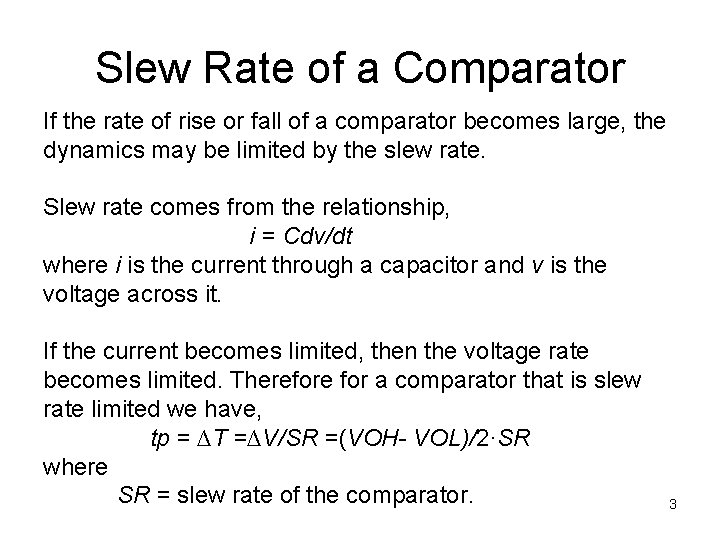

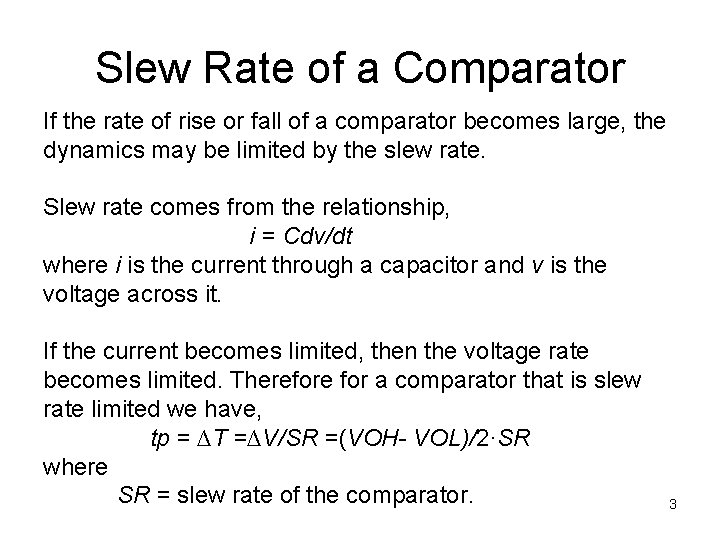

Slew Rate of a Comparator If the rate of rise or fall of a comparator becomes large, the dynamics may be limited by the slew rate. Slew rate comes from the relationship, i = Cdv/dt where i is the current through a capacitor and v is the voltage across it. If the current becomes limited, then the voltage rate becomes limited. Therefore for a comparator that is slew rate limited we have, tp = ∆T =∆V/SR =(VOH- VOL)/2·SR where SR = slew rate of the comparator. 3

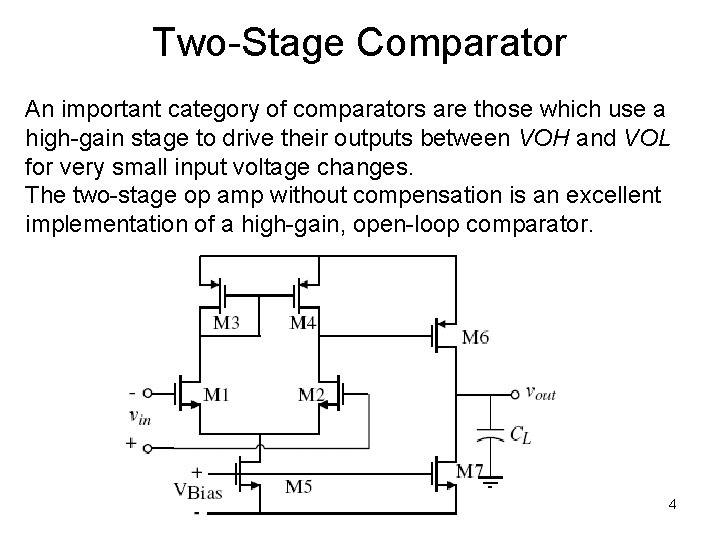

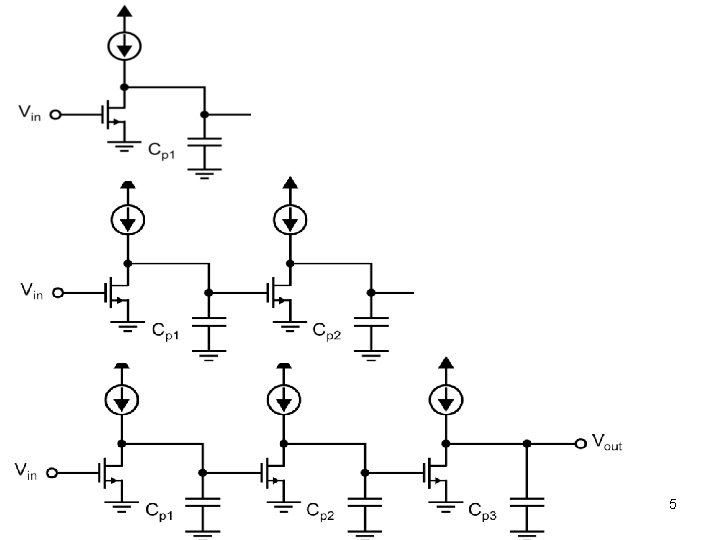

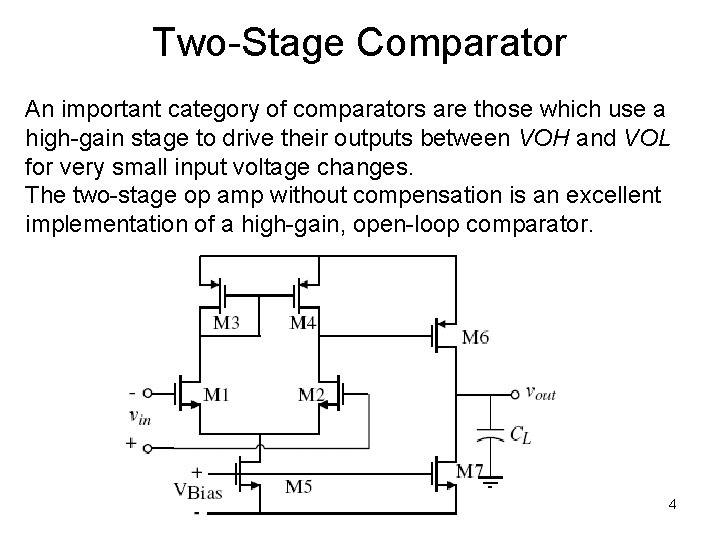

Two-Stage Comparator An important category of comparators are those which use a high-gain stage to drive their outputs between VOH and VOL for very small input voltage changes. The two-stage op amp without compensation is an excellent implementation of a high-gain, open-loop comparator. 4

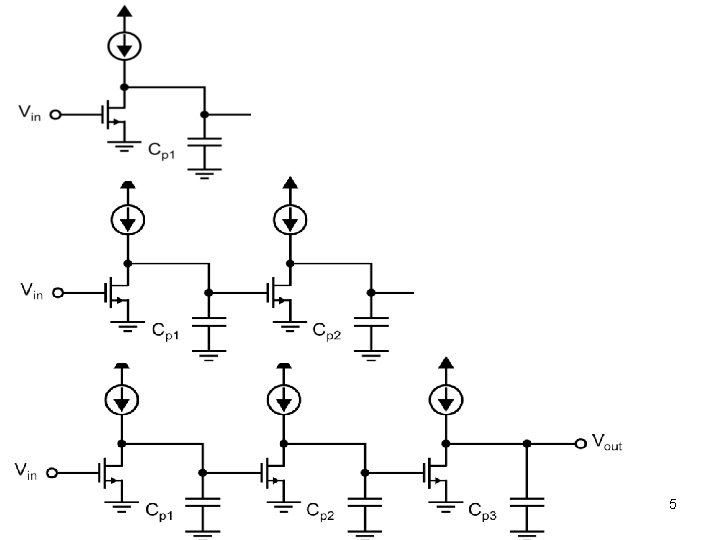

5

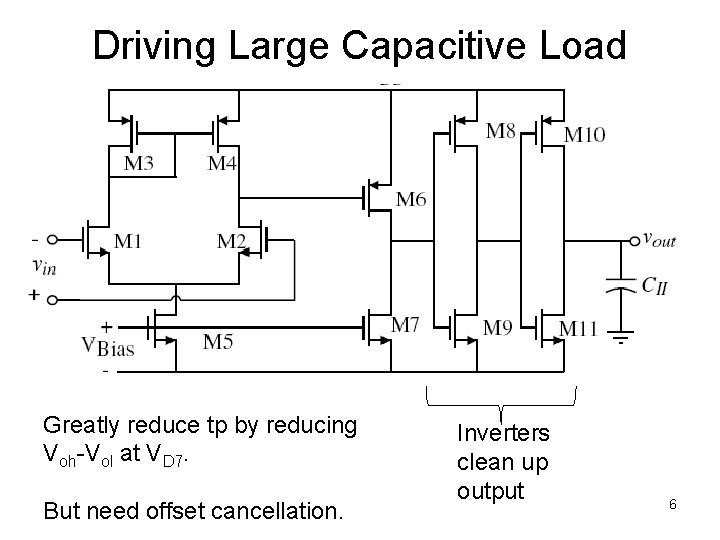

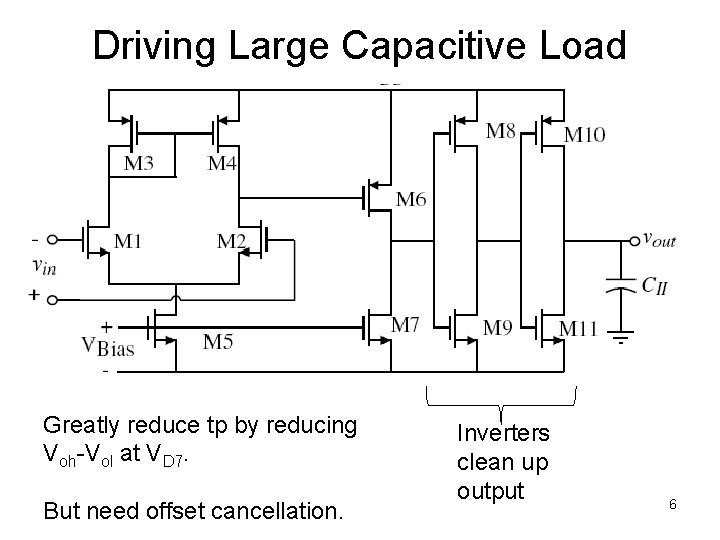

Driving Large Capacitive Load Greatly reduce tp by reducing Voh-Vol at VD 7. But need offset cancellation. Inverters clean up output 6

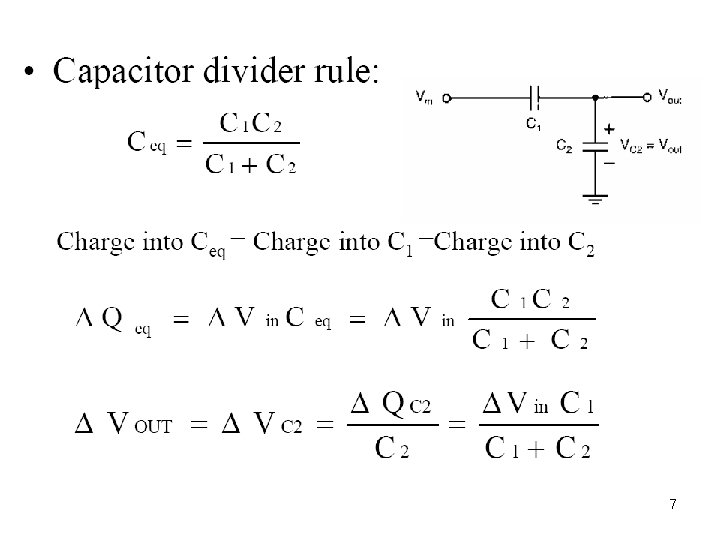

7

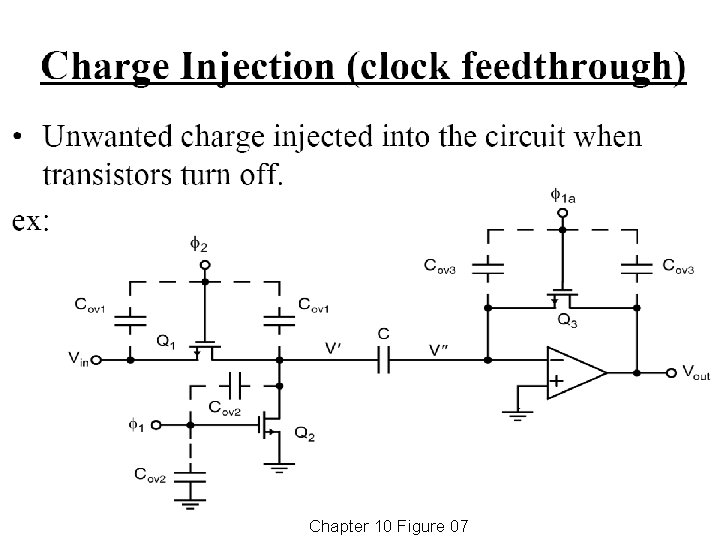

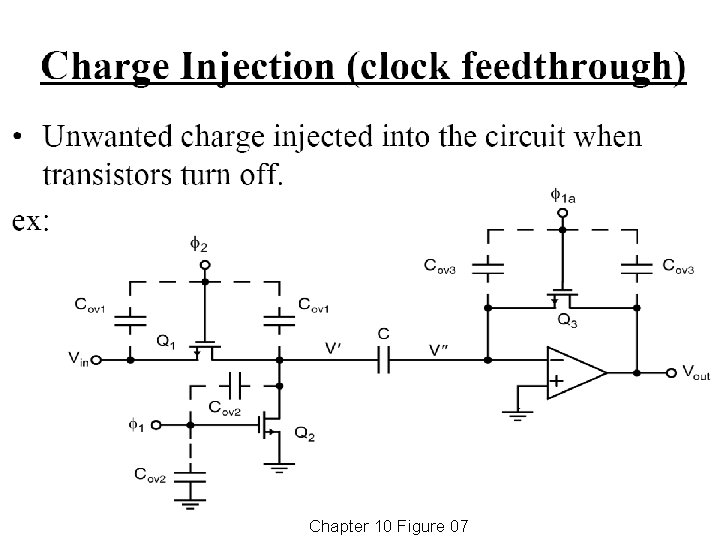

8 Chapter 10 Figure 07

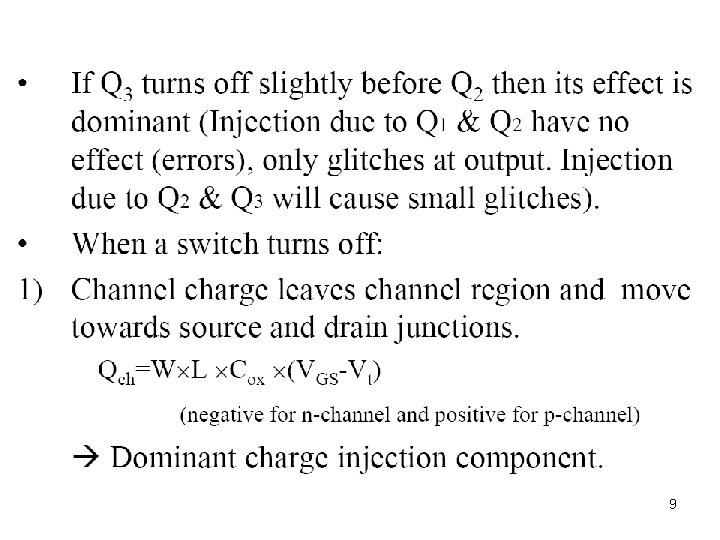

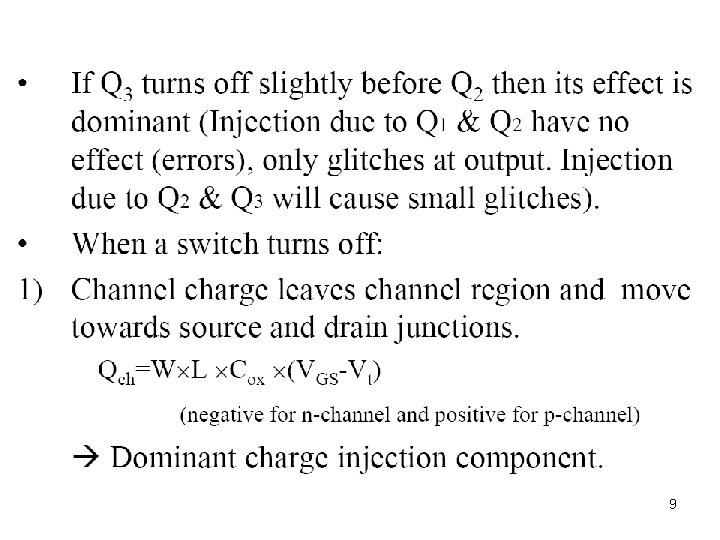

9

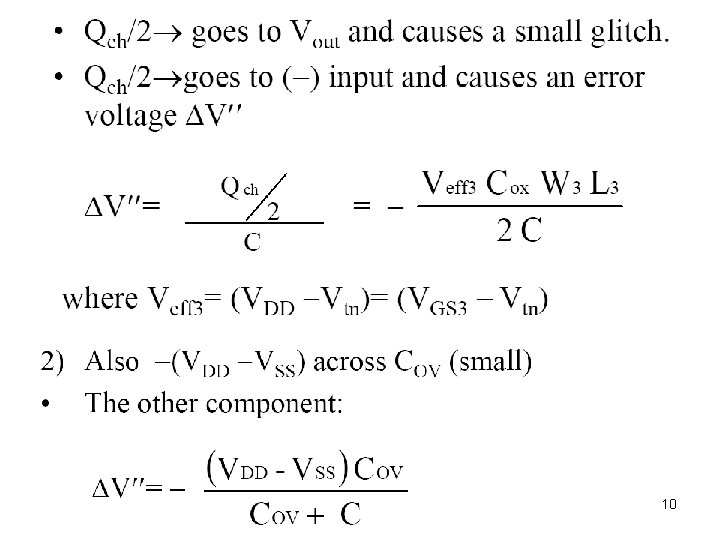

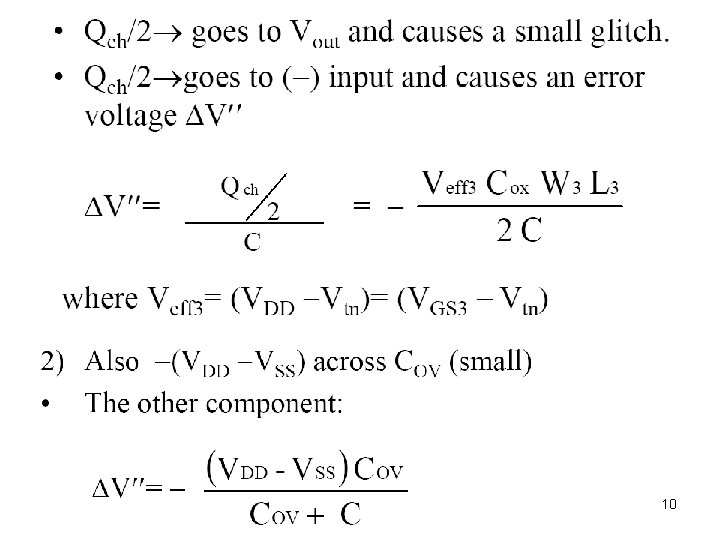

10

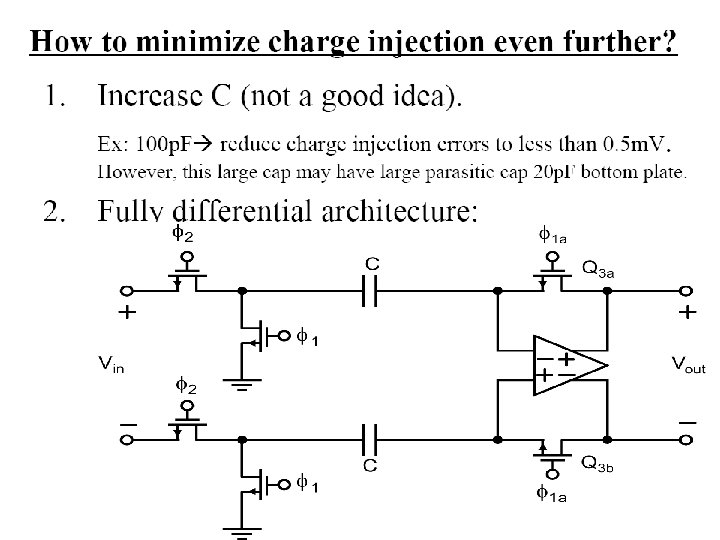

11

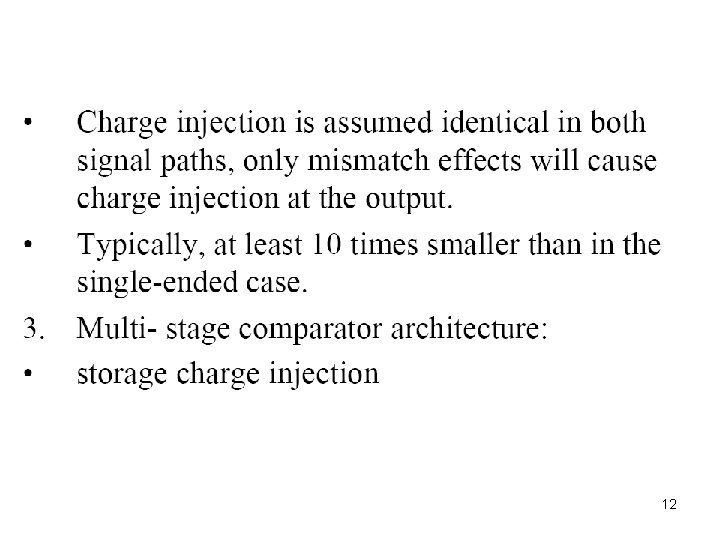

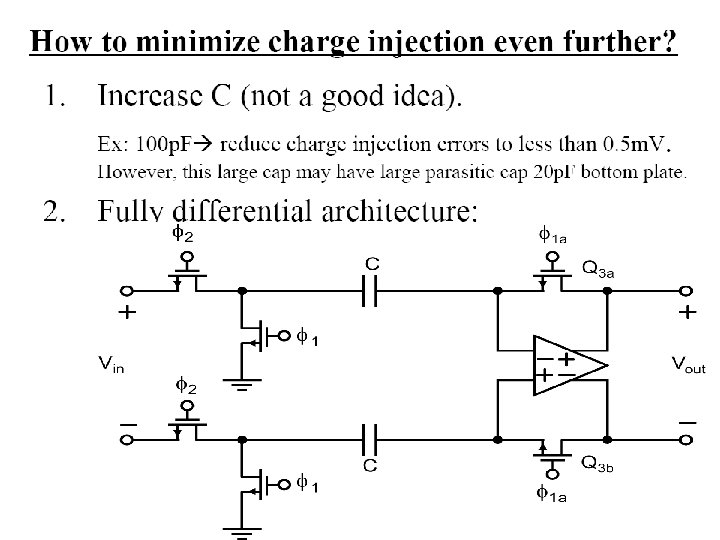

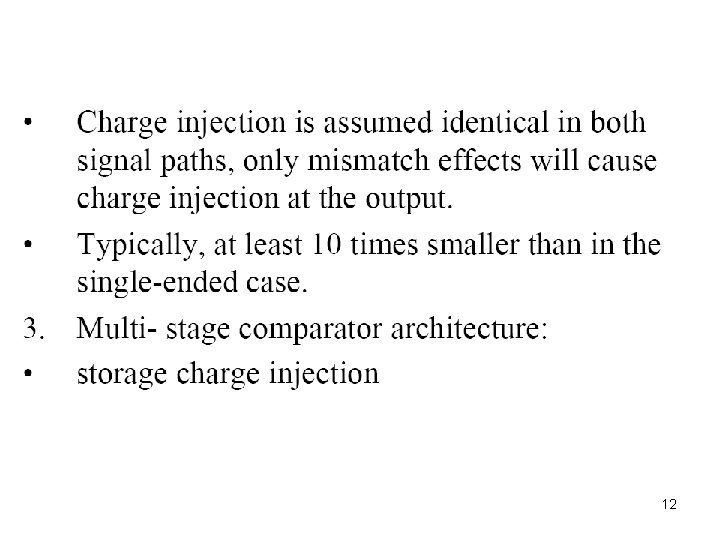

12

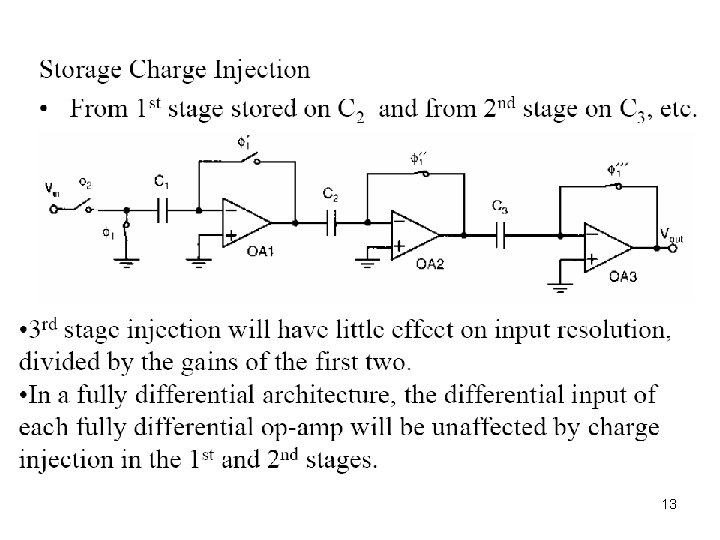

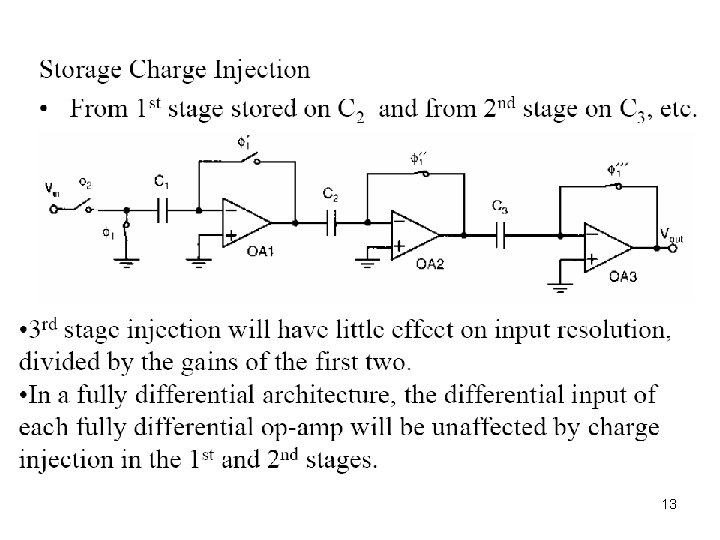

13

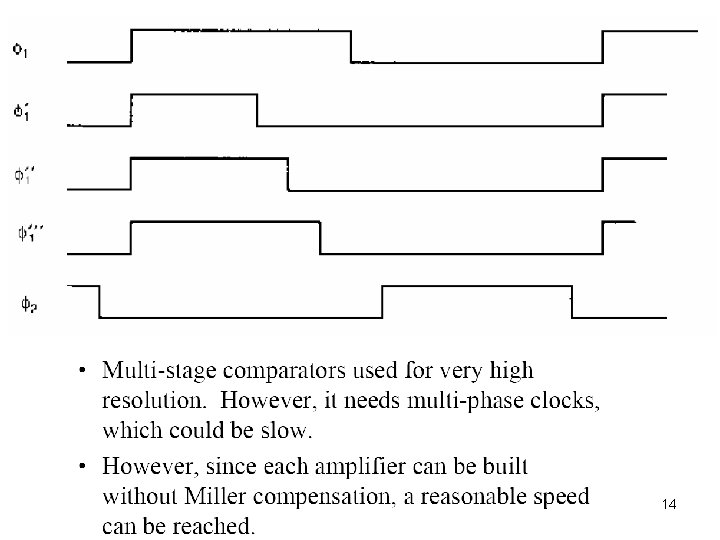

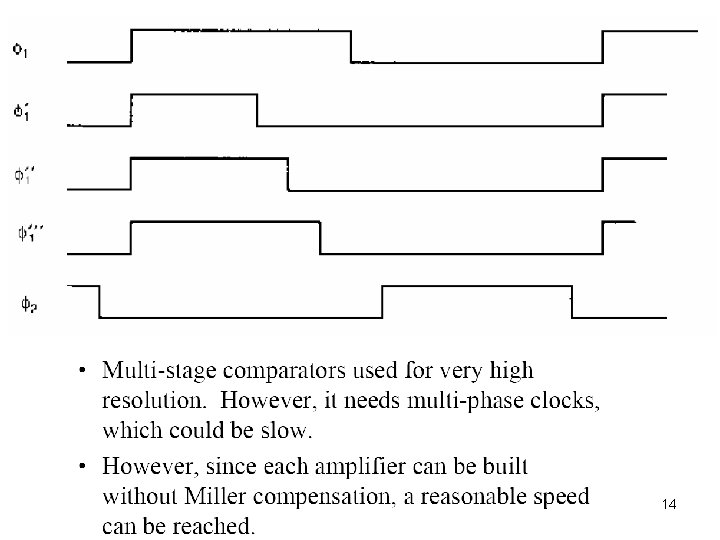

14

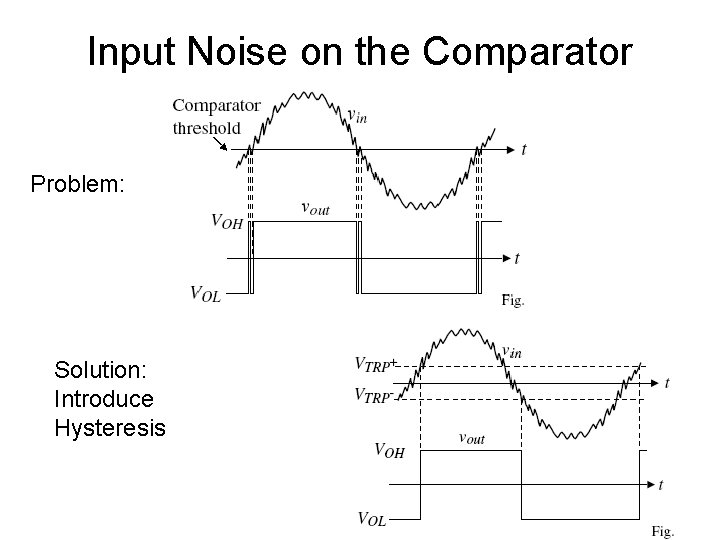

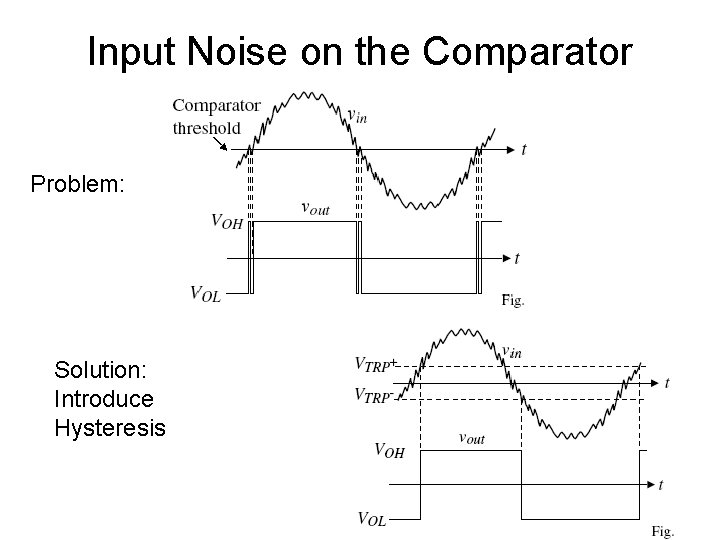

Input Noise on the Comparator Problem: Solution: Introduce Hysteresis 15

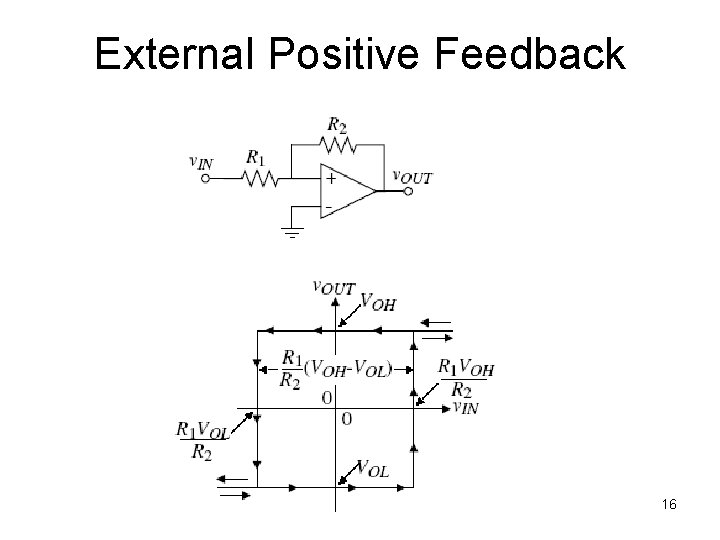

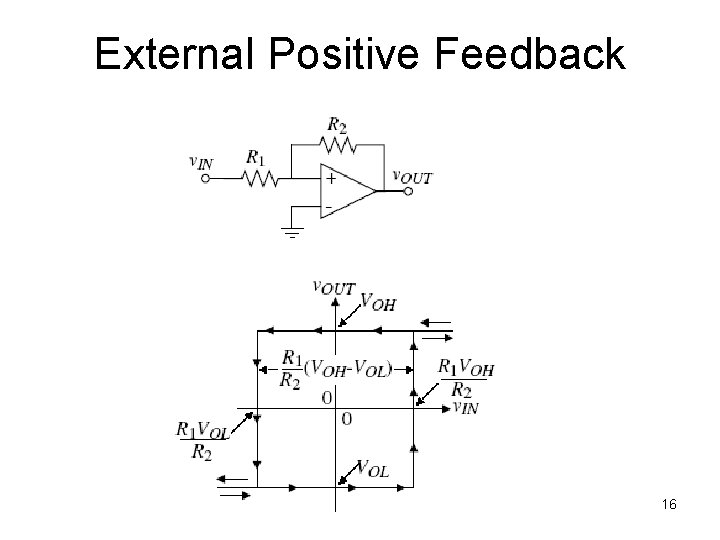

External Positive Feedback 16

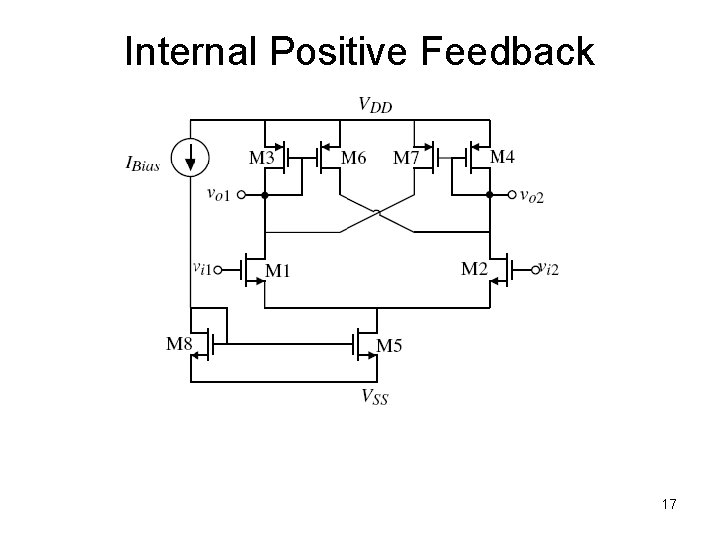

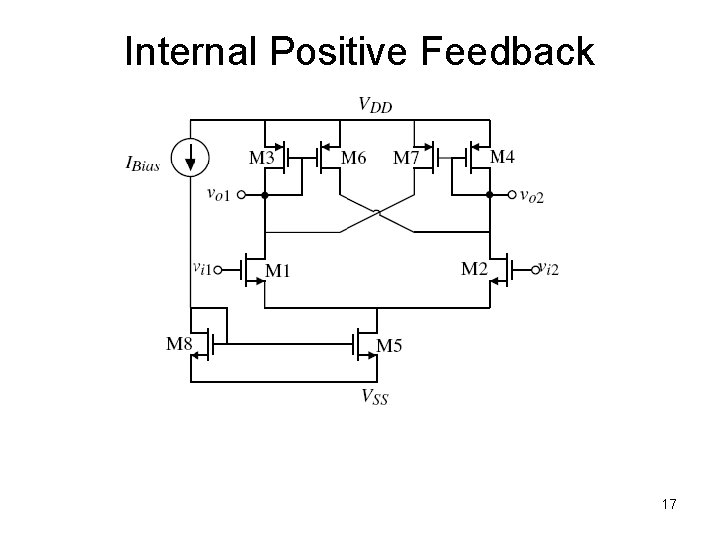

Internal Positive Feedback 17

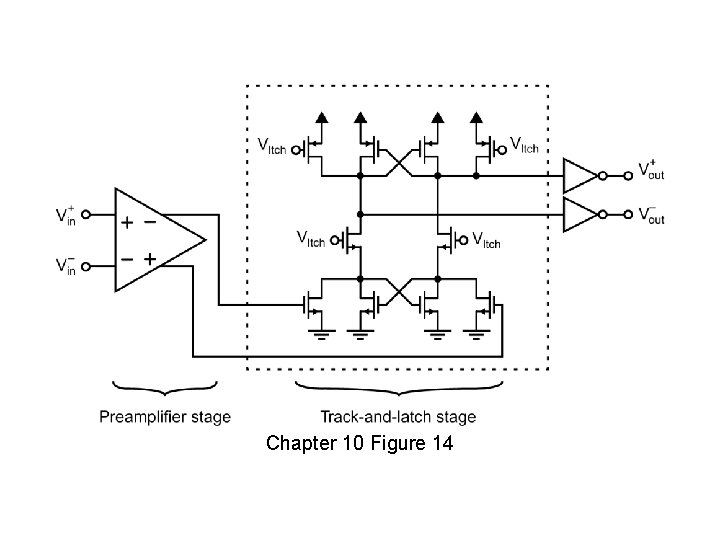

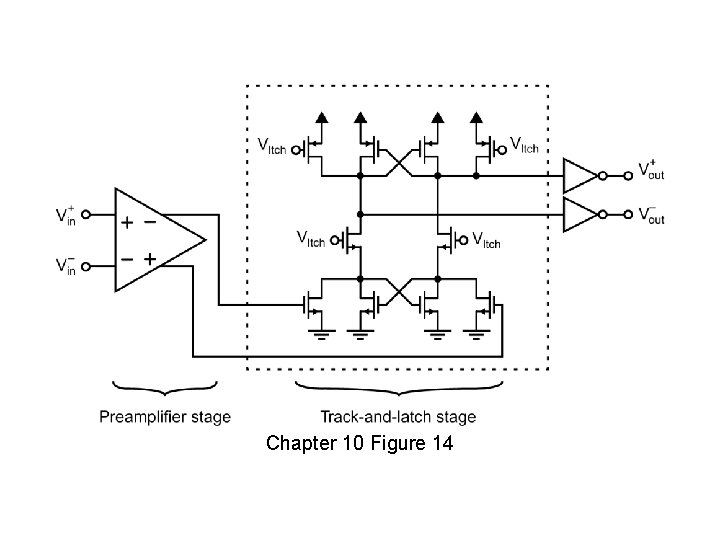

Chapter 10 Figure 14

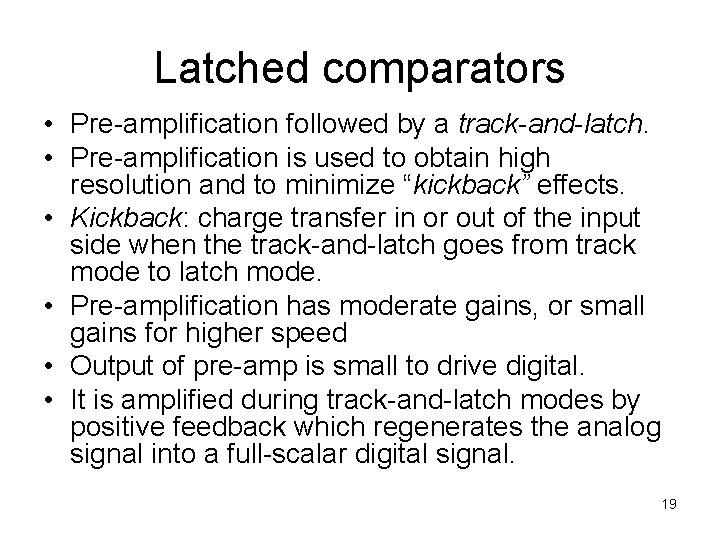

Latched comparators • Pre-amplification followed by a track-and-latch. • Pre-amplification is used to obtain high resolution and to minimize “kickback” effects. • Kickback: charge transfer in or out of the input side when the track-and-latch goes from track mode to latch mode. • Pre-amplification has moderate gains, or small gains for higher speed • Output of pre-amp is small to drive digital. • It is amplified during track-and-latch modes by positive feedback which regenerates the analog signal into a full-scalar digital signal. 19

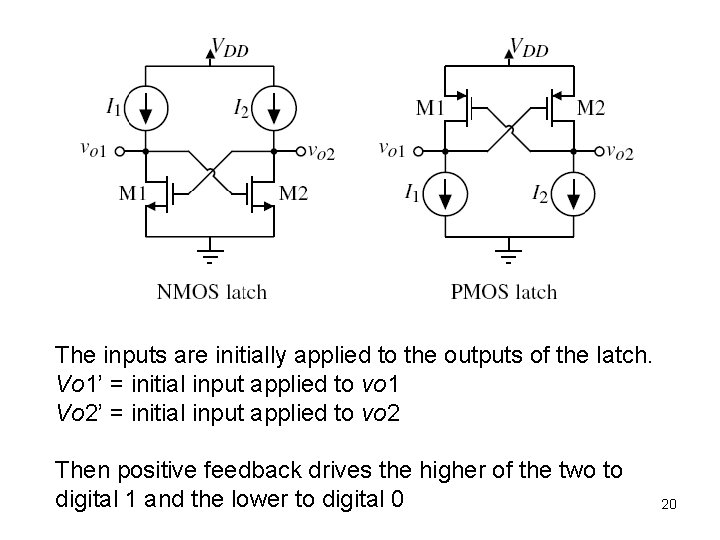

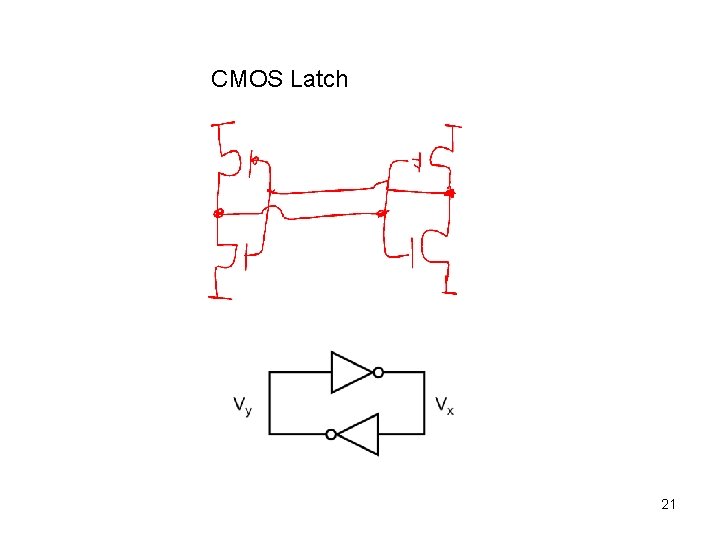

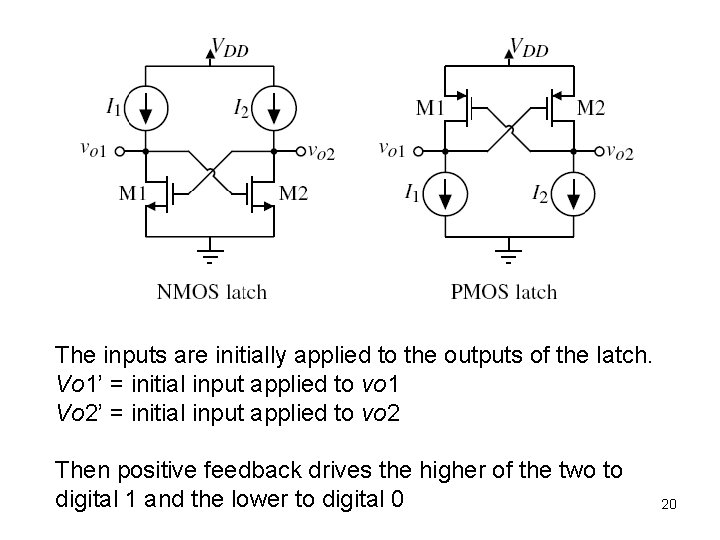

The inputs are initially applied to the outputs of the latch. Vo 1’ = initial input applied to vo 1 Vo 2’ = initial input applied to vo 2 Then positive feedback drives the higher of the two to digital 1 and the lower to digital 0 20

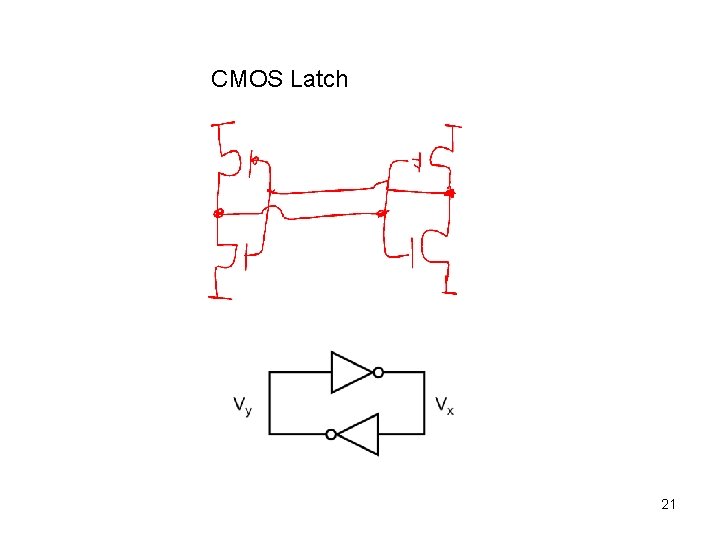

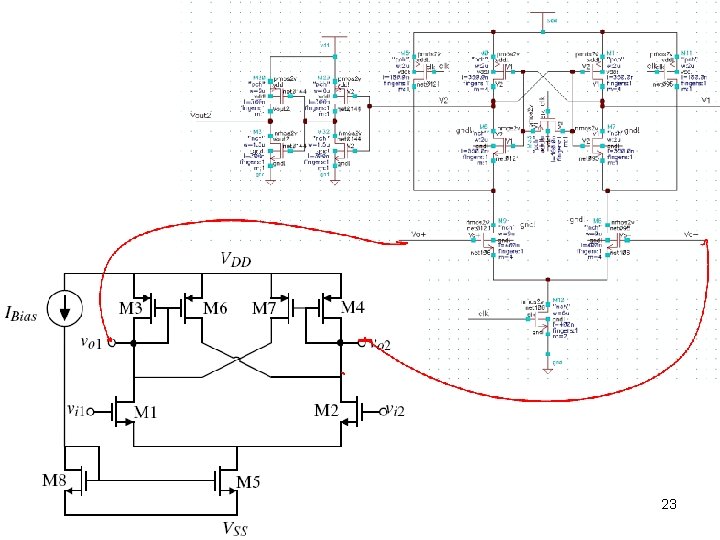

CMOS Latch 21

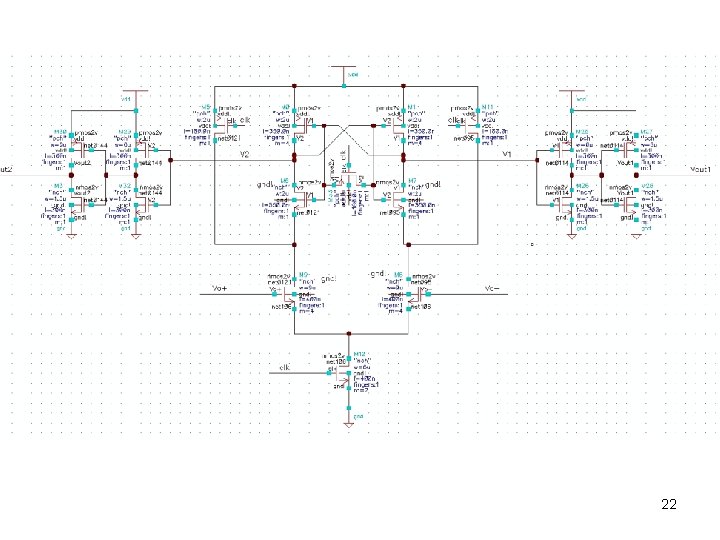

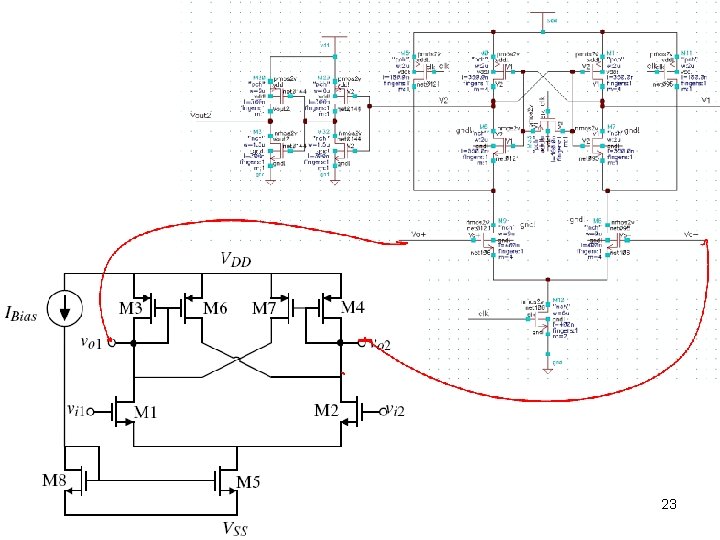

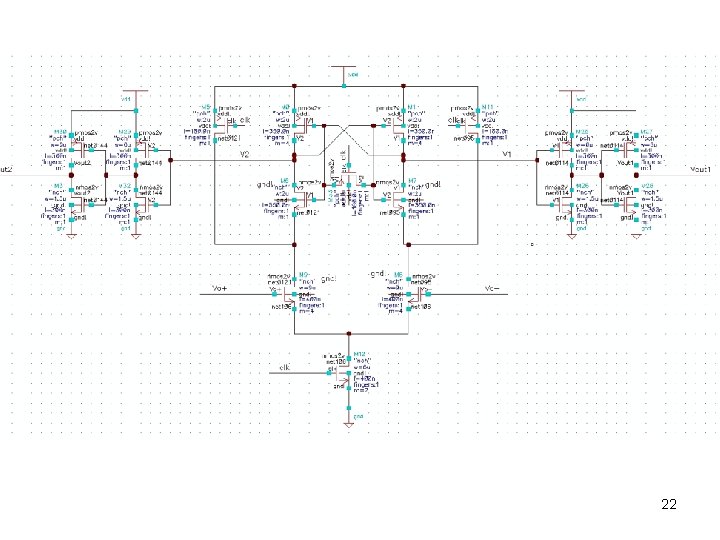

22

23

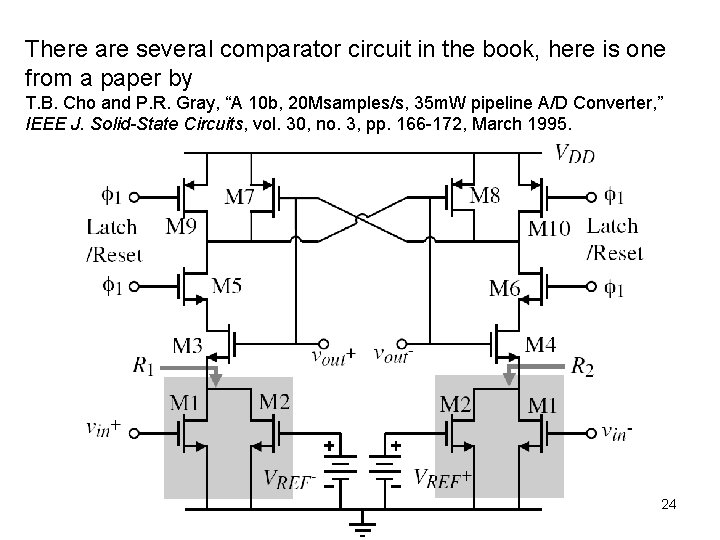

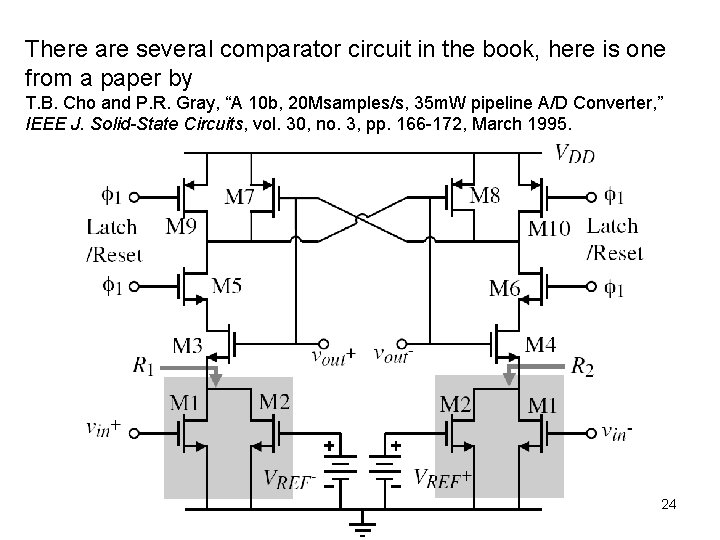

There are several comparator circuit in the book, here is one from a paper by T. B. Cho and P. R. Gray, “A 10 b, 20 Msamples/s, 35 m. W pipeline A/D Converter, ” IEEE J. Solid-State Circuits, vol. 30, no. 3, pp. 166 -172, March 1995. 24

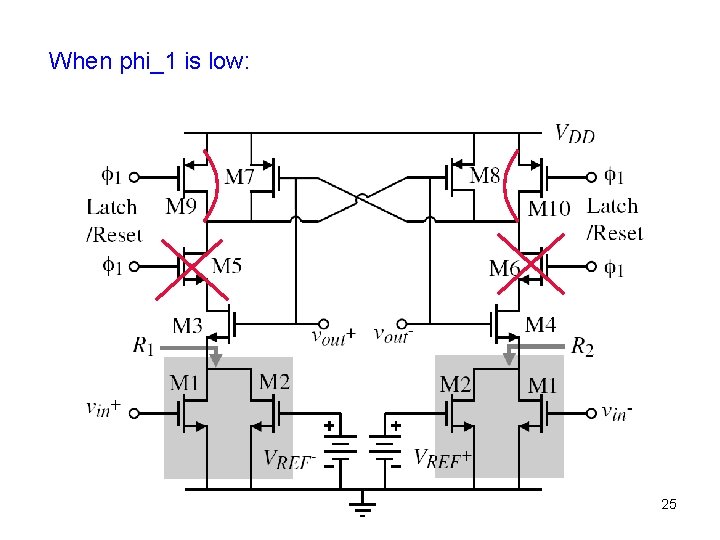

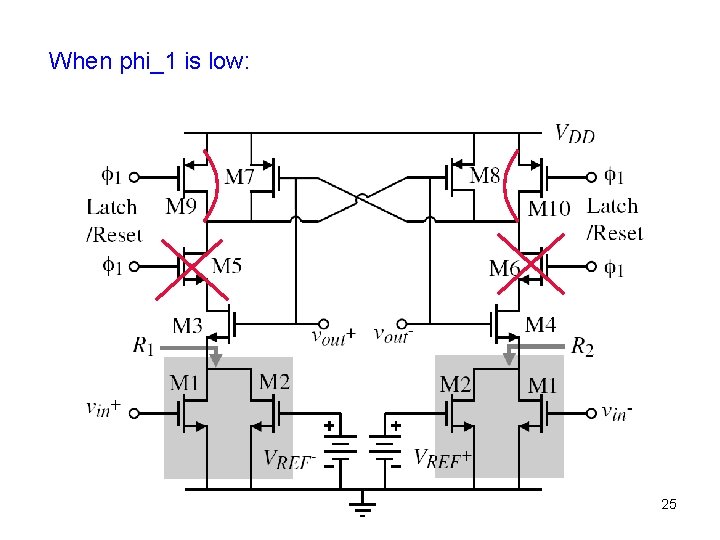

When phi_1 is low: 25

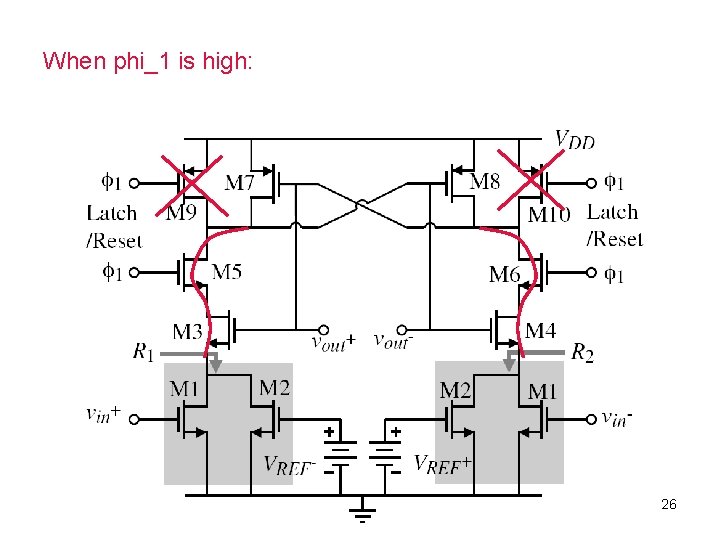

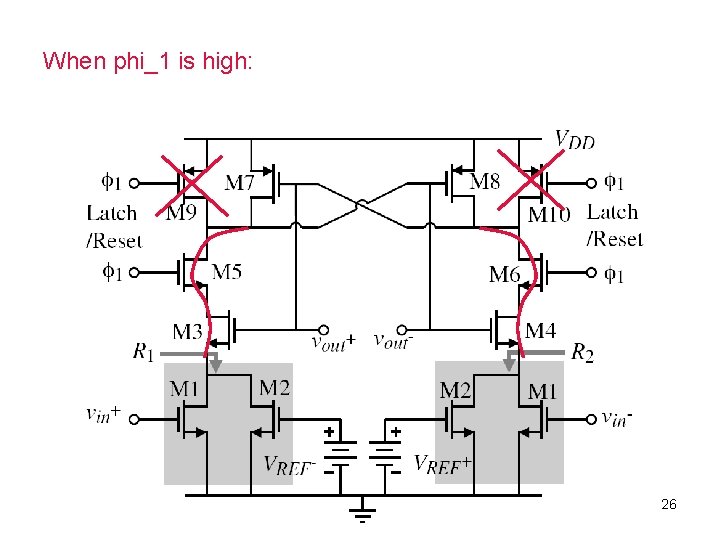

When phi_1 is high: 26