Projeto de Circuitos Integrados Semidedicados Prof Marcio Cunha

![Arquitetura v Declaração: v ARCHITECTURE arquitetura_nome OF entidade_nome IS v [declarações v opcionais] BEGIN Arquitetura v Declaração: v ARCHITECTURE arquitetura_nome OF entidade_nome IS v [declarações v opcionais] BEGIN](https://slidetodoc.com/presentation_image_h2/b884ca6c89a34d3d6826751d2580e894/image-13.jpg)

- Slides: 26

Projeto de Circuitos Integrados Semidedicados Prof. Marcio Cunha Aula 04 – Linguagem de Descrição de Hardware: VHDL

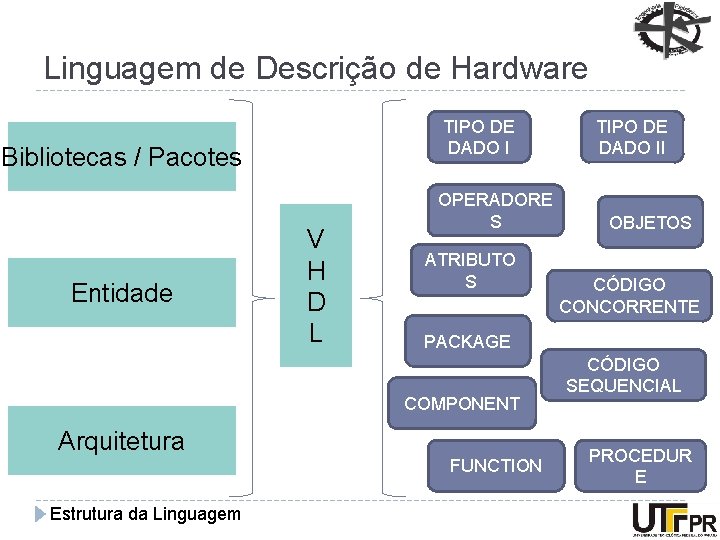

Agenda � Planejamento � Linguagem de Descrição de Hardware � Bibliotecas e Pacotes � Entidade � Arquitetura � Estilos de Programação

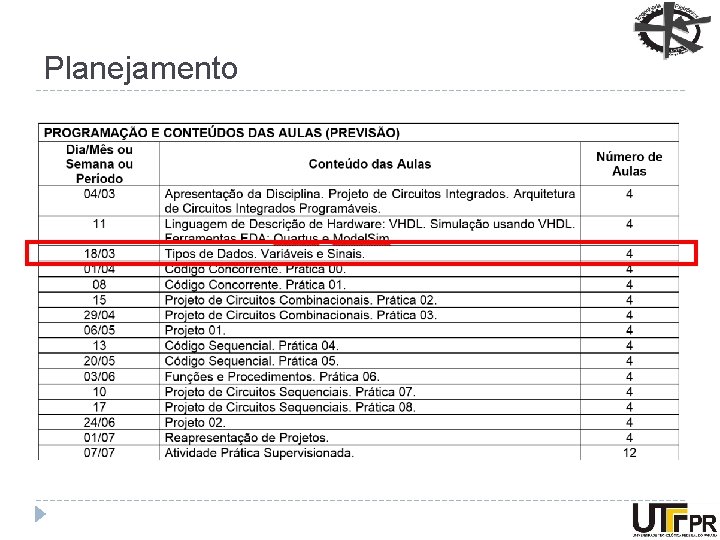

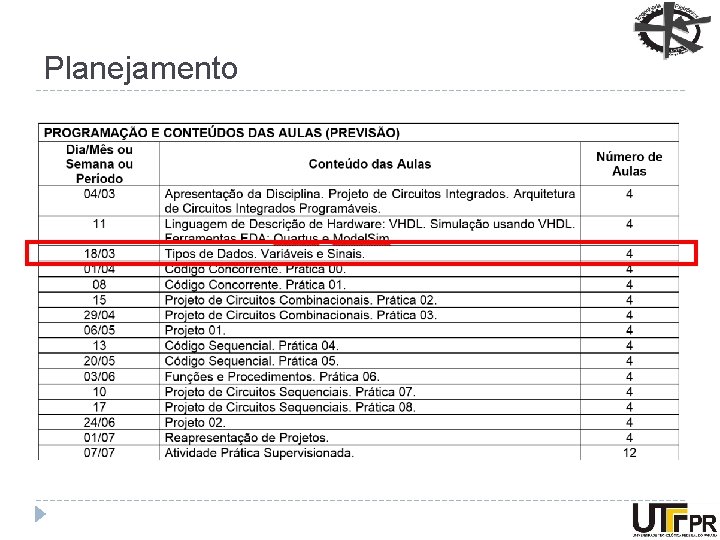

Planejamento

Agenda � Planejamento � Linguagem � Bibliotecas de Descrição de Hardware e Pacotes � Entidade � Arquitetura � Estilos de Programação

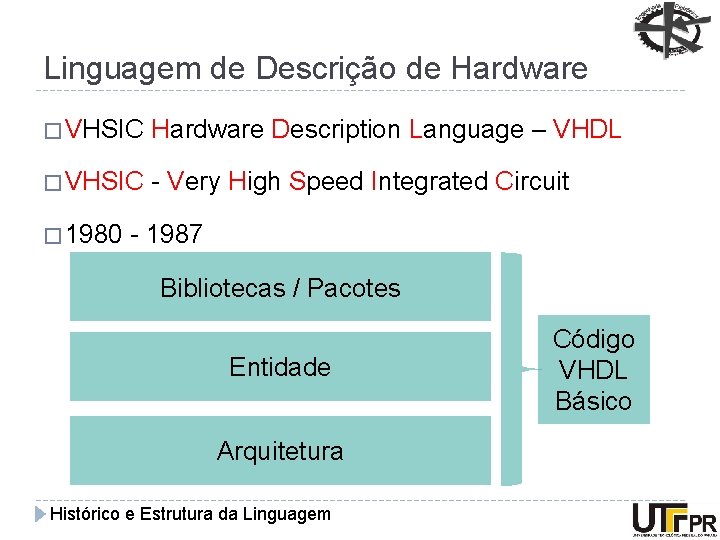

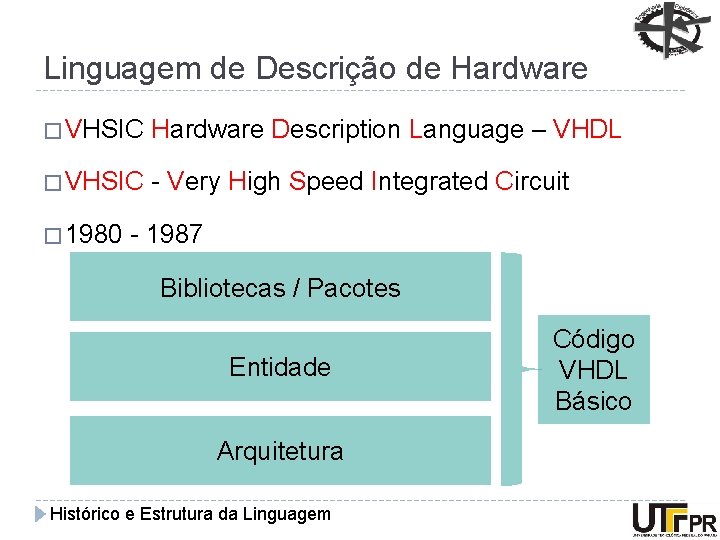

Linguagem de Descrição de Hardware � VHSIC Hardware Description Language – VHDL � VHSIC - Very High Speed Integrated Circuit � 1980 - 1987 Bibliotecas / Pacotes Entidade Arquitetura Histórico e Estrutura da Linguagem Código VHDL Básico

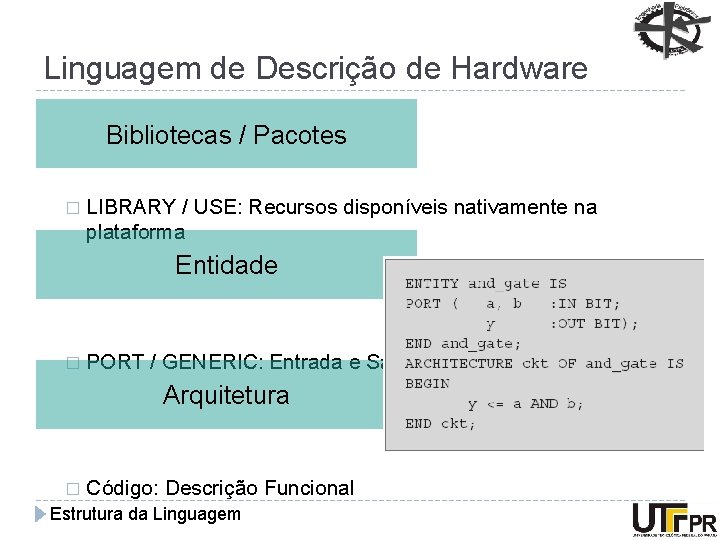

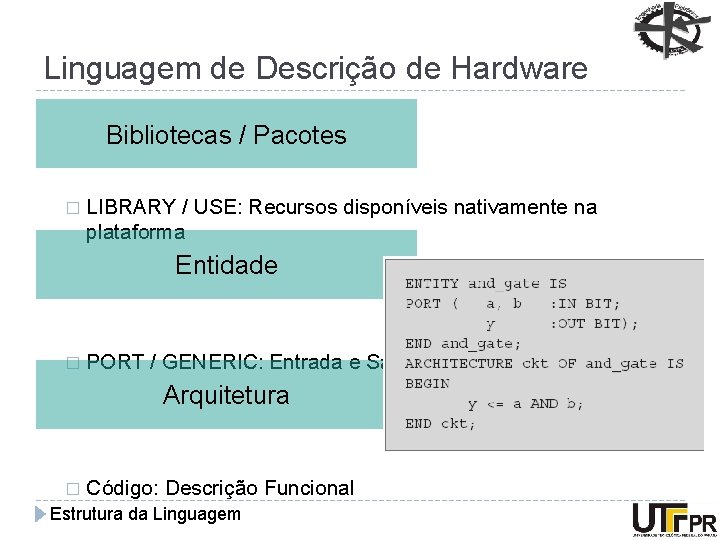

Linguagem de Descrição de Hardware Bibliotecas / Pacotes � LIBRARY / USE: Recursos disponíveis nativamente na plataforma Entidade � PORT / GENERIC: Entrada e Saída Arquitetura � Código: Descrição Funcional Estrutura da Linguagem

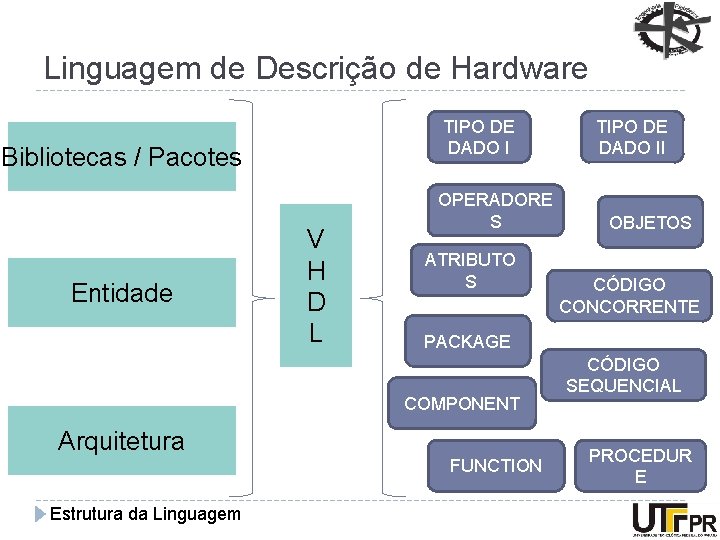

Linguagem de Descrição de Hardware TIPO DE DADO I Bibliotecas / Pacotes Entidade V H D L OPERADORE S ATRIBUTO S OBJETOS CÓDIGO CONCORRENTE PACKAGE COMPONENT Arquitetura FUNCTION Estrutura da Linguagem TIPO DE DADO II CÓDIGO SEQUENCIAL PROCEDUR E

Agenda � Planejamento � Linguagem de Descrição de Hardware � Bibliotecas e Pacotes � Entidade � Arquitetura � Estilos de Programação

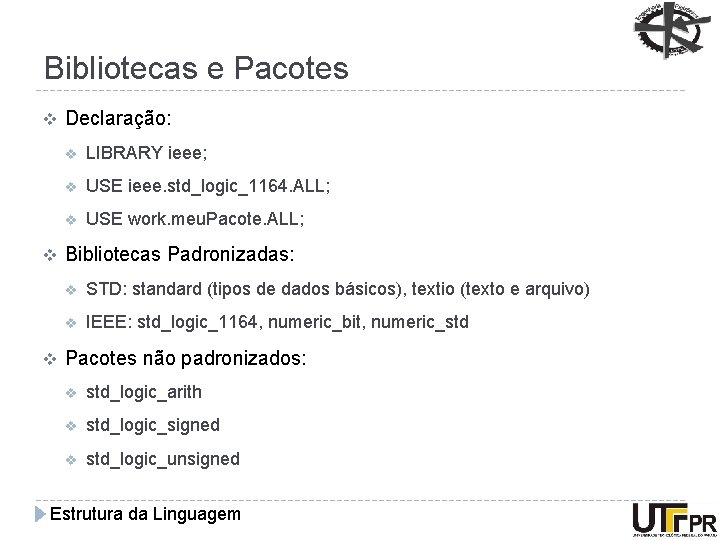

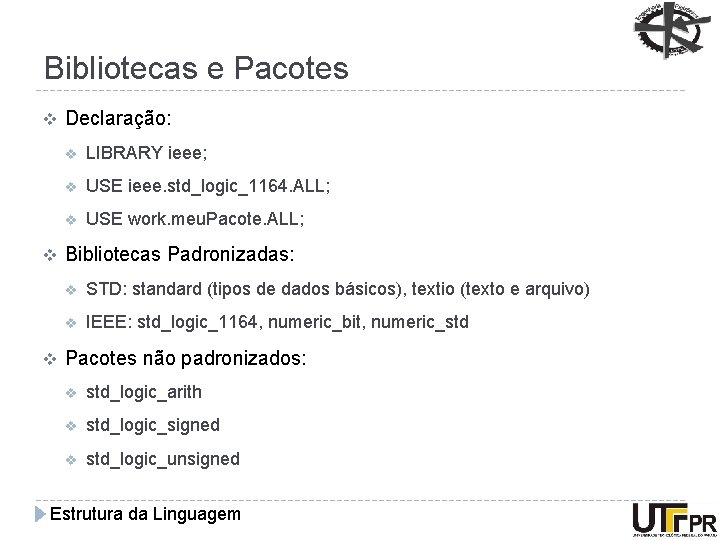

Bibliotecas e Pacotes v v v Declaração: v LIBRARY ieee; v USE ieee. std_logic_1164. ALL; v USE work. meu. Pacote. ALL; Bibliotecas Padronizadas: v STD: standard (tipos de dados básicos), textio (texto e arquivo) v IEEE: std_logic_1164, numeric_bit, numeric_std Pacotes não padronizados: v std_logic_arith v std_logic_signed v std_logic_unsigned Estrutura da Linguagem

Agenda � Planejamento � Linguagem de Descrição de Hardware � Bibliotecas e Pacotes � Entidade � Arquitetura � Estilos de Programação

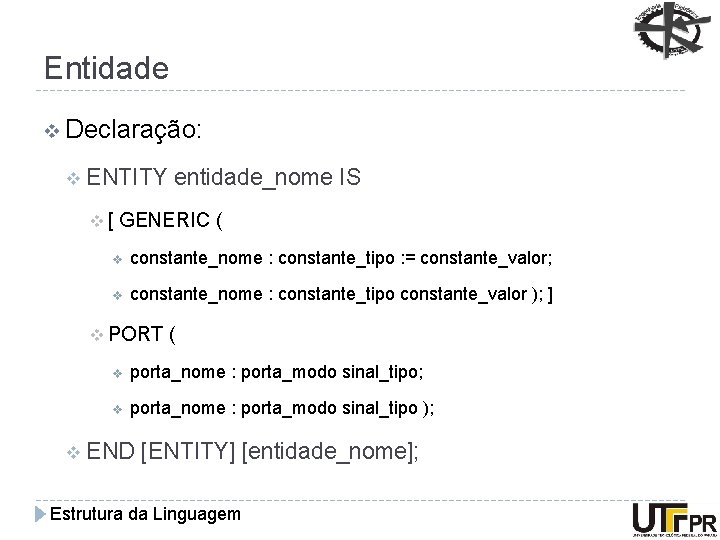

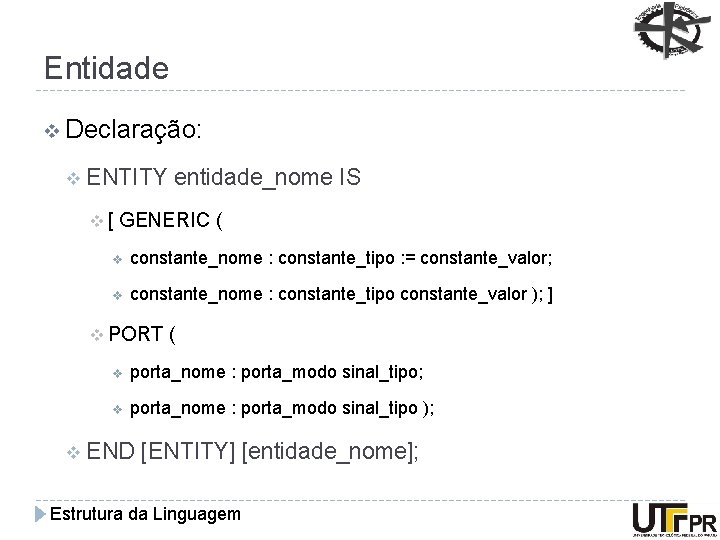

Entidade v Declaração: v ENTITY entidade_nome IS v[ GENERIC ( v constante_nome : constante_tipo : = constante_valor; v constante_nome : constante_tipo constante_valor ); ] v PORT v ( v porta_nome : porta_modo sinal_tipo; v porta_nome : porta_modo sinal_tipo ); END [ENTITY] [entidade_nome]; Estrutura da Linguagem

Agenda � Planejamento � Linguagem de Descrição de Hardware � Bibliotecas e Pacotes � Entidade � Arquitetura � Estilos de Programação

![Arquitetura v Declaração v ARCHITECTURE arquiteturanome OF entidadenome IS v declarações v opcionais BEGIN Arquitetura v Declaração: v ARCHITECTURE arquitetura_nome OF entidade_nome IS v [declarações v opcionais] BEGIN](https://slidetodoc.com/presentation_image_h2/b884ca6c89a34d3d6826751d2580e894/image-13.jpg)

Arquitetura v Declaração: v ARCHITECTURE arquitetura_nome OF entidade_nome IS v [declarações v opcionais] BEGIN v Código; v END [ARCHITECTURE] [arquitetura_nome]; Estrutura da Linguagem

Agenda � Planejamento � Linguagem de Descrição de Hardware � Bibliotecas e Pacotes � Entidade � Arquitetura � Estilos de Programação

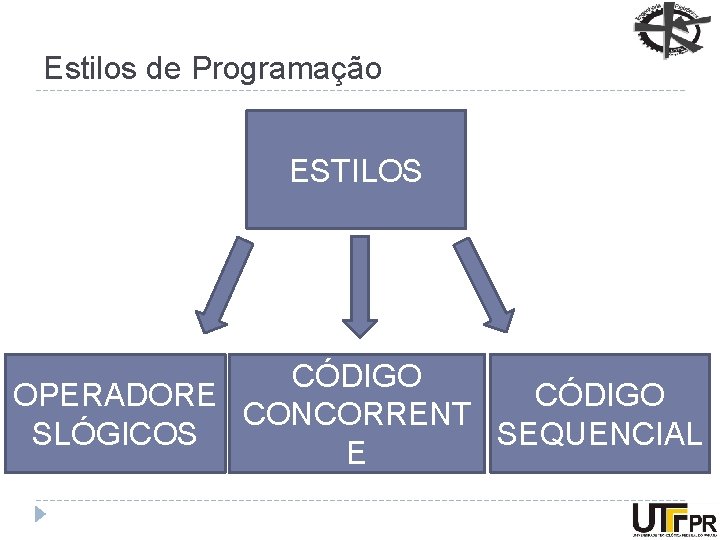

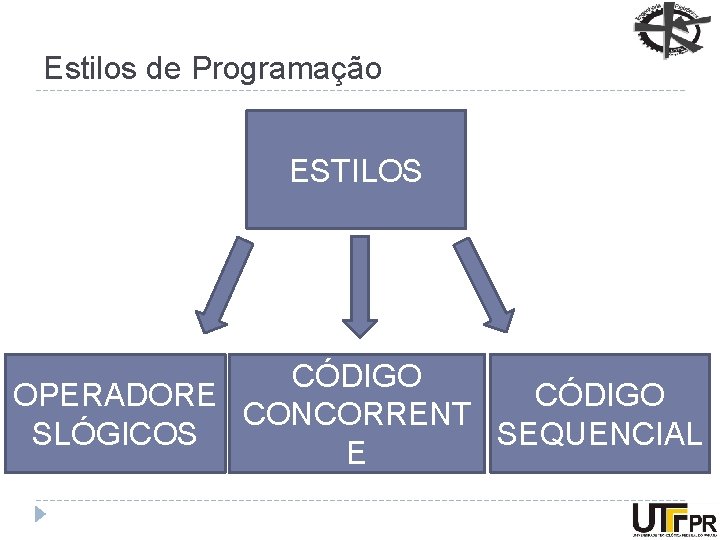

Estilos de Programação ESTILOS CÓDIGO OPERADORE CÓDIGO CONCORRENT SLÓGICOS SEQUENCIAL E

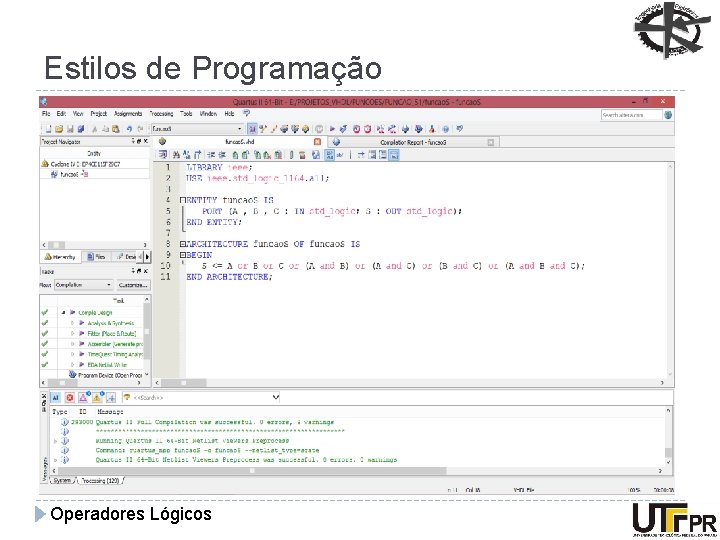

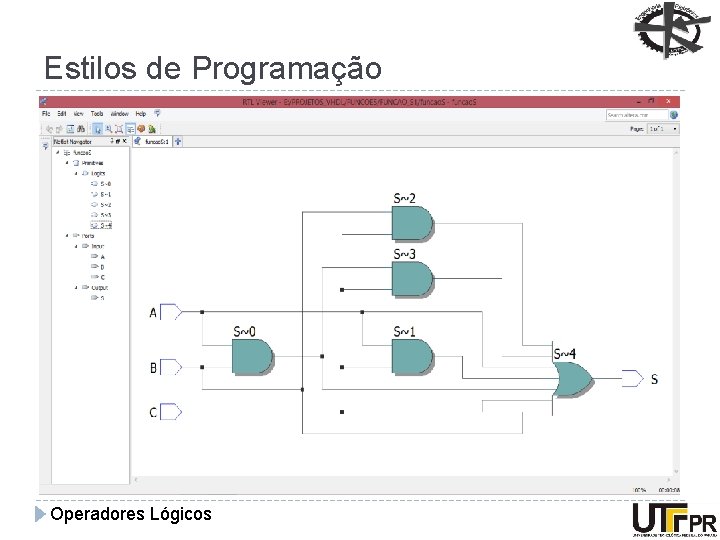

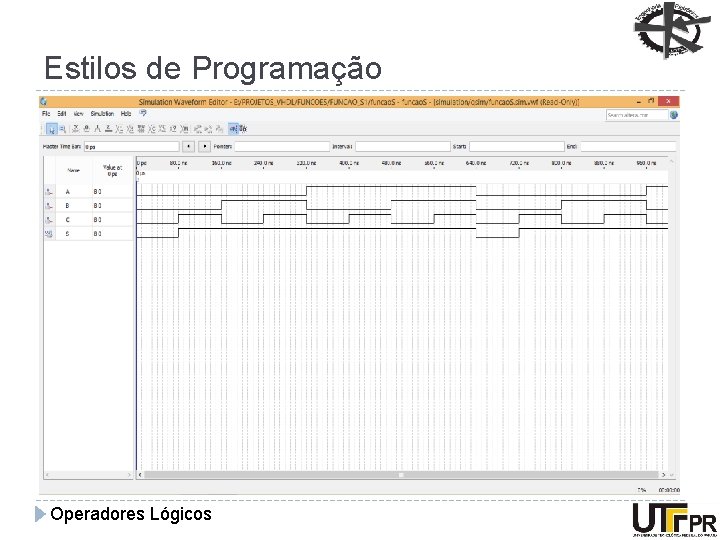

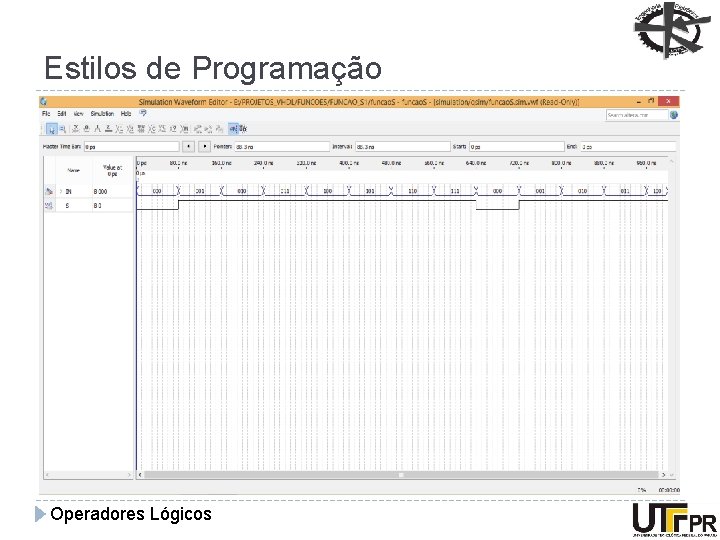

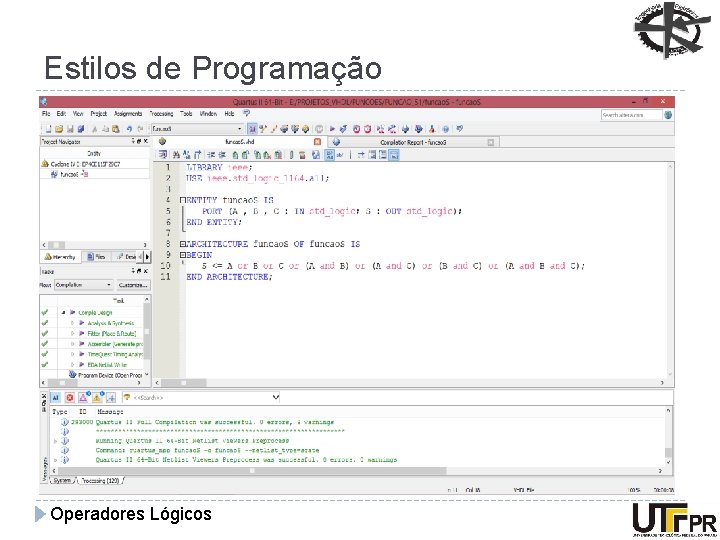

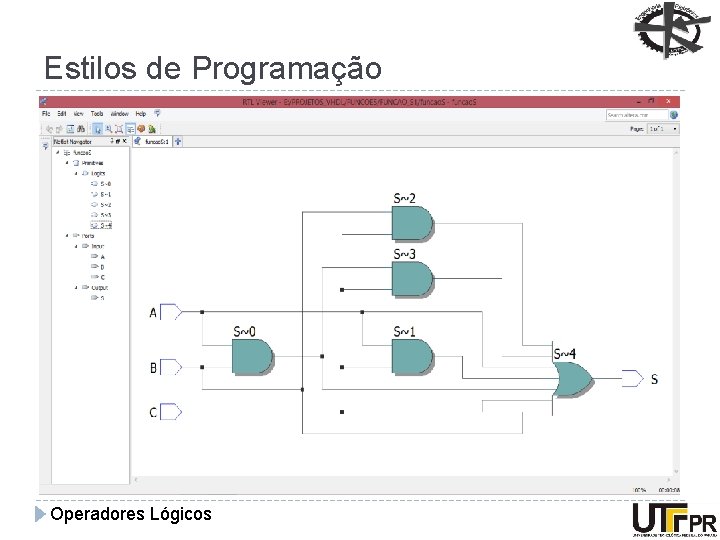

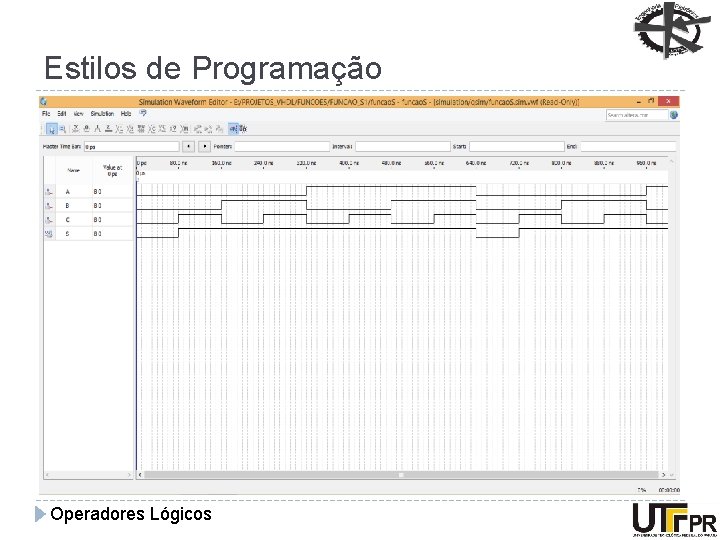

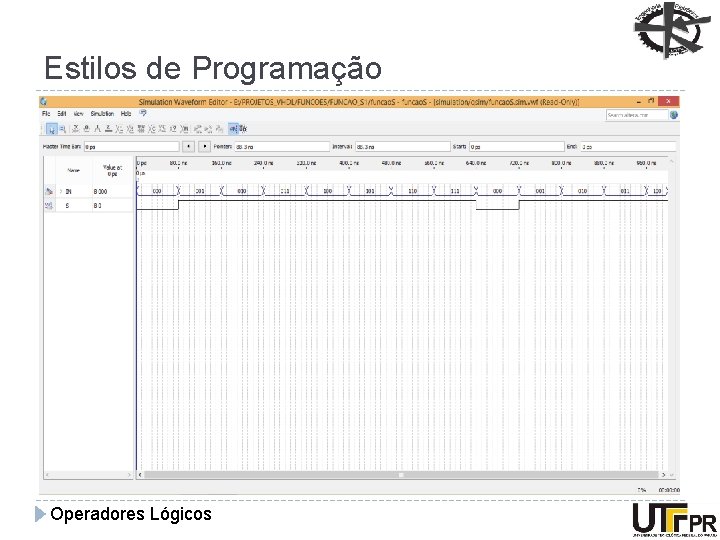

Estilos de Programação Operadores Lógicos

Estilos de Programação Operadores Lógicos

Estilos de Programação Operadores Lógicos

Estilos de Programação Operadores Lógicos

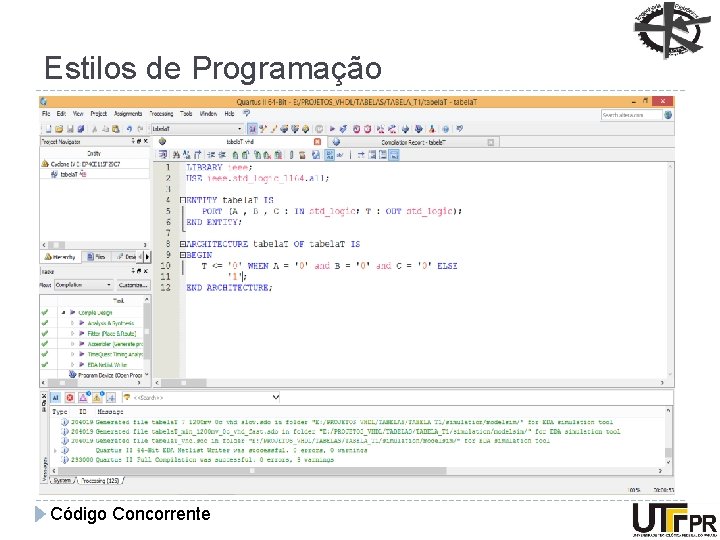

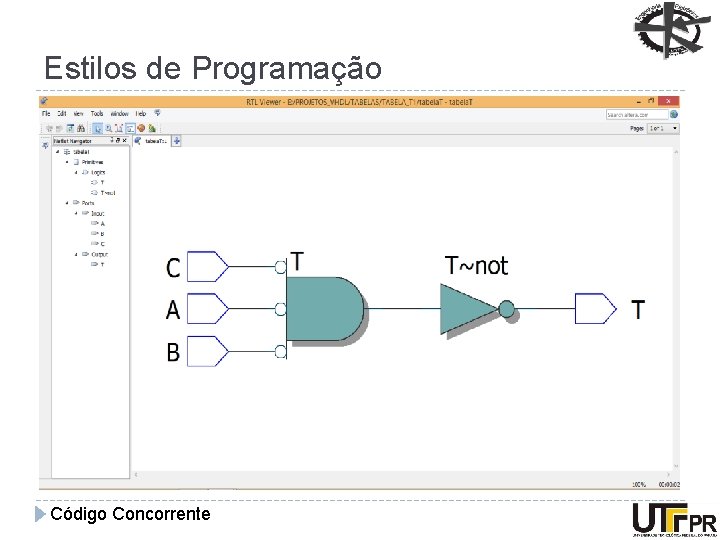

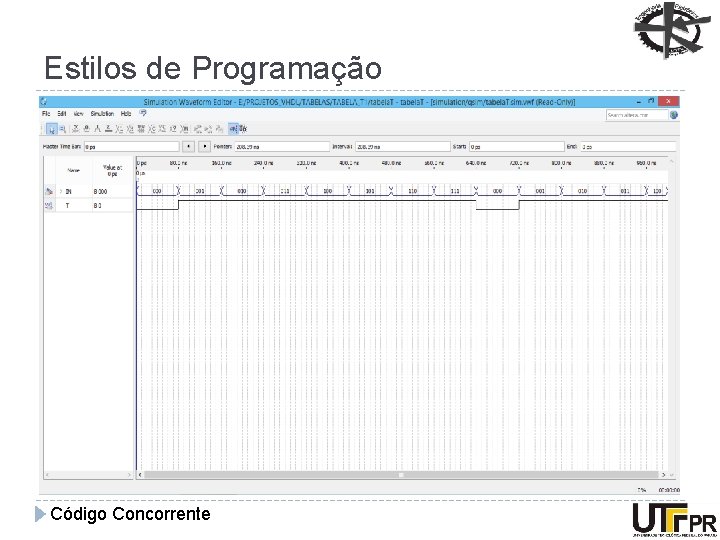

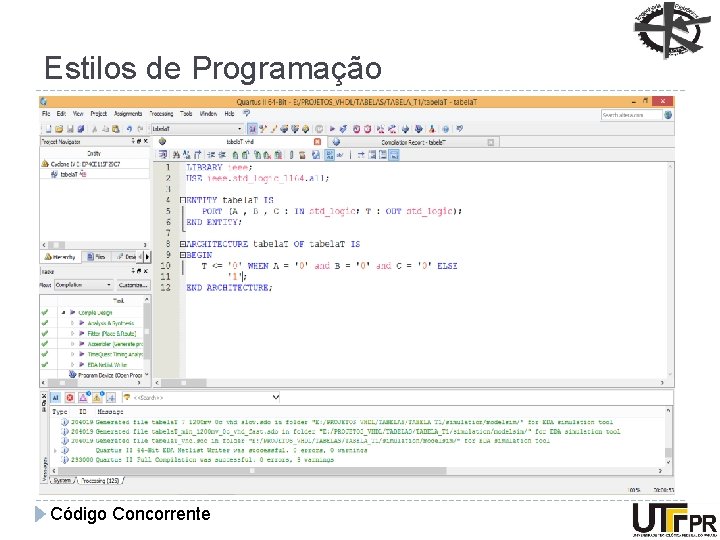

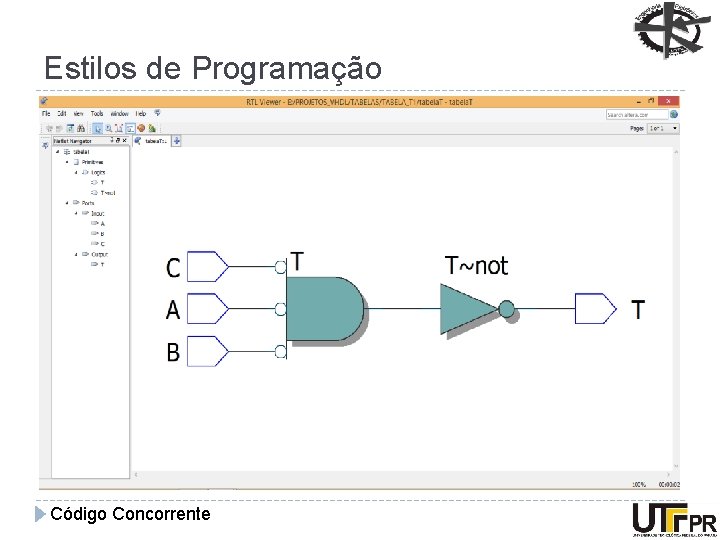

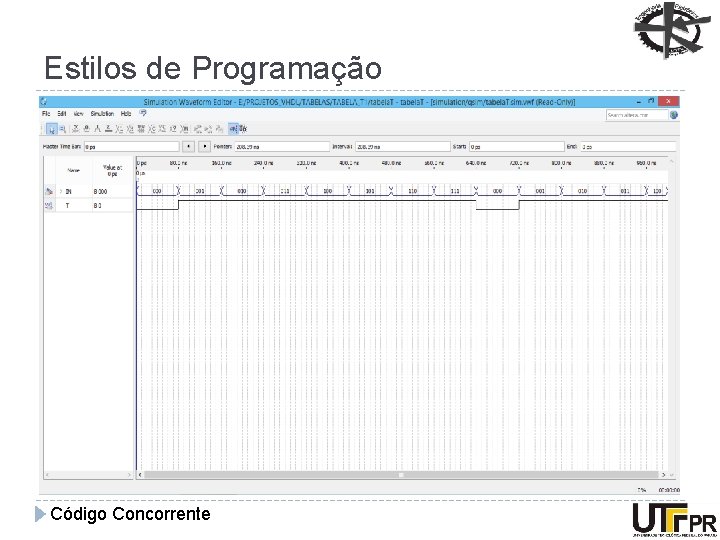

Estilos de Programação Código Concorrente

Estilos de Programação Código Concorrente

Estilos de Programação Código Concorrente

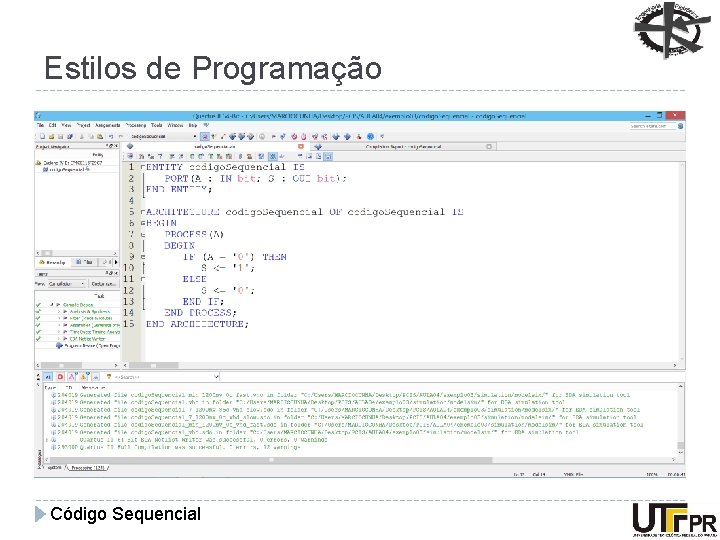

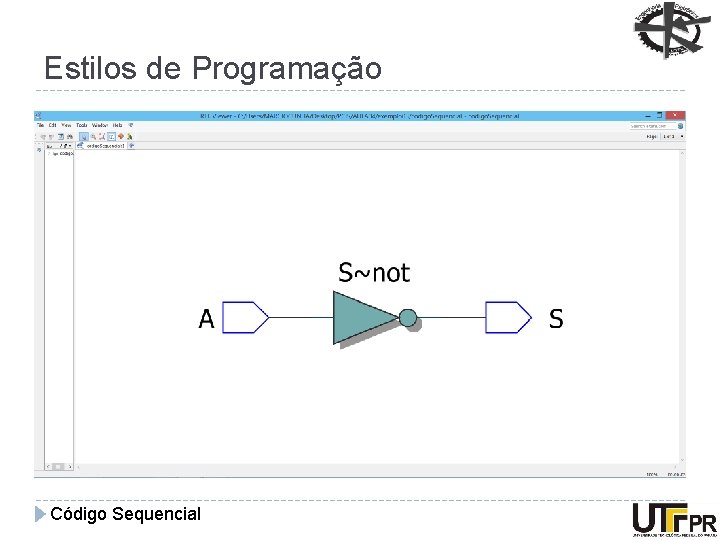

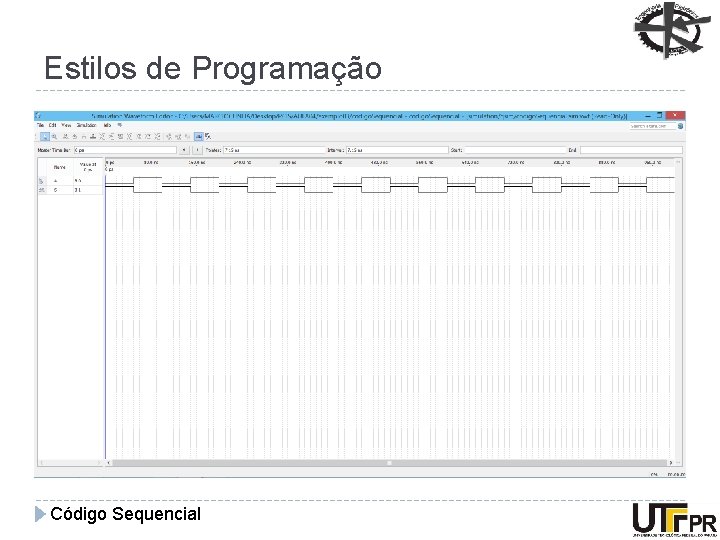

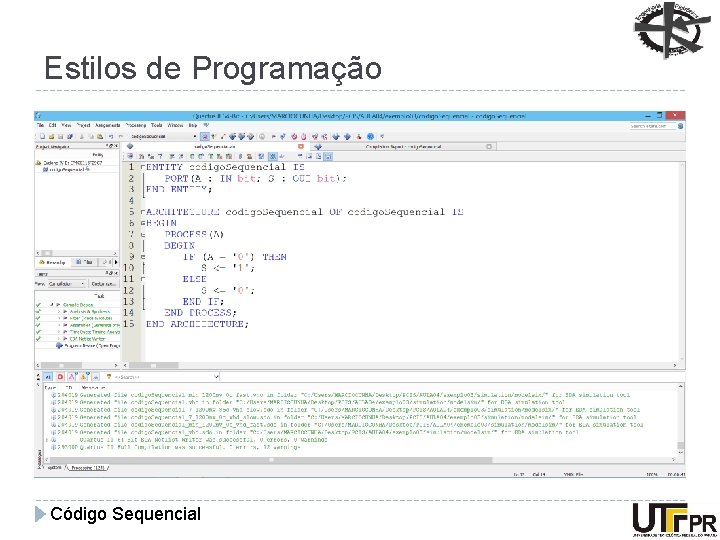

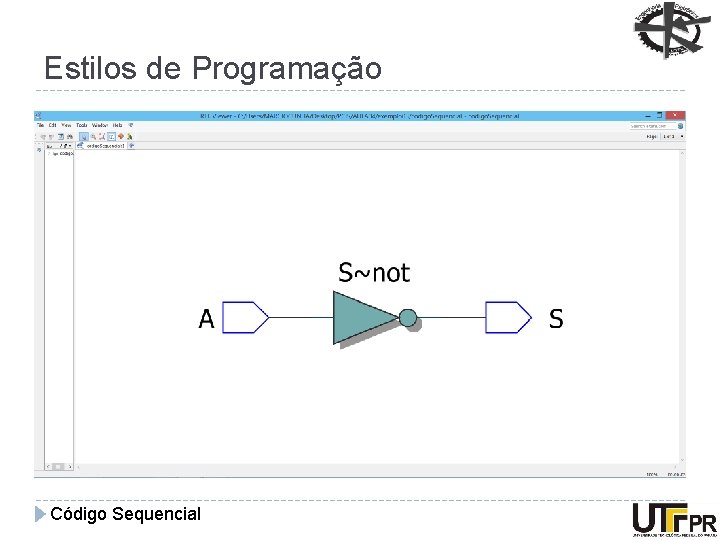

Estilos de Programação Código Sequencial

Estilos de Programação Código Sequencial

Estilos de Programação Código Sequencial

Projeto de Circuitos Integrados Semidedicados Prof. Marcio Cunha Aula 04 – Linguagem de Descrição de Hardware: VHDL