Progress on DCDC converters for Si Tracker for

- Slides: 30

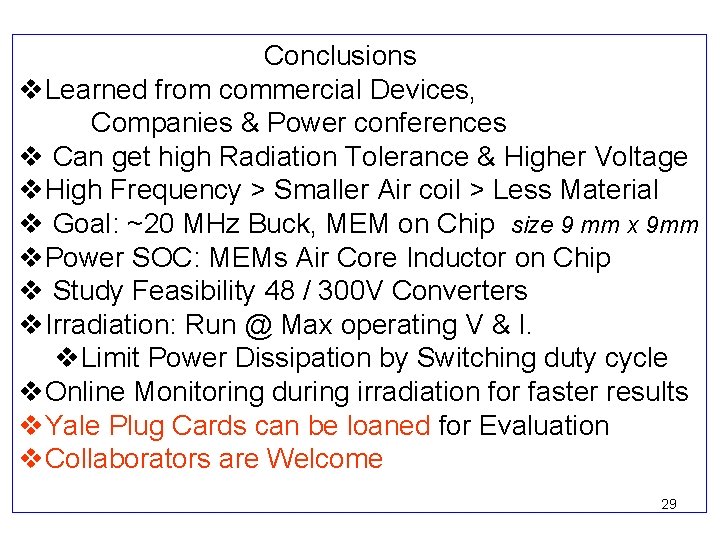

Progress on DC-DC converters for Si. Tracker for SLHC S. Dhawan, O. Baker, H. Chen, R. Khanna, J. Kierstead, F. Lanni, D. Lynn, A. Mincer, C. Musso S. Rescia, H. Smith, P. Tipton, M. Weber Yale University, New Haven, CT USA Brookhaven National Laboratory, Upton, NY USA Rutherford Appleton Laboratory, Chilton, Didcot, UK National Semiconductor Corp, Richardson, TX, USA New York University, New York, NY, USA 1

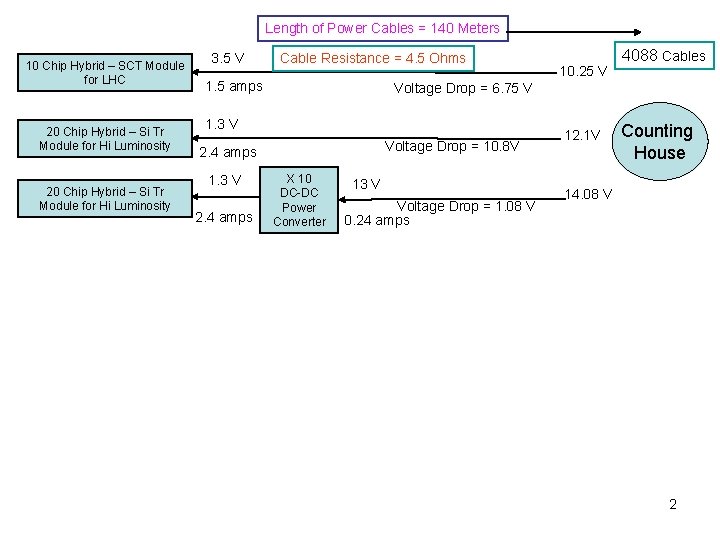

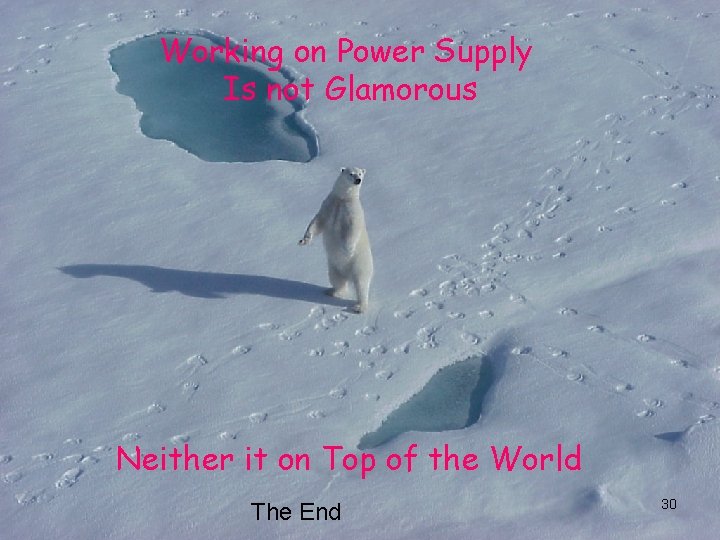

Length of Power Cables = 140 Meters 10 Chip Hybrid – SCT Module for LHC 20 Chip Hybrid – Si Tr Module for Hi Luminosity 3. 5 V Cable Resistance = 4. 5 Ohms 1. 5 amps Voltage Drop = 6. 75 V 1. 3 V Voltage Drop = 10. 8 V 2. 4 amps 1. 3 V 2. 4 amps 10. 25 V 4088 Cables X 10 DC-DC Power Converter 13 V Voltage Drop = 1. 08 V 0. 24 amps 12. 1 V Counting House 14. 08 V 2

Agenda §Learning from Commercial Devices § Buck > Voltage, EMI § Plug In Cards for ABCN 2. 5 Hybrids - Noise Tests @Liverpool § Require Radiation resistance & High Voltage operation § Thin Oxide § High Voltage with Thin Oxide ? § DMOS, Drain Extension 12 V @ 5 nm , 20 V @ 7 nm § HEMT has no Oxide – Higher Voltage ? 200 Mrads 20 V 3

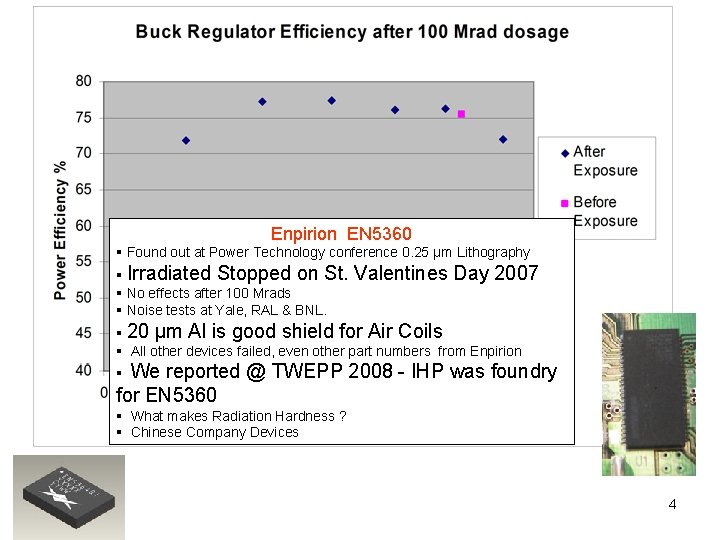

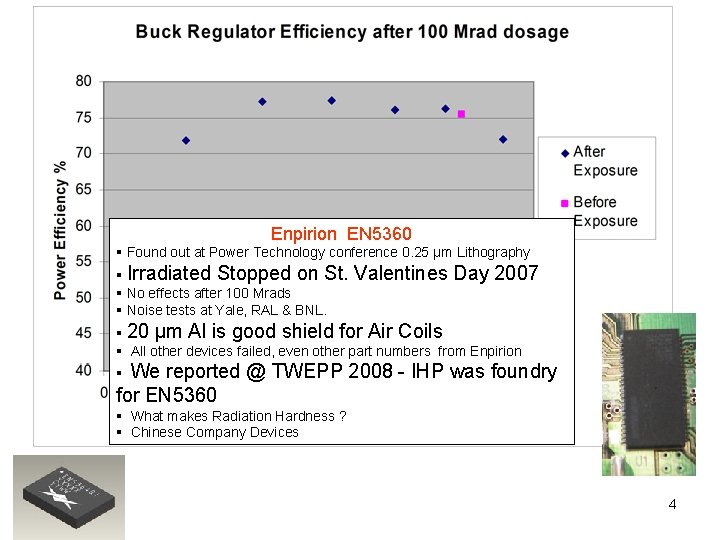

Enpirion EN 5360 § Found out at Power Technology conference 0. 25 µm Lithography § Irradiated Stopped on St. Valentines Day 2007 § No effects after 100 Mrads § Noise tests at Yale, RAL & BNL. § 20 µm Al is good shield for Air Coils § All other devices failed, even other part numbers from Enpirion § We reported @ TWEPP 2008 - IHP was foundry for EN 5360 § What makes Radiation Hardness ? § Chinese Company Devices 4

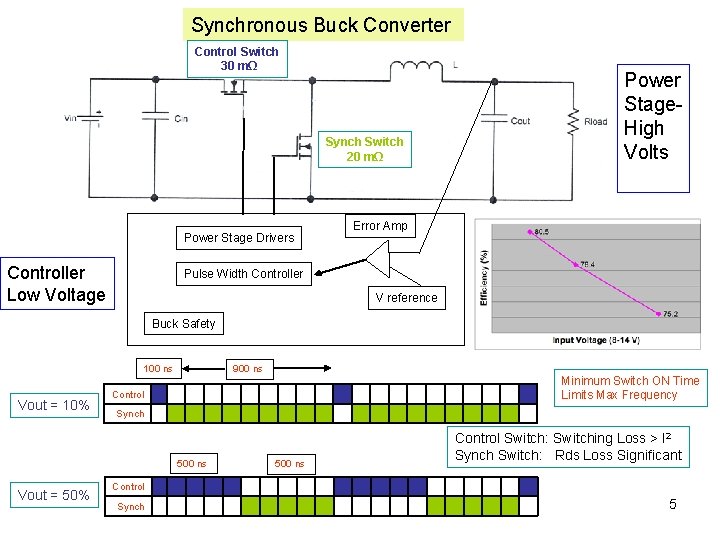

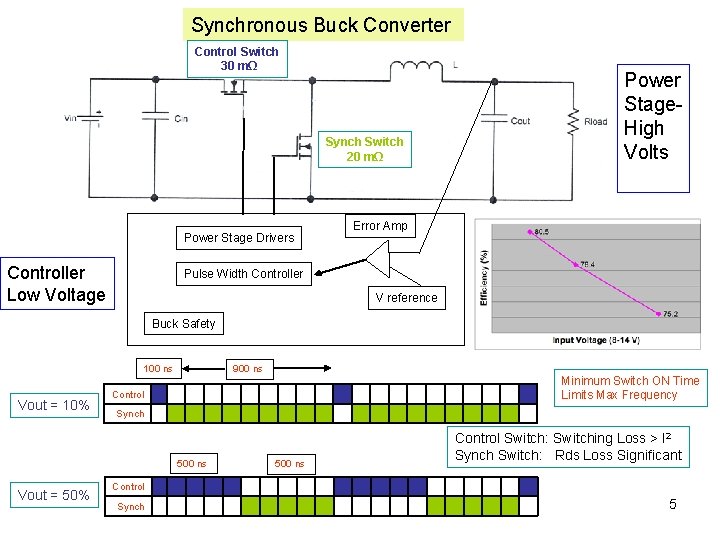

Synchronous Buck Converter Control Switch 30 mΩ Power Stage. High Volts Synch Switch 20 mΩ Error Amp Power Stage Drivers Controller Low Voltage Pulse Width Controller V reference Buck Safety 100 ns Vout = 10% 900 ns Control Synch 500 ns Vout = 50% Minimum Switch ON Time Limits Max Frequency Control Switch: Switching Loss > I 2 Synch Switch: Rds Loss Significant 500 ns Control Synch 5

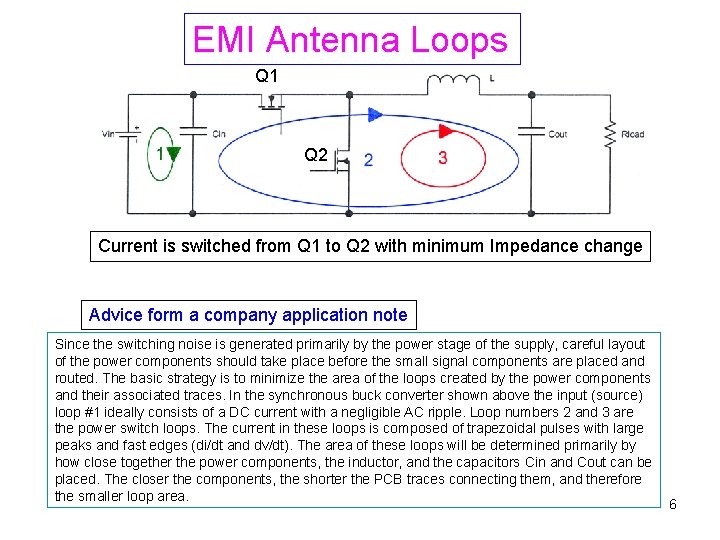

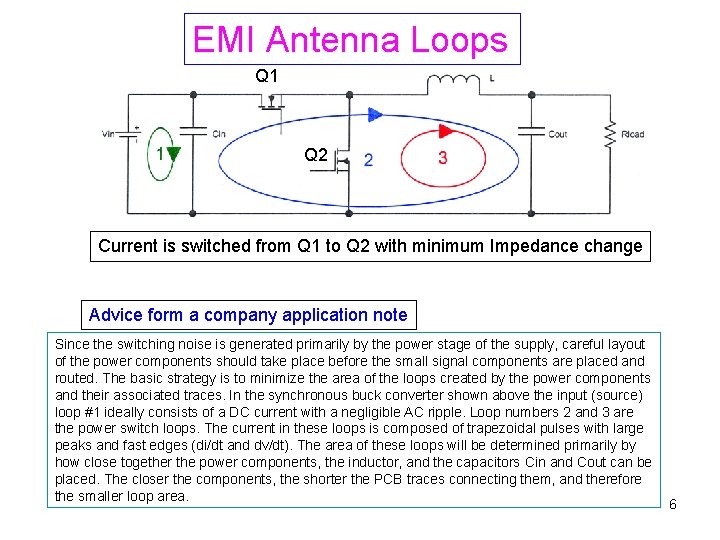

EMI Antenna Loops Control Switch Q 1 Q 2 Current is switched from Q 1 to Q 2 with minimum Impedance change Advice form a company application note Since the switching noise is generated primarily by the power stage of the supply, careful layout of the power components should take place before the small signal components are placed and routed. The basic strategy is to minimize the area of the loops created by the power components and their associated traces. In the synchronous buck converter shown above the input (source) loop #1 ideally consists of a DC current with a negligible AC ripple. Loop numbers 2 and 3 are the power switch loops. The current in these loops is composed of trapezoidal pulses with large peaks and fast edges (di/dt and dv/dt). The area of these loops will be determined primarily by how close together the power components, the inductor, and the capacitors Cin and Cout can be placed. The closer the components, the shorter the PCB traces connecting them, and therefore the smaller loop area. 6

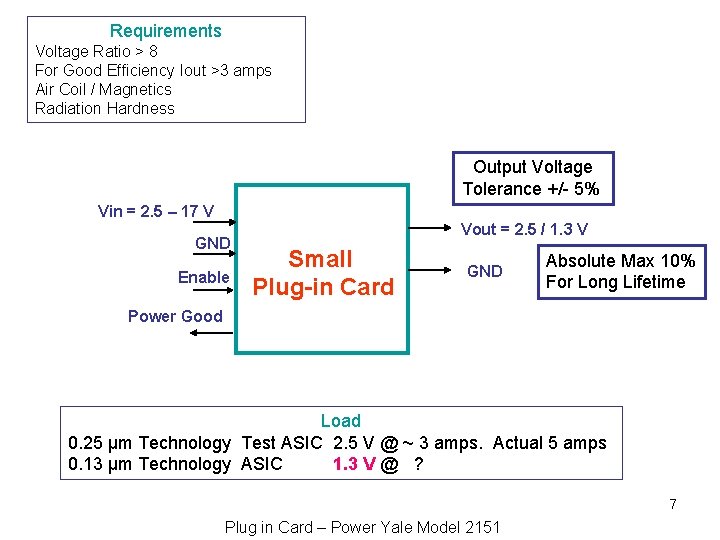

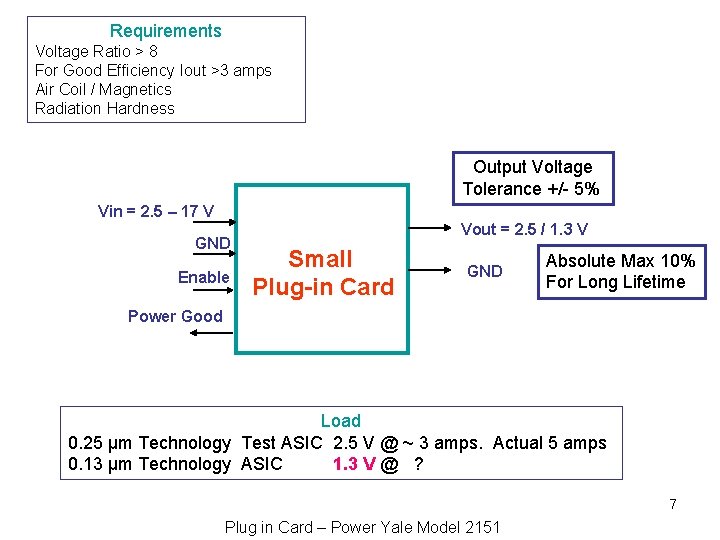

Requirements Voltage Ratio > 8 For Good Efficiency Iout >3 amps Air Coil / Magnetics Radiation Hardness Output Voltage Tolerance +/- 5% Vin = 2. 5 – 17 V GND Enable Vout = 2. 5 / 1. 3 V Small Plug-in Card GND Absolute Max 10% For Long Lifetime Power Good Load 0. 25 µm Technology Test ASIC 2. 5 V @ ~ 3 amps. Actual 5 amps 0. 13 µm Technology ASIC 1. 3 V @ ? 7 Plug in Card – Power Yale Model 2151

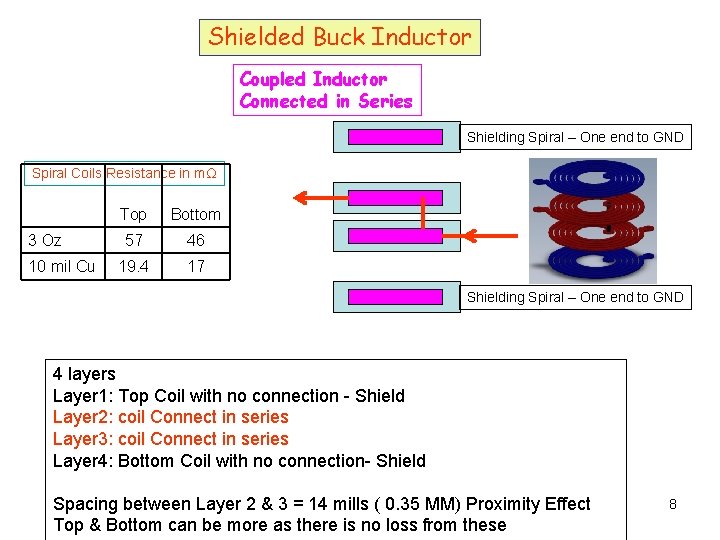

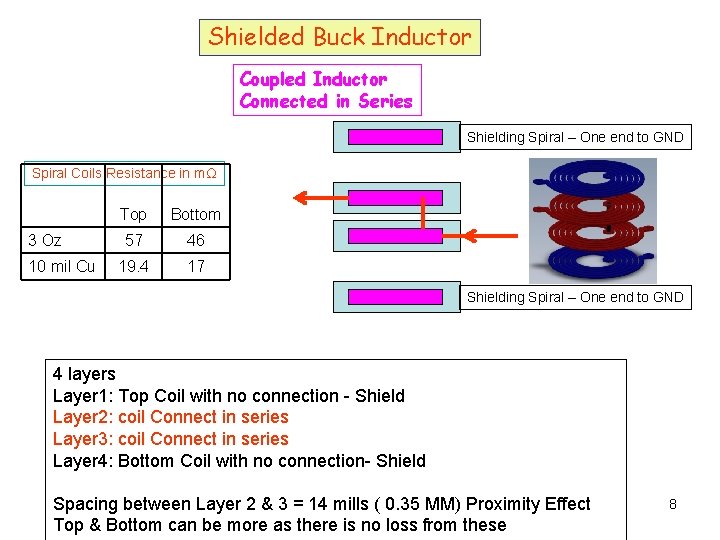

Shielded Buck Inductor Coupled Inductor Connected in Series Shielding Spiral – One end to GND Spiral Coils Resistance in mΩ 3 Oz 10 mil Cu Top Bottom 57 46 19. 4 17 Shielding Spiral – One end to GND 4 layers Layer 1: Top Coil with no connection - Shield Layer 2: coil Connect in series Layer 3: coil Connect in series Layer 4: Bottom Coil with no connection- Shield Spacing between Layer 2 & 3 = 14 mills ( 0. 35 MM) Proximity Effect Top & Bottom can be more as there is no loss from these 8

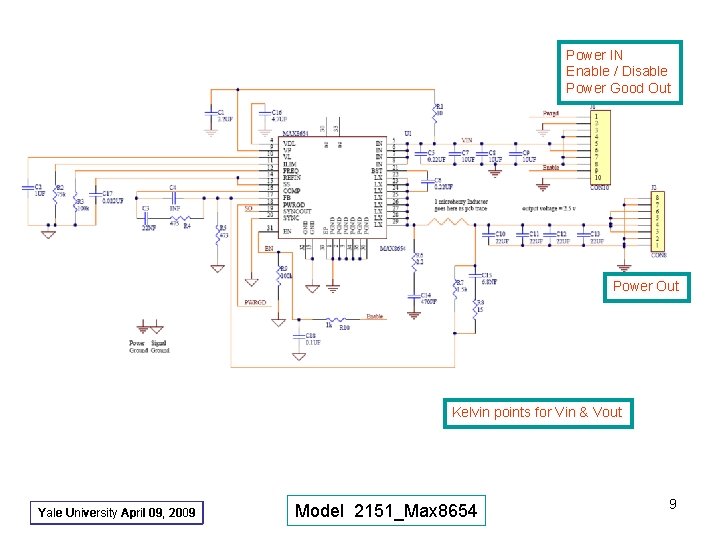

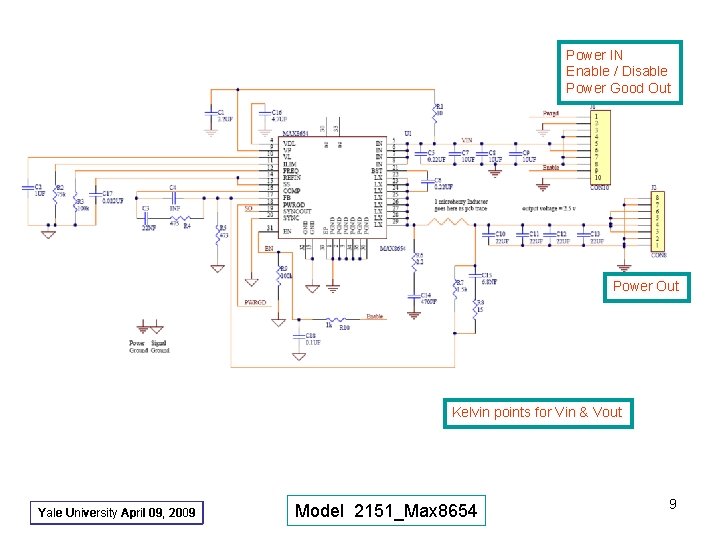

Power IN Enable / Disable Power Good Out Power Out Kelvin points for Vin & Vout Yale University April 09, 2009 Model 2151_Max 8654 9

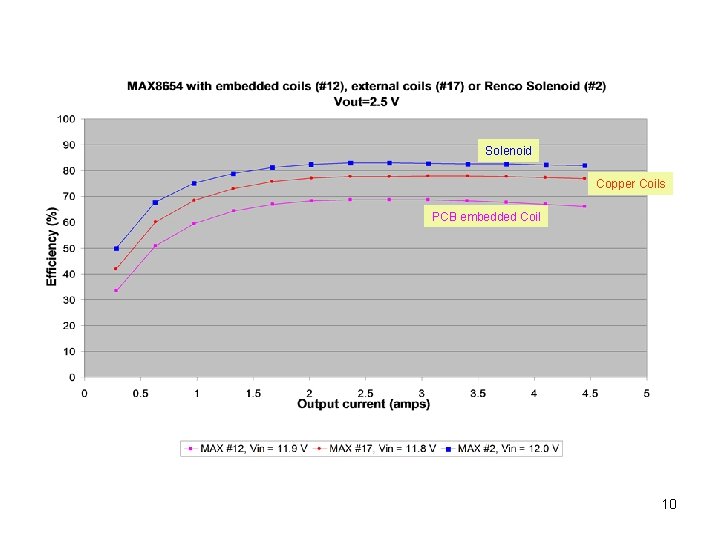

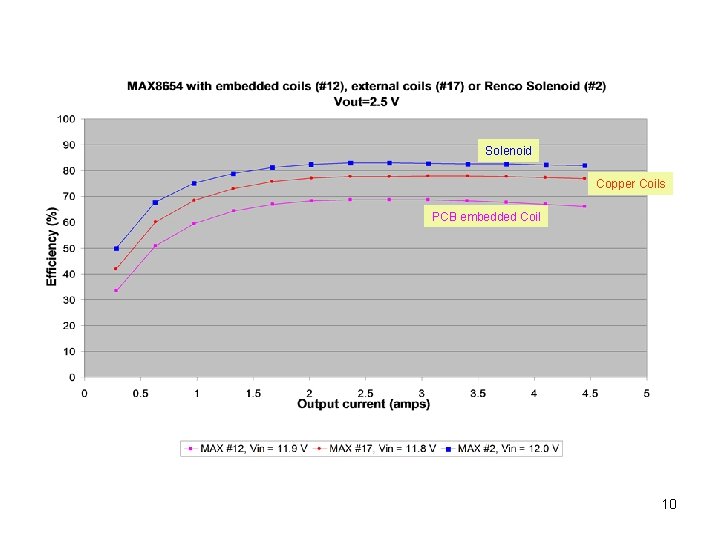

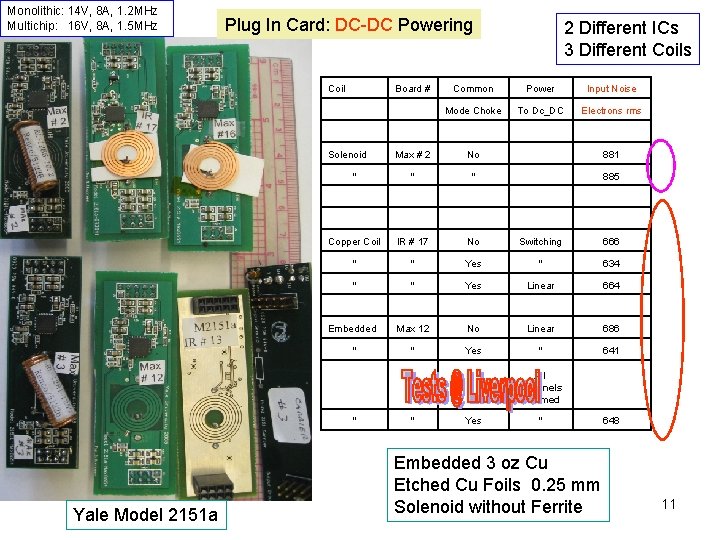

Solenoid Copper Coils PCB embedded Coil 10

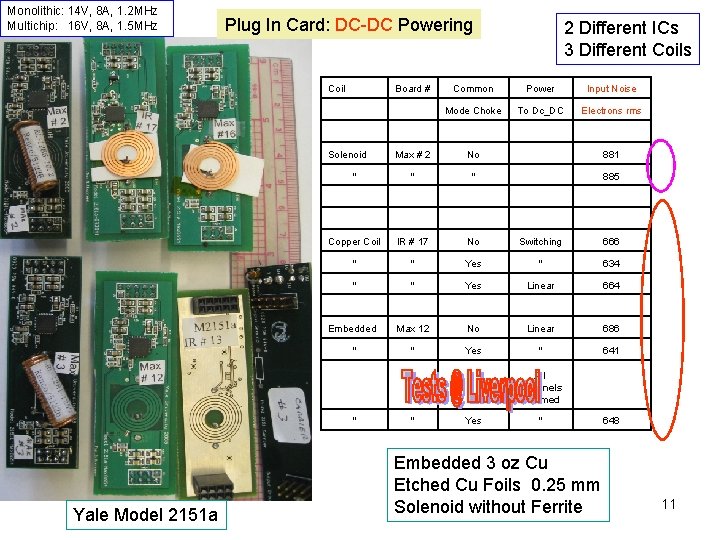

Monolithic: 14 V, 8 A, 1. 2 MHz Multichip: 16 V, 8 A, 1. 5 MHz Plug In Card: DC-DC Powering Coil Board # Common Power Input Noise Mode Choke To Dc_DC Electrons rms Max # 2 No 881 " " 885 Copper Coil IR # 17 No Switching 666 " " Yes " 634 " " Yes Linear 664 Embedded Max 12 No Linear 686 " " Yes " 641 648 Solenoid " Yale Model 2151 a 2 Different ICs 3 Different Coils All Channels Trimmed " " Yes " Embedded 3 oz Cu Etched Cu Foils 0. 25 mm Solenoid without Ferrite 11

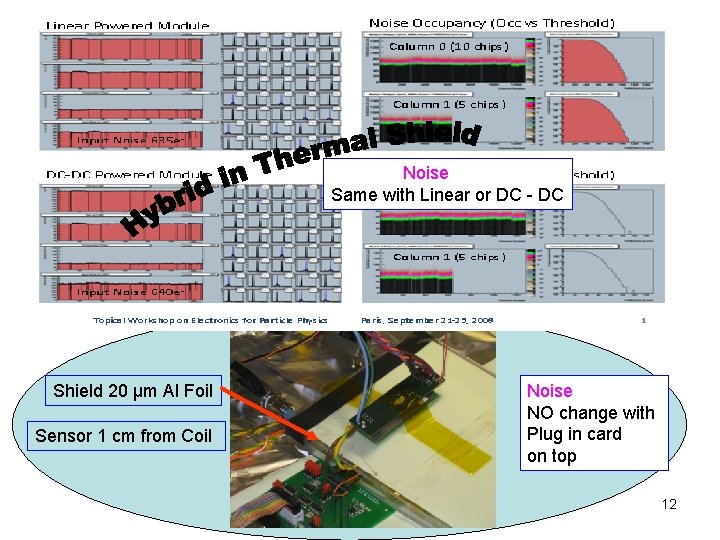

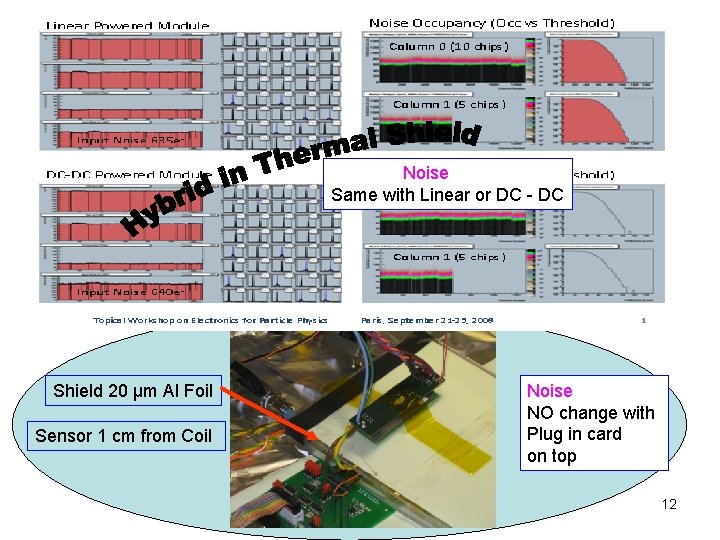

Noise Same with Linear or DC - DC Shield 20 µm Al Foil Sensor 1 cm from Coil Noise NO change with Plug in card on top 12

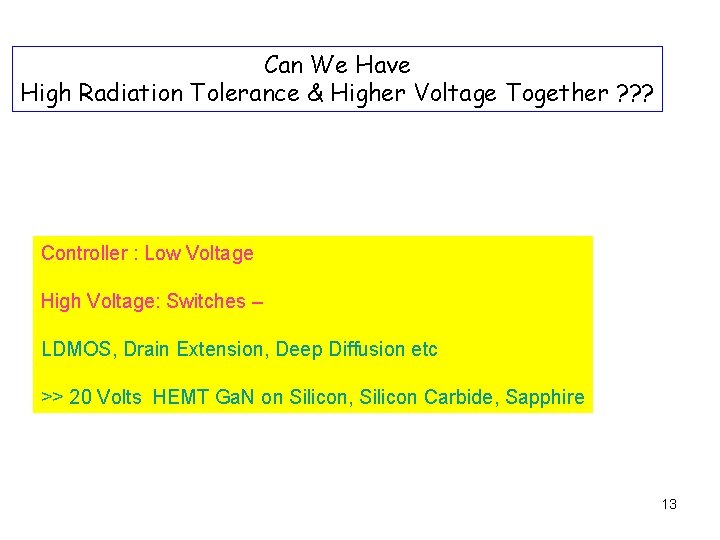

Can We Have High Radiation Tolerance & Higher Voltage Together ? ? ? Controller : Low Voltage High Voltage: Switches – LDMOS, Drain Extension, Deep Diffusion etc >> 20 Volts HEMT Ga. N on Silicon, Silicon Carbide, Sapphire 13

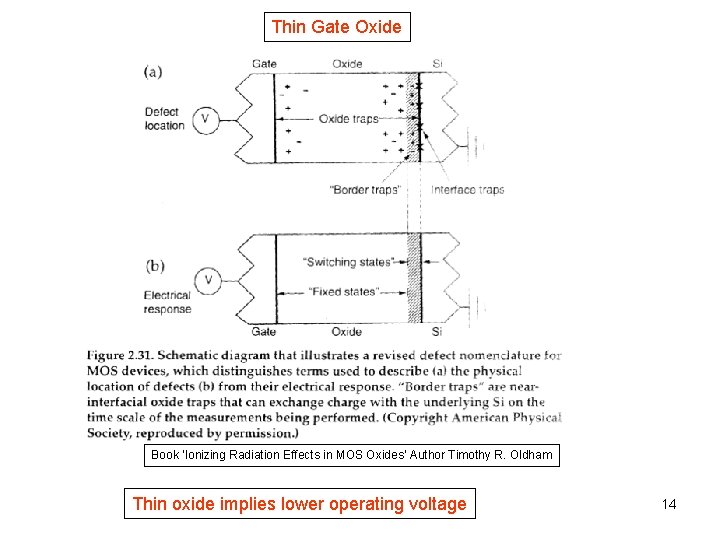

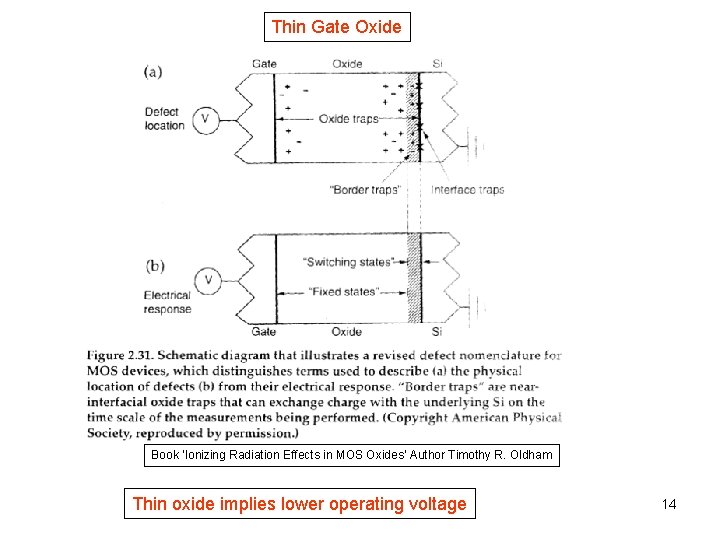

Thin Gate Oxide Book ‘Ionizing Radiation Effects in MOS Oxides’ Author Timothy R. Oldham Thin oxide implies lower operating voltage 14

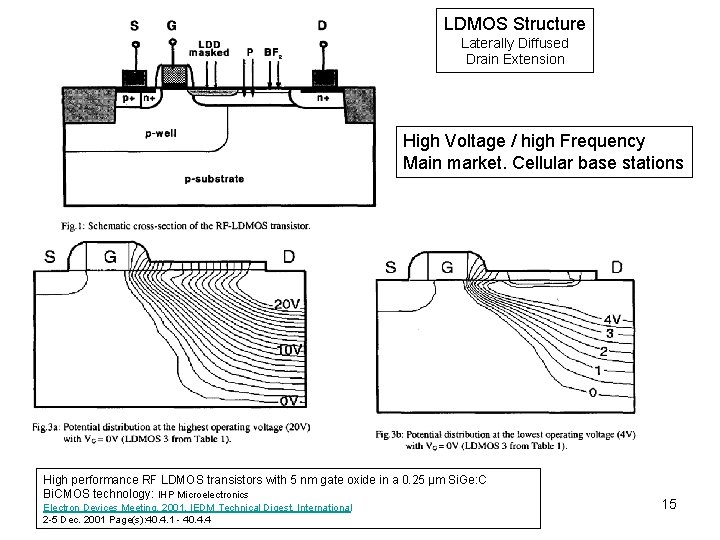

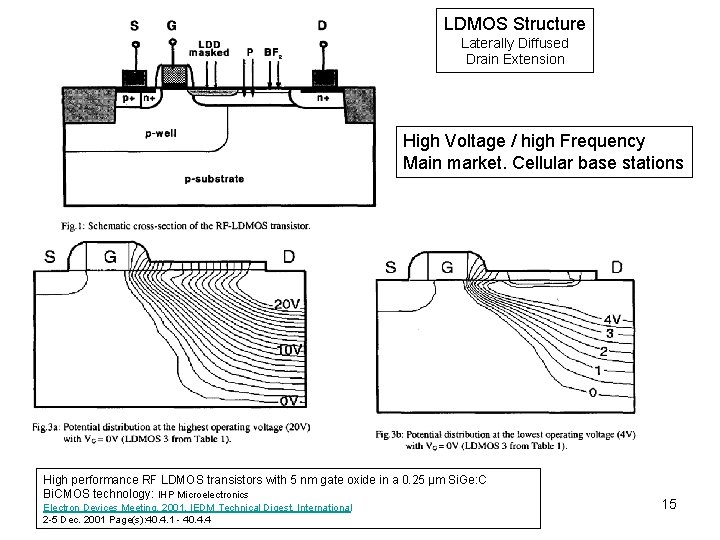

LDMOS Structure Laterally Diffused Drain Extension High Voltage / high Frequency Main market. Cellular base stations High performance RF LDMOS transistors with 5 nm gate oxide in a 0. 25 μm Si. Ge: C Bi. CMOS technology: IHP Microelectronics Electron Devices Meeting, 2001. IEDM Technical Digest. International 2 -5 Dec. 2001 Page(s): 40. 4. 1 - 40. 4. 4 15

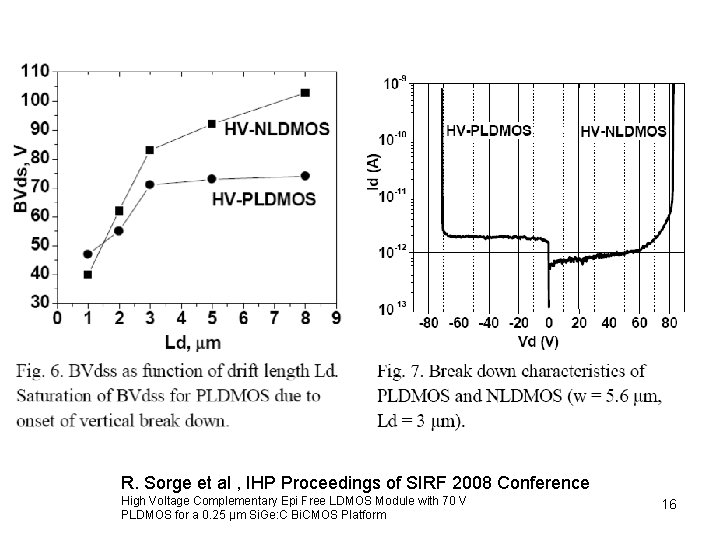

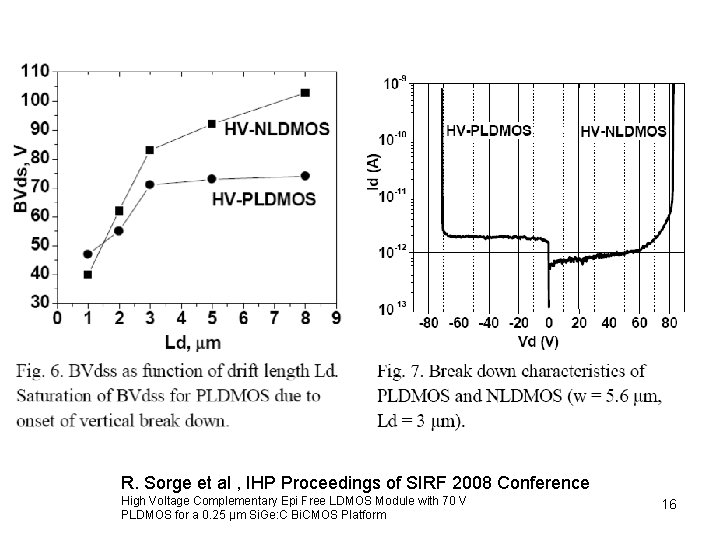

R. Sorge et al , IHP Proceedings of SIRF 2008 Conference High Voltage Complementary Epi Free LDMOS Module with 70 V PLDMOS for a 0. 25 μm Si. Ge: C Bi. CMOS Platform 16

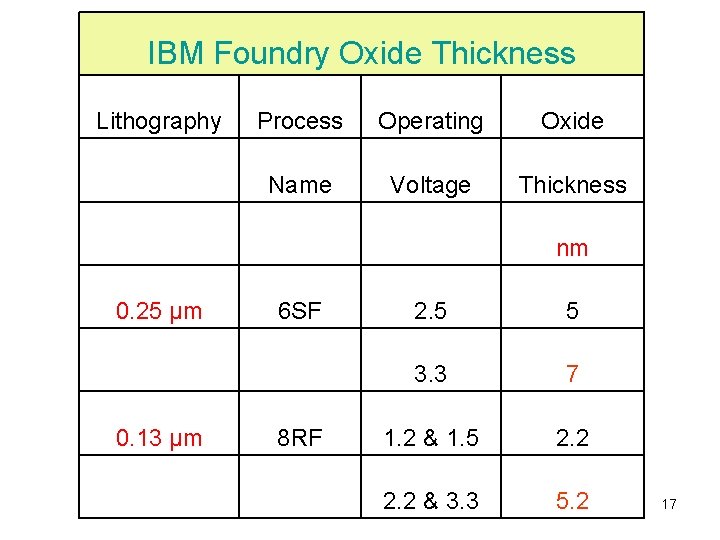

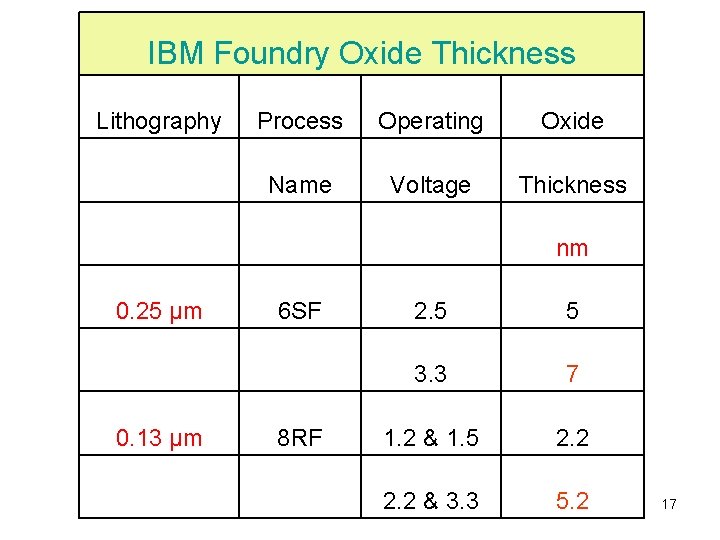

IBM Foundry Oxide Thickness Lithography Process Operating Oxide Name Voltage Thickness 0. 25 µm 0. 13 µm nm 6 SF 2. 5 5 3. 3 7 8 RF 1. 2 & 1. 5 2. 2 & 3. 3 5. 2 17

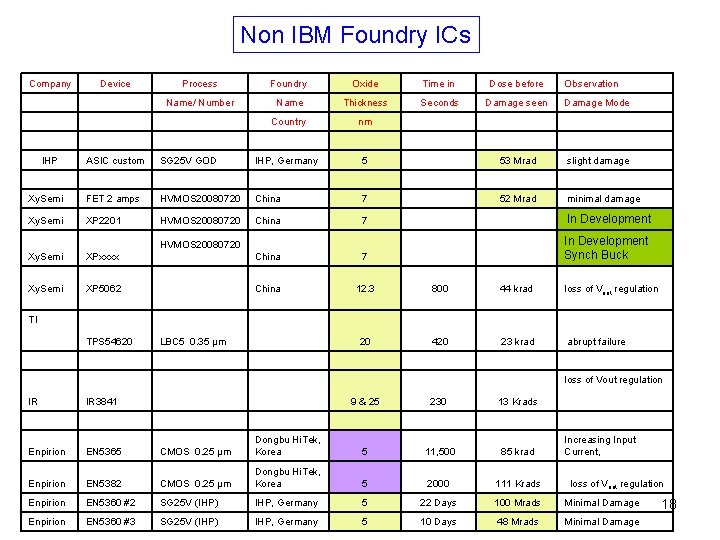

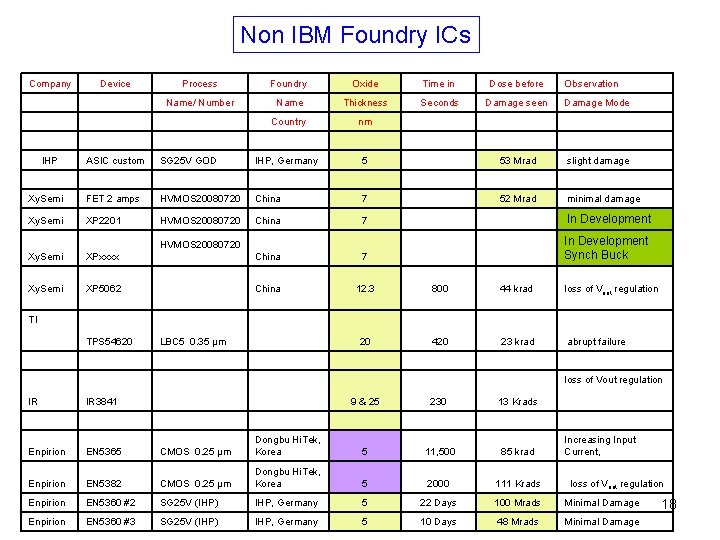

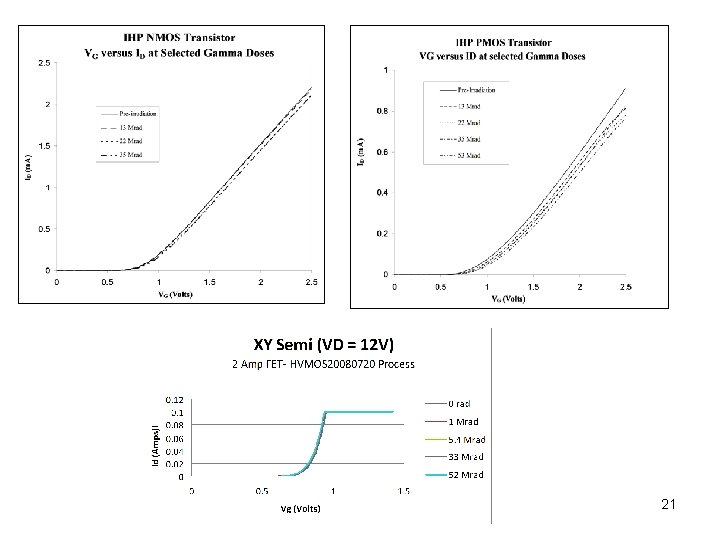

Non IBM Foundry ICs Company Device Process Foundry Oxide Time in Dose before Observation Name/ Number Name Thickness Seconds Damage seen nm Country ASIC custom SG 25 V GOD IHP, Germany 5 53 Mrad Xy. Semi FET 2 amps HVMOS 20080720 China 7 52 Mrad Xy. Semi XP 2201 HVMOS 20080720 China 7 In Development Xy. Semi XPxxxx HVMOS 20080720 China 7 In Development Synch Buck Xy. Semi XP 5062 China TPS 54620 LBC 5 0. 35 µm IHP Damage Mode slight damage minimal damage 12. 3 800 44 krad loss of Vout regulation 20 420 23 krad abrupt failure TI loss of Vout regulation IR IR 3841 Enpirion EN 5365 CMOS 0. 25 µm Dongbu Hi. Tek, Korea Enpirion EN 5382 CMOS 0. 25 µm Enpirion EN 5360 #2 Enpirion EN 5360 #3 9 & 25 230 13 Krads 5 11, 500 85 krad Dongbu Hi. Tek, Korea 5 2000 111 Krads loss of Vout regulation SG 25 V (IHP) IHP, Germany 5 22 Days 100 Mrads Minimal Damage SG 25 V (IHP) IHP, Germany 5 10 Days 48 Mrads Minimal Damage Increasing Input Current, 18

For Higher Radiation Resistance v Oxide Thickness is predominant Effect v Others Epi Free processing is Good ? v Oxide Processing is standard v ? ? ? 19

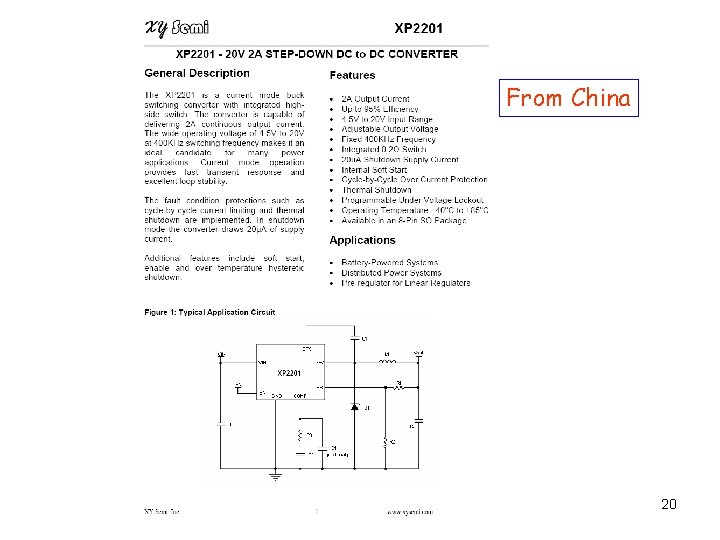

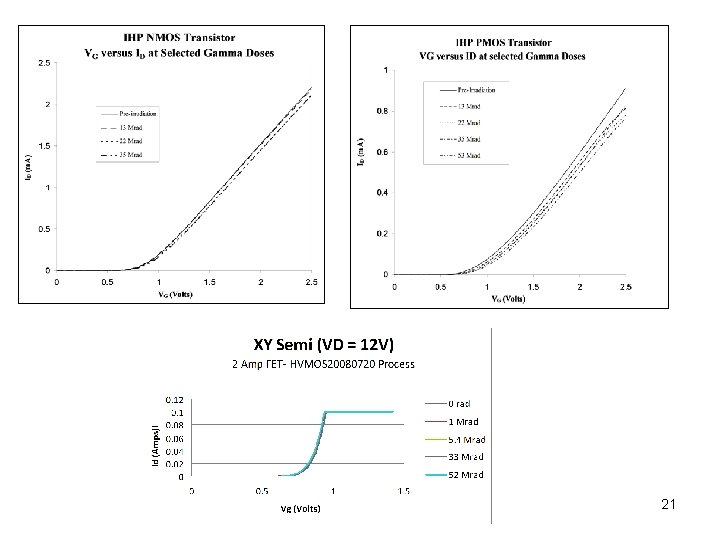

From China 20

21

Depletion Mode Normally ON Enhancement Mode Normally OFF 22

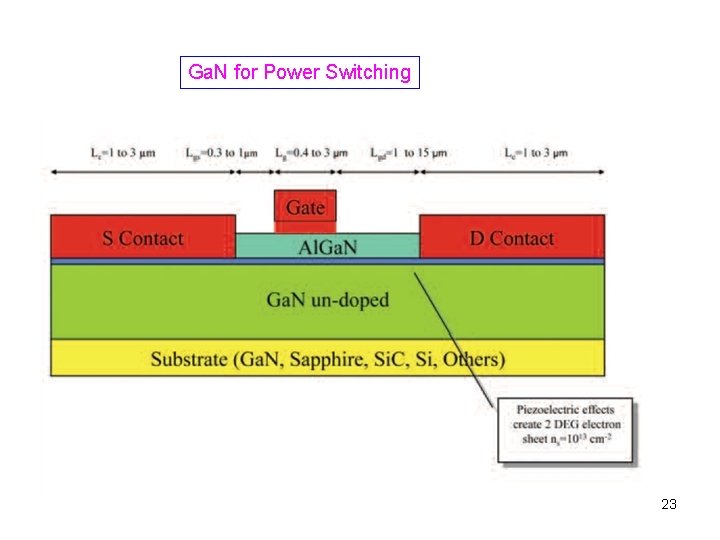

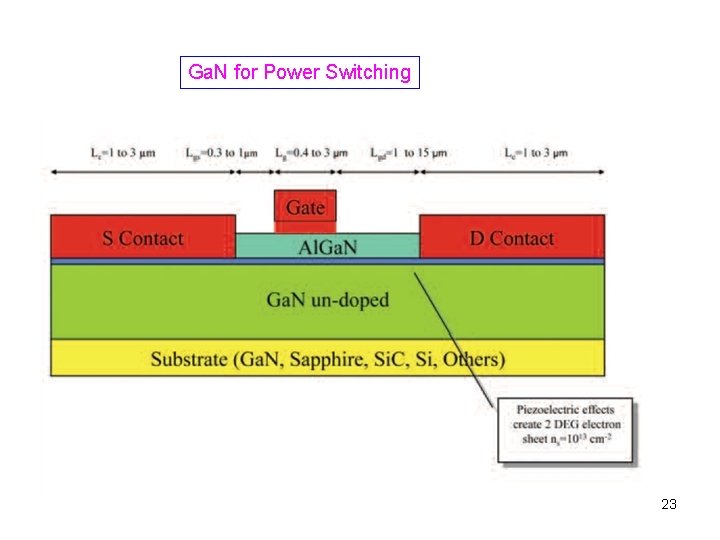

Ga. N for Power Switching 23

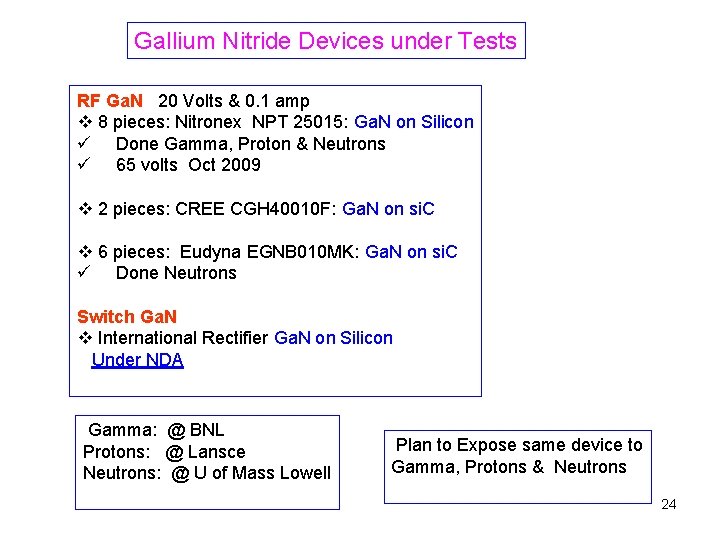

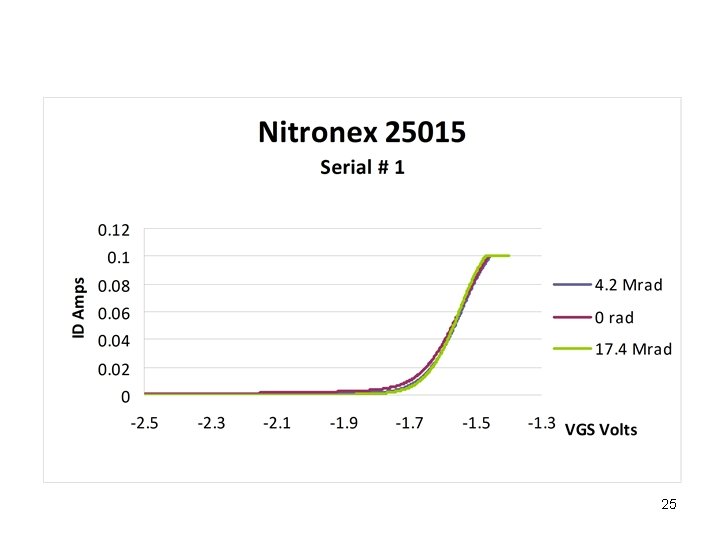

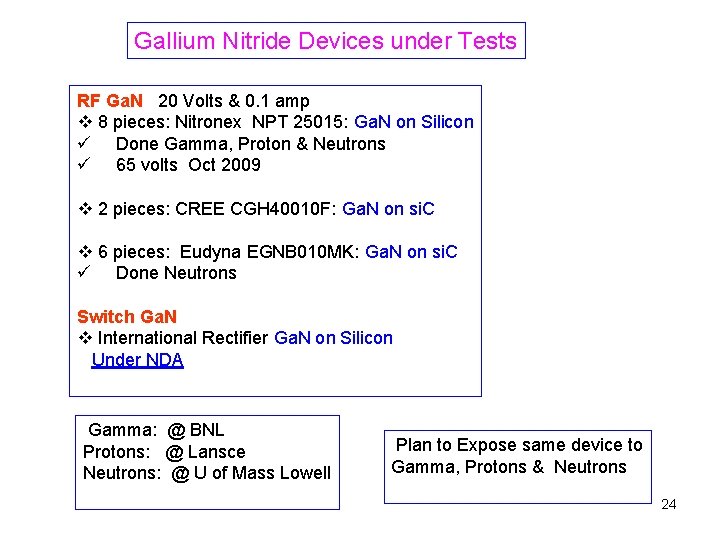

Gallium Nitride Devices under Tests RF Ga. N 20 Volts & 0. 1 amp v 8 pieces: Nitronex NPT 25015: Ga. N on Silicon ü Done Gamma, Proton & Neutrons ü 65 volts Oct 2009 v 2 pieces: CREE CGH 40010 F: Ga. N on si. C v 6 pieces: Eudyna EGNB 010 MK: Ga. N on si. C ü Done Neutrons Switch Ga. N v International Rectifier Ga. N on Silicon Under NDA Gamma: @ BNL Protons: @ Lansce Neutrons: @ U of Mass Lowell Plan to Expose same device to Gamma, Protons & Neutrons 24

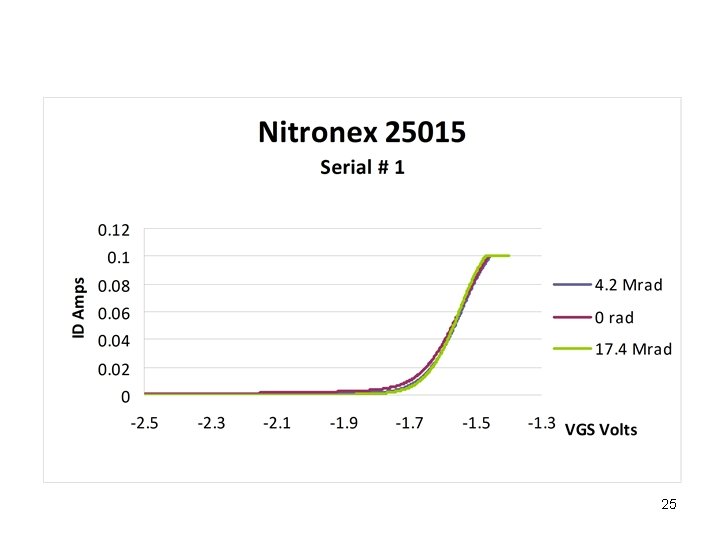

25

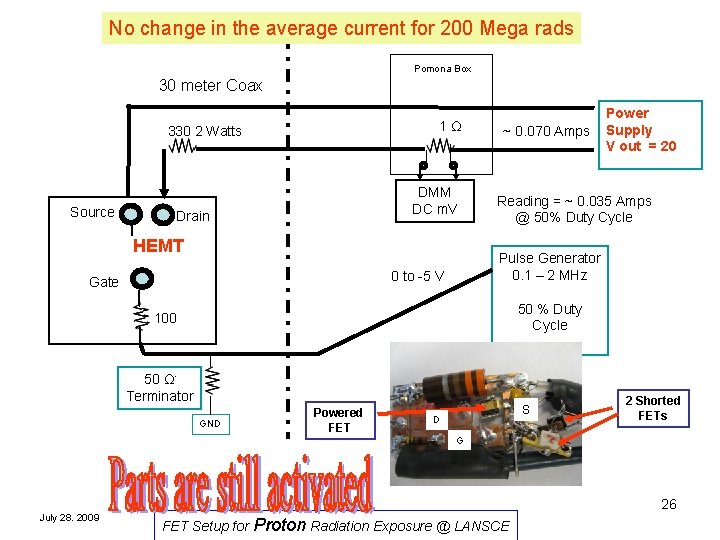

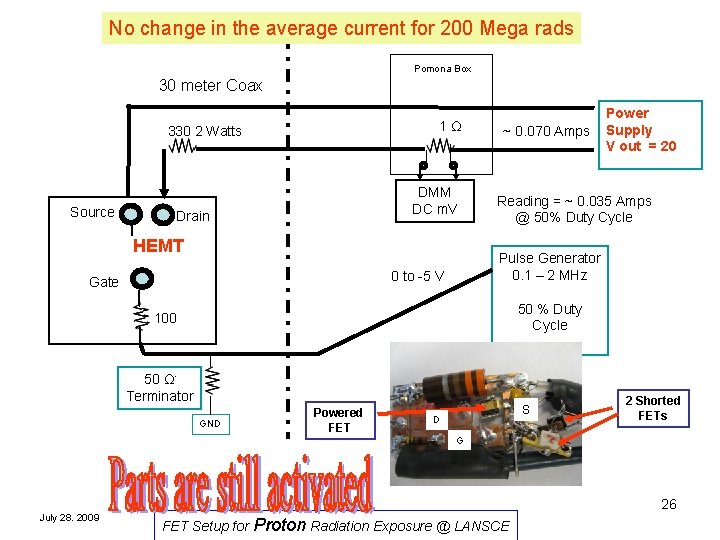

No change in the average current for 200 Mega rads Pomona Box 30 meter Coax 1 Ω 330 2 Watts Source DMM DC m. V Drain HEMT Reading = ~ 0. 035 Amps @ 50% Duty Cycle Pulse Generator 0. 1 – 2 MHz 0 to -5 V Gate ~ 0. 070 Amps Power Supply V out = 20 50 % Duty Cycle 100 . 50 Ω Terminator GND Powered FET S D 2 Shorted FETs G 26 July 28. 2009 FET Setup for Proton Radiation Exposure @ LANSCE

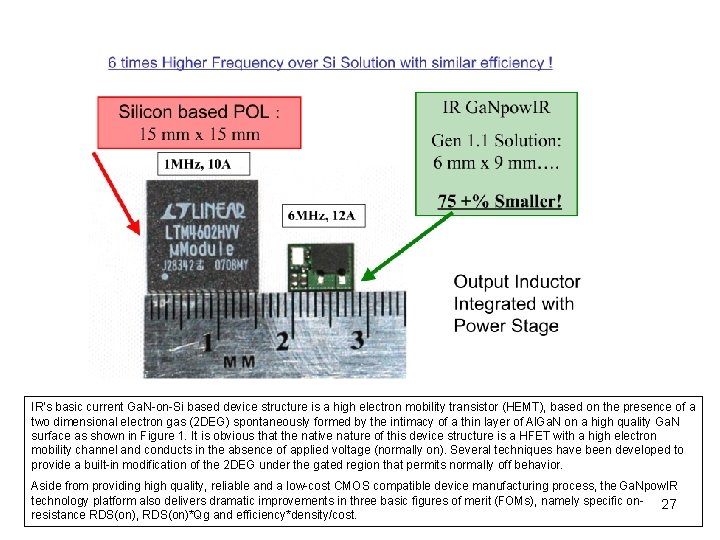

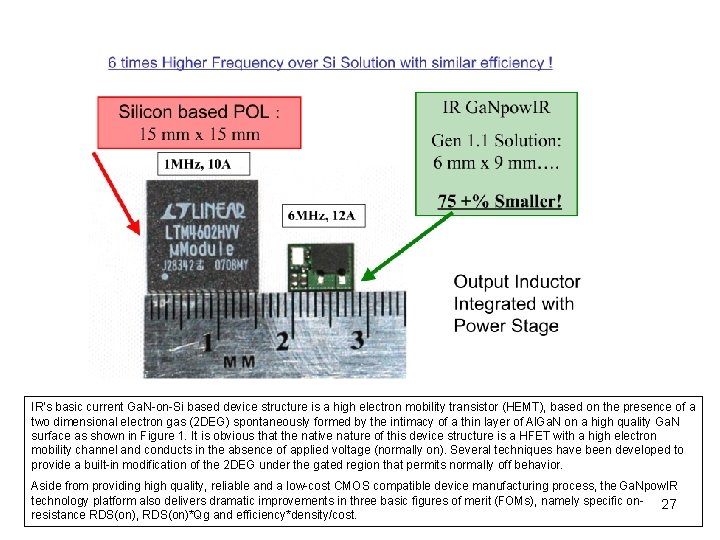

IR’s basic current Ga. N-on-Si based device structure is a high electron mobility transistor (HEMT), based on the presence of a two dimensional electron gas (2 DEG) spontaneously formed by the intimacy of a thin layer of Al. Ga. N on a high quality Ga. N surface as shown in Figure 1. It is obvious that the native nature of this device structure is a HFET with a high electron mobility channel and conducts in the absence of applied voltage (normally on). Several techniques have been developed to provide a built-in modification of the 2 DEG under the gated region that permits normally off behavior. Aside from providing high quality, reliable and a low-cost CMOS compatible device manufacturing process, the Ga. Npow. IR technology platform also delivers dramatic improvements in three basic figures of merit (FOMs), namely specific on- 27 resistance RDS(on), RDS(on)*Qg and efficiency*density/cost.

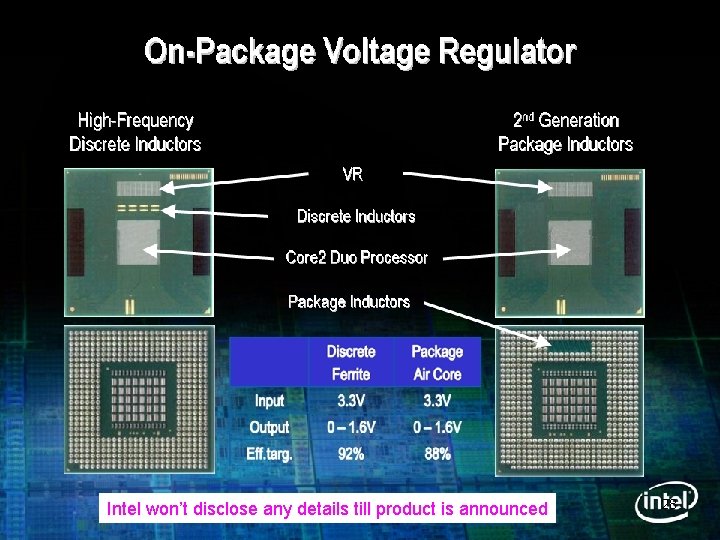

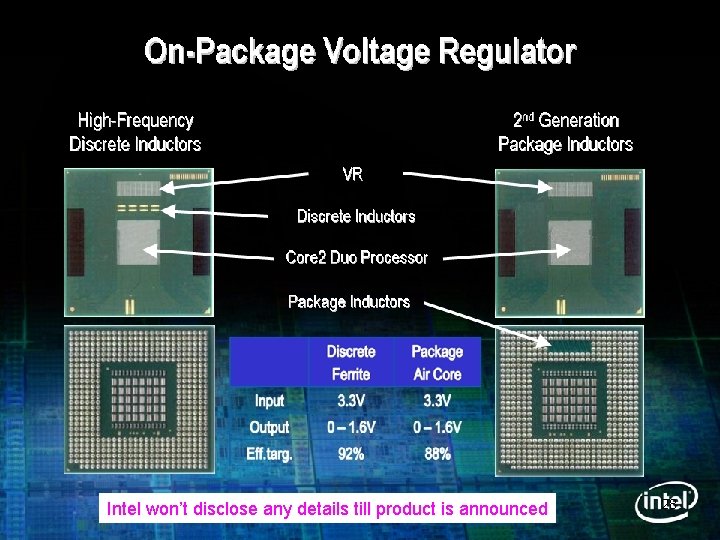

Intel won’t disclose any details till product is announced 28

Conclusions v. Learned from commercial Devices, Companies & Power conferences v Can get high Radiation Tolerance & Higher Voltage v. High Frequency > Smaller Air coil > Less Material v Goal: ~20 MHz Buck, MEM on Chip size 9 mm x 9 mm v. Power SOC: MEMs Air Core Inductor on Chip v Study Feasibility 48 / 300 V Converters v. Irradiation: Run @ Max operating V & I. v. Limit Power Dissipation by Switching duty cycle v. Online Monitoring during irradiation for faster results v. Yale Plug Cards can be loaned for Evaluation v. Collaborators are Welcome 29

Working on Power Supply Is not Glamorous Neither it on Top of the World The End 30