Programowanie Procesorw Sygnaowych Krzysztof Bikonis binioeti pg gda

Programowanie Procesorów Sygnałowych Krzysztof Bikonis binio@eti. pg. gda. pl p. 738 tel. 347 1326

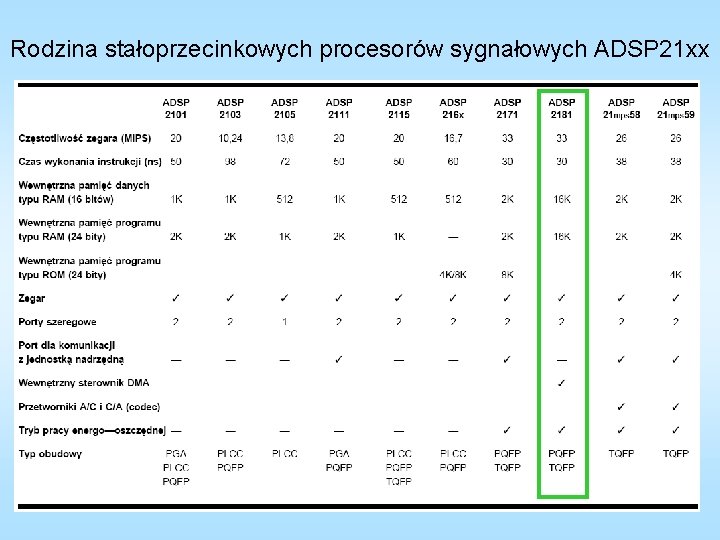

Tematyka zajęć • • Procesory stałoprzecinkowe rodziny ADSP-21 xx Procesory zmiennoprzecinkowe rodziny ADSP-21 k Środowisko programistyczne (symulacja, kompilacja, uruchamianie) Praca w grupach z zestawami - ADSP-2181 EZ-LAB x 5

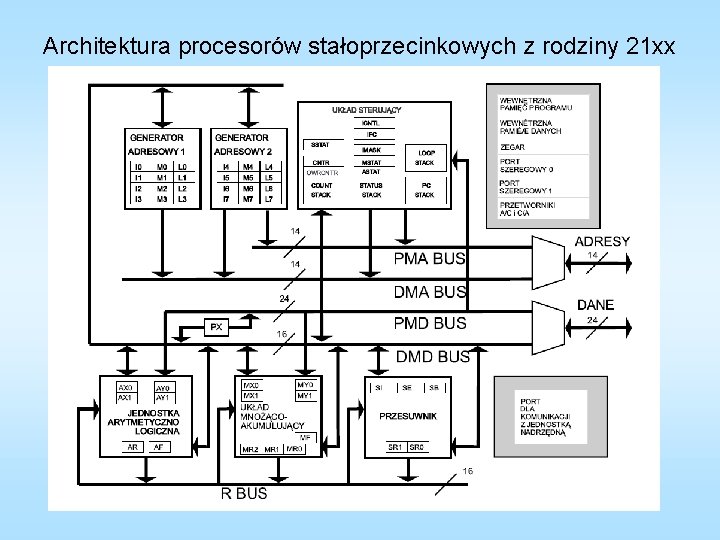

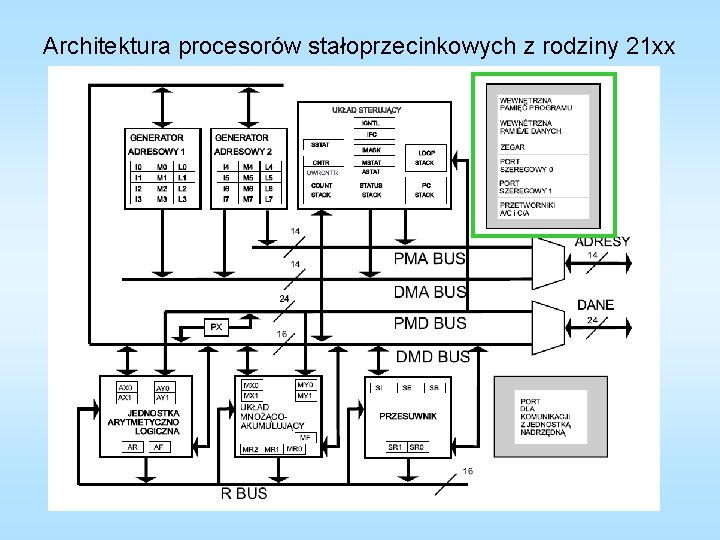

Architektura procesorów stałoprzecinkowych z rodziny 21 xx

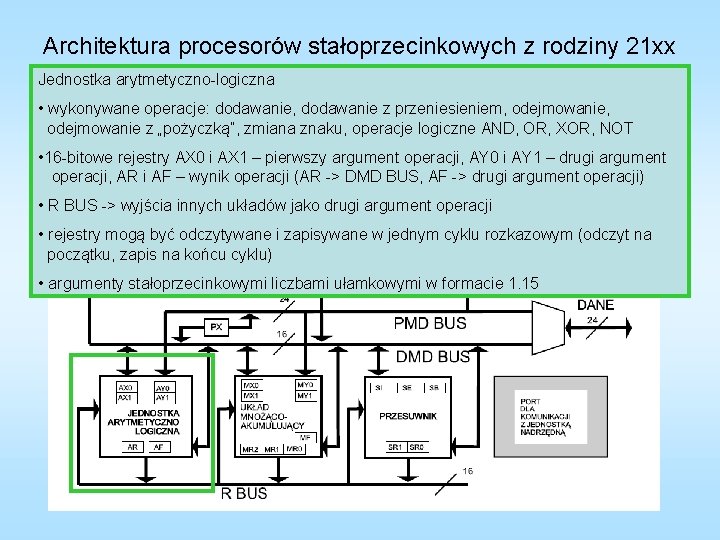

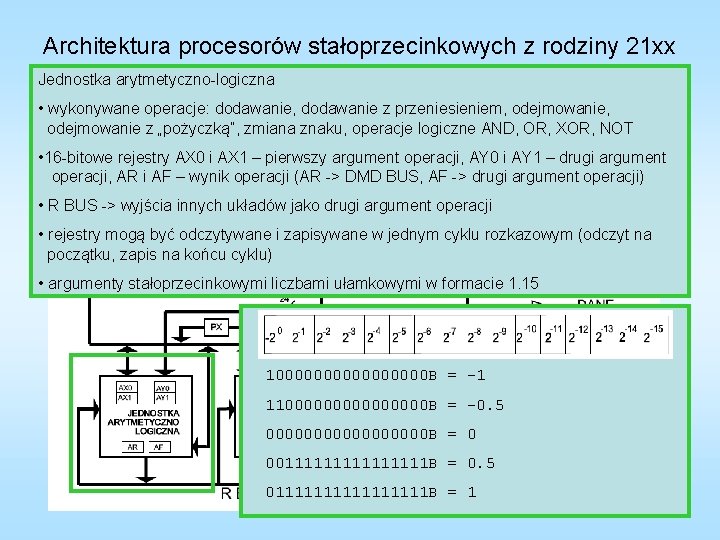

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Jednostka arytmetyczno-logiczna • wykonywane operacje: dodawanie, dodawanie z przeniesieniem, odejmowanie z „pożyczką”, zmiana znaku, operacje logiczne AND, OR, XOR, NOT • 16 -bitowe rejestry AX 0 i AX 1 – pierwszy argument operacji, AY 0 i AY 1 – drugi argument operacji, AR i AF – wynik operacji (AR -> DMD BUS, AF -> drugi argument operacji) • R BUS -> wyjścia innych układów jako drugi argument operacji • rejestry mogą być odczytywane i zapisywane w jednym cyklu rozkazowym (odczyt na początku, zapis na końcu cyklu) • argumenty stałoprzecinkowymi liczbami ułamkowymi w formacie 1. 15

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Jednostka arytmetyczno-logiczna • wykonywane operacje: dodawanie, dodawanie z przeniesieniem, odejmowanie z „pożyczką”, zmiana znaku, operacje logiczne AND, OR, XOR, NOT • 16 -bitowe rejestry AX 0 i AX 1 – pierwszy argument operacji, AY 0 i AY 1 – drugi argument operacji, AR i AF – wynik operacji (AR -> DMD BUS, AF -> drugi argument operacji) • R BUS -> wyjścia innych układów jako drugi argument operacji • rejestry mogą być odczytywane i zapisywane w jednym cyklu rozkazowym (odczyt na początku, zapis na końcu cyklu) • argumenty stałoprzecinkowymi liczbami ułamkowymi w formacie 1. 15 100000000 B = -1 1100000000 B = -0. 5 000000000 B = 0 0011111111 B = 0. 5 011111111 B = 1

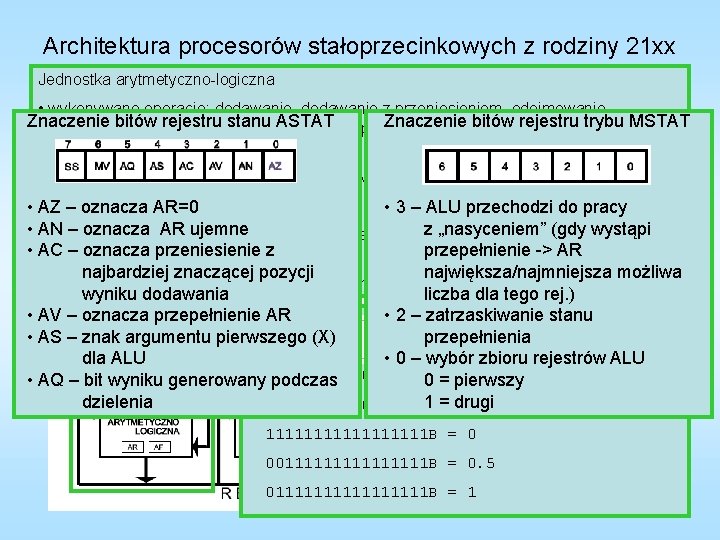

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Jednostka arytmetyczno-logiczna • wykonywane operacje: dodawanie, dodawanie z przeniesieniem, odejmowanie, Znaczenie bitów rejestru stanu ASTAT Znaczenie trybu odejmowanie z „pożyczką”, zmiana znaku, operacje logicznebitów AND, rejestru OR, XOR, NOTMSTAT • 16 -bitowe rejestry AX 0 i AX 1 – pierwszy argument operacji, AY 0 i AY 1 – drugi argument operacji, AR i AF – wynik operacji (AR -> DMD BUS, AF -> drugi argument operacji) R BUS -> wyjścia innych układów jako drugi argument operacji • • AZ – oznacza AR=0 • 3 – ALU przechodzi do pracy • • AN – oznacza ARodczytywane ujemne i zapisywane w jednym z „nasyceniem” (gdy(odczyt wystąpi rejestry mogą być cyklu rozkazowym na • AC – oznacza przepełnienie -> AR początku, zapisprzeniesienie na końcu cyklu)z najbardziej znaczącej pozycji największa/najmniejsza możliwa • argumenty stałoprzecinkowymi liczbami ułamkowymi w formacie 1. 15 wyniku dodawania liczba dla tego rej. ) • AV – oznacza przepełnienie AR • 2 – zatrzaskiwanie stanu • AS – znak argumentu pierwszego (X) przepełnienia dla ALU • 0 – wybór zbioru rejestrów ALU -1 • AQ – bit wyniku generowany 100000000 B podczas 0 ==pierwszy dzielenia 1 ==drugi 1100000000 B -0. 5 111111111 B = 0 0011111111 B = 0. 5 011111111 B = 1

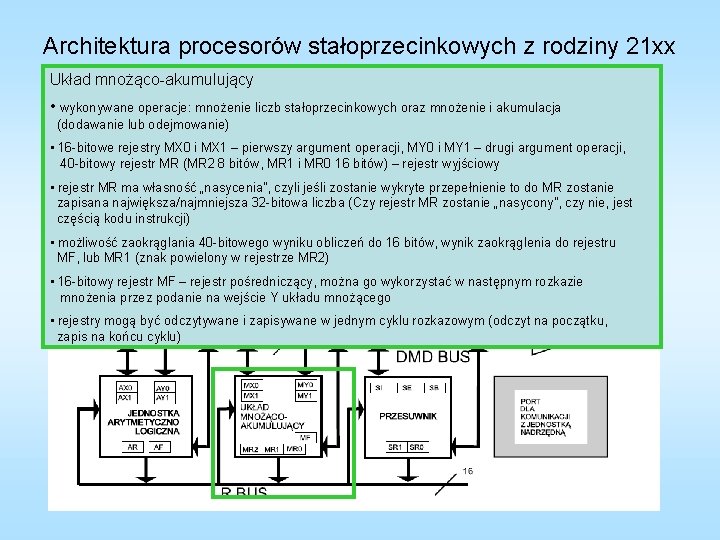

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Układ mnożąco-akumulujący • wykonywane operacje: mnożenie liczb stałoprzecinkowych oraz mnożenie i akumulacja (dodawanie lub odejmowanie) • 16 -bitowe rejestry MX 0 i MX 1 – pierwszy argument operacji, MY 0 i MY 1 – drugi argument operacji, 40 -bitowy rejestr MR (MR 2 8 bitów, MR 1 i MR 0 16 bitów) – rejestr wyjściowy • rejestr MR ma własność „nasycenia”, czyli jeśli zostanie wykryte przepełnienie to do MR zostanie zapisana największa/najmniejsza 32 -bitowa liczba (Czy rejestr MR zostanie „nasycony”, czy nie, jest częścią kodu instrukcji) • możliwość zaokrąglania 40 -bitowego wyniku obliczeń do 16 bitów, wynik zaokrąglenia do rejestru MF, lub MR 1 (znak powielony w rejestrze MR 2) • 16 -bitowy rejestr MF – rejestr pośredniczący, można go wykorzystać w następnym rozkazie mnożenia przez podanie na wejście Y układu mnożącego • rejestry mogą być odczytywane i zapisywane w jednym cyklu rozkazowym (odczyt na początku, zapis na końcu cyklu)

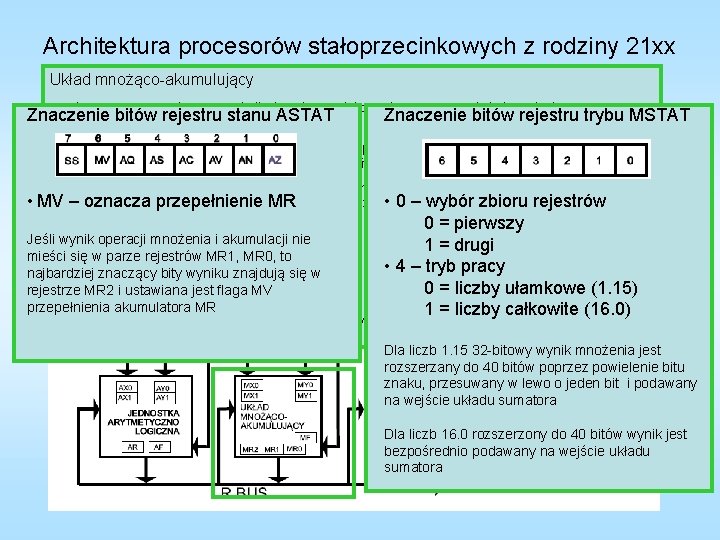

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Układ mnożąco-akumulujący • wykonywane operacje: mnożenie liczb stałoprzecinkowych oraz mnożenie i akumulacja Znaczenie bitów rejestru stanu ASTAT Znaczenie bitów rejestru trybu MSTAT (dodawanie lub odejmowanie) • 16 -bitowe rejestry MX 0 i MX 1 – pierwszy argument operacji, MY 0 i MY 1 – drugi argument operacji, 40 -bitowy rejestr MR (MR 2 8 bitów, MR 1 i MR 0 16 bitów) – rejestr wyjściowy • • rejestr MR ma własność „nasycenia”, czyli jeśli zostanie wykryte przepełnienie to do MR zostanie największa/najmniejsza 32 -bitowa zostanie „nasycony”, czy nie, jest MVzapisana – oznacza przepełnienie MR liczba (Czy rejestr • 0 –MR wybór zbioru rejestrów częścią kodu instrukcji) 0 = pierwszy Jeśli • możliwość wynik operacji mnożenia akumulacji nie obliczeń do 16 bitów, zaokrąglania 40 ibitowego wyniku zaokrąglenia do rejestru 1 =wynik drugi mieści sięlub w MR 1 parze(znak rejestrów MR 1, to MR 2) MF, powielony w MR 0, rejestrze • 4 – tryb pracy najbardziej znaczący bity wyniku znajdują się w • 16 -bitowy rejestr MF – rejestr pośredniczący, można go wykorzystać w następnym rozkazie 0 = liczby ułamkowe (1. 15) rejestrze MR 2 i ustawiana jest flaga MV mnożenia przez podanie na wejście Y układu mnożącego przepełnienia akumulatora MR 1 = liczby całkowite (16. 0) • rejestry mogą być odczytywane i zapisywane w jednym cyklu rozkazowym (odczyt na początku, zapis na końcu cyklu) Dla liczb 1. 15 32 -bitowy wynik mnożenia jest rozszerzany do 40 bitów poprzez powielenie bitu znaku, przesuwany w lewo o jeden bit i podawany na wejście układu sumatora Dla liczb 16. 0 rozszerzony do 40 bitów wynik jest bezpośrednio podawany na wejście układu sumatora

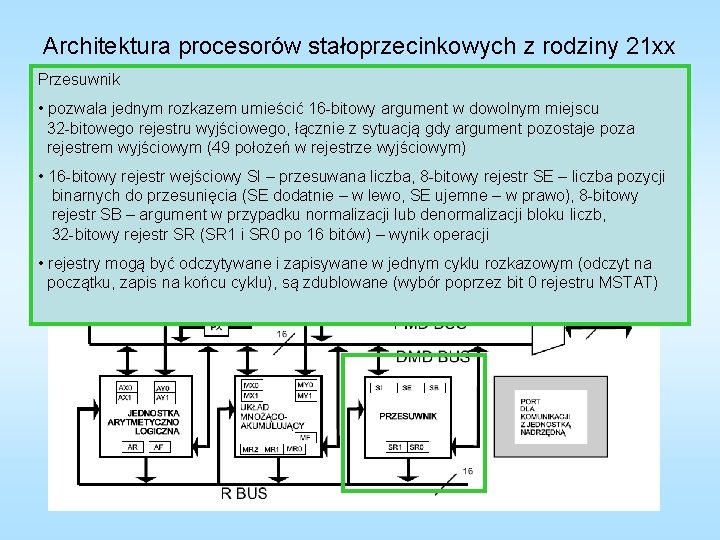

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Przesuwnik • pozwala jednym rozkazem umieścić 16 -bitowy argument w dowolnym miejscu 32 -bitowego rejestru wyjściowego, łącznie z sytuacją gdy argument pozostaje poza rejestrem wyjściowym (49 położeń w rejestrze wyjściowym) • 16 -bitowy rejestr wejściowy SI – przesuwana liczba, 8 -bitowy rejestr SE – liczba pozycji binarnych do przesunięcia (SE dodatnie – w lewo, SE ujemne – w prawo), 8 -bitowy rejestr SB – argument w przypadku normalizacji lub denormalizacji bloku liczb, 32 -bitowy rejestr SR (SR 1 i SR 0 po 16 bitów) – wynik operacji • rejestry mogą być odczytywane i zapisywane w jednym cyklu rozkazowym (odczyt na początku, zapis na końcu cyklu), są zdublowane (wybór poprzez bit 0 rejestru MSTAT)

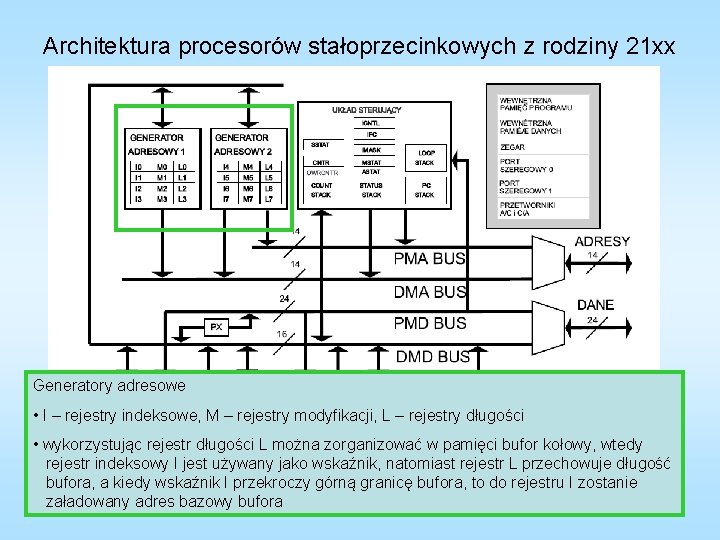

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Generatory adresowe • I – rejestry indeksowe, M – rejestry modyfikacji, L – rejestry długości • wykorzystując rejestr długości L można zorganizować w pamięci bufor kołowy, wtedy rejestr indeksowy I jest używany jako wskaźnik, natomiast rejestr L przechowuje długość bufora, a kiedy wskaźnik I przekroczy górną granicę bufora, to do rejestru I zostanie załadowany adres bazowy bufora

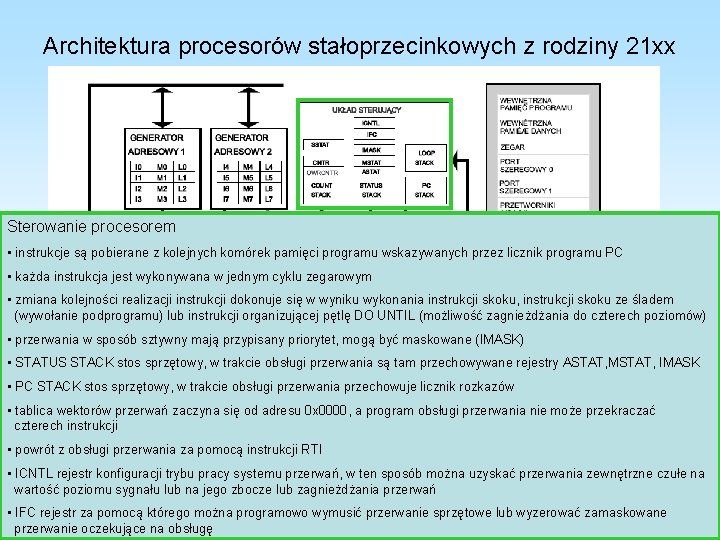

Architektura procesorów stałoprzecinkowych z rodziny 21 xx Sterowanie procesorem • instrukcje są pobierane z kolejnych komórek pamięci programu wskazywanych przez licznik programu PC • każda instrukcja jest wykonywana w jednym cyklu zegarowym • zmiana kolejności realizacji instrukcji dokonuje się w wyniku wykonania instrukcji skoku, instrukcji skoku ze śladem (wywołanie podprogramu) lub instrukcji organizującej pętlę DO UNTIL (możliwość zagnieżdżania do czterech poziomów) • przerwania w sposób sztywny mają przypisany priorytet, mogą być maskowane (IMASK) • STATUS STACK stos sprzętowy, w trakcie obsługi przerwania są tam przechowywane rejestry ASTAT, MSTAT, IMASK • PC STACK stos sprzętowy, w trakcie obsługi przerwania przechowuje licznik rozkazów • tablica wektorów przerwań zaczyna się od adresu 0 x 0000, a program obsługi przerwania nie może przekraczać czterech instrukcji • powrót z obsługi przerwania za pomocą instrukcji RTI • ICNTL rejestr konfiguracji trybu pracy systemu przerwań, w ten sposób można uzyskać przerwania zewnętrzne czułe na wartość poziomu sygnału lub na jego zbocze lub zagnieżdżania przerwań • IFC rejestr za pomocą którego można programowo wymusić przerwanie sprzętowe lub wyzerować zamaskowane przerwanie oczekujące na obsługę

Architektura procesorów stałoprzecinkowych z rodziny 21 xx

Rodzina stałoprzecinkowych procesorów sygnałowych ADSP 21 xx

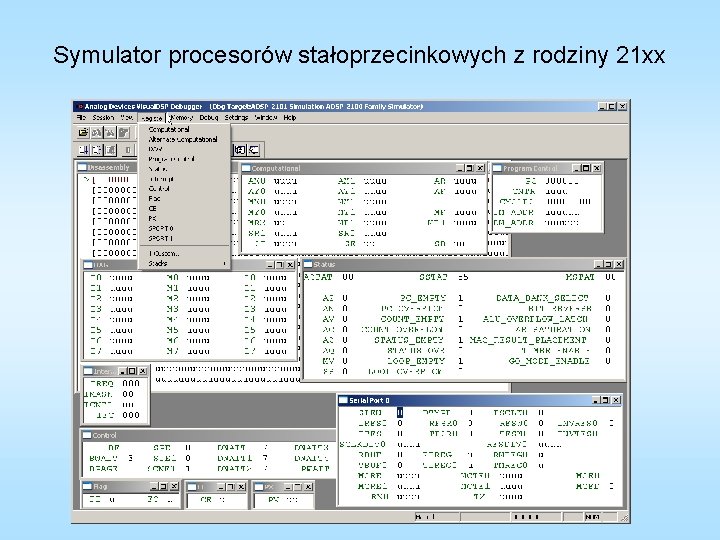

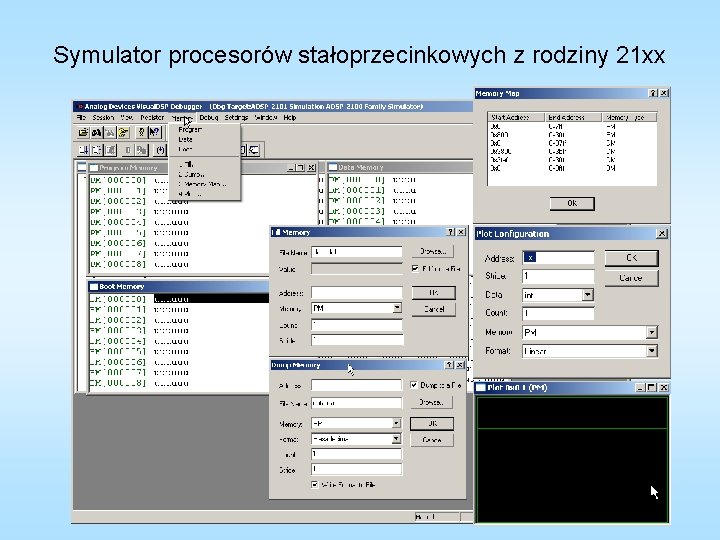

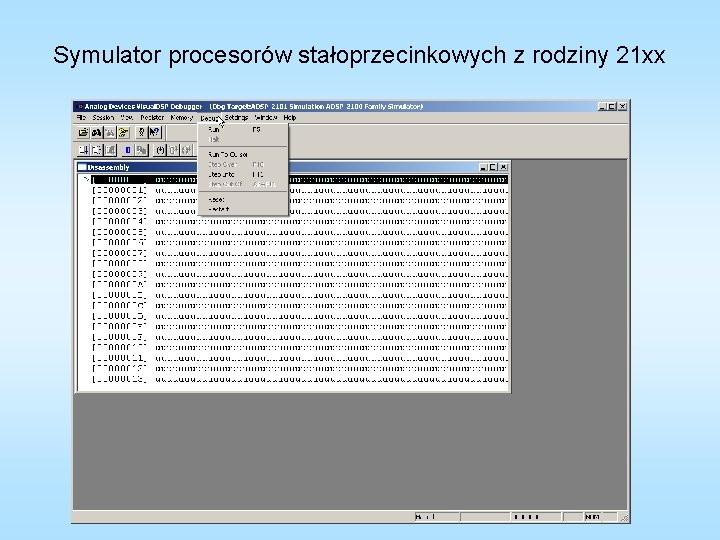

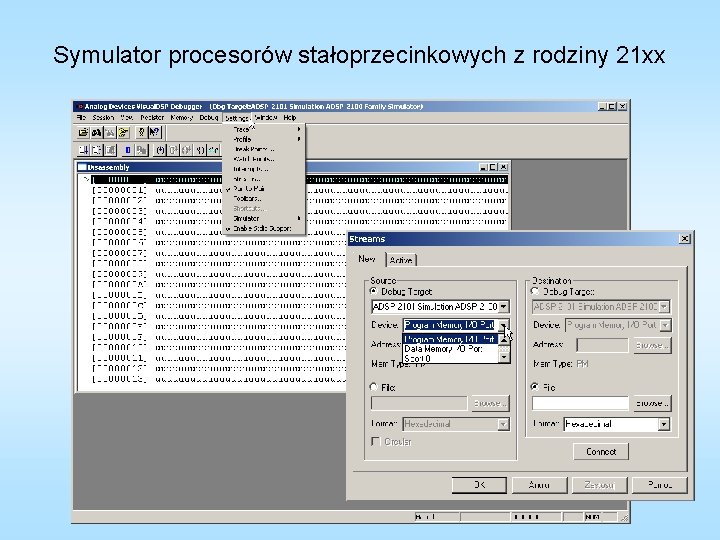

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

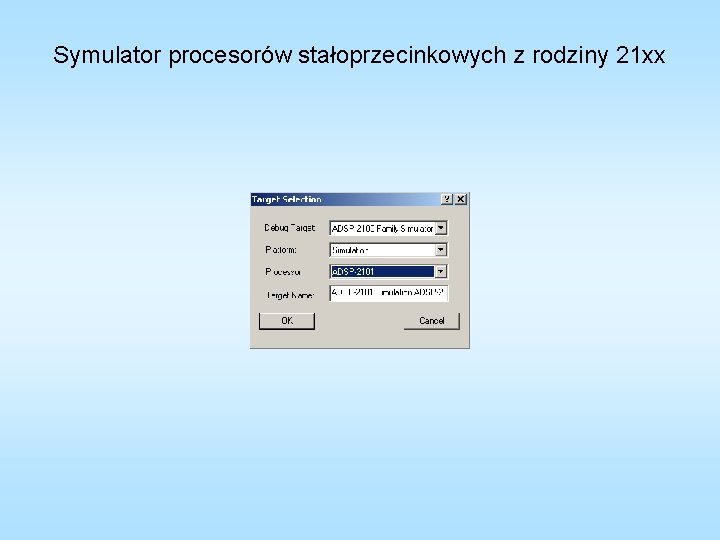

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

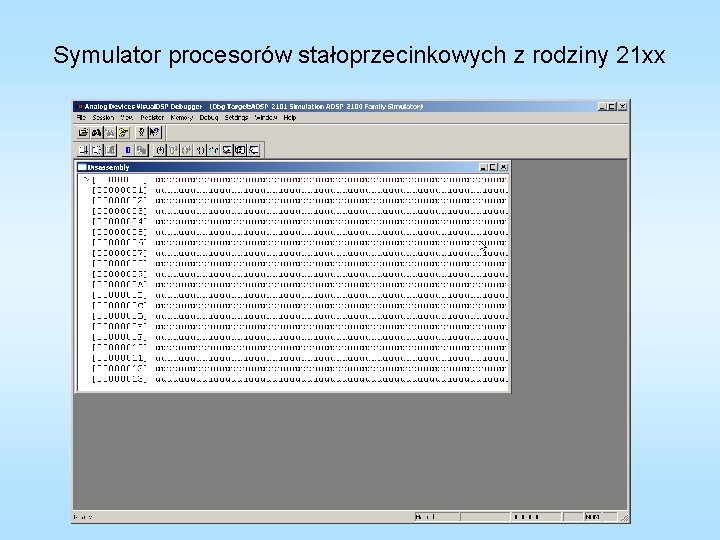

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

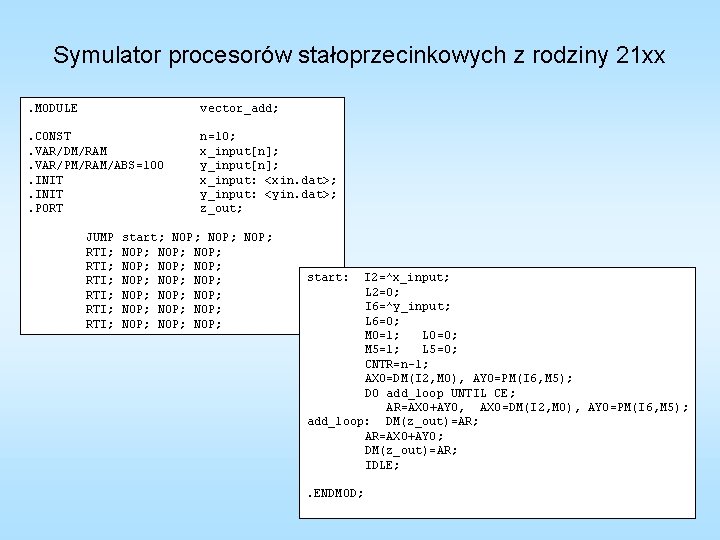

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

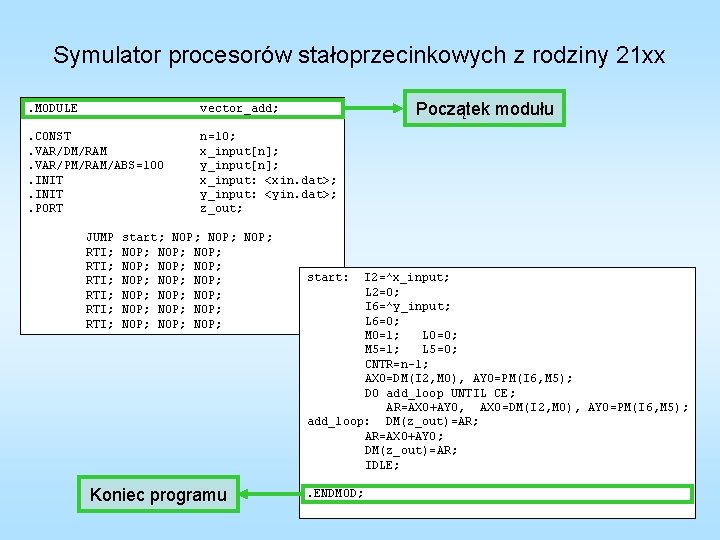

Symulator procesorów stałoprzecinkowych z rodziny 21 xx Początek modułu . MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; Koniec programu start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

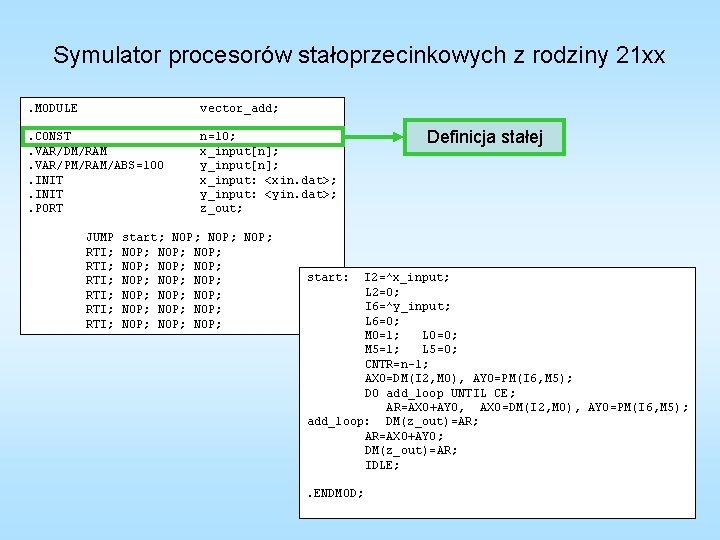

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Definicja stałej I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

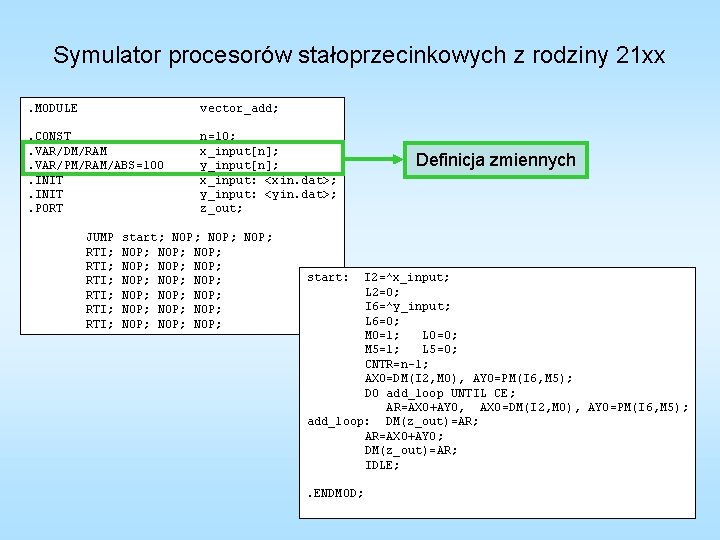

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Definicja zmiennych I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

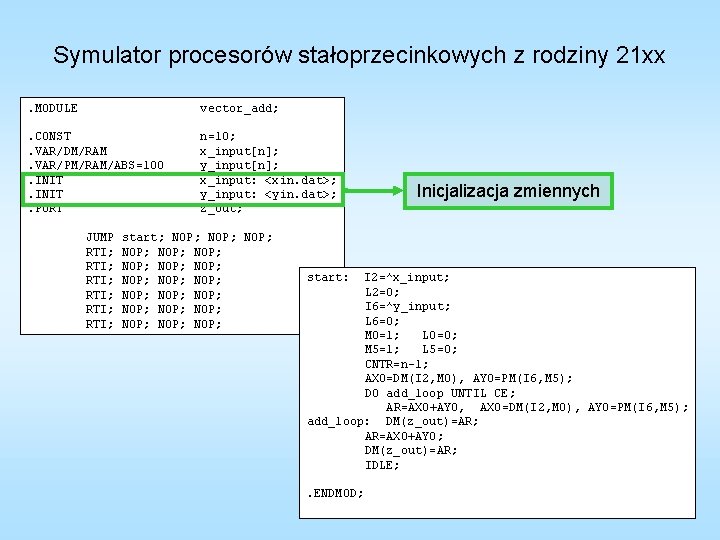

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Inicjalizacja zmiennych I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

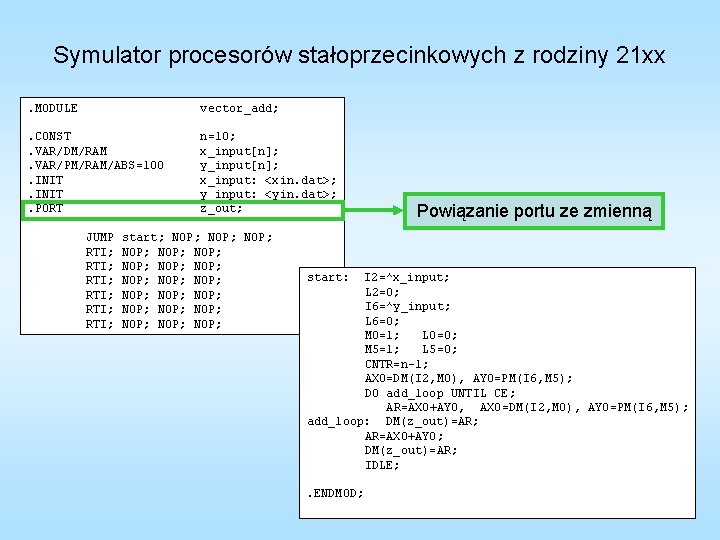

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Powiązanie portu ze zmienną I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

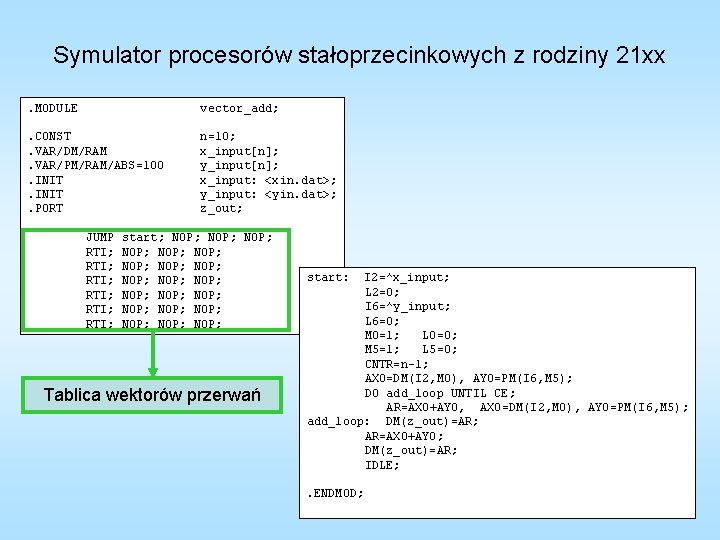

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; Tablica wektorów przerwań start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

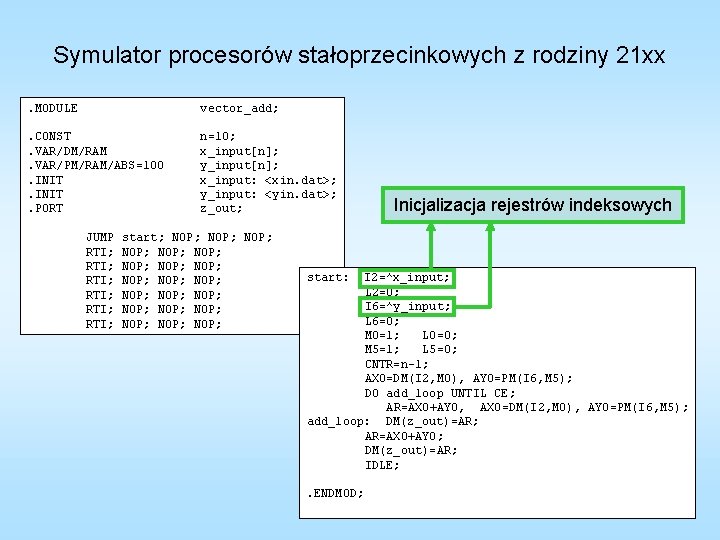

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Inicjalizacja rejestrów indeksowych I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

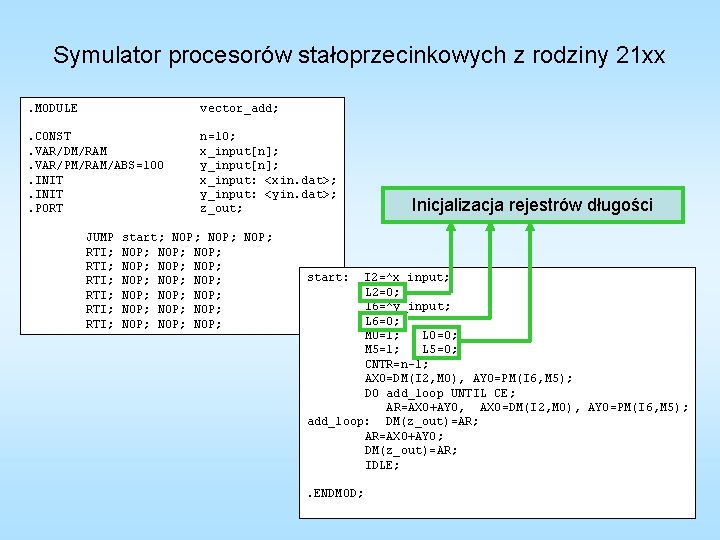

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Inicjalizacja rejestrów długości I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

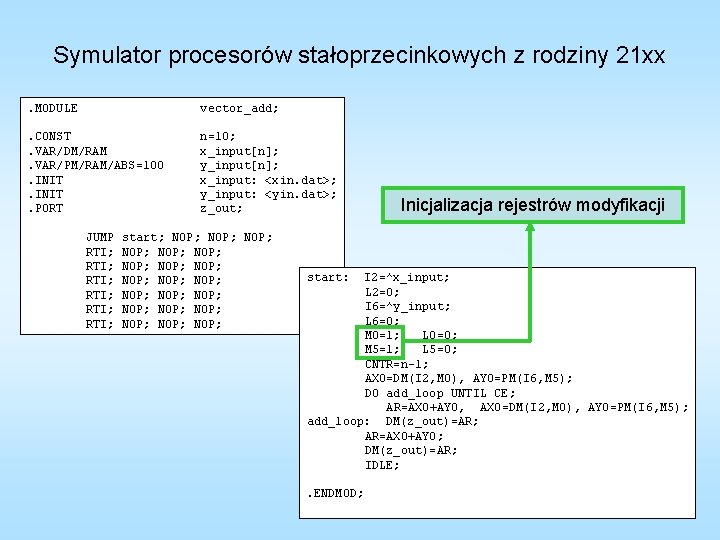

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; start: Inicjalizacja rejestrów modyfikacji I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

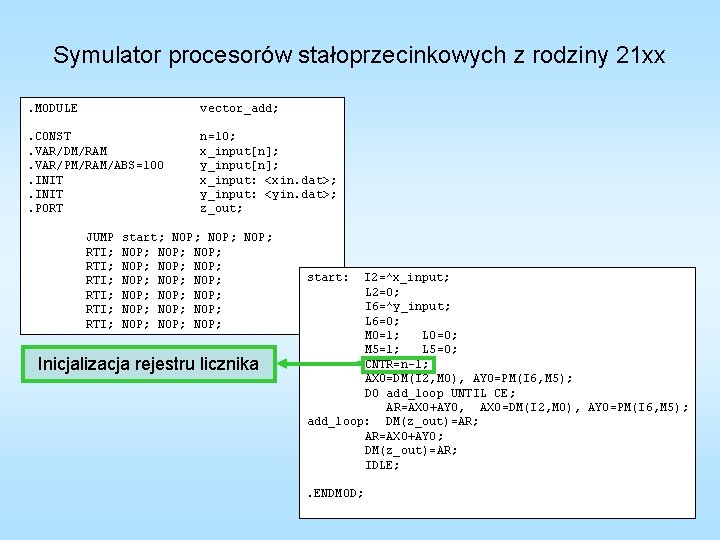

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; Inicjalizacja rejestru licznika start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

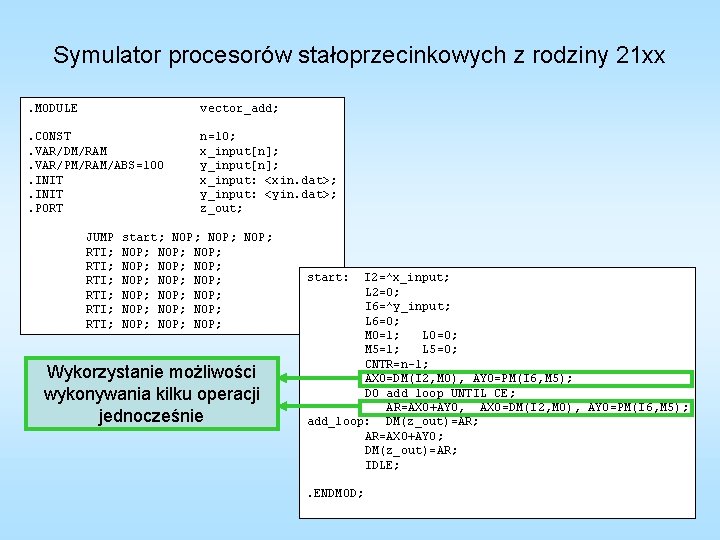

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; Wykorzystanie możliwości wykonywania kilku operacji jednocześnie start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

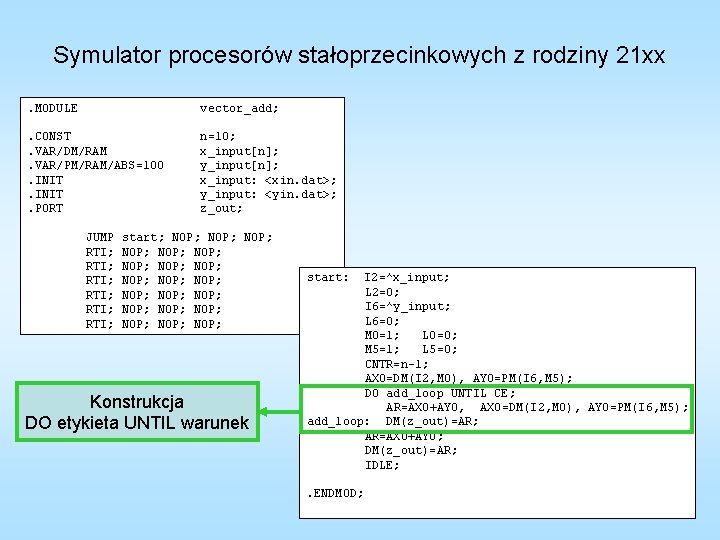

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; Konstrukcja DO etykieta UNTIL warunek start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

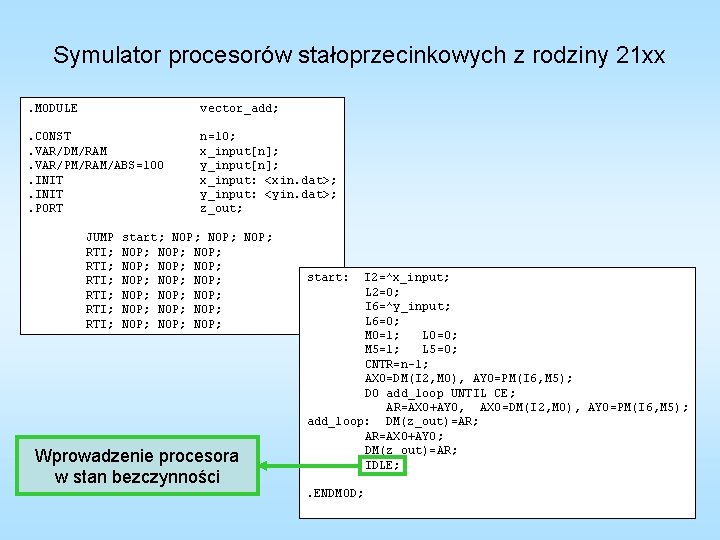

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. MODULE vector_add; . CONST. VAR/DM/RAM. VAR/PM/RAM/ABS=100. INIT. PORT n=10; x_input[n]; y_input[n]; x_input: <xin. dat>; y_input: <yin. dat>; z_out; JUMP RTI; RTI; start; NOP; NOP; NOP; NOP; NOP; NOP; Wprowadzenie procesora w stan bezczynności start: I 2=^x_input; L 2=0; I 6=^y_input; L 6=0; M 0=1; L 0=0; M 5=1; L 5=0; CNTR=n-1; AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); DO add_loop UNTIL CE; AR=AX 0+AY 0, AX 0=DM(I 2, M 0), AY 0=PM(I 6, M 5); add_loop: DM(z_out)=AR; AR=AX 0+AY 0; DM(z_out)=AR; IDLE; . ENDMOD;

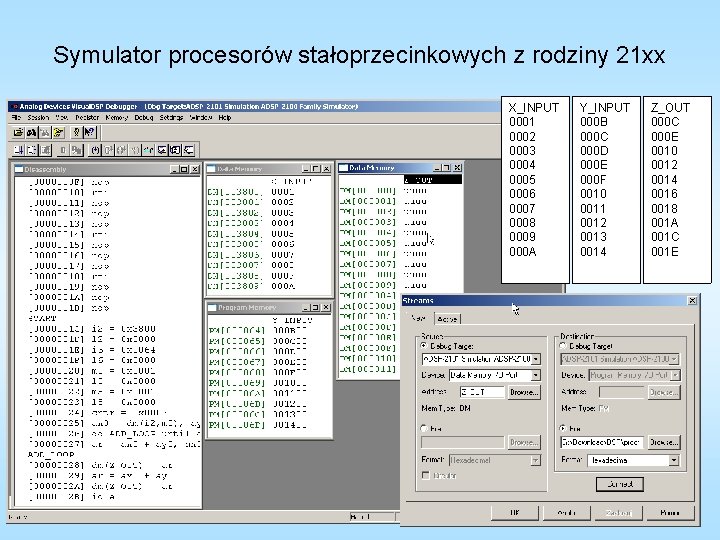

Symulator procesorów stałoprzecinkowych z rodziny 21 xx X_INPUT 0001 0002 0003 0004 0005 0006 0007 0008 0009 000 A Y_INPUT 000 B 000 C 000 D 000 E 000 F 0010 0011 0012 0013 0014 Z_OUT 000 C 000 E 0010 0012 0014 0016 0018 001 A 001 C 001 E

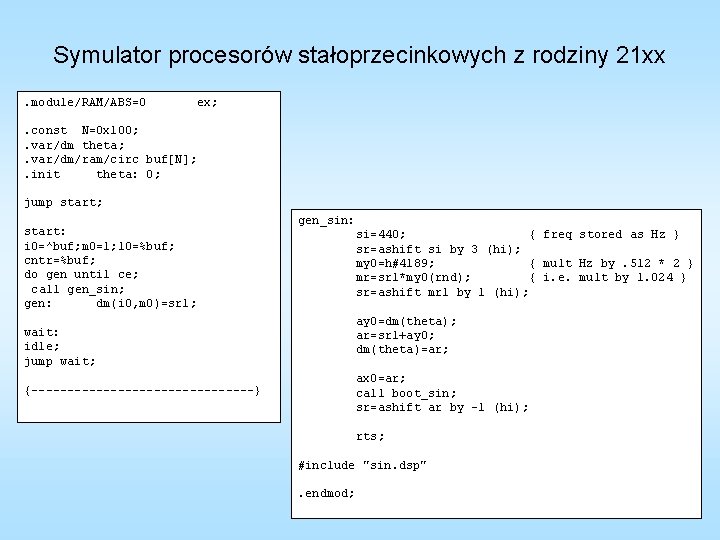

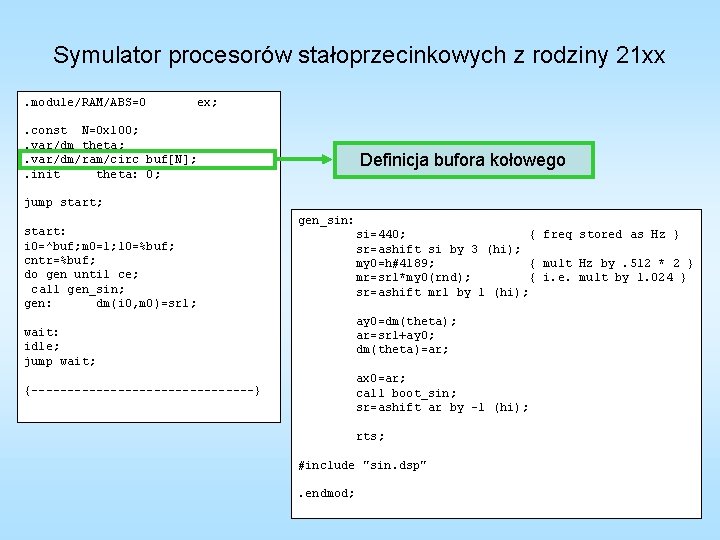

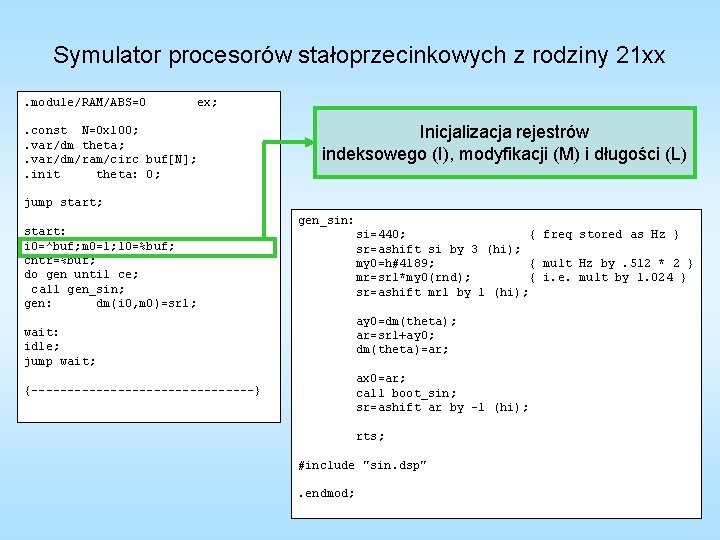

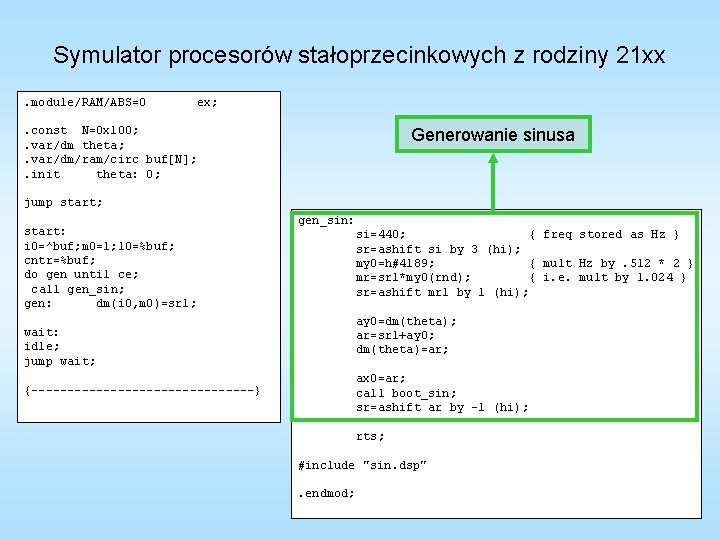

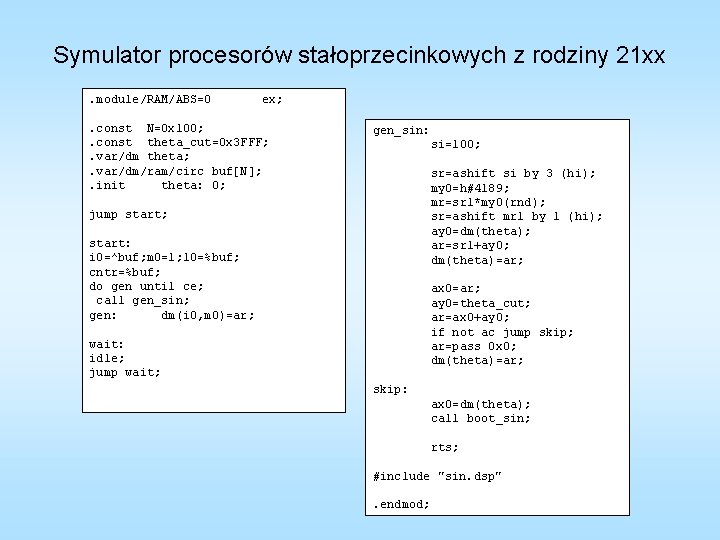

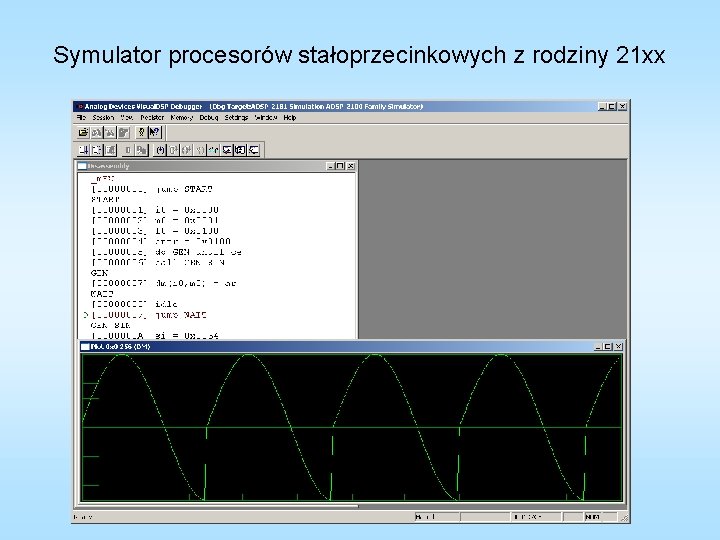

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; Definicja bufora kołowego jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; Inicjalizacja rejestrów indeksowego (I), modyfikacji (M) i długości (L) jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; Generowanie sinusa . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

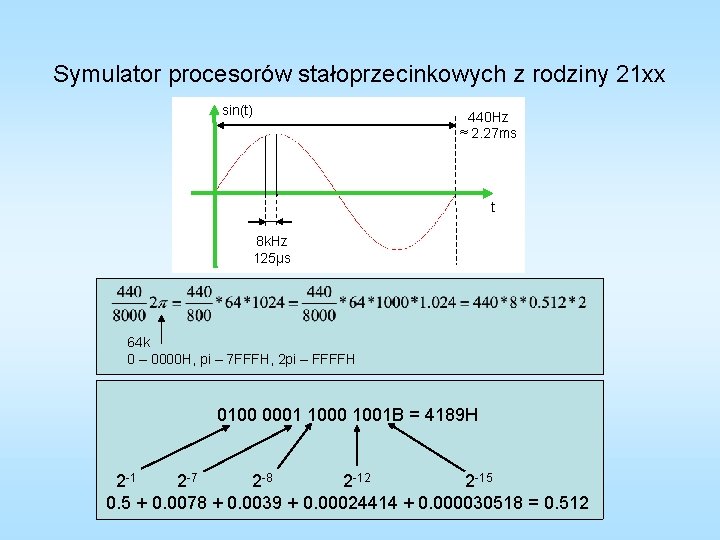

Symulator procesorów stałoprzecinkowych z rodziny 21 xx sin(t) 440 Hz ≈ 2. 27 ms t 8 k. Hz 125μs 64 k 0 – 0000 H, pi – 7 FFFH, 2 pi – FFFFH 0100 0001 1000 1001 B = 4189 H 2 -1 2 -7 2 -8 2 -12 2 -15 0. 5 + 0. 0078 + 0. 0039 + 0. 00024414 + 0. 000030518 = 0. 512

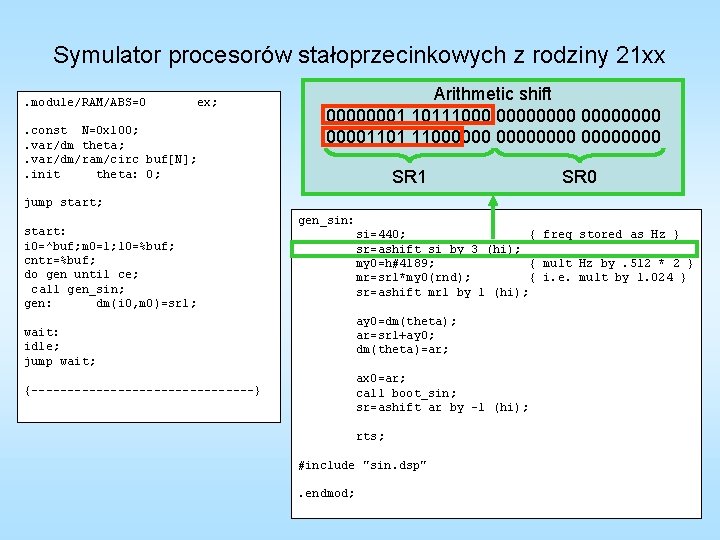

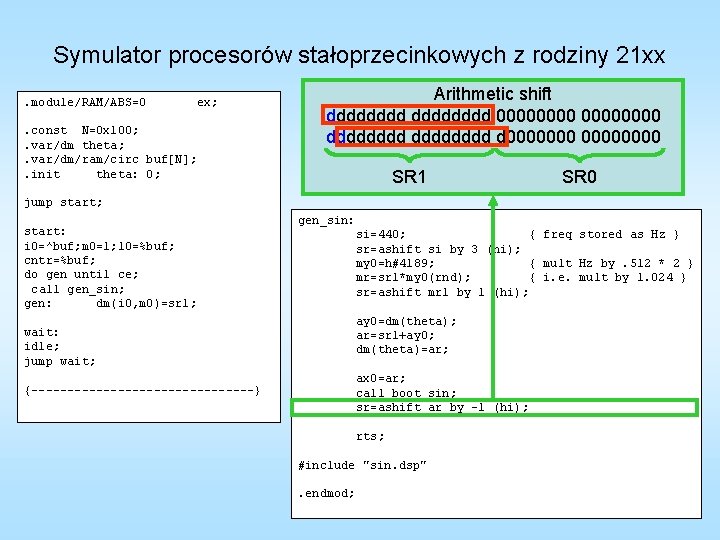

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; Arithmetic shift 00000001 10111000 000000001101 1100000000 SR 1 SR 0 jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

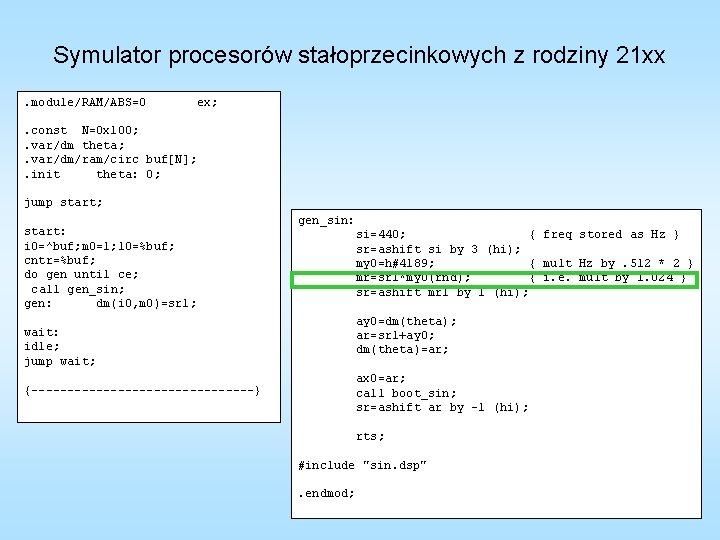

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

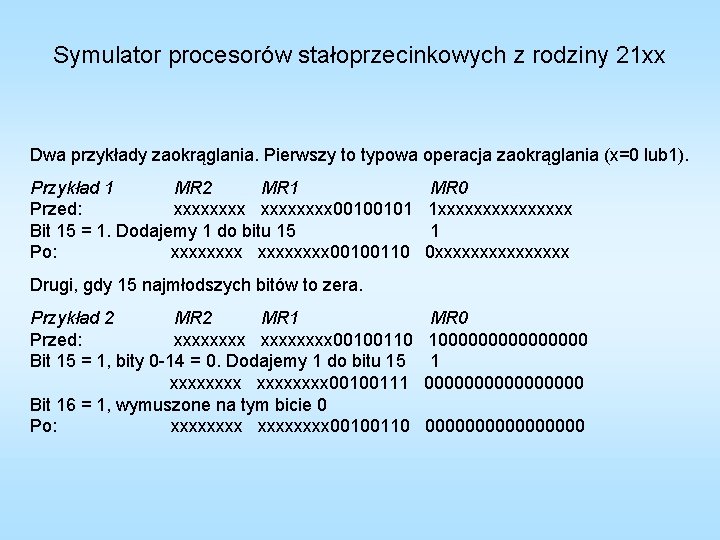

Symulator procesorów stałoprzecinkowych z rodziny 21 xx Dwa przykłady zaokrąglania. Pierwszy to typowa operacja zaokrąglania (x=0 lub 1). Przykład 1 MR 2 MR 1 Przed: xxxxxxxx 00100101 Bit 15 = 1. Dodajemy 1 do bitu 15 Po: xxxxxxxx 00100110 MR 0 1 xxxxxxxx 1 0 xxxxxxxx Drugi, gdy 15 najmłodszych bitów to zera. Przykład 2 MR 1 Przed: xxxxxxxx 00100110 Bit 15 = 1, bity 0 -14 = 0. Dodajemy 1 do bitu 15 xxxxxxxx 00100111 Bit 16 = 1, wymuszone na tym bicie 0 Po: xxxxxxxx 00100110 MR 0 100000000 1 0000000000000000

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; Arithmetic shift dddddddd 00000000 dddddddd d 00000000 SR 1 SR 0 jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=sr 1; gen_sin: si=440; { freq stored as Hz } sr=ashift si by 3 (hi); my 0=h#4189; { mult Hz by. 512 * 2 } mr=sr 1*my 0(rnd); { i. e. mult by 1. 024 } sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; wait: idle; jump wait; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); {----------------} rts; #include "sin. dsp". endmod;

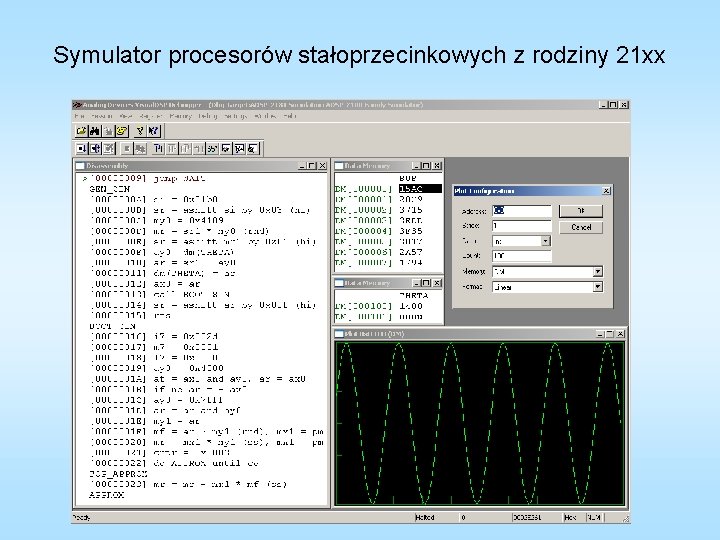

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

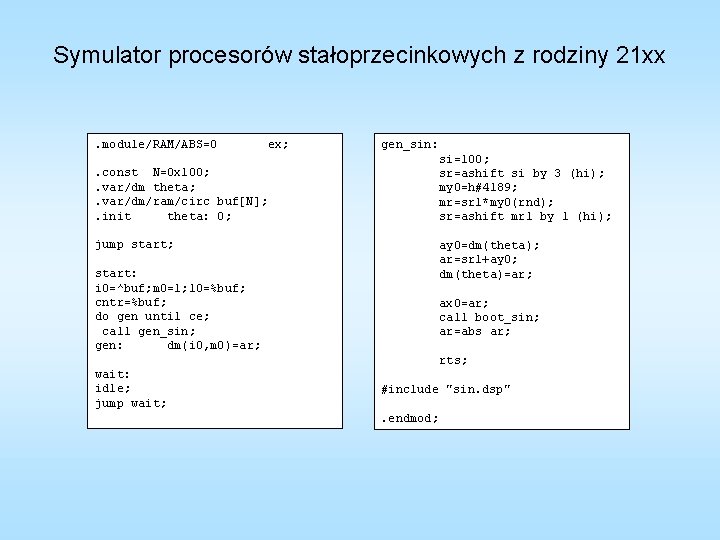

Symulator procesorów stałoprzecinkowych z rodziny 21 xx . module/RAM/ABS=0 ex; gen_sin: si=100; sr=ashift si by 3 (hi); my 0=h#4189; mr=sr 1*my 0(rnd); sr=ashift mr 1 by 1 (hi); . const N=0 x 100; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; jump start; ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=ar; ax 0=ar; call boot_sin; ar=abs ar; rts; wait: idle; jump wait; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

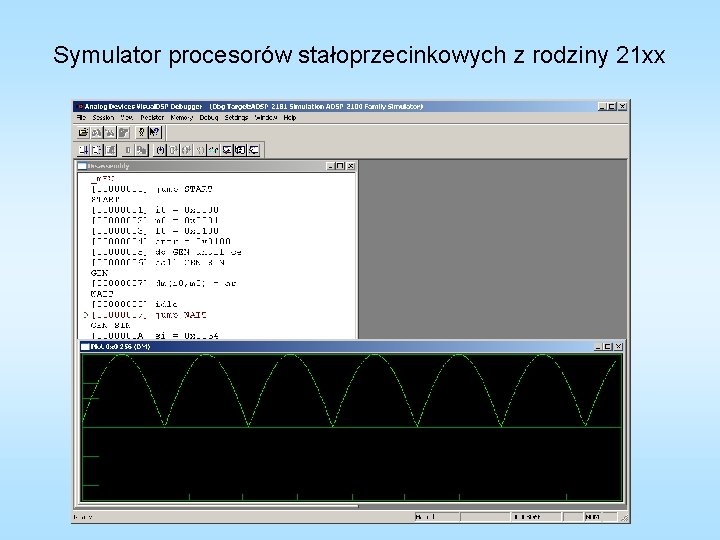

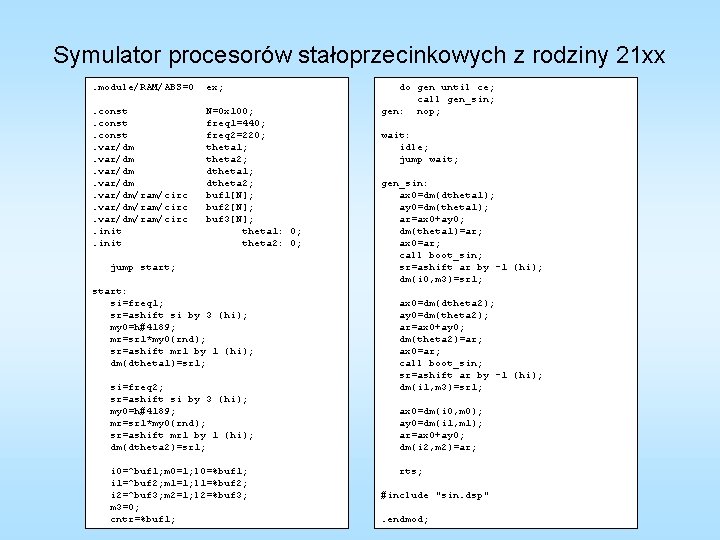

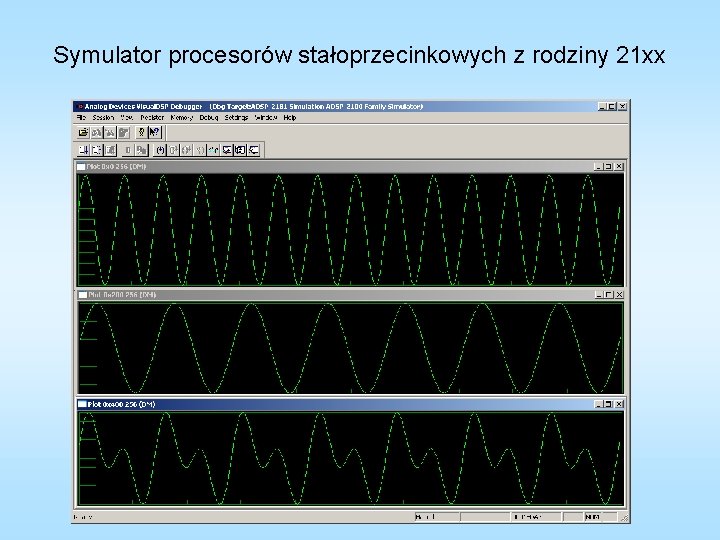

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const. var/dm/ram/circ. init N=0 x 100; freq 1=440; freq 2=220; theta 1; theta 2; dtheta 1; dtheta 2; buf 1[N]; buf 2[N]; buf 3[N]; theta 1: 0; theta 2: 0; jump start; start: si=freq 1; sr=ashift si by 3 (hi); my 0=h#4189; mr=sr 1*my 0(rnd); sr=ashift mr 1 by 1 (hi); dm(dtheta 1)=sr 1; si=freq 2; sr=ashift si by 3 (hi); my 0=h#4189; mr=sr 1*my 0(rnd); sr=ashift mr 1 by 1 (hi); dm(dtheta 2)=sr 1; i 0=^buf 1; m 0=1; l 0=%buf 1; i 1=^buf 2; m 1=1; l 1=%buf 2; i 2=^buf 3; m 2=1; l 2=%buf 3; m 3=0; cntr=%buf 1; do gen until ce; call gen_sin; gen: nop; wait: idle; jump wait; gen_sin: ax 0=dm(dtheta 1); ay 0=dm(theta 1); ar=ax 0+ay 0; dm(theta 1)=ar; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); dm(i 0, m 3)=sr 1; ax 0=dm(dtheta 2); ay 0=dm(theta 2); ar=ax 0+ay 0; dm(theta 2)=ar; ax 0=ar; call boot_sin; sr=ashift ar by -1 (hi); dm(i 1, m 3)=sr 1; ax 0=dm(i 0, m 0); ay 0=dm(i 1, m 1); ar=ax 0+ay 0; dm(i 2, m 2)=ar; rts; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

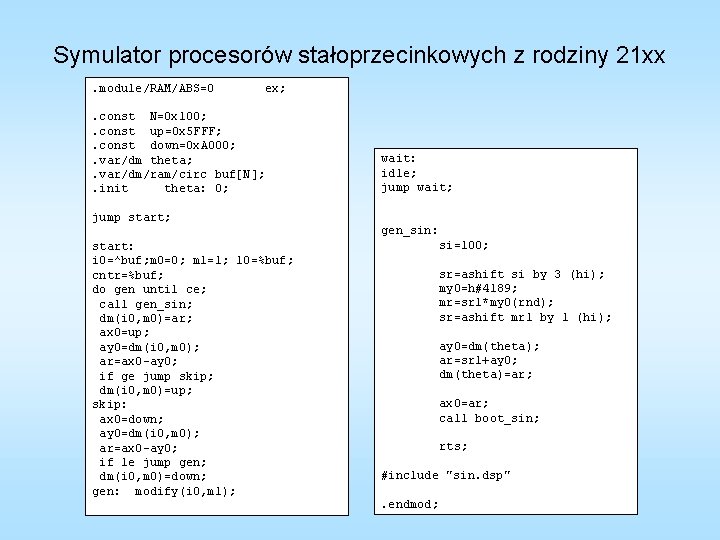

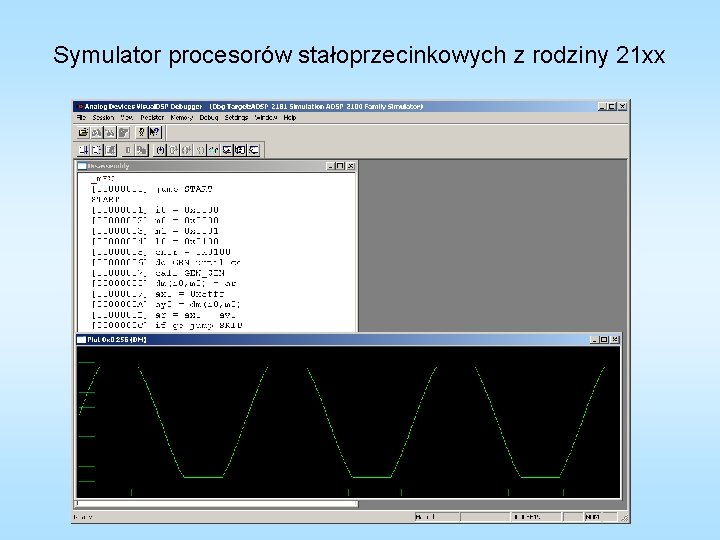

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . const up=0 x 5 FFF; . const down=0 x. A 000; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; jump start; start: i 0=^buf; m 0=0; m 1=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; dm(i 0, m 0)=ar; ax 0=up; ay 0=dm(i 0, m 0); ar=ax 0 -ay 0; if ge jump skip; dm(i 0, m 0)=up; skip: ax 0=down; ay 0=dm(i 0, m 0); ar=ax 0 -ay 0; if le jump gen; dm(i 0, m 0)=down; gen: modify(i 0, m 1); wait: idle; jump wait; gen_sin: si=100; sr=ashift si by 3 (hi); my 0=h#4189; mr=sr 1*my 0(rnd); sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; ax 0=ar; call boot_sin; rts; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex; . const N=0 x 100; . const theta_cut=0 x 3 FFF; . var/dm theta; . var/dm/ram/circ buf[N]; . init theta: 0; gen_sin: si=100; sr=ashift si by 3 (hi); my 0=h#4189; mr=sr 1*my 0(rnd); sr=ashift mr 1 by 1 (hi); ay 0=dm(theta); ar=sr 1+ay 0; dm(theta)=ar; jump start; start: i 0=^buf; m 0=1; l 0=%buf; cntr=%buf; do gen until ce; call gen_sin; gen: dm(i 0, m 0)=ar; ax 0=ar; ay 0=theta_cut; ar=ax 0+ay 0; if not ac jump skip; ar=pass 0 x 0; dm(theta)=ar; wait: idle; jump wait; skip: ax 0=dm(theta); call boot_sin; rts; #include "sin. dsp". endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

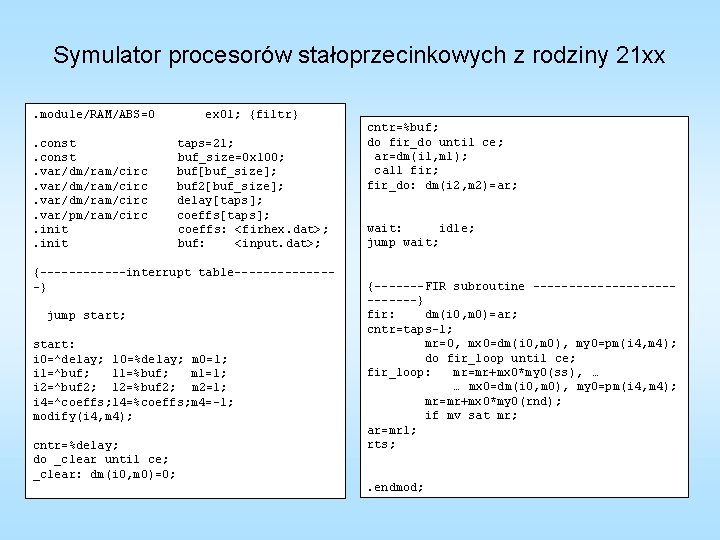

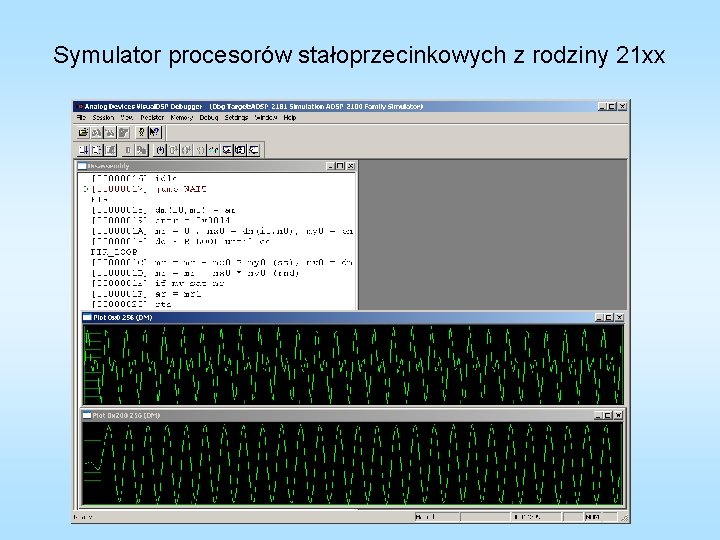

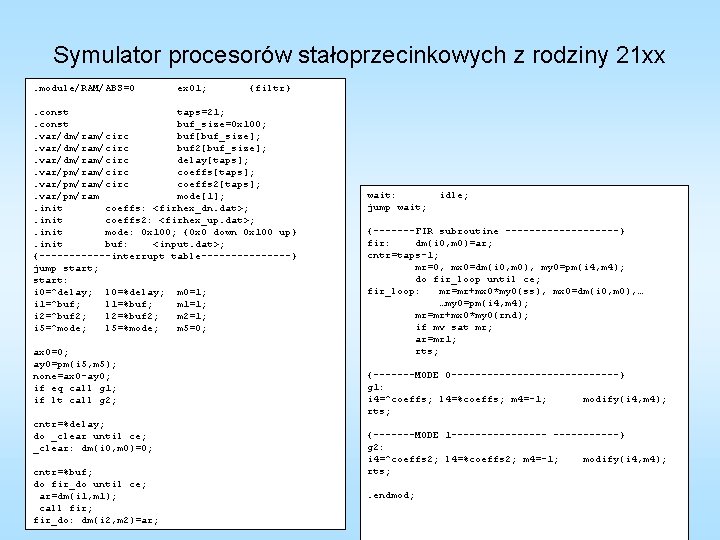

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex 01; {filtr} . const. var/dm/ram/circ. var/pm/ram/circ. init taps=21; buf_size=0 x 100; buf[buf_size]; buf 2[buf_size]; delay[taps]; coeffs: <firhex. dat>; buf: <input. dat>; {------interrupt table-------} jump start; start: i 0=^delay; l 0=%delay; m 0=1; i 1=^buf; l 1=%buf; m 1=1; i 2=^buf 2; l 2=%buf 2; m 2=1; i 4=^coeffs; l 4=%coeffs; m 4=-1; modify(i 4, m 4); cntr=%delay; do _clear until ce; _clear: dm(i 0, m 0)=0; cntr=%buf; do fir_do until ce; ar=dm(i 1, m 1); call fir; fir_do: dm(i 2, m 2)=ar; wait: idle; jump wait; {-------FIR subroutine -------------} fir: dm(i 0, m 0)=ar; cntr=taps-1; mr=0, mx 0=dm(i 0, m 0), my 0=pm(i 4, m 4); do fir_loop until ce; fir_loop: mr=mr+mx 0*my 0(ss), … … mx 0=dm(i 0, m 0), my 0=pm(i 4, m 4); mr=mr+mx 0*my 0(rnd); if mv sat mr; ar=mr 1; rts; . endmod;

Symulator procesorów stałoprzecinkowych z rodziny 21 xx

Symulator procesorów stałoprzecinkowych z rodziny 21 xx. module/RAM/ABS=0 ex 01; {filtr} . const taps=21; . const buf_size=0 x 100; . var/dm/ram/circ buf[buf_size]; . var/dm/ram/circ buf 2[buf_size]; . var/dm/ram/circ delay[taps]; . var/pm/ram/circ coeffs 2[taps]; . var/pm/ram mode[1]; . init coeffs: <firhex_dn. dat>; . init coeffs 2: <firhex_up. dat>; . init mode: 0 x 100; {0 x 0 down 0 x 100 up}. init buf: <input. dat>; {------interrupt table--------} jump start; start: i 0=^delay; l 0=%delay; m 0=1; i 1=^buf; l 1=%buf; m 1=1; i 2=^buf 2; l 2=%buf 2; m 2=1; i 5=^mode; l 5=%mode; m 5=0; ax 0=0; ay 0=pm(i 5, m 5); none=ax 0 -ay 0; if eq call g 1; if lt call g 2; cntr=%delay; do _clear until ce; _clear: dm(i 0, m 0)=0; cntr=%buf; do fir_do until ce; ar=dm(i 1, m 1); call fir; fir_do: dm(i 2, m 2)=ar; wait: jump wait; idle; {-------FIR subroutine ----------} fir: dm(i 0, m 0)=ar; cntr=taps-1; mr=0, mx 0=dm(i 0, m 0), my 0=pm(i 4, m 4); do fir_loop until ce; fir_loop: mr=mr+mx 0*my 0(ss), mx 0=dm(i 0, m 0), … …my 0=pm(i 4, m 4); mr=mr+mx 0*my 0(rnd); if mv sat mr; ar=mr 1; rts; {-------MODE 0 --------------} g 1: i 4=^coeffs; l 4=%coeffs; m 4=-1; modify(i 4, m 4); rts; {-------MODE 1 --------} g 2: i 4=^coeffs 2; l 4=%coeffs 2; m 4=-1; modify(i 4, m 4); rts; . endmod;

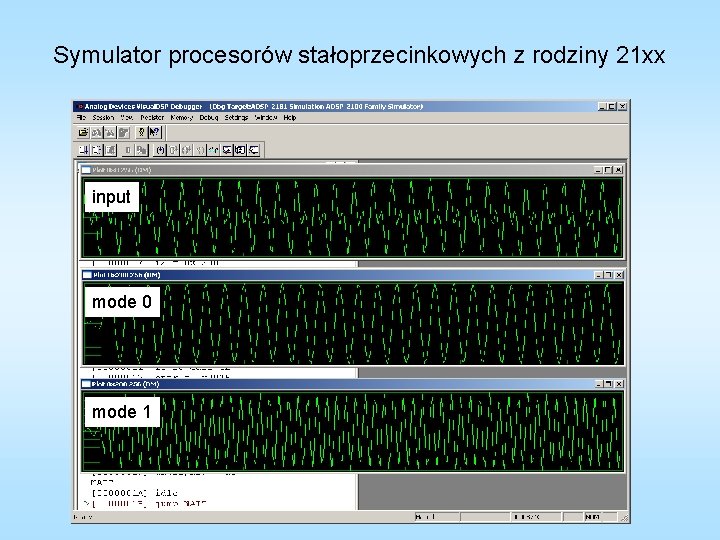

Symulator procesorów stałoprzecinkowych z rodziny 21 xx input mode 0 mode 1

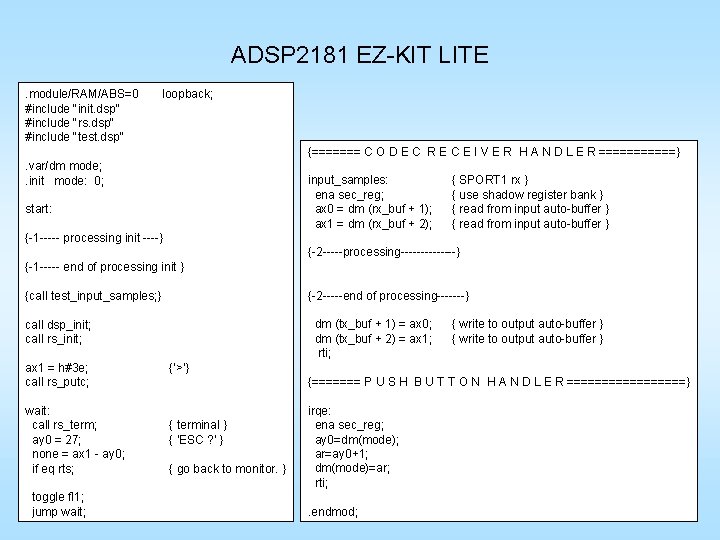

ADSP 2181 EZ-KIT LITE. module/RAM/ABS=0 #include "init. dsp" #include "rs. dsp" #include "test. dsp" loopback; {======= C O D E C R E C E I V E R H A N D L E R ======}. var/dm mode; . init mode: 0; input_samples: ena sec_reg; ax 0 = dm (rx_buf + 1); ax 1 = dm (rx_buf + 2); start: { SPORT 1 rx } { use shadow register bank } { read from input auto-buffer } {-1 ----- processing init ----} {-2 -----processing-------} {-1 ----- end of processing init } {-2 -----end of processing-------} {call test_input_samples; } dm (tx_buf + 1) = ax 0; dm (tx_buf + 2) = ax 1; rti; call dsp_init; call rs_init; ax 1 = h#3 e; call rs_putc; wait: call rs_term; ay 0 = 27; none = ax 1 - ay 0; if eq rts; toggle fl 1; jump wait; { write to output auto-buffer } {'>'} {======= P U S H B U T T O N H A N D L E R =========} { terminal } { 'ESC ? ' } { go back to monitor. } irqe: ena sec_reg; ay 0=dm(mode); ar=ay 0+1; dm(mode)=ar; rti; . endmod;

- Slides: 60