Programmable Solutions in Smart Card Readers Xilinx Overview

Programmable Solutions in Smart Card Readers

Xilinx Overview w Xilinx - The Industry Leader in Logic Solutions FPGAs & CPLDs — High-density & high-speed — Re-programmable — Low power & low cost ® www. xilinx. com

Xilinx Overview w Perfect match for use in Smart Card Readers — Faster Time-To-Market with programmable logic — Easily integrates system logic functions – Interface, control, decode, state machines, etc. — Extremely cost effective — Very low power – Ideal for hand held , battery powered card readers — Flexible – Design changes can be made In-system to meet changing requirements and standards ® www. xilinx. com

How Xilinx Fits in Smart Card Readers Application Need Xilinx Fit Continuous feature integration Quick time-to-market Low power consumption Fast In-system programming Mixed voltages (5 V & 3 V) Small form factor Programmability Cool. Runner CSP & TQFP ® www. xilinx. com

Design Example Hand Held Smart Card Reader w Design objectives — Low power consumption – Battery powered — — Lowest possible total product cost Small and light Flexible solution to allow for system upgrades Mixed voltage operation (smart cards require 5 V) ® www. xilinx. com

Design Example Hand Held Smart Card Reader w Cool. Runner Support Solution — 2 Cool. Runner CPLDs per system – Total 0. 05 m. A static power consumption — Cool. Runner provides a cost effective, low power solution — Small form factor packages — ISP & JTAG for system upgradability and testability — 3 V parts with 5 V tolerant I/O ® www. xilinx. com

Smart Card Readers Display Driver Memory Modem I/F Modem Main Data Processing Security Logic Card Reader Interface Keypad Decoder LCD Card Reader 1 2 3 4 5 6 7 8 9 Keypad 0 ® www. xilinx. com

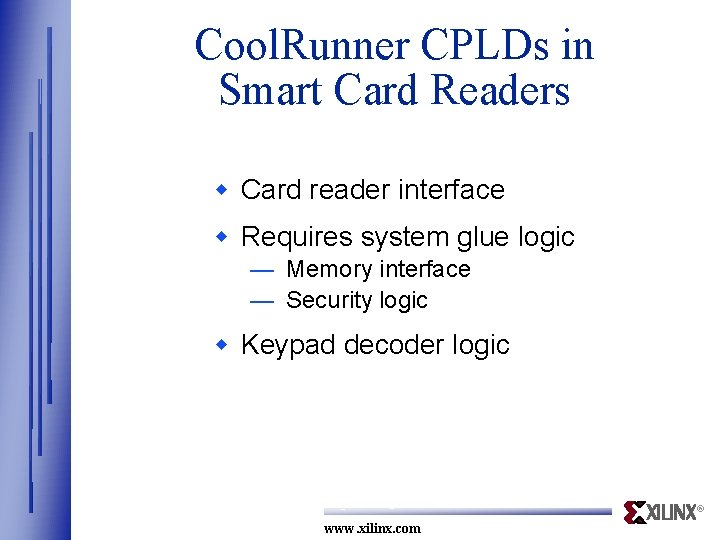

Cool. Runner CPLDs in Smart Card Readers w Card reader interface w Requires system glue logic — Memory interface — Security logic w Keypad decoder logic ® www. xilinx. com

Cool. Runner Functionality ® www. xilinx. com

Cool. Runner Key Features w Ultra low power — Standby current <100 u. A w Fast, flexible architecture — t. PD= 5 ns — Excellent pin-locking for ISP w Full range of densities — 22 V 10 & 32 to 960 macrocells w Small, surface mount packaging — QFP & 0. 5 mm 56 -pin CSP w ISP/JTAG compatible ® www. xilinx. com

Cool. Runner Key Features 1000 X 100. 0 1. 0 Icc Standby (m. A) Icc Dynamic 0. 5 10. 0 1. 0 0. 1 1 X Icc Standby Icc Dynamic Cool. Runner is a Leader Against Other Industry C ® www. xilinx. com

Xilinx Programmable Logic Solutions Features Cool. Runner CPLDs XCR 3000 (3. 3 v) XCR 5000 (5 v) XCR 22 V 10 (3. 3 V & 5 V) Key Features 32 to 960 macrocells Very Low Power High performance Low cost In-system programmable Chip scale packages 1 K System Gates www. xilinx. com 30 K ®

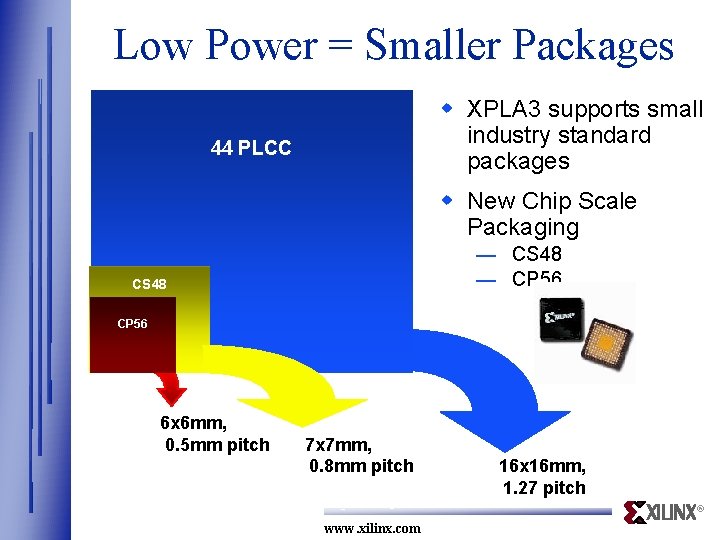

Low Power = Smaller Packages w XPLA 3 supports small industry standard packages 44 PLCC w New Chip Scale Packaging — CS 48 — CP 56 CS 48 CP 56 6 x 6 mm, 0. 5 mm pitch 7 x 7 mm, 0. 8 mm pitch 16 x 16 mm, 1. 27 pitch ® www. xilinx. com

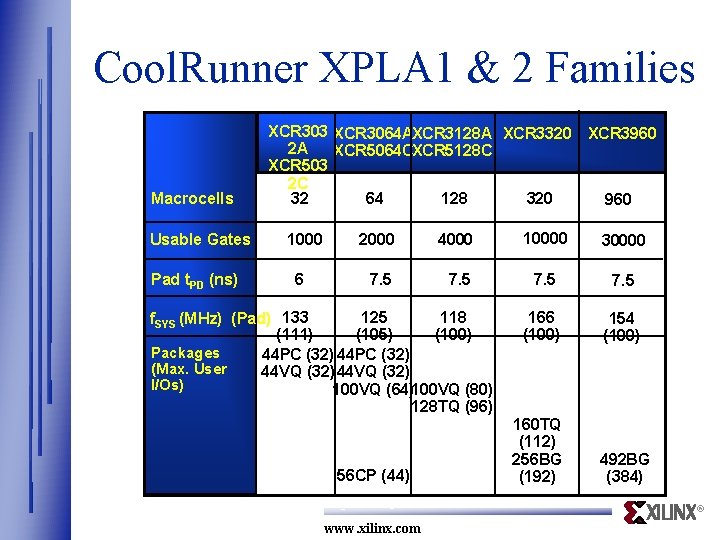

Cool. Runner XPLA 1 & 2 Families Macrocells Usable Gates Pad t. PD (ns) XCR 303 XCR 3064 AXCR 3128 A XCR 3320 XCR 3960 2 A XCR 5064 CXCR 5128 C XCR 503 2 C 320 32 64 128 960 1000 6 2000 4000 10000 30000 7. 5 166 (100) 154 (100) 160 TQ (112) 256 BG (192) 492 BG (384) 125 118 f. SYS (MHz) (Pad) 133 (111) (105) (100) Packages 44 PC (32) (Max. User 44 VQ (32) I/Os) 100 VQ (64)100 VQ (80) 128 TQ (96) 56 CP (44) ® www. xilinx. com

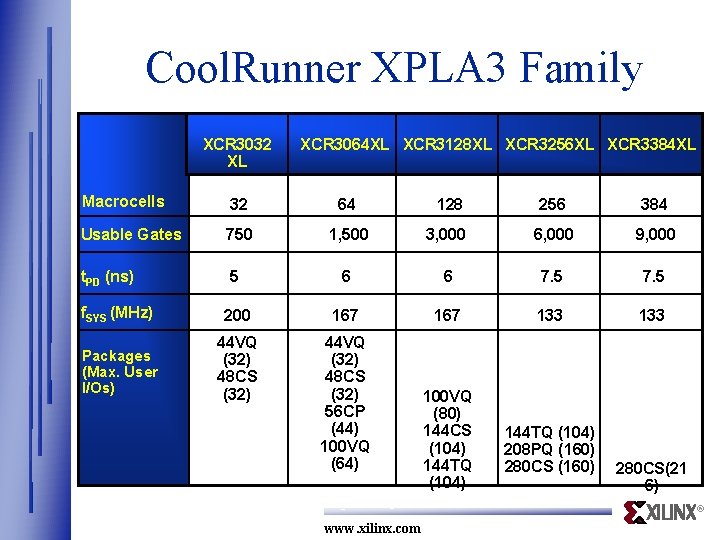

Cool. Runner XPLA 3 Family XCR 3032 XL XCR 3064 XL XCR 3128 XL XCR 3256 XL XCR 3384 XL Macrocells 32 64 128 256 384 Usable Gates 750 1, 500 3, 000 6, 000 9, 000 t. PD (ns) 5 6 6 7. 5 f. SYS (MHz) 200 167 133 Packages (Max. User I/Os) 44 VQ (32) 48 CS (32) 56 CP (44) 100 VQ (64) 100 VQ (80) 144 CS (104) 144 TQ (104) 208 PQ (160) 280 CS(21 6) ® www. xilinx. com

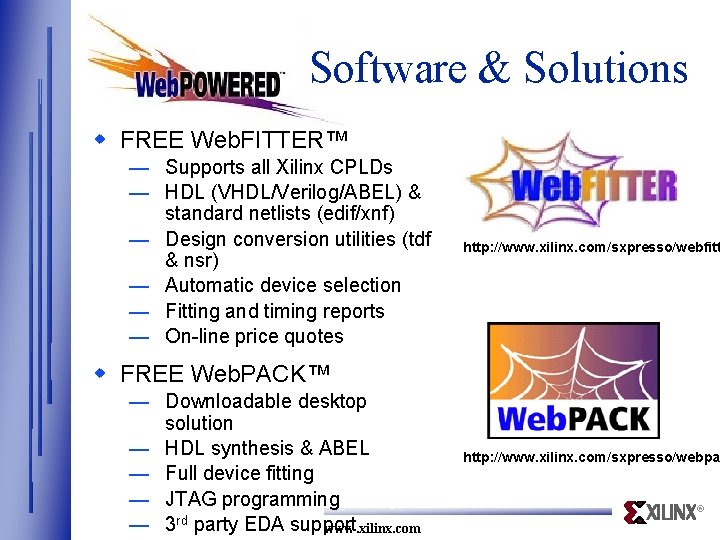

Software & Solutions w FREE Web. FITTER™ — Supports all Xilinx CPLDs — HDL (VHDL/Verilog/ABEL) & standard netlists (edif/xnf) — Design conversion utilities (tdf & nsr) — Automatic device selection — Fitting and timing reports — On-line price quotes http: //www. xilinx. com/sxpresso/webfitt w FREE Web. PACK™ — Downloadable desktop solution — HDL synthesis & ABEL — Full device fitting — JTAG programming — 3 rd party EDA support www. xilinx. com http: //www. xilinx. com/sxpresso/webpac ®

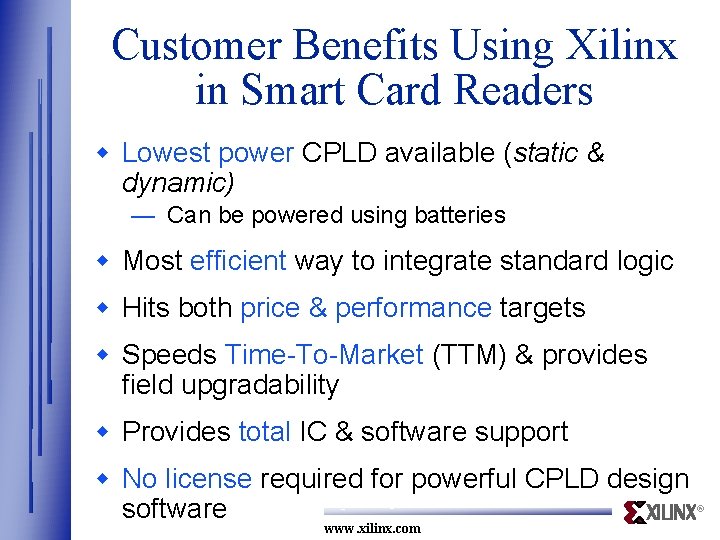

Customer Benefits Using Xilinx in Smart Card Readers w Lowest power CPLD available (static & dynamic) — Can be powered using batteries w Most efficient way to integrate standard logic w Hits both price & performance targets w Speeds Time-To-Market (TTM) & provides field upgradability w Provides total IC & software support w No license required for powerful CPLD design software www. xilinx. com ®

- Slides: 17