Programmable Logic System Design Lab 02 Design Entry

Programmable Logic System Design Lab 02 - Design Entry with VHDL SOC LAB. 2019. 10

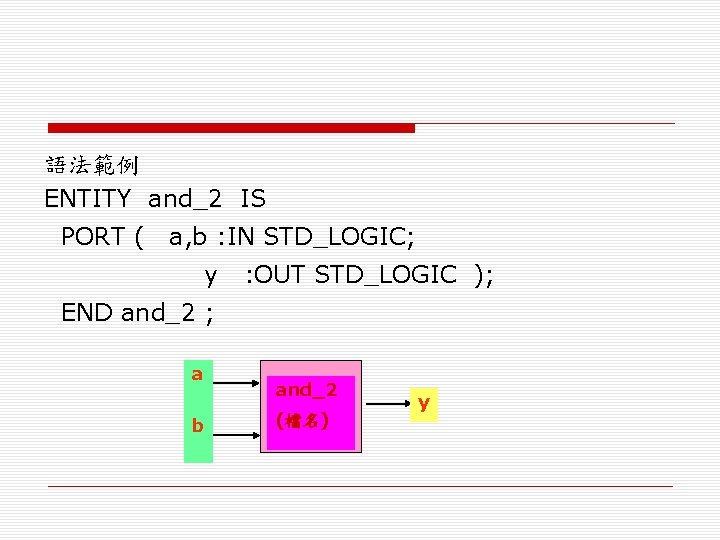

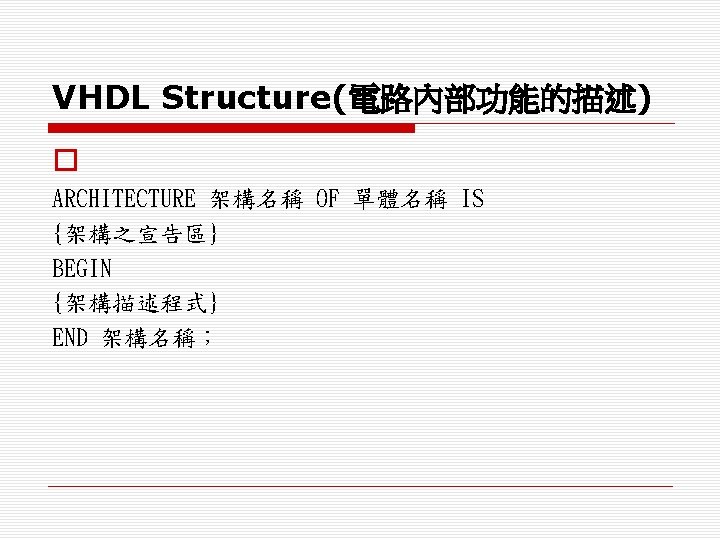

語法範例 ENTITY and_2 IS PORT ( a, b : IN STD_LOGIC; y : OUT STD_LOGIC ); END and_2 ; a b and_2 (檔名) y

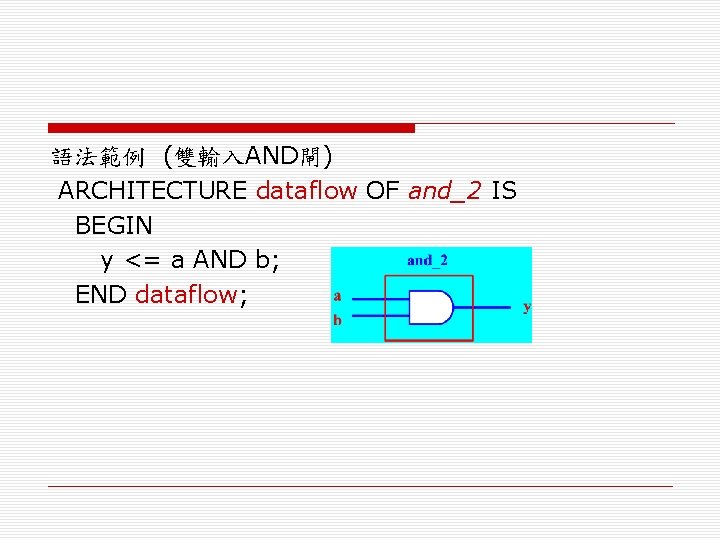

語法範例 (雙輸入AND閘) ARCHITECTURE dataflow OF and_2 IS BEGIN y <= a AND b; END dataflow;

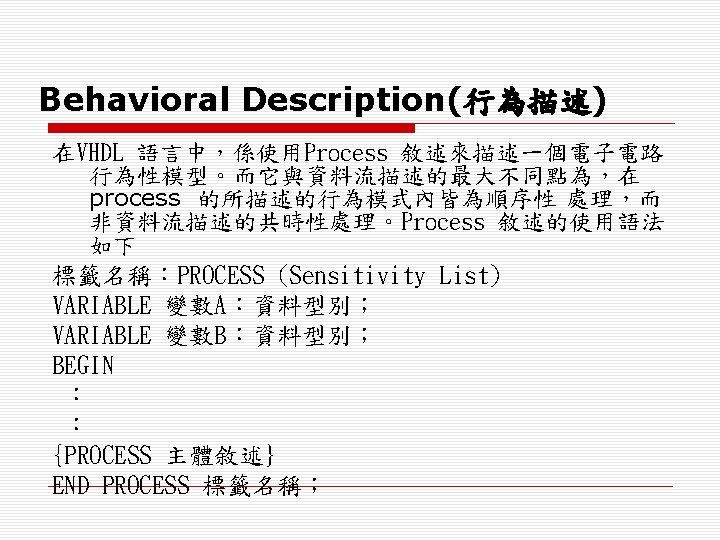

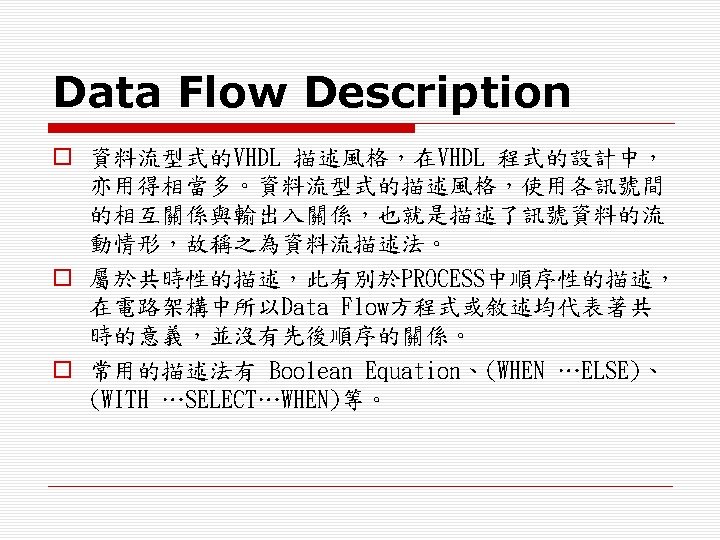

電路架構描述部分其設計的風格可歸納為三 種型式: 1. Behavioral Description (行為描述) 2. Data Flow Description(資料流描述) 3. Structure Descriptions (結構描述)

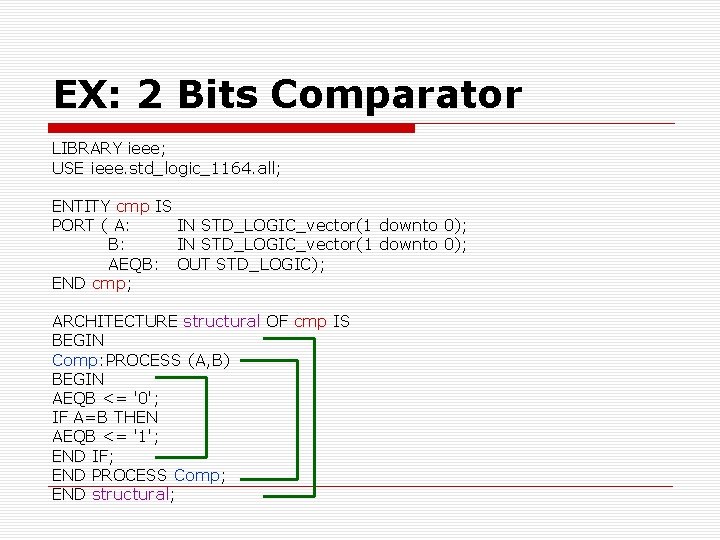

EX: 2 Bits Comparator LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY cmp IS PORT ( A: IN STD_LOGIC_vector(1 downto 0); B: IN STD_LOGIC_vector(1 downto 0); AEQB: OUT STD_LOGIC); END cmp; ARCHITECTURE structural OF cmp IS BEGIN Comp: PROCESS (A, B) BEGIN AEQB <= '0'; IF A=B THEN AEQB <= '1'; END IF; END PROCESS Comp; END structural;

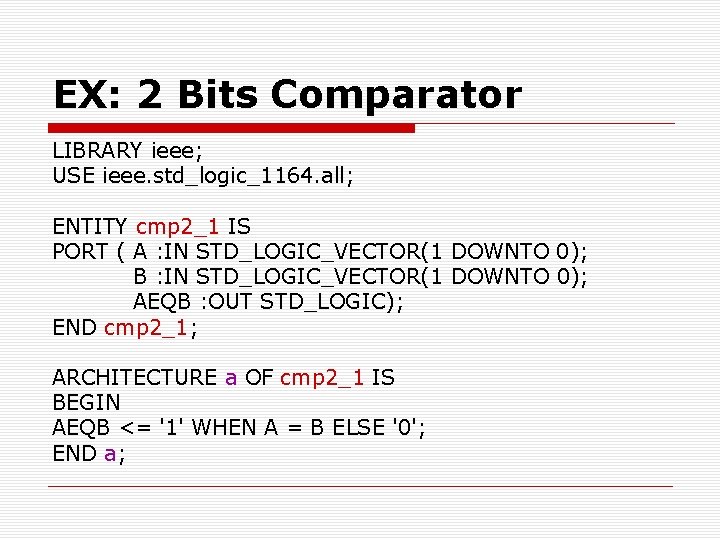

EX: 2 Bits Comparator LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY cmp 2_1 IS PORT ( A : IN STD_LOGIC_VECTOR(1 DOWNTO 0); B : IN STD_LOGIC_VECTOR(1 DOWNTO 0); AEQB : OUT STD_LOGIC); END cmp 2_1; ARCHITECTURE a OF cmp 2_1 IS BEGIN AEQB <= '1' WHEN A = B ELSE '0'; END a;

![Structure Descriptions (Cont’d) COMPONENT 元件名稱 PORT ( 訊號A :模式[IN, OUT, INOUT] 資料型別; 訊號B :模式[IN, Structure Descriptions (Cont’d) COMPONENT 元件名稱 PORT ( 訊號A :模式[IN, OUT, INOUT] 資料型別; 訊號B :模式[IN,](http://slidetodoc.com/presentation_image_h2/de7ef1dd012f2c0b516749f898533119/image-14.jpg)

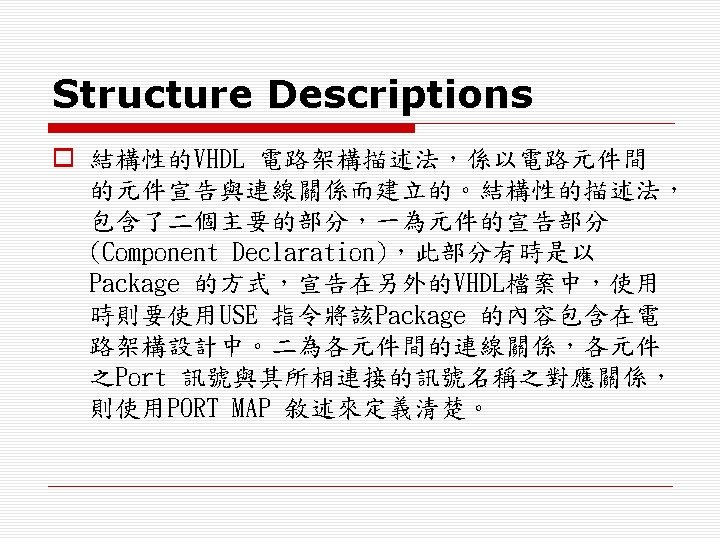

Structure Descriptions (Cont’d) COMPONENT 元件名稱 PORT ( 訊號A :模式[IN, OUT, INOUT] 資料型別; 訊號B :模式[IN, OUT, INOUT] 資料型別; : : 訊號N :模式[IN, OUT, INOUT] 資料型別; END COMPONENT

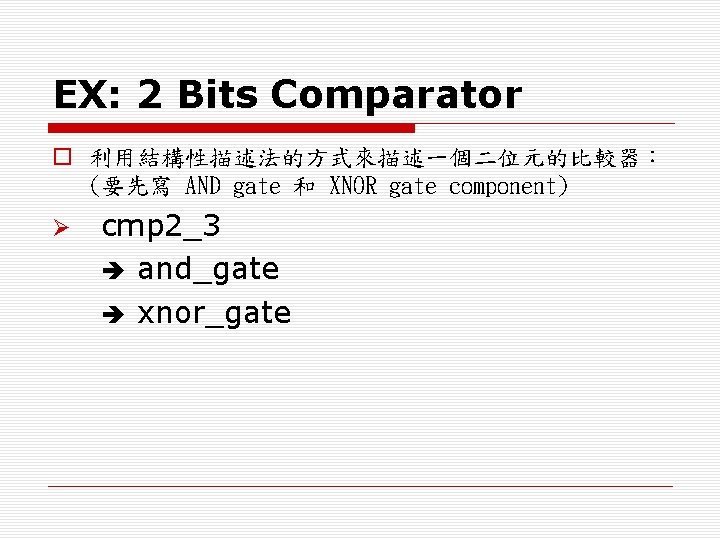

EX: 2 Bits Comparator o 利用結構性描述法的方式來描述一個二位元的比較器: (要先寫 AND gate 和 XNOR gate component) Ø cmp 2_3 and_gate xnor_gate

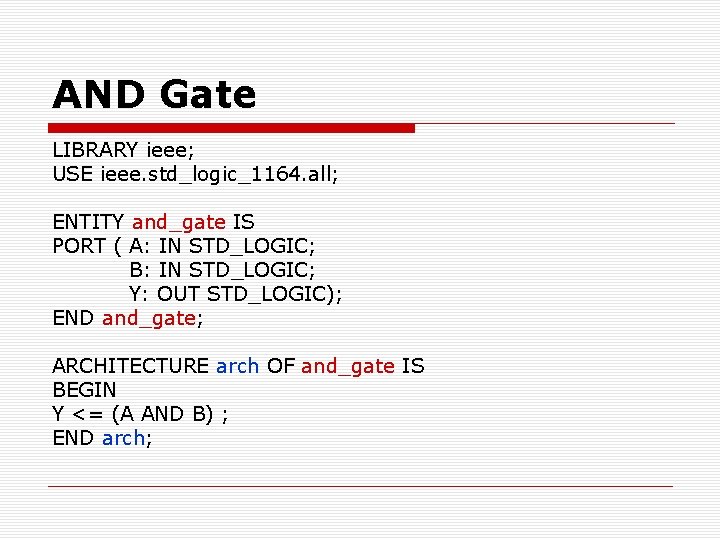

AND Gate LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY and_gate IS PORT ( A: IN STD_LOGIC; B: IN STD_LOGIC; Y: OUT STD_LOGIC); END and_gate; ARCHITECTURE arch OF and_gate IS BEGIN Y <= (A AND B) ; END arch;

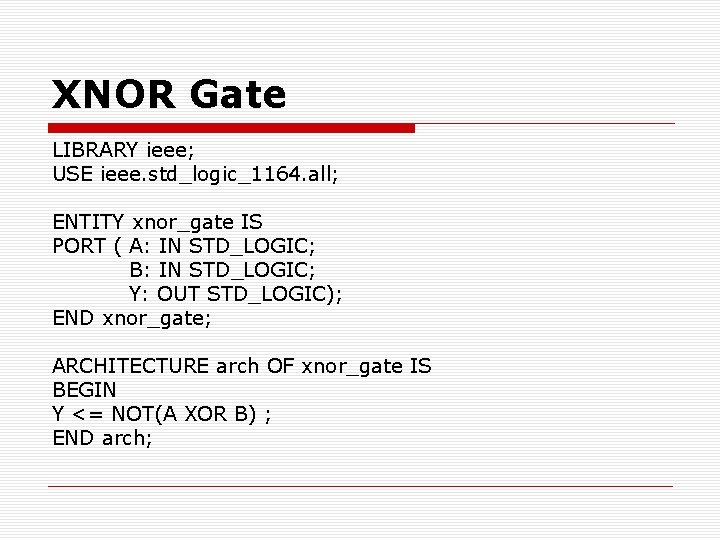

XNOR Gate LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY xnor_gate IS PORT ( A: IN STD_LOGIC; B: IN STD_LOGIC; Y: OUT STD_LOGIC); END xnor_gate; ARCHITECTURE arch OF xnor_gate IS BEGIN Y <= NOT(A XOR B) ; END arch;

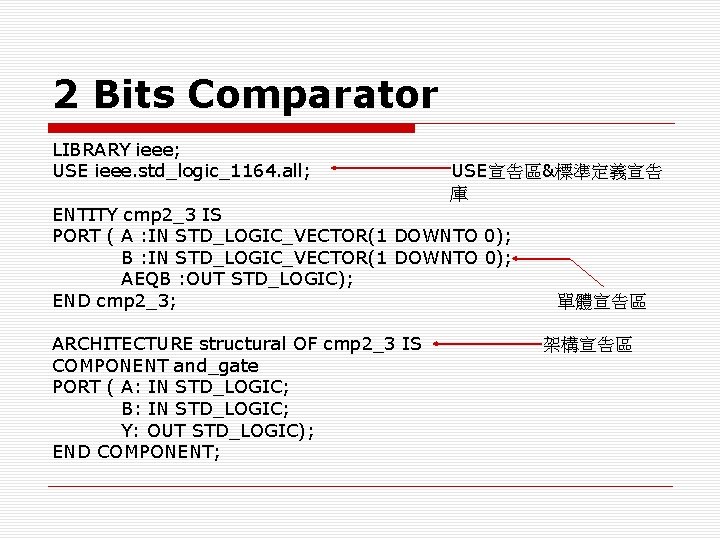

2 Bits Comparator LIBRARY ieee; USE ieee. std_logic_1164. all; USE宣告區&標準定義宣告 庫 ENTITY cmp 2_3 IS PORT ( A : IN STD_LOGIC_VECTOR(1 DOWNTO 0); B : IN STD_LOGIC_VECTOR(1 DOWNTO 0); AEQB : OUT STD_LOGIC); END cmp 2_3; ARCHITECTURE structural OF cmp 2_3 IS COMPONENT and_gate PORT ( A: IN STD_LOGIC; B: IN STD_LOGIC; Y: OUT STD_LOGIC); END COMPONENT; 單體宣告區 架構宣告區

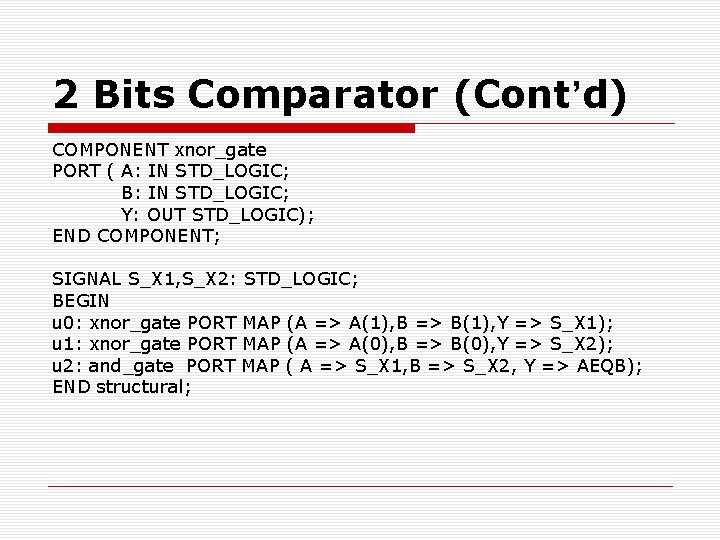

2 Bits Comparator (Cont’d) COMPONENT xnor_gate PORT ( A: IN STD_LOGIC; B: IN STD_LOGIC; Y: OUT STD_LOGIC); END COMPONENT; SIGNAL S_X 1, S_X 2: STD_LOGIC; BEGIN u 0: xnor_gate PORT MAP (A => A(1), B => B(1), Y => S_X 1); u 1: xnor_gate PORT MAP (A => A(0), B => B(0), Y => S_X 2); u 2: and_gate PORT MAP ( A => S_X 1, B => S_X 2, Y => AEQB); END structural;

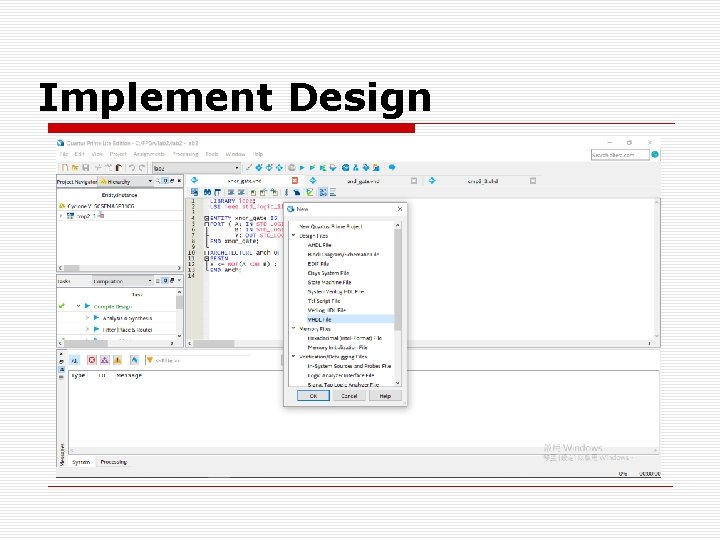

Implement Design

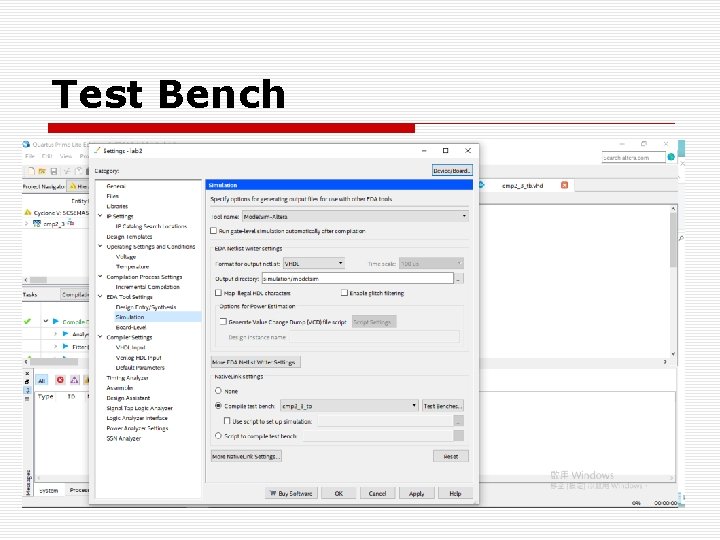

Test Bench

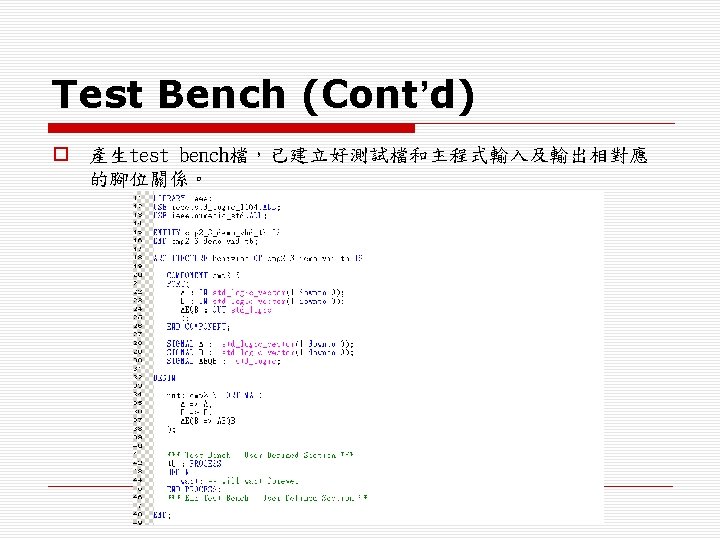

Test Bench (Cont’d) p 加入自行設計的輸入值和時間的對應關係 -- *** Test Bench - User Defined Section *** tb : PROCESS BEGIN A <= "01" ; (注意: 2 bits以上用雙引號, 1 bit用單引號) B <= "10" ; wait for 25 ns; A <= "11" ; B <= "10" ; wait for 25 ns; A <= "10" ; B <= "10" ; wait for 25 ns; A <= “ 00" ; B <= "11" ; wait; END PROCESS; -- *** End Test Bench - User Defined Section ***

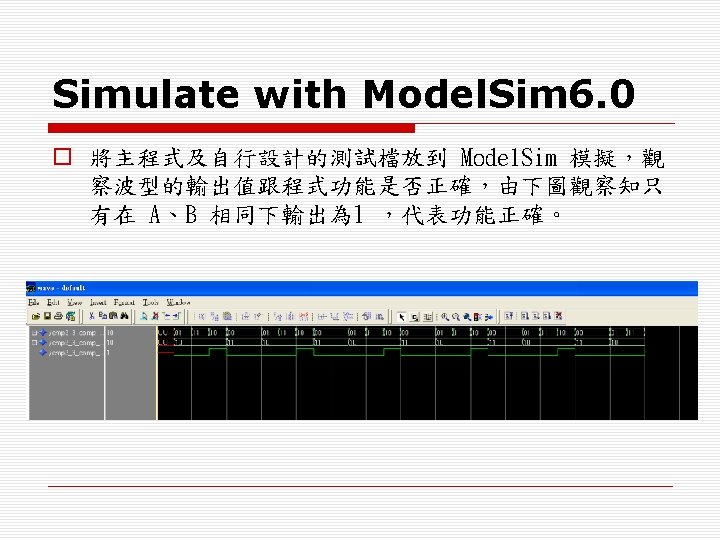

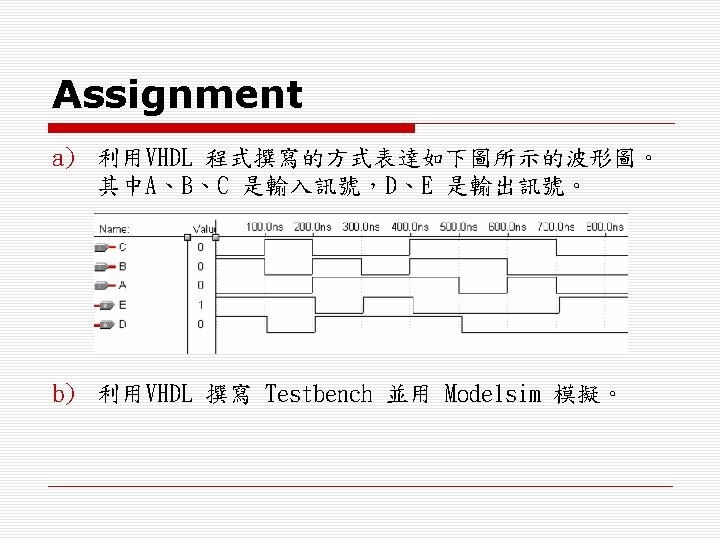

- Slides: 25