Programmable Configurations Read Only Memory ROM a fixed

Programmable Configurations • Read Only Memory (ROM) – – a fixed array of AND gates and a programmable array of OR gates • Programmable Array Logic (PAL)Ò – – a programmable array of AND gates feeding a fixed array of OR gates. • Programmable Logic Array (PLA) – – a programmable array of AND gates feeding a programmable array of OR gates. • Complex Programmable Logic Device (CPLD) /Field. Programmable Gate Array (FPGA) – – complex enough to be called “architectures” 1

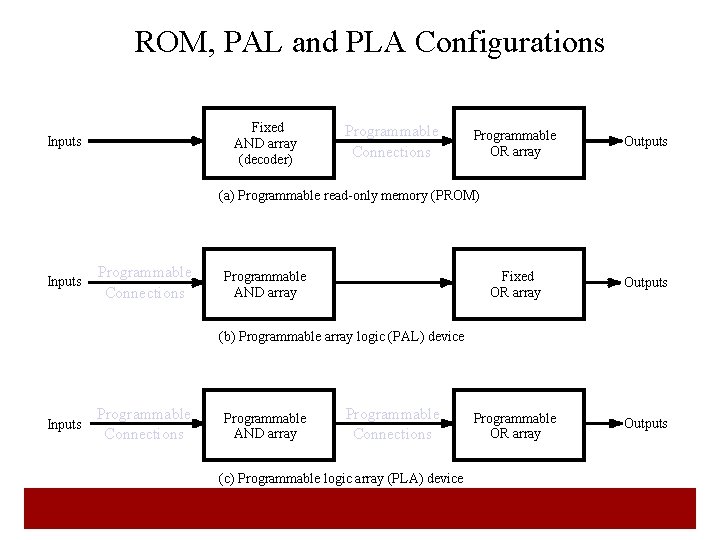

ROM, PAL and PLA Configurations Fixed AND array (decoder) Inputs Programmable Connections Programmable OR array Outputs (a) Programmable read-only memory (PROM) Inputs Programmable Connections Programmable AND array Fixed OR array Outputs Programmable OR array Outputs (b) Programmable array logic (PAL) device Inputs Programmable Connections Programmable AND array Programmable Connections (c) Programmable logic array (PLA) device 2

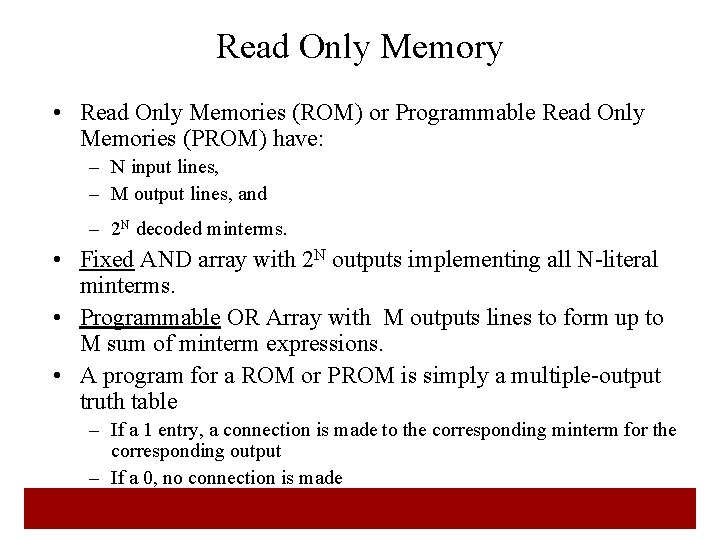

Read Only Memory • Read Only Memories (ROM) or Programmable Read Only Memories (PROM) have: – N input lines, – M output lines, and – 2 N decoded minterms. • Fixed AND array with 2 N outputs implementing all N-literal minterms. • Programmable OR Array with M outputs lines to form up to M sum of minterm expressions. • A program for a ROM or PROM is simply a multiple-output truth table – If a 1 entry, a connection is made to the corresponding minterm for the corresponding output – If a 0, no connection is made 3

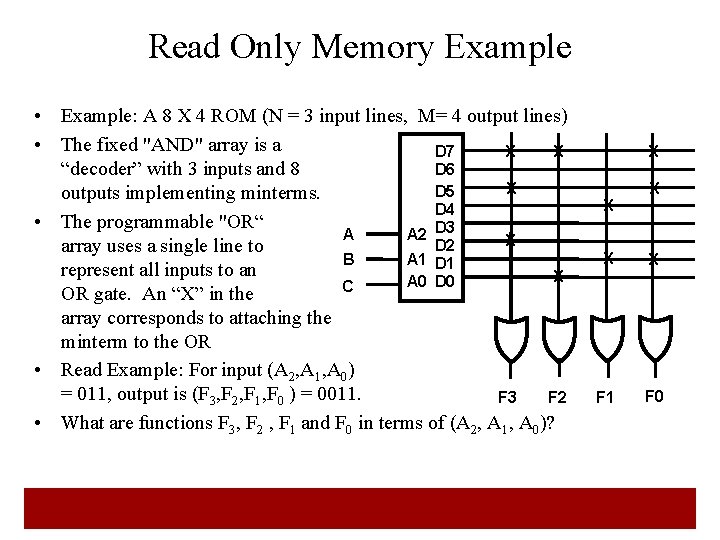

Read Only Memory Example • Example: A 8 X 4 ROM (N = 3 input lines, M= 4 output lines) • The fixed "AND" array is a X X D 7 “decoder” with 3 inputs and 8 D 6 X D 5 outputs implementing minterms. D 4 • The programmable "OR“ A 2 D 3 A X D 2 array uses a single line to B A 1 D 1 represent all inputs to an X A 0 D 0 C OR gate. An “X” in the array corresponds to attaching the minterm to the OR • Read Example: For input (A 2, A 1, A 0) = 011, output is (F 3, F 2, F 1, F 0 ) = 0011. F 2 F 3 • What are functions F 3, F 2 , F 1 and F 0 in terms of (A 2, A 1, A 0)? X X X F 1 F 0 4

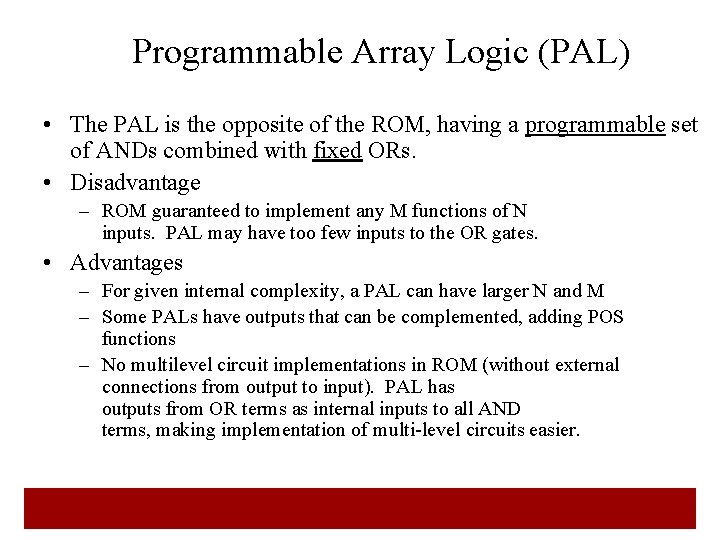

Programmable Array Logic (PAL) • The PAL is the opposite of the ROM, having a programmable set of ANDs combined with fixed ORs. • Disadvantage – ROM guaranteed to implement any M functions of N inputs. PAL may have too few inputs to the OR gates. • Advantages – For given internal complexity, a PAL can have larger N and M – Some PALs have outputs that can be complemented, adding POS functions – No multilevel circuit implementations in ROM (without external connections from output to input). PAL has outputs from OR terms as internal inputs to all AND terms, making implementation of multi-level circuits easier. 5

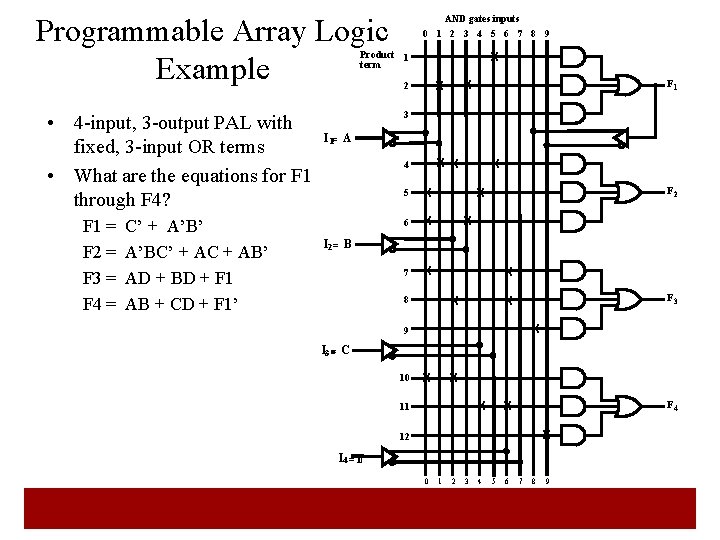

Programmable Array Logic Example AND gates inputs 0 1 2 3 4 5 6 7 8 9 Product 1 term X X F 1 3 I 1= A X X X 6 X 7 F 2 X 5 X 4 X X I 2 = B X X 8 F 3 X X 9 I 3 = C X 11 X X 10 X F 4 X F 1 = C’ + A’B’ F 2 = A’BC’ + AC + AB’ F 3 = AD + BD + F 1 F 4 = AB + CD + F 1’ X • 4 -input, 3 -output PAL with fixed, 3 -input OR terms • What are the equations for F 1 through F 4? 2 12 I 4 = D 0 1 2 3 4 5 6 7 8 9 6

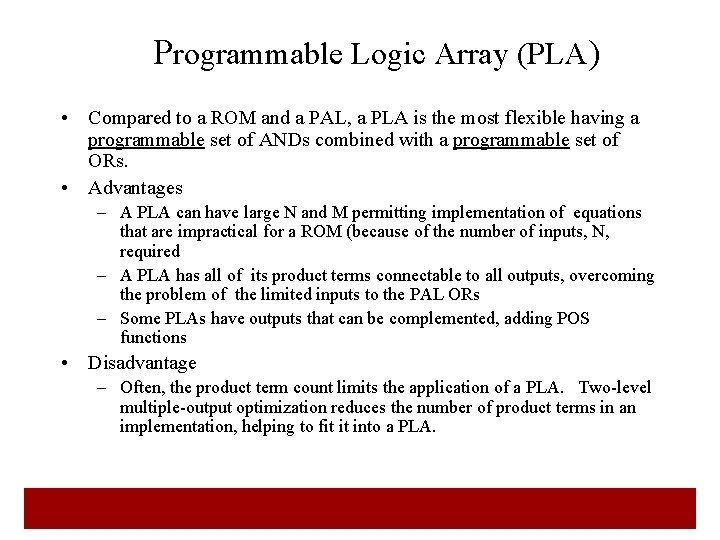

Programmable Logic Array (PLA) • Compared to a ROM and a PAL, a PLA is the most flexible having a programmable set of ANDs combined with a programmable set of ORs. • Advantages – A PLA can have large N and M permitting implementation of equations that are impractical for a ROM (because of the number of inputs, N, required – A PLA has all of its product terms connectable to all outputs, overcoming the problem of the limited inputs to the PAL ORs – Some PLAs have outputs that can be complemented, adding POS functions • Disadvantage – Often, the product term count limits the application of a PLA. Two-level multiple-output optimization reduces the number of product terms in an implementation, helping to fit it into a PLA. 7

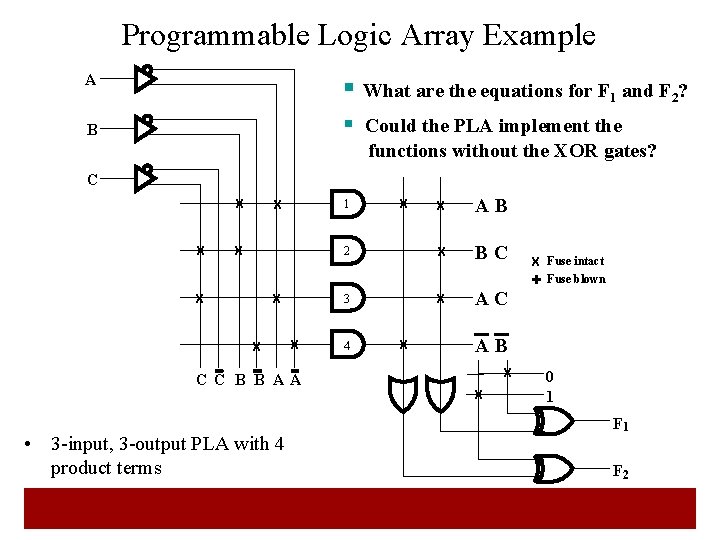

Programmable Logic Array Example A § What are the equations for F 1 and F 2? B § Could the PLA implement the functions without the XOR gates? C X X X X C C B B AA • 3 -input, 3 -output PLA with 4 product terms X AB 2 X BC 3 X AC 1 X 4 X X X Fuse intact Fuse blown AB X X 0 1 F 2 8

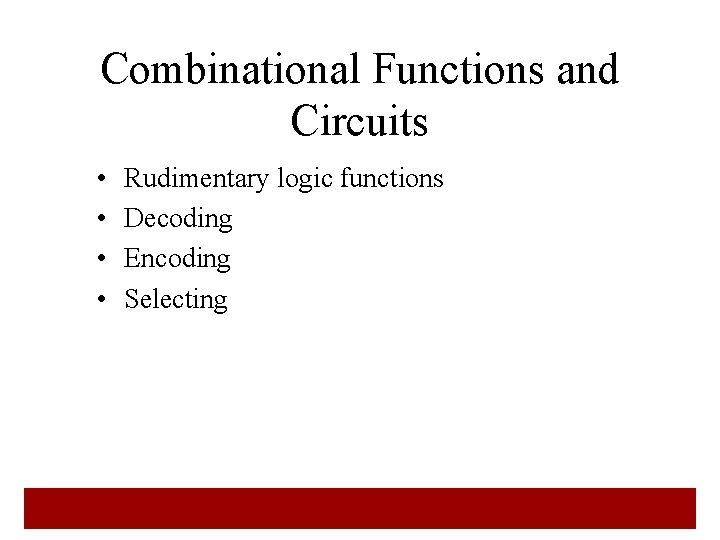

Combinational Functions and Circuits • • Rudimentary logic functions Decoding Encoding Selecting 9

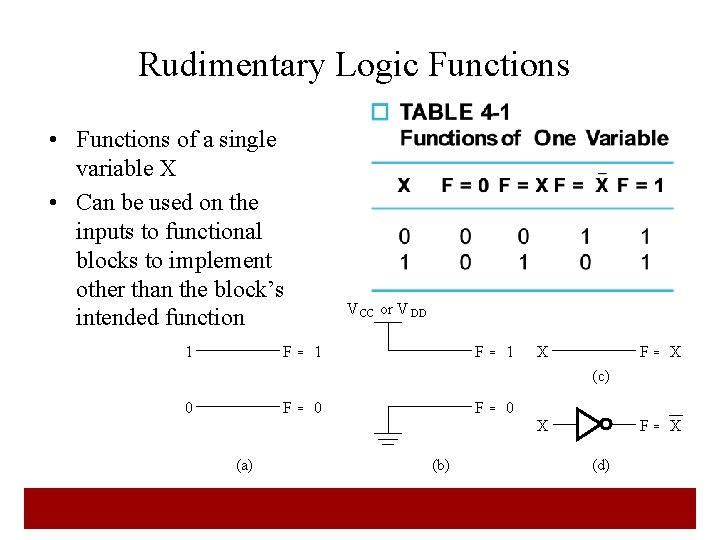

Rudimentary Logic Functions • Functions of a single variable X • Can be used on the inputs to functional blocks to implement other than the block’s intended function 1 V CC or V DD F = 1 X F = X (c) 0 F = 0 X (a) (b) F = X (d) 10

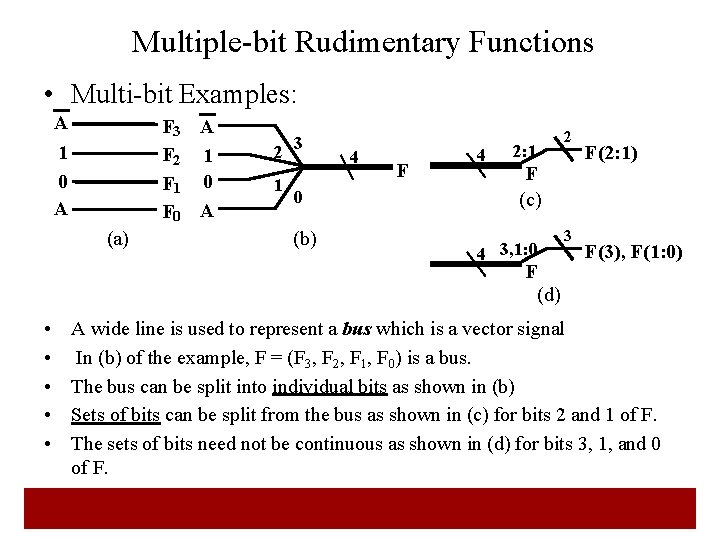

Multiple-bit Rudimentary Functions • Multi-bit Examples: A 1 0 A F 3 F 2 F 1 F 0 (a) A 1 0 A 2 1 3 0 (b) 4 F 4 2: 1 F (c) 4 3, 1: 0 F (d) • • • 2 3 F(2: 1) F(3), F(1: 0) A wide line is used to represent a bus which is a vector signal In (b) of the example, F = (F 3, F 2, F 1, F 0) is a bus. The bus can be split into individual bits as shown in (b) Sets of bits can be split from the bus as shown in (c) for bits 2 and 1 of F. The sets of bits need not be continuous as shown in (d) for bits 3, 1, and 0 of F. 11

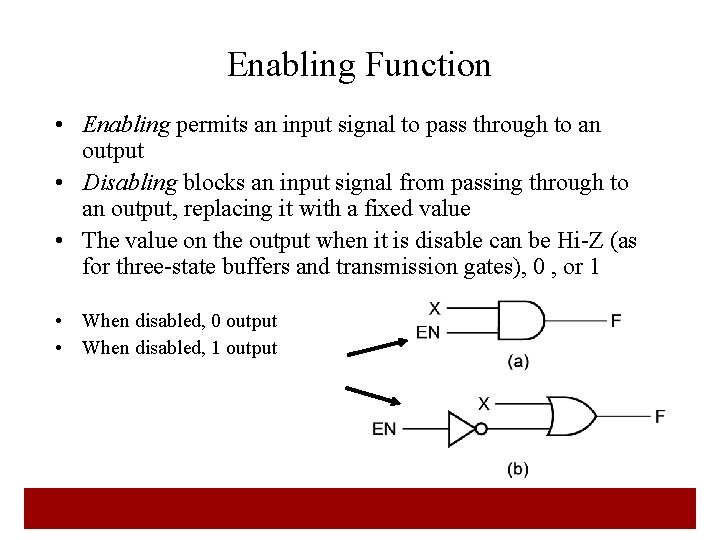

Enabling Function • Enabling permits an input signal to pass through to an output • Disabling blocks an input signal from passing through to an output, replacing it with a fixed value • The value on the output when it is disable can be Hi-Z (as for three-state buffers and transmission gates), 0 , or 1 • When disabled, 0 output • When disabled, 1 output 12

Decoders • Multiple-input multiple-output logic circuit which maps coded inputs to coded outputs • n input bits can code upto 2 n different output bits • n-to-m decoder: maps n-bit input to m-bit output where m < 2 n 13

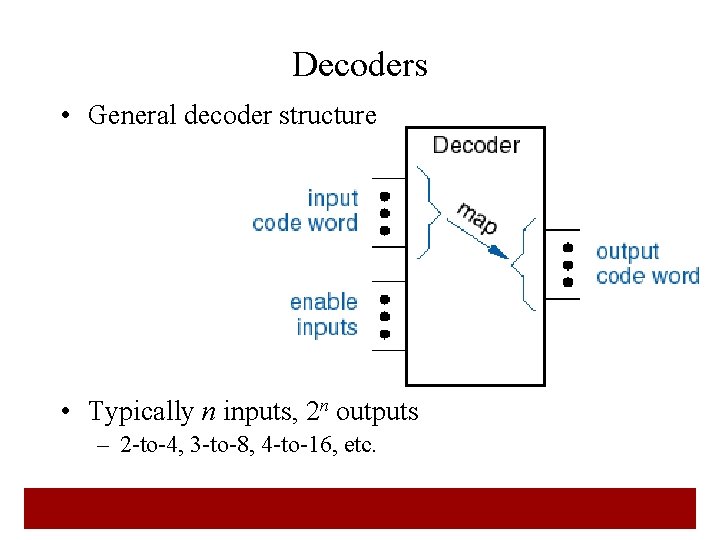

Decoders • General decoder structure • Typically n inputs, 2 n outputs – 2 -to-4, 3 -to-8, 4 -to-16, etc. 14

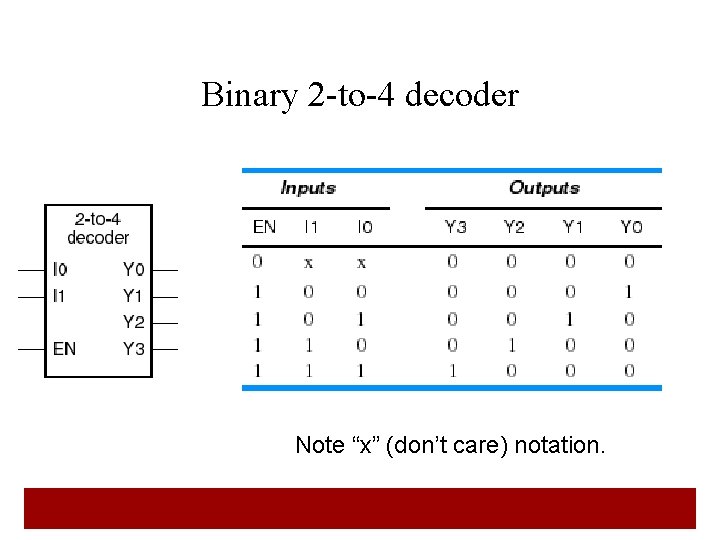

Binary 2 -to-4 decoder Note “x” (don’t care) notation. 15

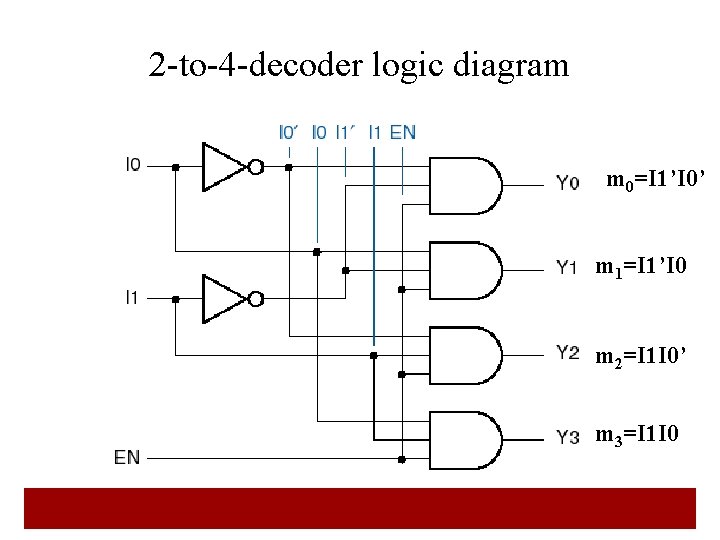

2 -to-4 -decoder logic diagram m 0=I 1’I 0’ m 1=I 1’I 0 m 2=I 1 I 0’ m 3=I 1 I 0 16

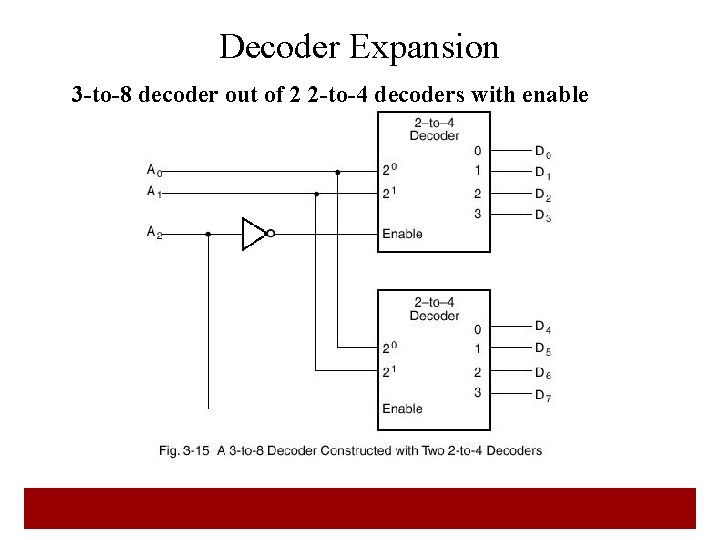

Decoder Expansion 3 -to-8 decoder out of 2 2 -to-4 decoders with enable 17

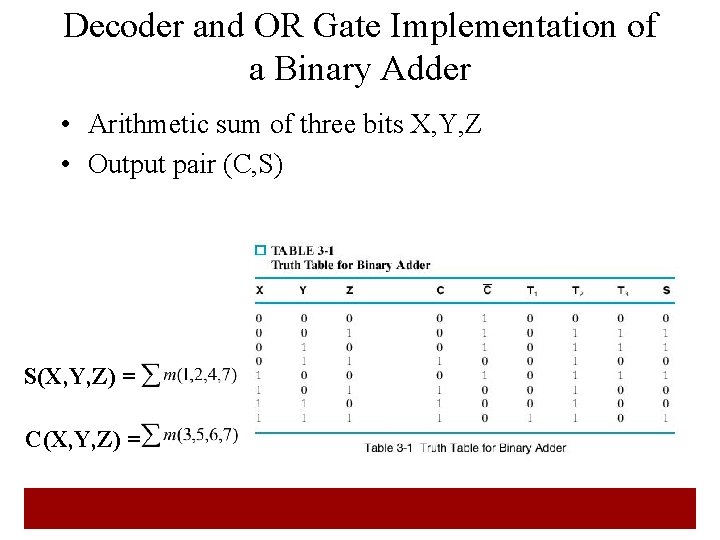

Decoder and OR Gate Implementation of a Binary Adder • Arithmetic sum of three bits X, Y, Z • Output pair (C, S) S(X, Y, Z) = C(X, Y, Z) = 18

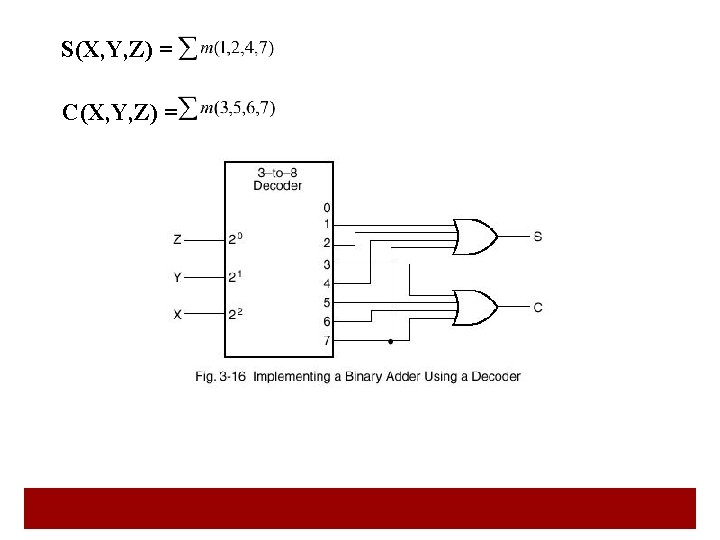

S(X, Y, Z) = C(X, Y, Z) = 19

Decoder Applications • Microprocessor memory systems – Selecting different banks of memory • Microprocessor input/output systems – Selecting different devices • Microprocessor instruction decoding – Enabling different functional units • Memory chips – Enabling different rows of memory depending on address • Lots of other applications – Seven segment decoder, 4 -to-7 decoder 20

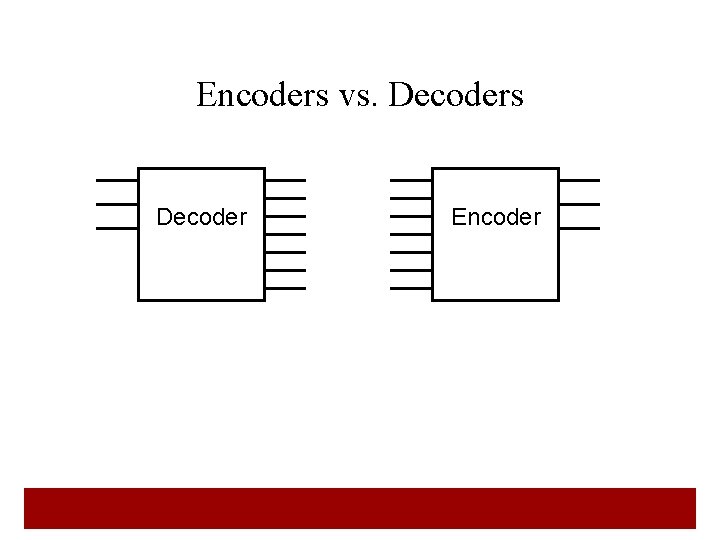

Encoders vs. Decoders Decoder Encoder 21

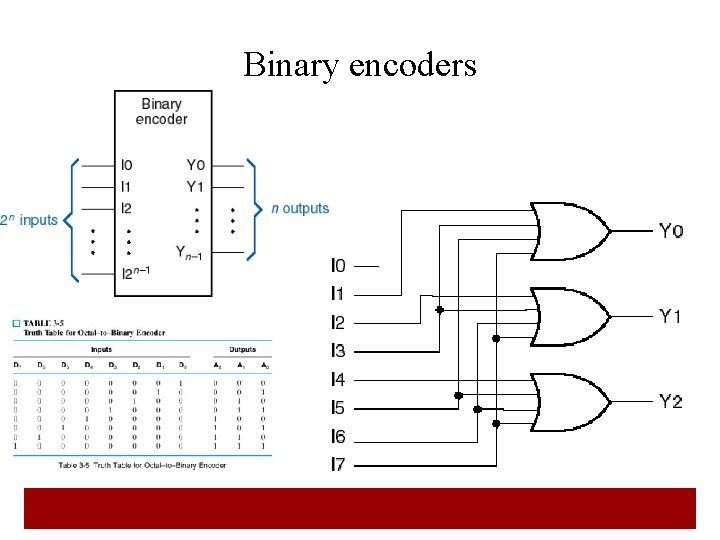

Binary encoders 22

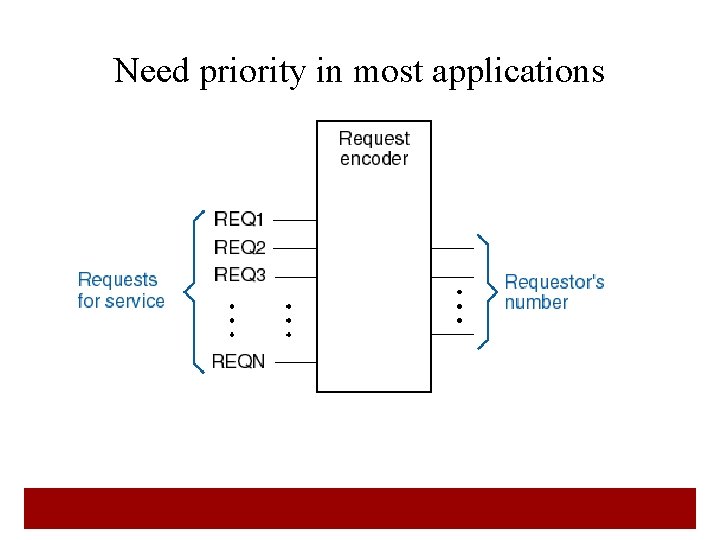

Need priority in most applications 23

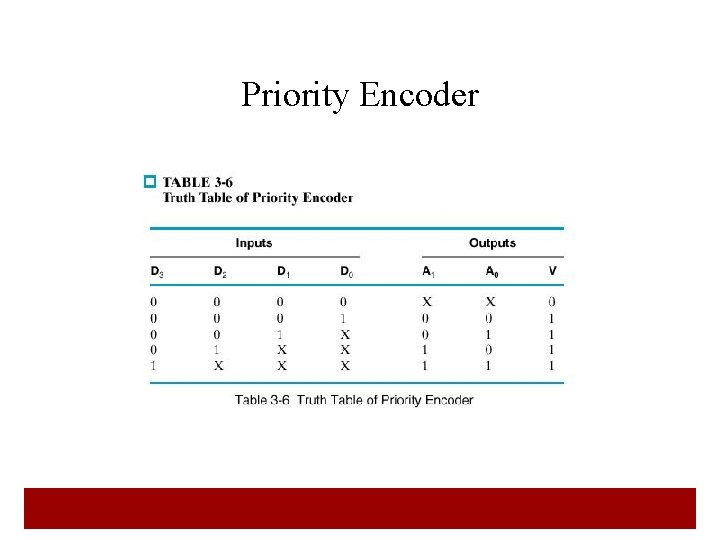

Priority Encoder 24

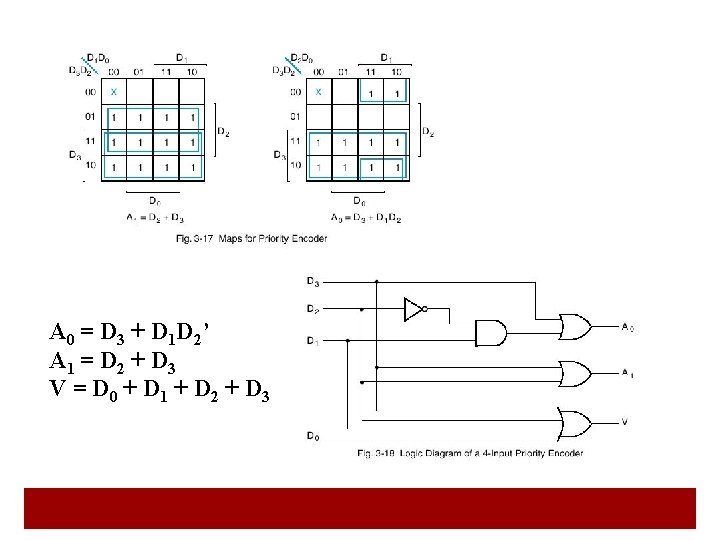

A 0 = D 3 + D 1 D 2’ A 1 = D 2 + D 3 V = D 0 + D 1 + D 2 + D 3 25

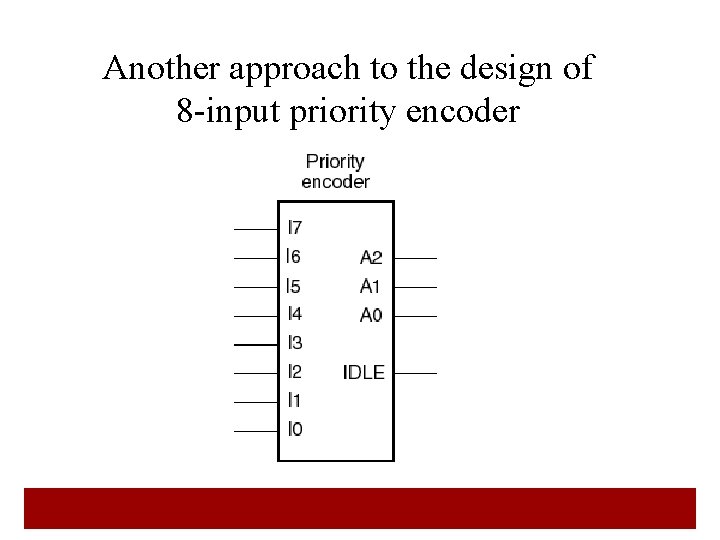

Another approach to the design of 8 -input priority encoder 26

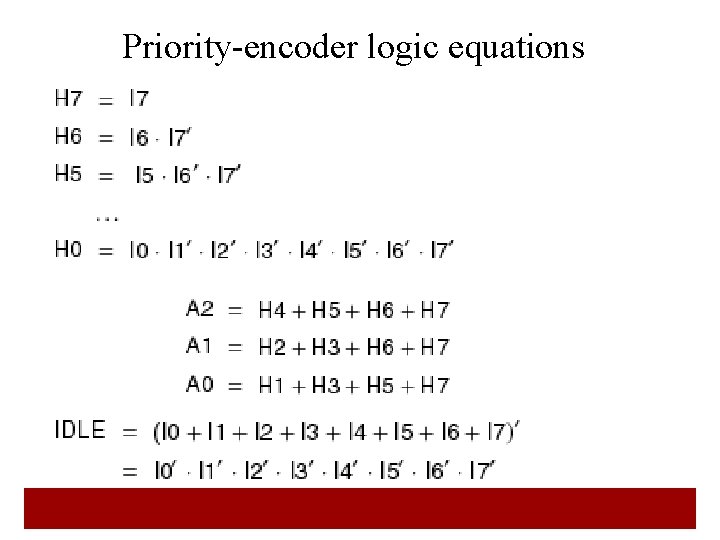

Priority-encoder logic equations 27

Selecting • Selecting of data or information is a critical function in digital systems and computers • Circuits that perform selecting have: – A set of information inputs from which the selection is made – A single output – A set of control lines for making the selection • Logic circuits that perform selecting are called multiplexers • Selecting can also be done by three-state logic or transmission gates 28

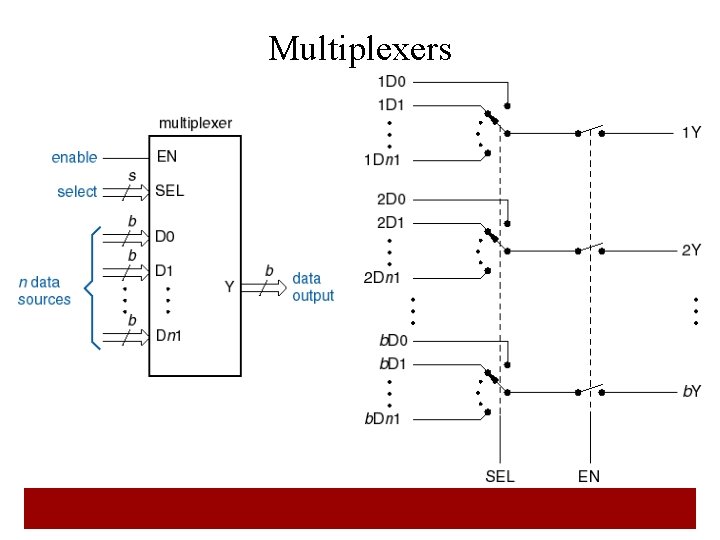

Multiplexers • MUX: – Selects binary information from one of many input lines and directs the information to a single output line. – Selection of a particular input is controlled by a set of input variables. – # of selection control bits: n n-to-1 MUX 2 – # of possible input lines: 2 n – # of output: 1 29

Multiplexers 30

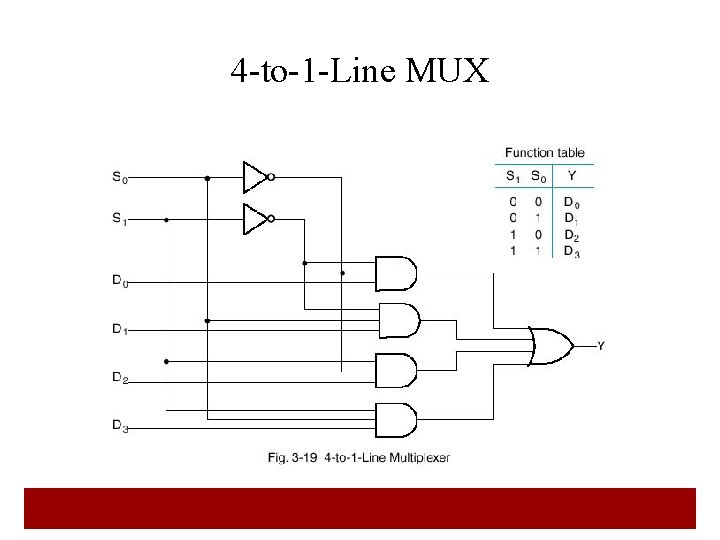

4 -to-1 -Line MUX 31

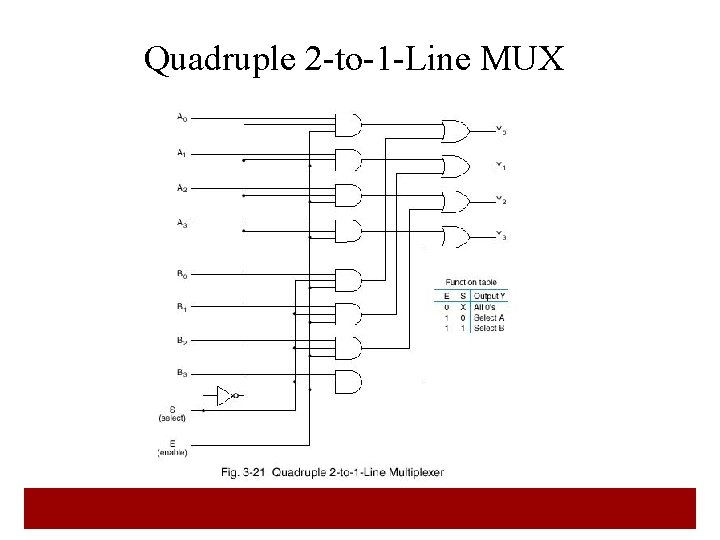

Quadruple 2 -to-1 -Line MUX 32

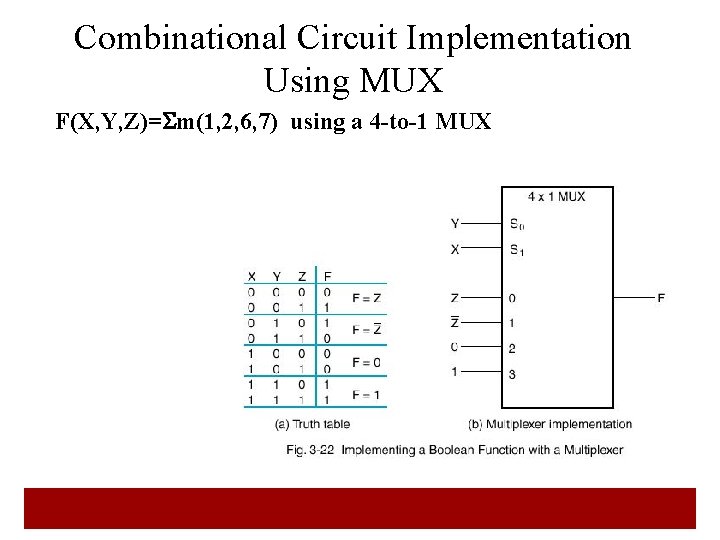

Combinational Circuit Implementation Using MUX F(X, Y, Z)= m(1, 2, 6, 7) using a 4 -to-1 MUX 33

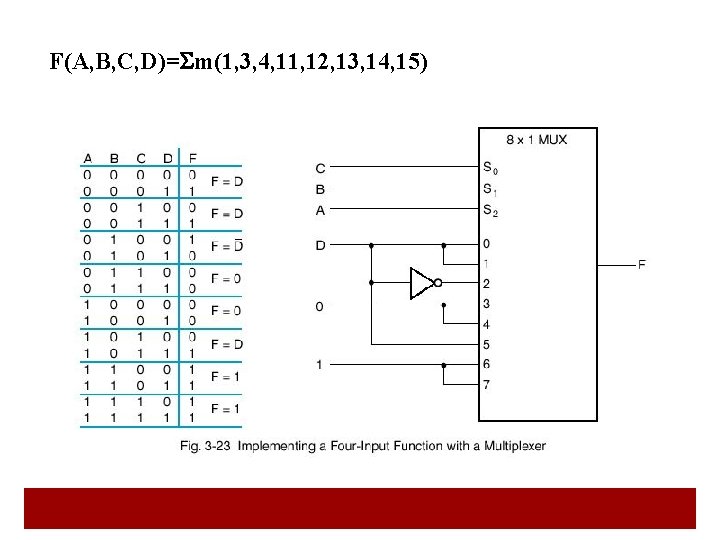

F(A, B, C, D)= m(1, 3, 4, 11, 12, 13, 14, 15) 34

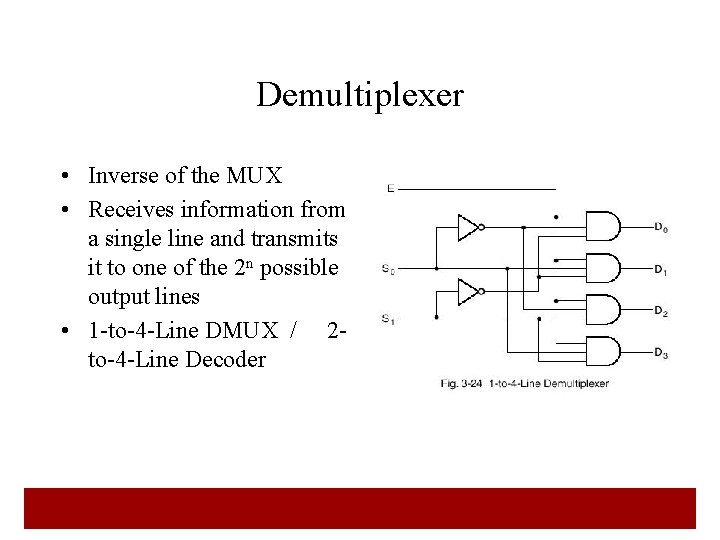

Demultiplexer • Inverse of the MUX • Receives information from a single line and transmits it to one of the 2 n possible output lines • 1 -to-4 -Line DMUX / 2 to-4 -Line Decoder 35

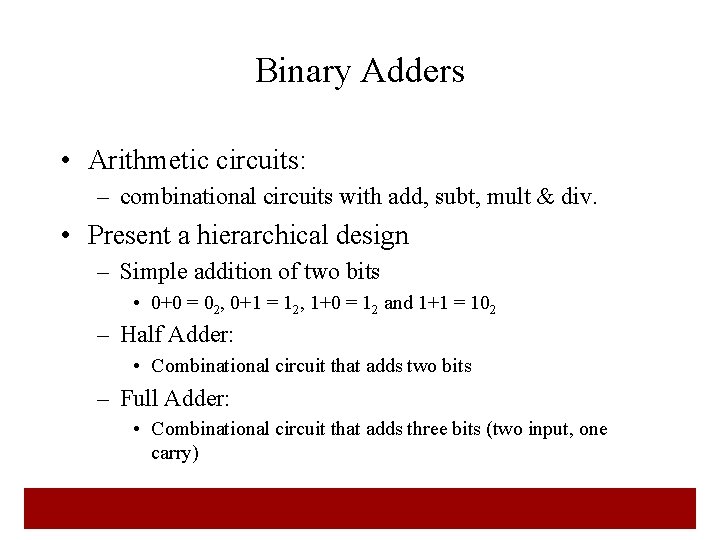

Binary Adders • Arithmetic circuits: – combinational circuits with add, subt, mult & div. • Present a hierarchical design – Simple addition of two bits • 0+0 = 02, 0+1 = 12, 1+0 = 12 and 1+1 = 102 – Half Adder: • Combinational circuit that adds two bits – Full Adder: • Combinational circuit that adds three bits (two input, one carry) 36

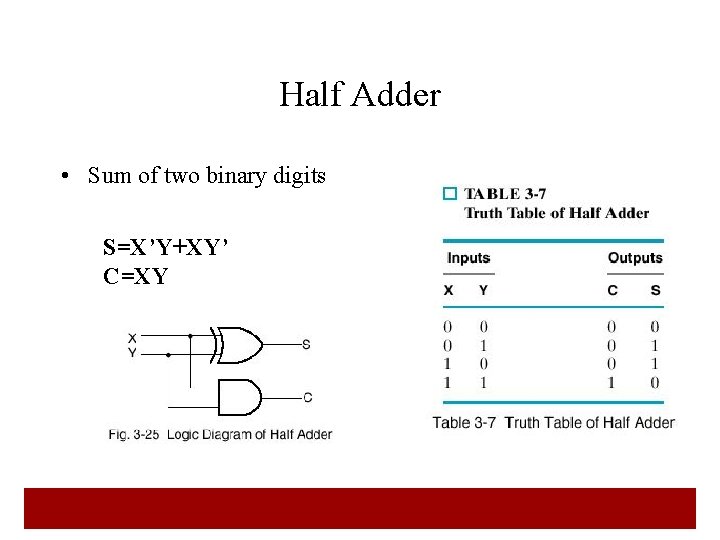

Half Adder • Sum of two binary digits S=X’Y+XY’ C=XY 37

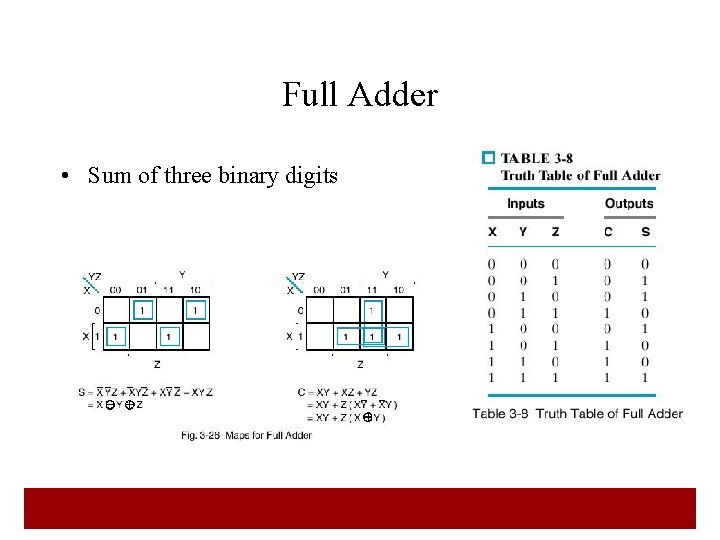

Full Adder • Sum of three binary digits 38

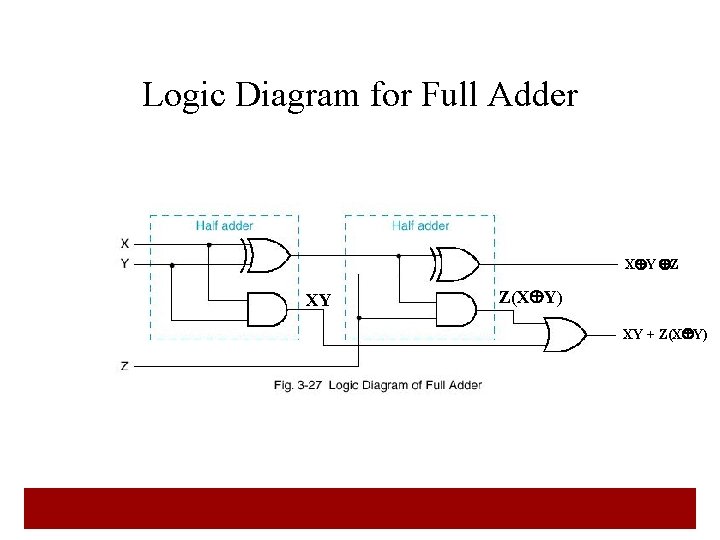

Logic Diagram for Full Adder X Y Z XY Z(X Y) XY + Z(X Y) 39

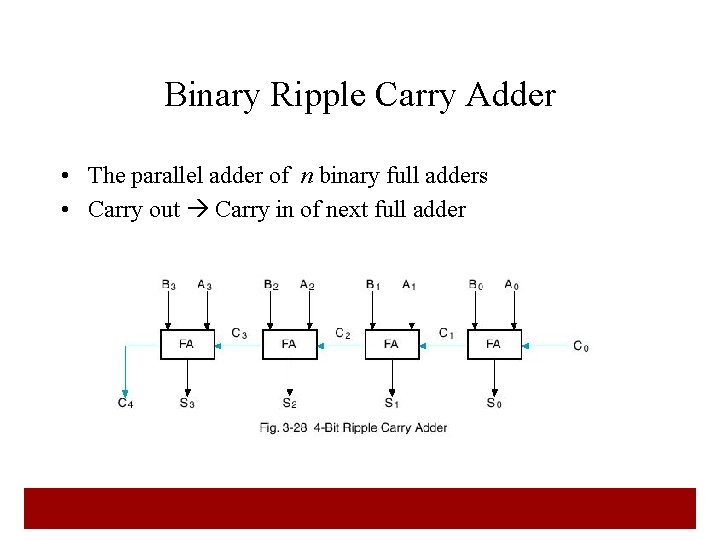

Binary Ripple Carry Adder • The parallel adder of n binary full adders • Carry out Carry in of next full adder 40

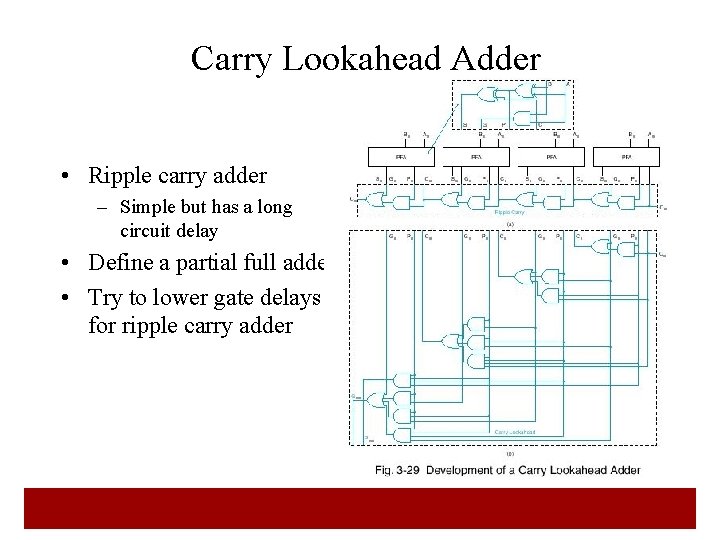

Carry Lookahead Adder • Ripple carry adder – Simple but has a long circuit delay • Define a partial full adder • Try to lower gate delays for ripple carry adder 41

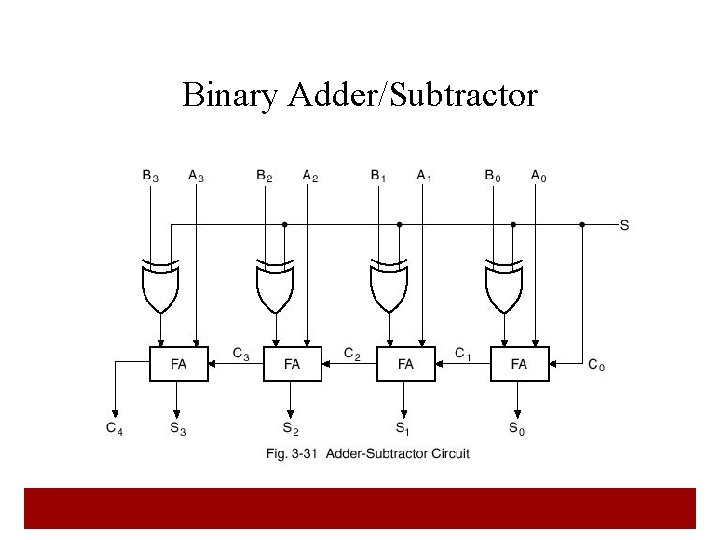

Binary Adder/Subtractor 42

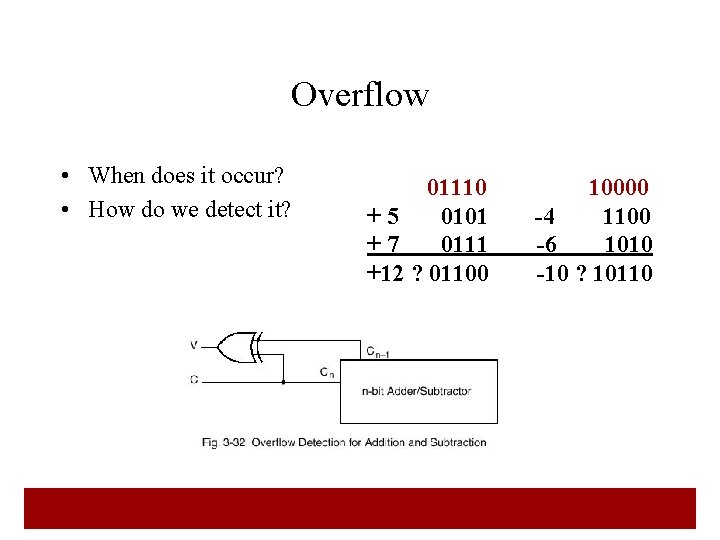

Overflow • When does it occur? • How do we detect it? 01110 +5 0101 +7 0111 +12 ? 01100 10000 -4 1100 -6 1010 -10 ? 10110 43

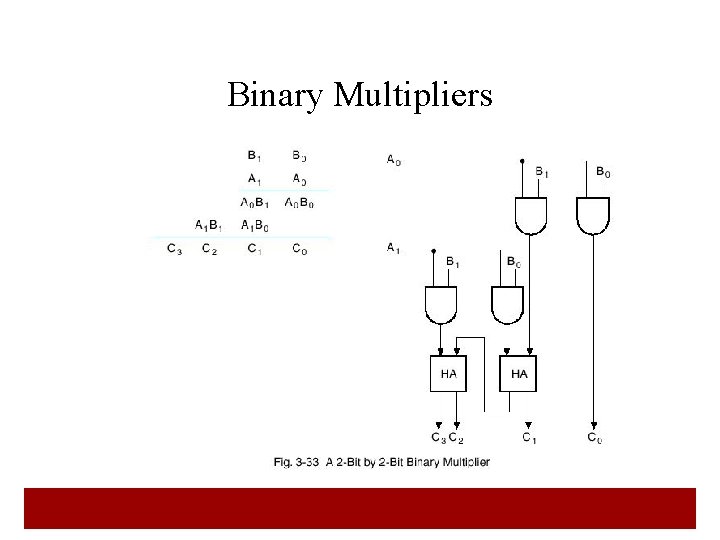

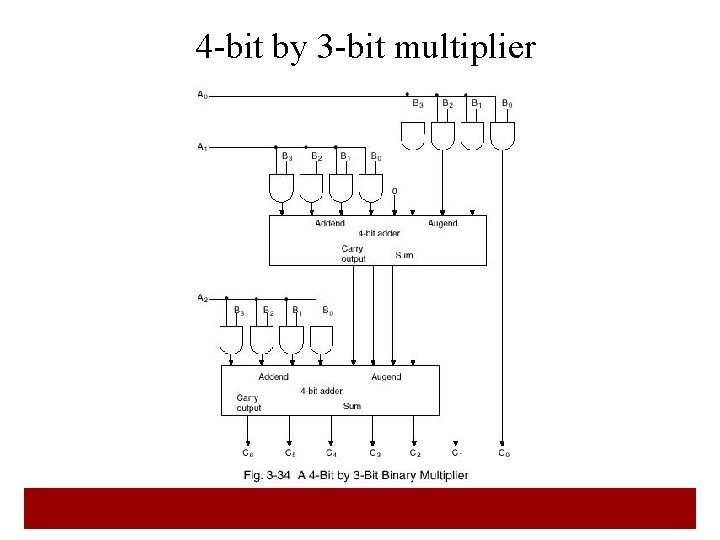

Binary Multipliers 44

4 -bit by 3 -bit multiplier 45

- Slides: 45