Programmable and Adaptive Analog FloatingGate Circuits Jeff Dugger

Programmable and Adaptive Analog Floating-Gate Circuits Jeff Dugger Georgia Tech School of ECE 2001 Telluride Neuromorphic Workshop

Overview of Floating-Gate Systems Ø Basic Floating-Gate Operation: • Computation • Weight Storage • Weight Programming and Adaptation Mechanisms Ø Computing in Memory: programmable/adaptive vector-matrix core Ø Programming infrastructure and methods Ø Adaptation via correlation learning rules

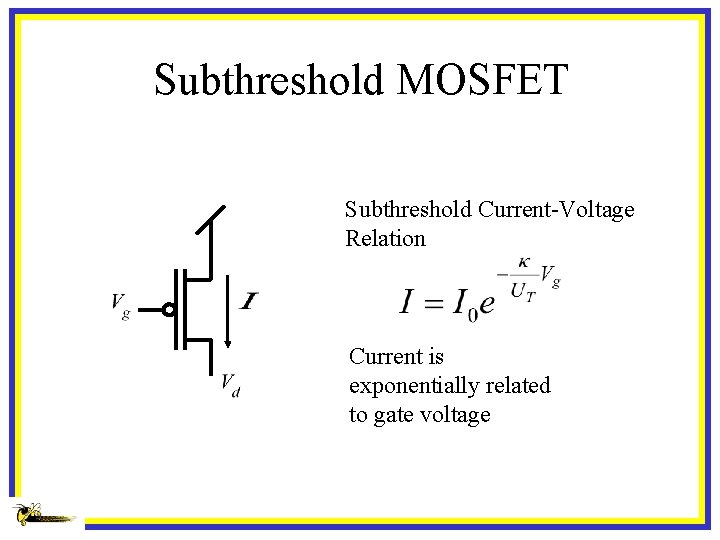

Subthreshold MOSFET Subthreshold Current-Voltage Relation Current is exponentially related to gate voltage

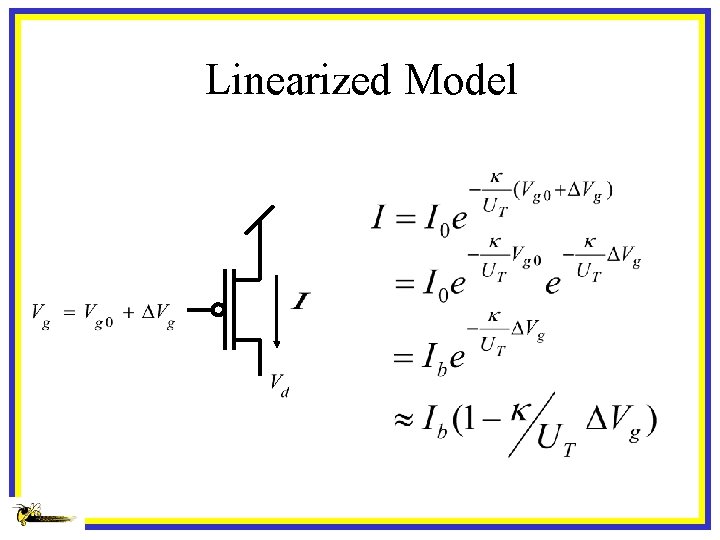

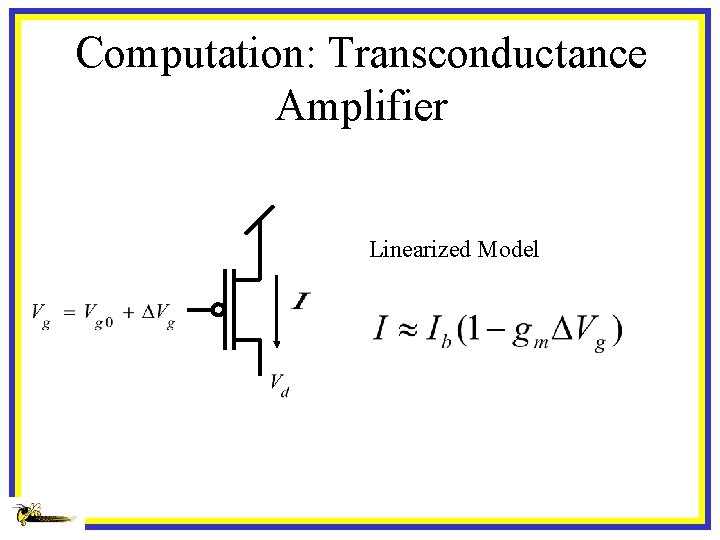

Linearized Model

Computation: Transconductance Amplifier Linearized Model

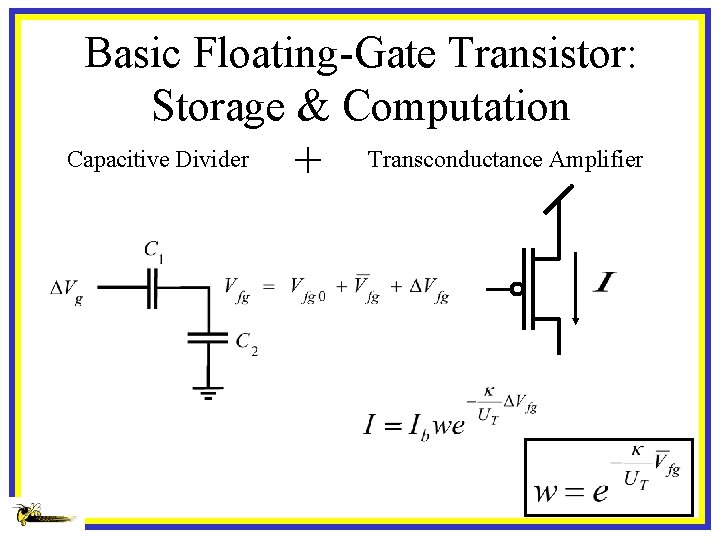

Basic Floating-Gate Transistor: Storage & Computation Capacitive Divider + Transconductance Amplifier

Basic Floating-Gate Transistor: Storage & Computation Weight Capacitor-coupled transconductance

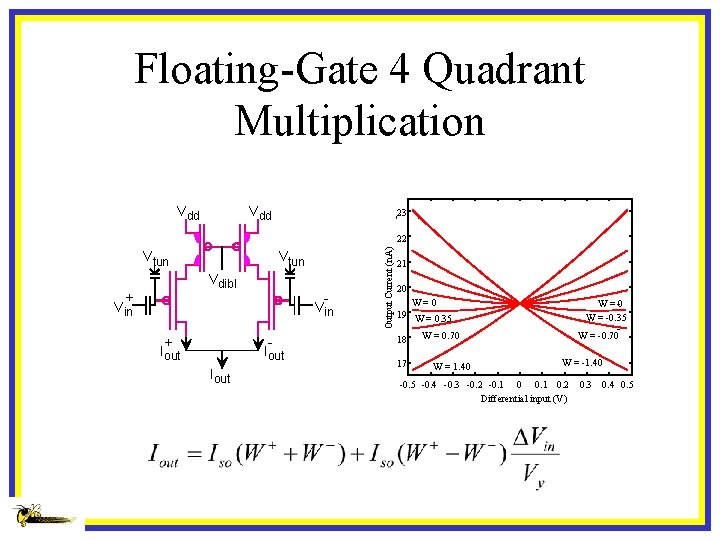

Floating-Gate 4 Quadrant Multiplication Vdd 23 Vtun Vdibl + Vin + Iout Output Current (n. A) 22 21 20 W=0 19 W = 0. 35 18 17 W=0 W = -0. 35 W = -0. 70 W = 1. 40 W = -1. 40 -0. 5 -0. 4 -0. 3 -0. 2 -0. 1 0. 2 Differential input (V) 0. 3 0. 4 0. 5

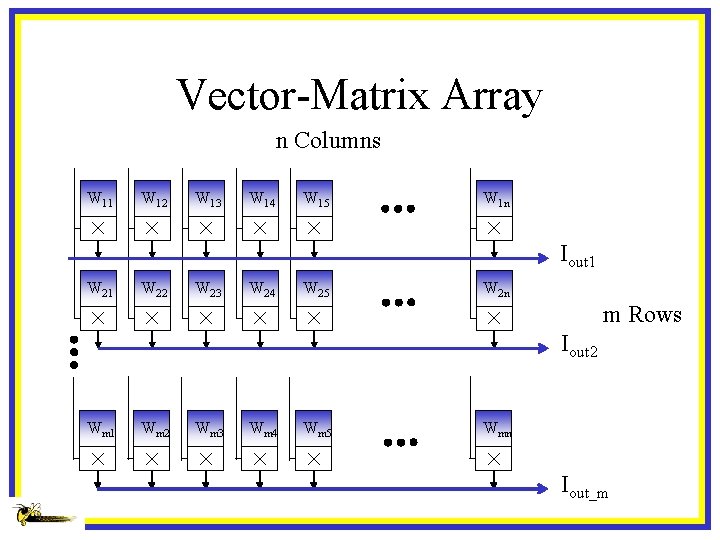

Vector-Matrix Array n Columns W 11 W 12 W 13 W 14 W 15 W 1 n Iout 1 W 22 W 23 W 24 W 25 W 2 n m Rows Iout 2 Wm 1 Wm 2 Wm 3 Wm 4 Wm 5 Wmn Iout_m

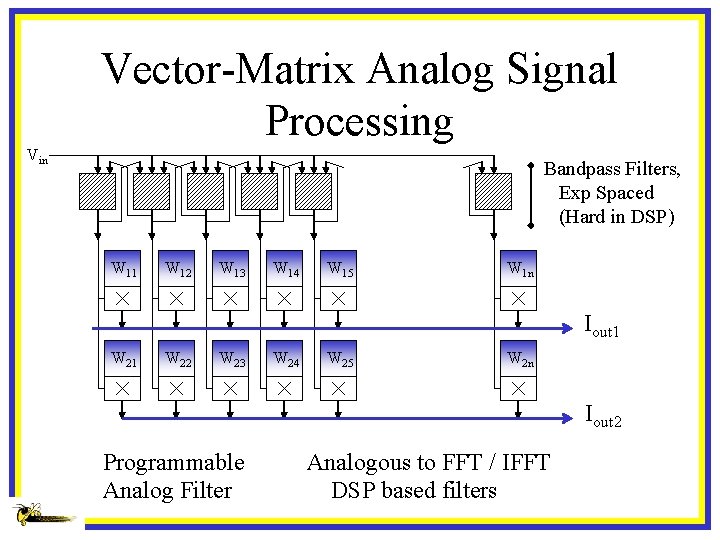

Vector-Matrix Analog Signal Processing Vin Bandpass Filters, Bandpass Exp Spaced Filters (Hard in DSP) W 11 W 12 W 13 W 14 W 15 W 1 n Iout 1 W 22 W 23 W 24 W 25 W 2 n Iout 2 Programmable Analog Filter Analogous to FFT / IFFT DSP based filters

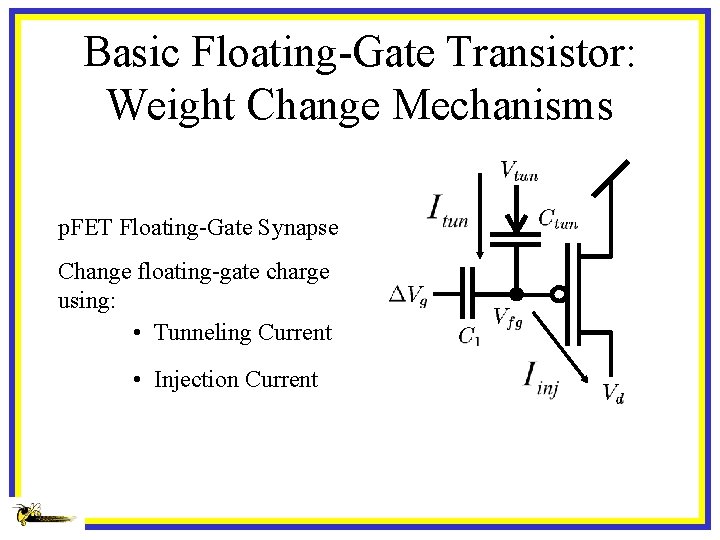

Basic Floating-Gate Transistor: Weight Change Mechanisms p. FET Floating-Gate Synapse Change floating-gate charge using: • Tunneling Current • Injection Current

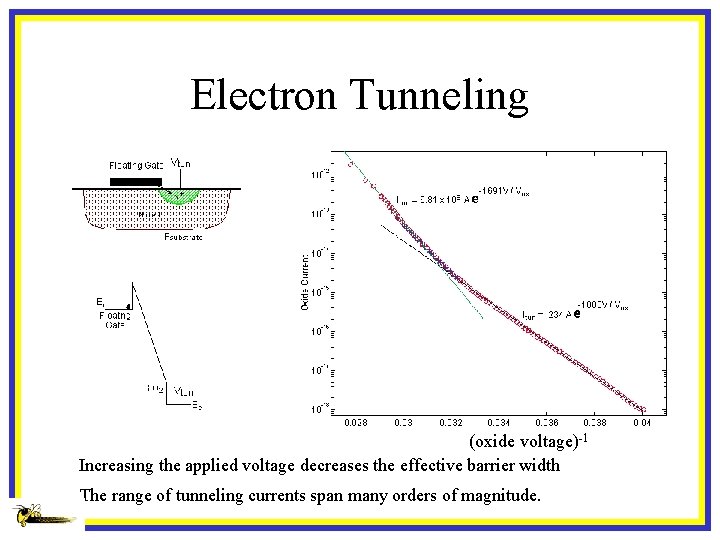

Electron Tunneling (oxide voltage)-1 Increasing the applied voltage decreases the effective barrier width The range of tunneling currents span many orders of magnitude.

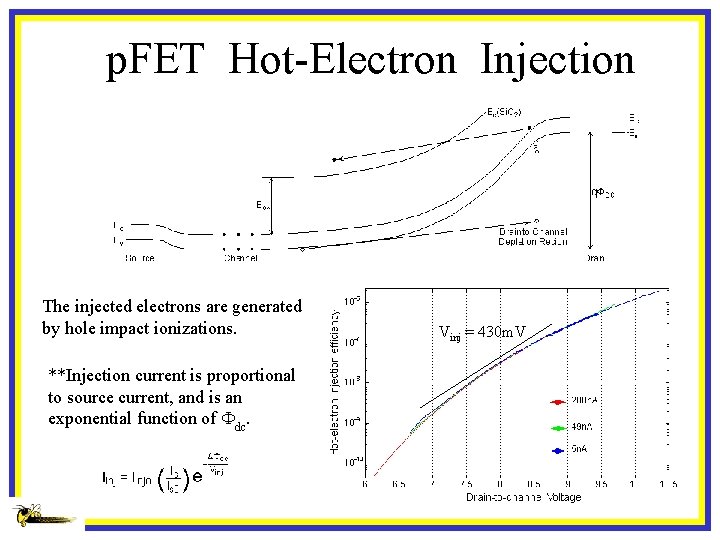

p. FET Hot-Electron Injection The injected electrons are generated by hole impact ionizations. **Injection current is proportional to source current, and is an exponential function of Fdc. Vinj = 430 m. V

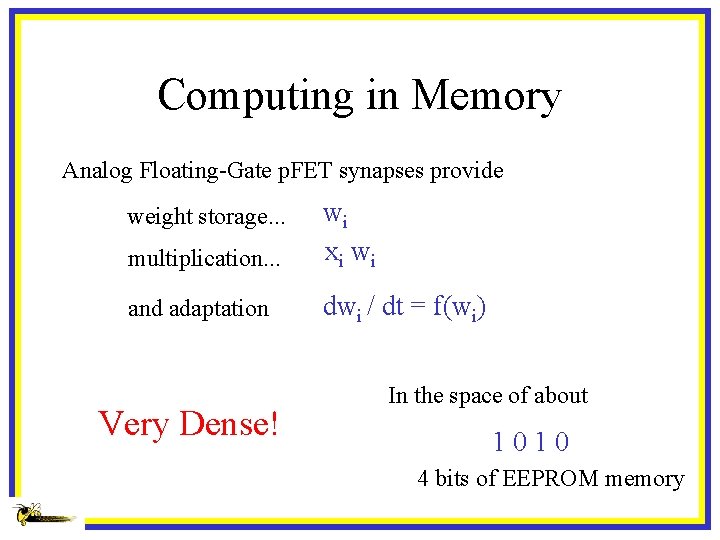

Computing in Memory Analog Floating-Gate p. FET synapses provide multiplication. . . wi xi wi and adaptation dwi / dt = f(wi) weight storage. . . Very Dense! In the space of about 1010 4 bits of EEPROM memory

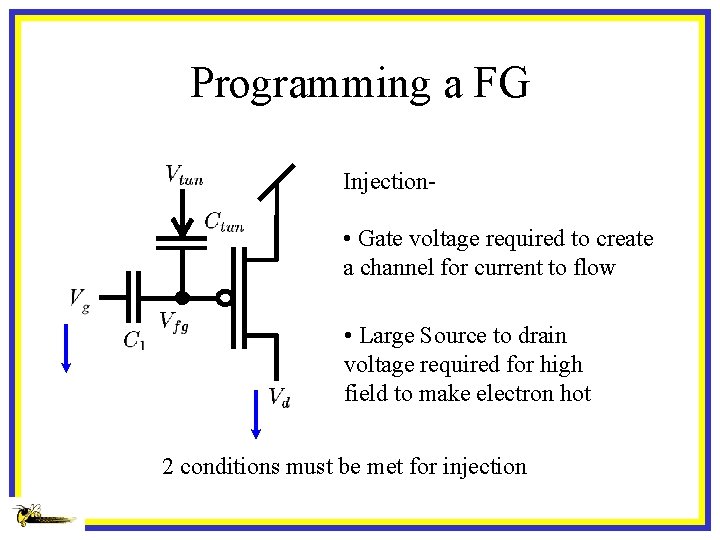

Programming a FG Injection- • Gate voltage required to create a channel for current to flow • Large Source to drain voltage required for high field to make electron hot 2 conditions must be met for injection

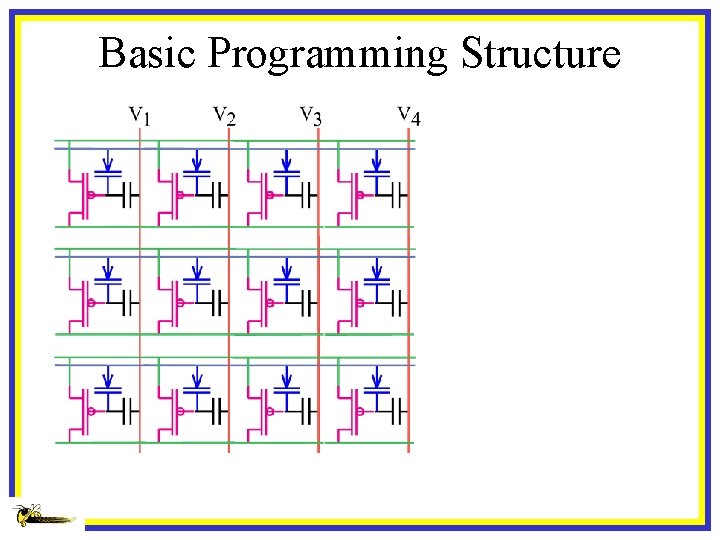

Basic Programming Structure Injection • Requires Voltage across the Source-Drain • Requires Voltage on the Gate Tunneling • Requires a voltage across the tunneling cap.

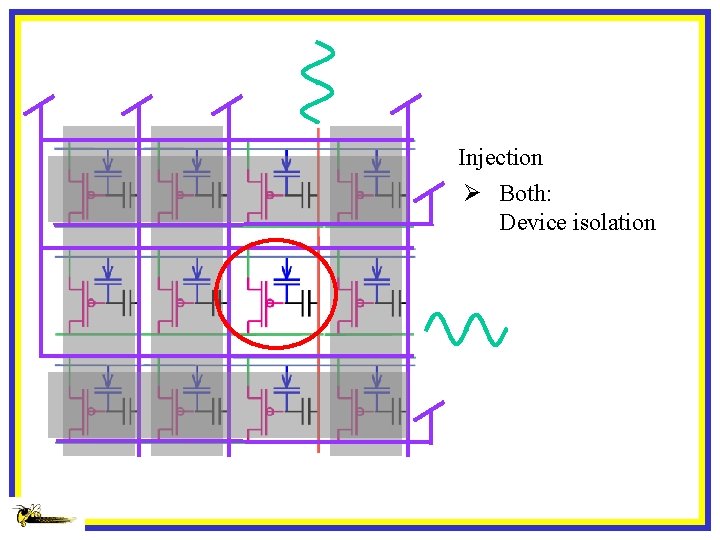

Basic Programming Structure Injection Ø Both: Gate: Columnisolation Device isolation Ø Source-Drain: Row isolation

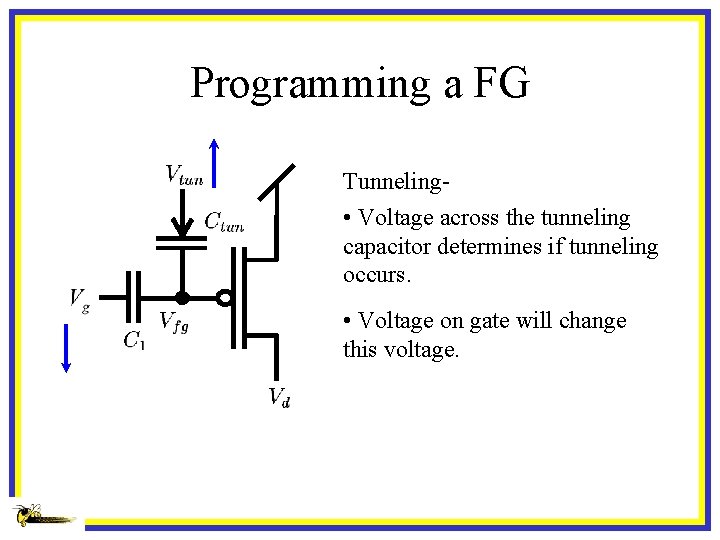

Programming a FG Tunneling • Voltage across the tunneling capacitor determines if tunneling occurs. • Voltage on gate will change this voltage.

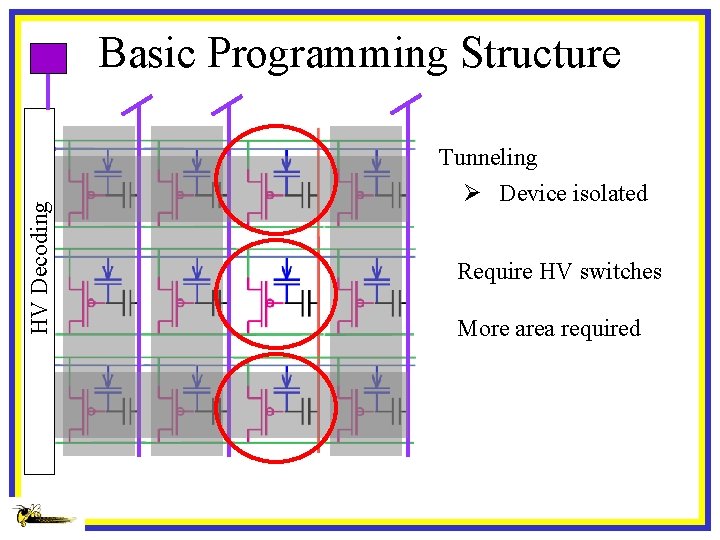

HV Decoding Basic Programming Structure Tunneling Ø Device Columnisolated Require HV switches More area required

Selectivity in Array

Basic Programming Structure

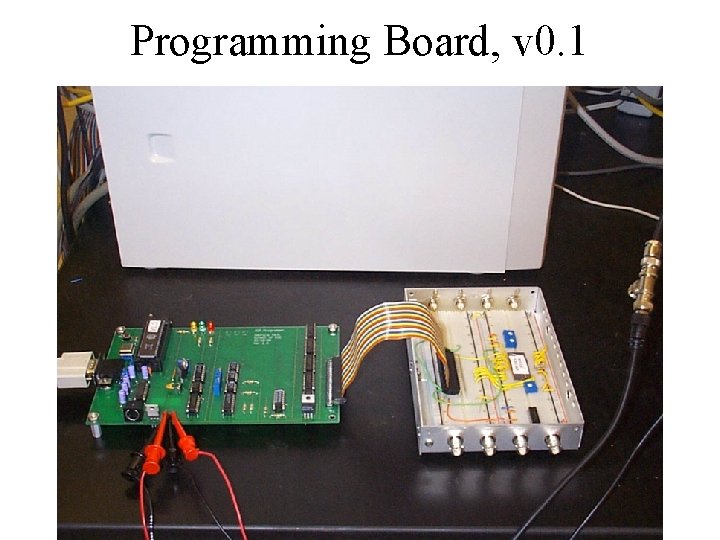

Programming Board, v 0. 1

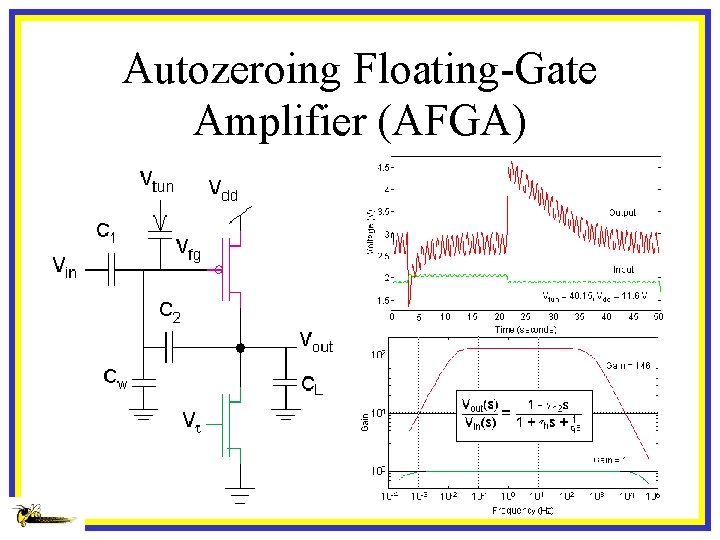

Autozeroing Floating-Gate Amplifier (AFGA)

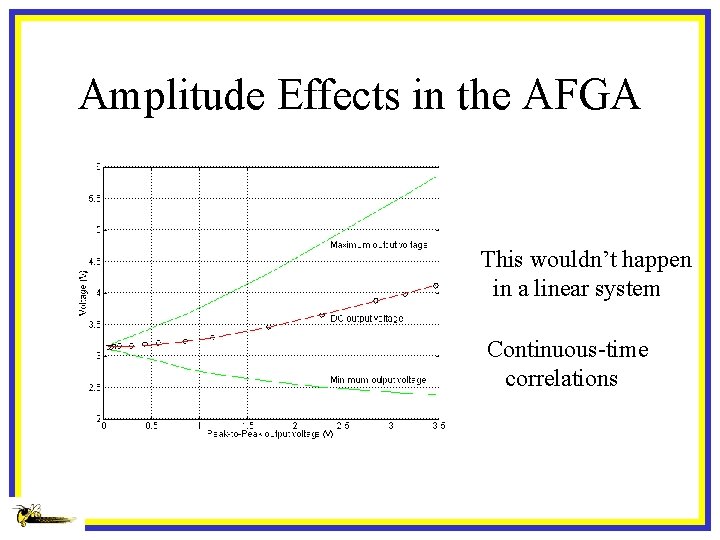

Amplitude Effects in the AFGA This wouldn’t happen in a linear system Continuous-time correlations

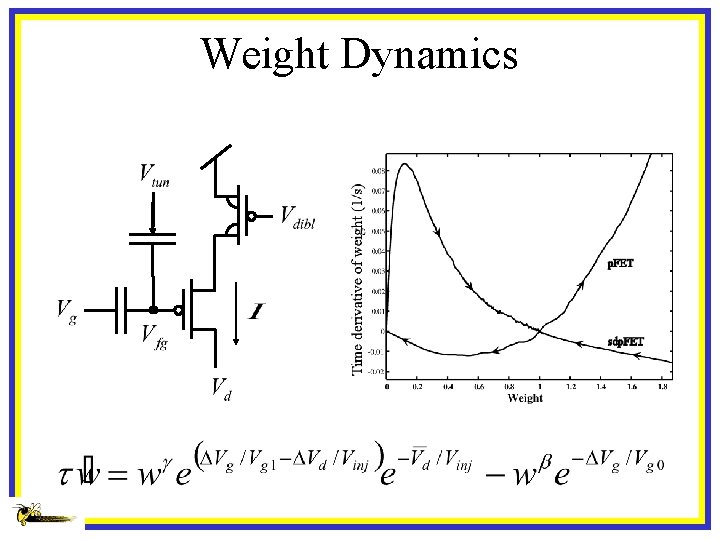

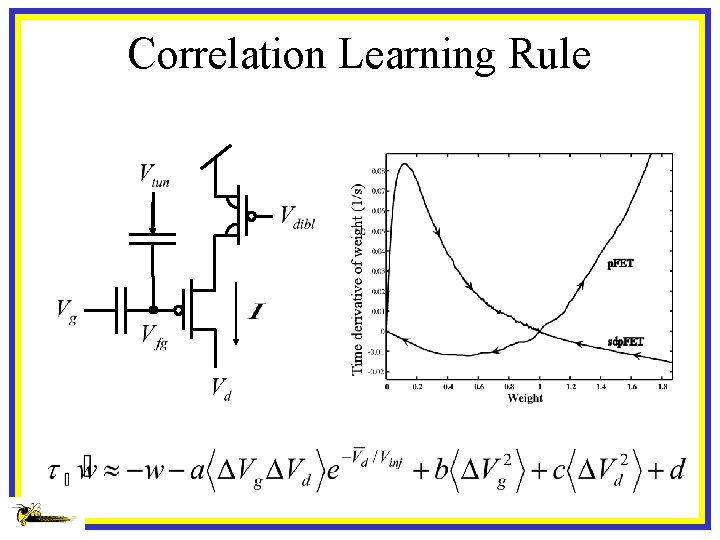

Single Transistor Floating-Gate Synapse: Adaptation p. FET Floating-Gate Synapse Adapts floating-gate charge using: • Tunneling Current • Injection Current From KCL at floating-gate:

Weight Dynamics

Correlation Learning Rule

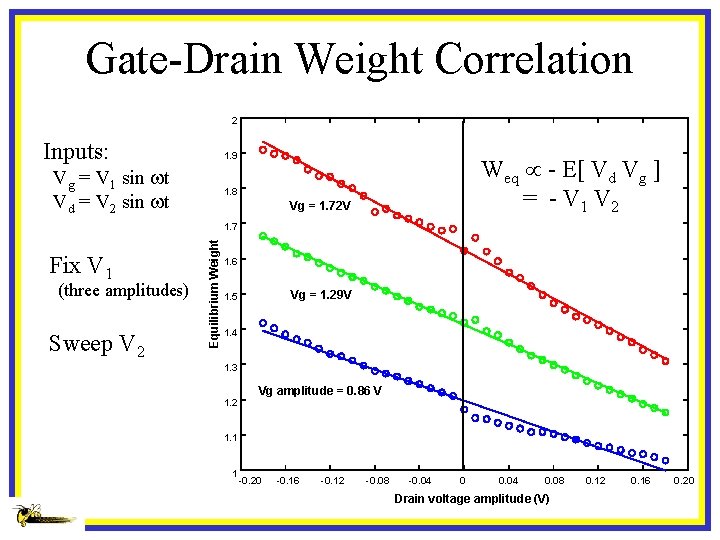

Gate-Drain Weight Correlation 2 Inputs: 1. 9 Vg = V 1 sin wt Vd = V 2 sin wt Weq - E[ Vd Vg ] = - V 1 V 2 1. 8 Vg = 1. 72 V Fix V 1 (three amplitudes) Sweep V 2 Equilibrium Weight 1. 7 1. 6 Vg = 1. 29 V 1. 5 1. 4 1. 3 1. 2 Vg amplitude = 0. 86 V 1. 1 1 -0. 20 -0. 16 -0. 12 -0. 08 -0. 04 0. 08 Drain voltage amplitude (V) 0. 12 0. 16 0. 20

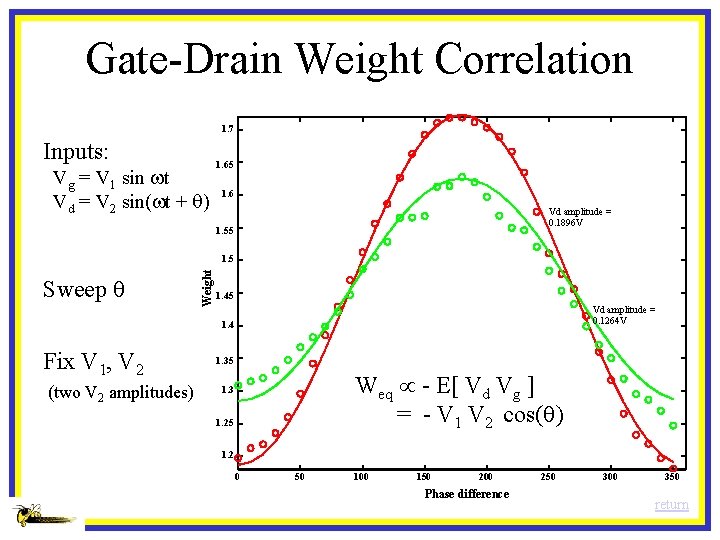

Gate-Drain Weight Correlation 1. 7 Inputs: Vg = V 1 sin wt Vd = V 2 sin(wt + q) 1. 65 1. 6 Vd amplitude = 0. 1896 V 1. 55 Sweep q Weight 1. 5 1. 45 Vd amplitude = 0. 1264 V 1. 4 Fix V 1, V 2 (two V 2 amplitudes) 1. 35 Weq - E[ Vd Vg ] = - V 1 V 2 cos(q) 1. 3 1. 25 1. 2 0 50 100 150 200 Phase difference 250 300 350 return

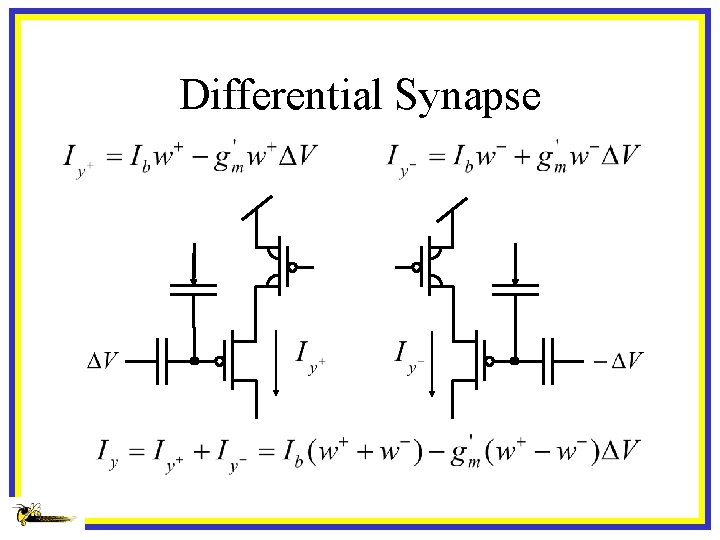

Differential Synapse

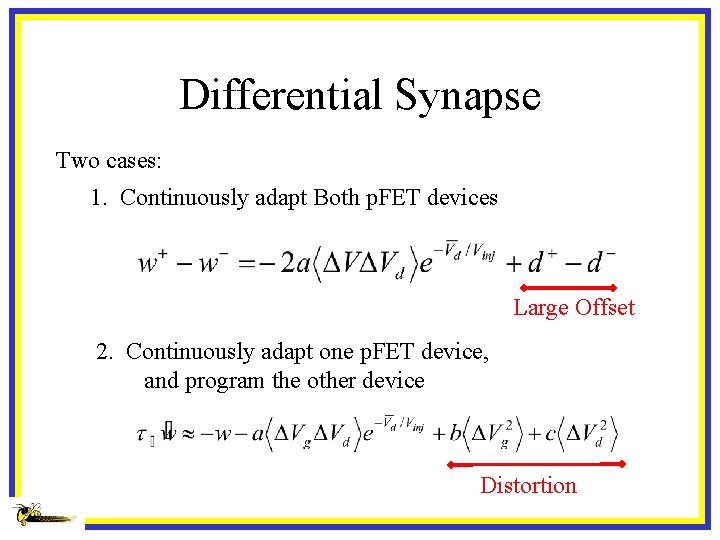

Differential Synapse Two cases: 1. Continuously adapt Both p. FET devices Large Offset 2. Continuously adapt one p. FET device, and program the other device Distortion

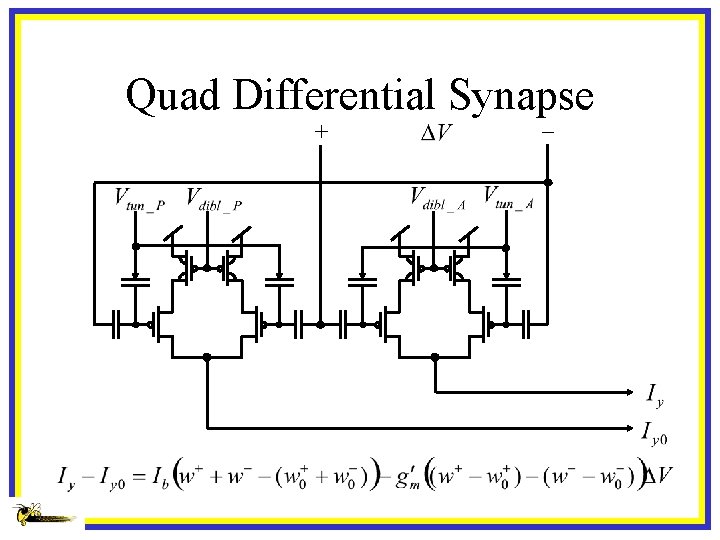

Quad Differential Synapse _ +

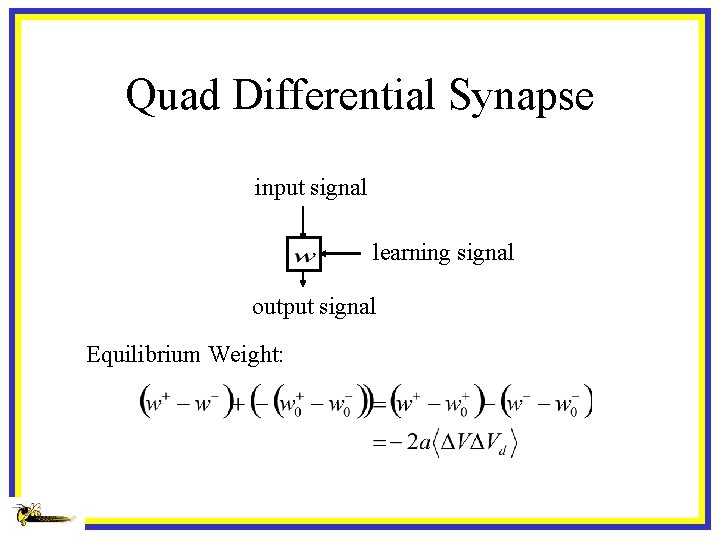

Quad Differential Synapse input signal learning signal output signal Equilibrium Weight:

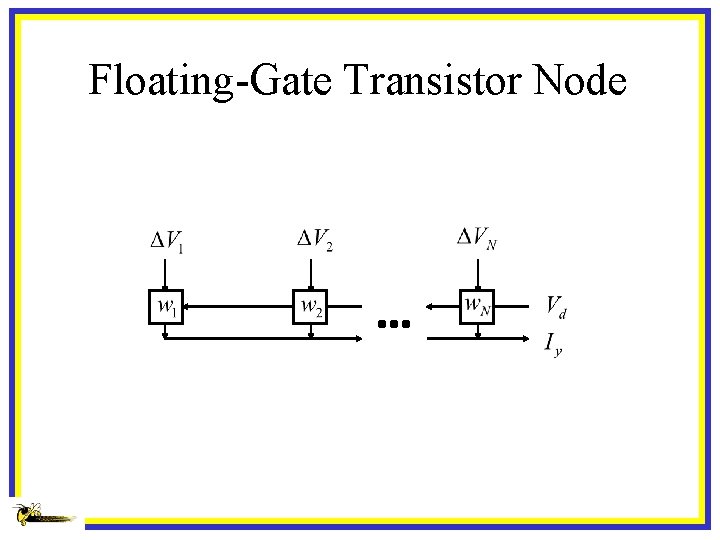

Floating-Gate Transistor Node

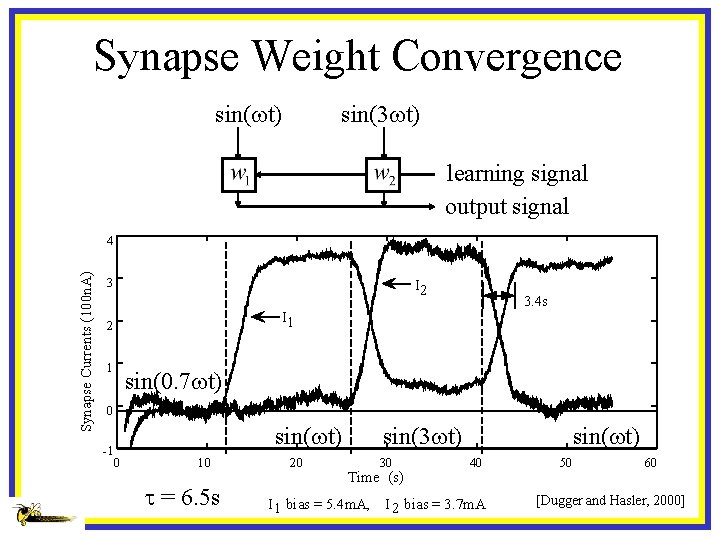

Synapse Weight Convergence sin(wt) sin(3 wt) learning signal output signal Synapse Currents (100 n. A) 4 3 I 2 I 1 2 1 3. 4 s sin(0. 7 wt) 0 -1 0 sin(wt) 10 t = 6. 5 s 20 sin(3 wt) 30 Time (s) sin(wt) 40 I 1 bias = 5. 4 m. A, I 2 bias = 3. 7 m. A 50 60 [Dugger and Hasler, 2000]

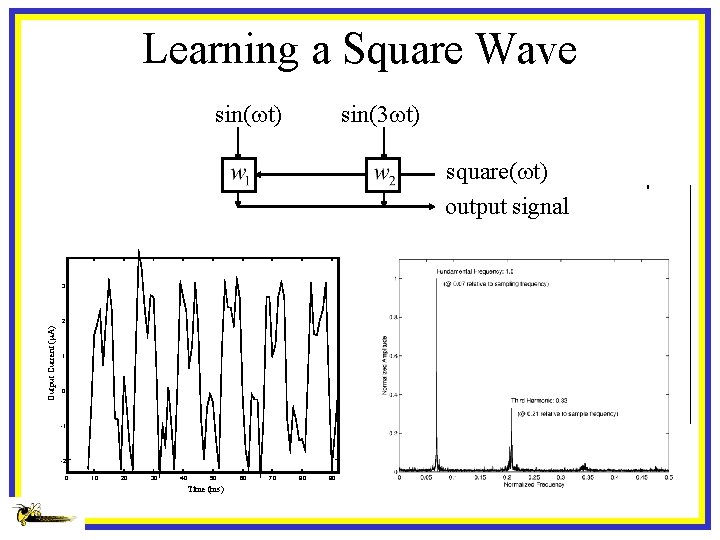

Learning a Square Wave sin(wt) sin(3 wt) square(wt) output signal 3 Output Current (m. A) 2 1 0 -1 -2 0 10 20 30 40 50 Time (ms) 60 70 80 90

Learning Rule Circuits Vd = f(Iy, Vtarget) Vtarget

Adaptive Diff-Pair

- Slides: 38