Programare i securitate la nivelul arhitecturii x 86

![Semnale pe magistrala PCI n n n n AD[63 -0] adrese si date multiplexate Semnale pe magistrala PCI n n n n AD[63 -0] adrese si date multiplexate](https://slidetodoc.com/presentation_image_h2/eb3d5996016780493e6a73b423698240/image-8.jpg)

- Slides: 34

Programare și securitate la nivelul arhitecturii x 86 Prof. dr. ing. Gheorghe Sebestyen Cursul 5. Magistrala PCI, Placi PCI, PCIe Identificarea resurselor din sistem

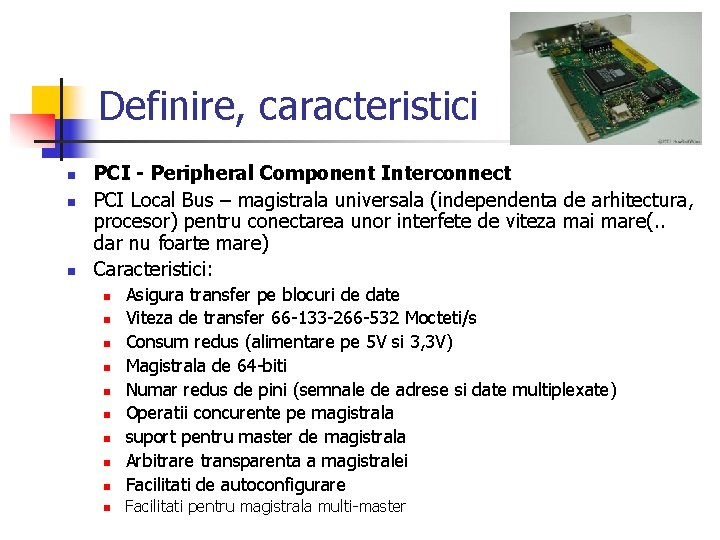

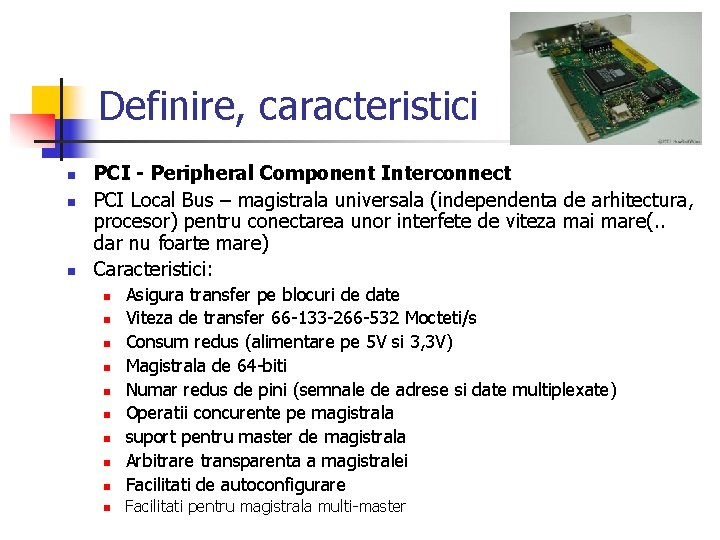

Definire, caracteristici n n n PCI - Peripheral Component Interconnect PCI Local Bus – magistrala universala (independenta de arhitectura, procesor) pentru conectarea unor interfete de viteza mai mare(. . dar nu foarte mare) Caracteristici: n Asigura transfer pe blocuri de date Viteza de transfer 66 -133 -266 -532 Mocteti/s Consum redus (alimentare pe 5 V si 3, 3 V) Magistrala de 64 -biti Numar redus de pini (semnale de adrese si date multiplexate) Operatii concurente pe magistrala suport pentru master de magistrala Arbitrare transparenta a magistralei Facilitati de autoconfigurare n Facilitati pentru magistrala multi-master n n n n

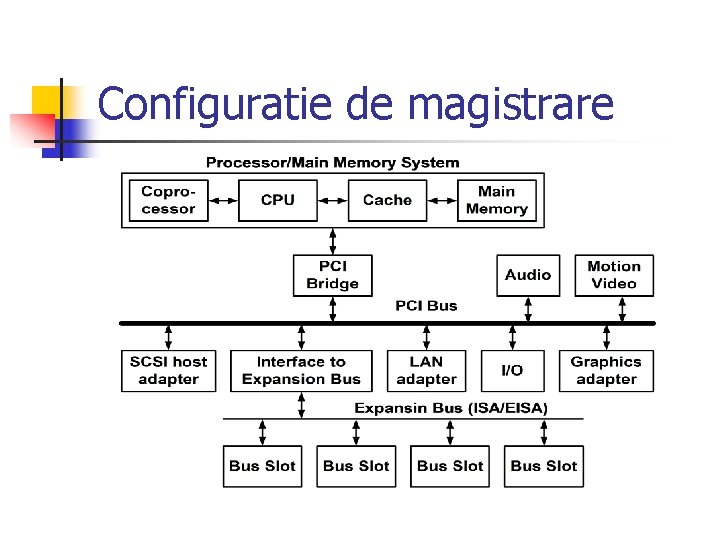

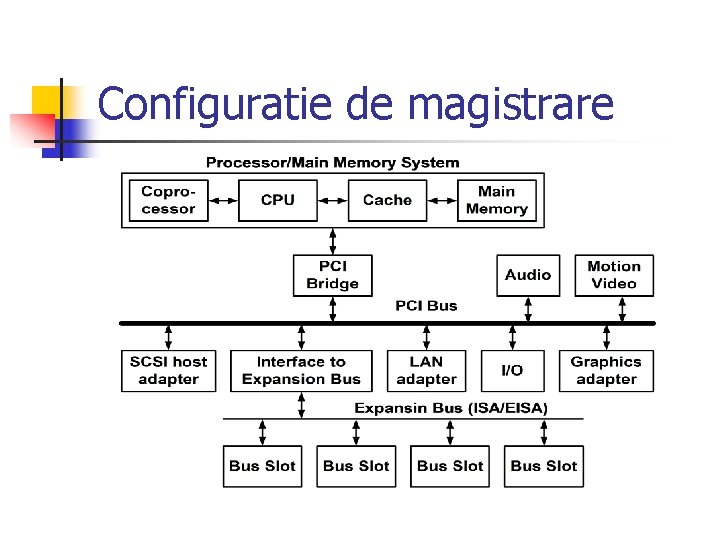

Configuratie de magistrare

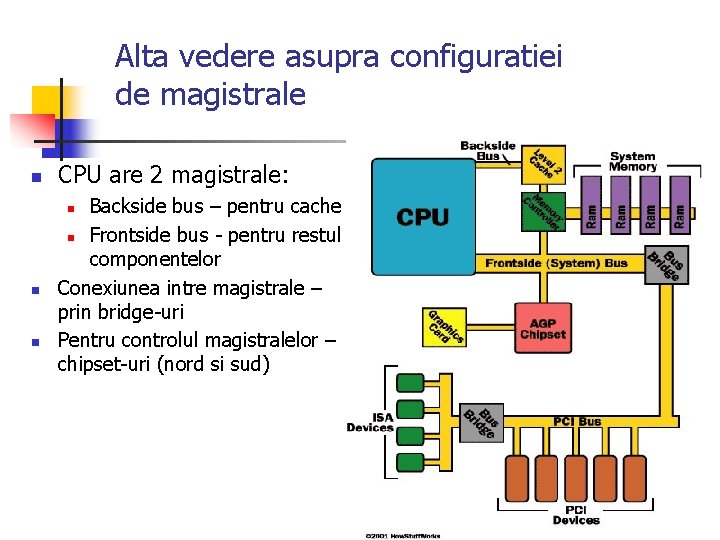

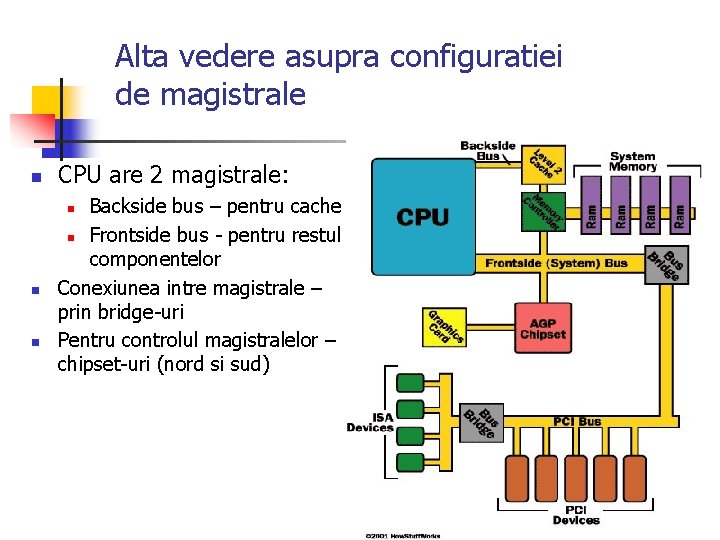

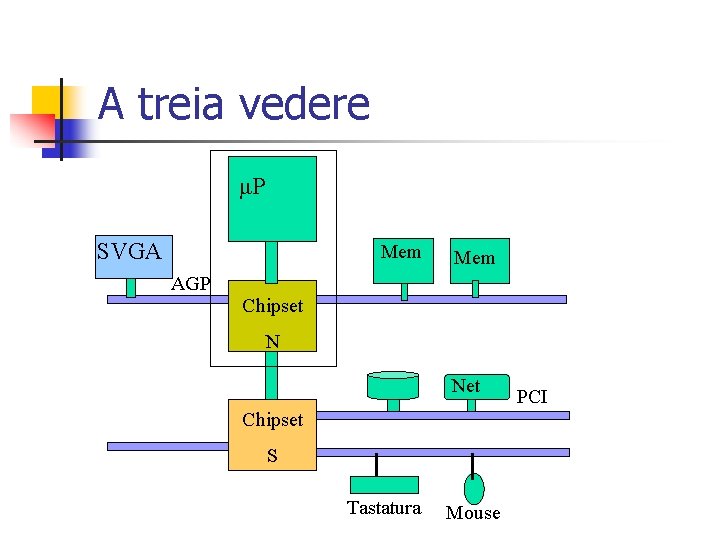

Alta vedere asupra configuratiei de magistrale n CPU are 2 magistrale: n Backside bus – pentru cache n Frontside bus - pentru restul componentelor Conexiunea intre magistrale – prin bridge-uri Pentru controlul magistralelor – chipset-uri (nord si sud) n n

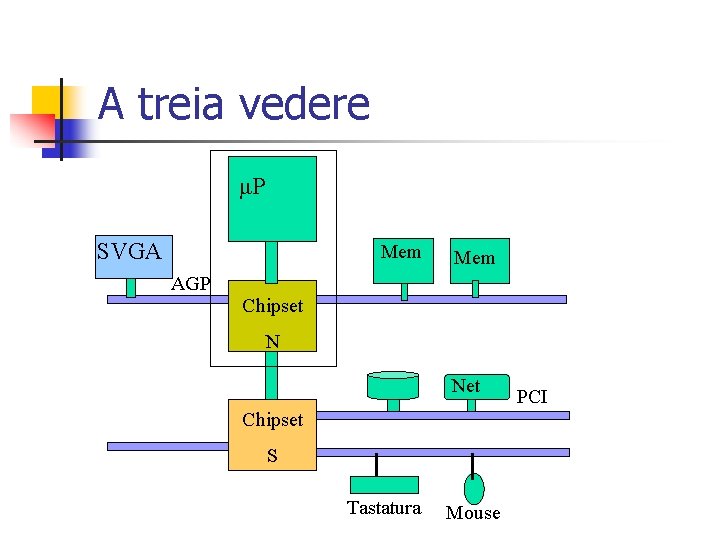

A treia vedere μP SVGA Mem AGP Chipset N Net Chipset S Tastatura Mouse PCI

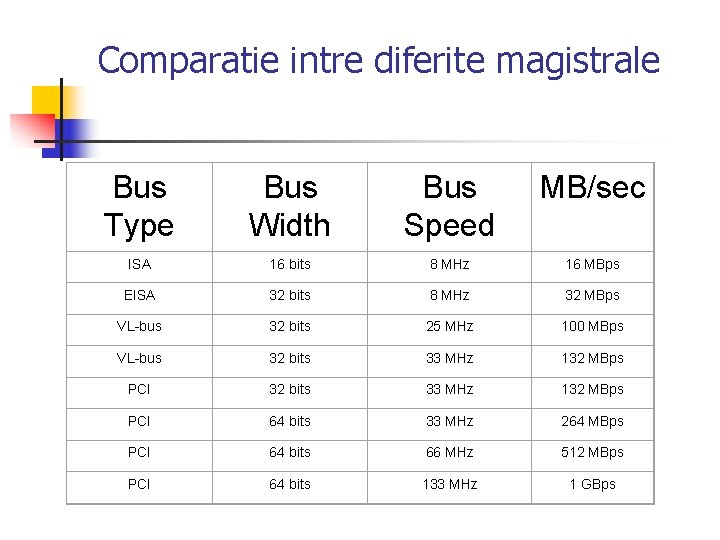

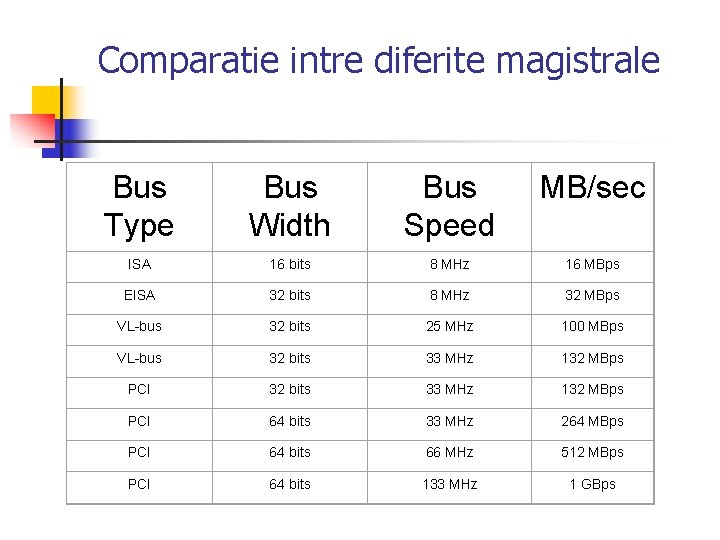

Comparatie intre diferite magistrale Bus Type Bus Width Bus Speed MB/sec ISA 16 bits 8 MHz 16 MBps EISA 32 bits 8 MHz 32 MBps VL-bus 32 bits 25 MHz 100 MBps VL-bus 32 bits 33 MHz 132 MBps PCI 64 bits 33 MHz 264 MBps PCI 64 bits 66 MHz 512 MBps PCI 64 bits 133 MHz 1 GBps

Terminologie PCI n Initiator sau Mater n n n Target (tinta) sau Slave n n Detine magistrala si initiaza transferuri de date Orice initiator trebuie sa fie si o tinta (Target) Este tinta unui transfer de citire sau scriere Agent n orice initiator/tinta sau (doar) tinta pe

![Semnale pe magistrala PCI n n n n AD63 0 adrese si date multiplexate Semnale pe magistrala PCI n n n n AD[63 -0] adrese si date multiplexate](https://slidetodoc.com/presentation_image_h2/eb3d5996016780493e6a73b423698240/image-8.jpg)

Semnale pe magistrala PCI n n n n AD[63 -0] adrese si date multiplexate C/BE[7 -0] – semnale pentru comenzi sau validare date Semnale pentru controlul si confirmarea selectiei sau a transferului (Interface control) Semnale de arbitrare a magistralei REQ, GNT Semnale de sistem CLK, RST Intreruperi INTA, B, C, D De testare? JTAG

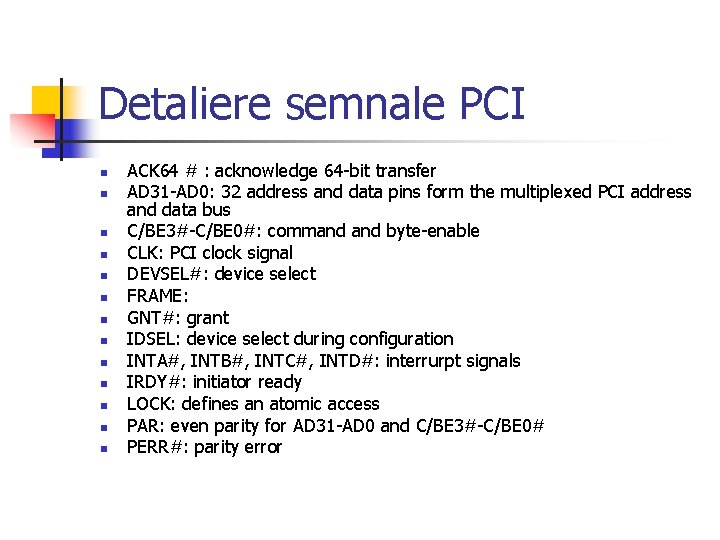

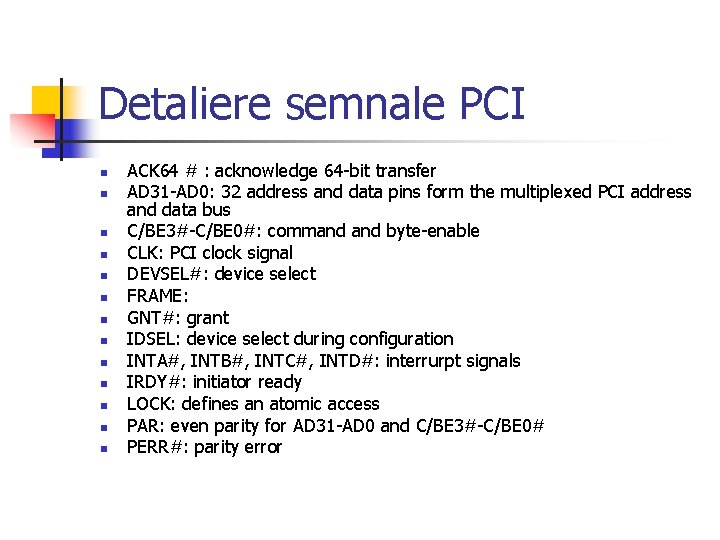

Detaliere semnale PCI n n n n ACK 64 # : acknowledge 64 -bit transfer AD 31 -AD 0: 32 address and data pins form the multiplexed PCI address and data bus C/BE 3#-C/BE 0#: command byte-enable CLK: PCI clock signal DEVSEL#: device select FRAME: GNT#: grant IDSEL: device select during configuration INTA#, INTB#, INTC#, INTD#: interrurpt signals IRDY#: initiator ready LOCK: defines an atomic access PAR: even parity for AD 31 -AD 0 and C/BE 3#-C/BE 0# PERR#: parity error

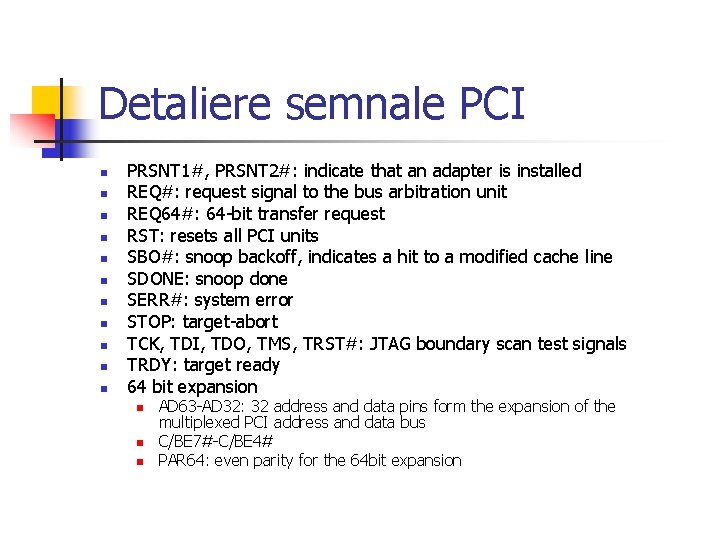

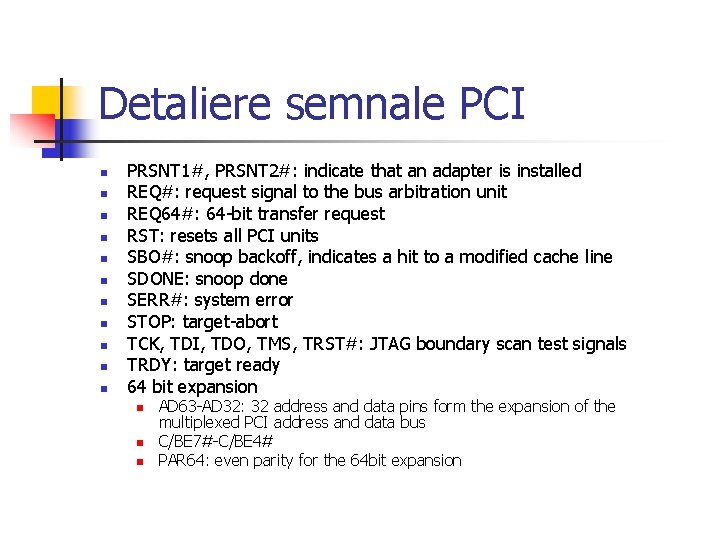

Detaliere semnale PCI n n n PRSNT 1#, PRSNT 2#: indicate that an adapter is installed REQ#: request signal to the bus arbitration unit REQ 64#: 64 -bit transfer request RST: resets all PCI units SBO#: snoop backoff, indicates a hit to a modified cache line SDONE: snoop done SERR#: system error STOP: target-abort TCK, TDI, TDO, TMS, TRST#: JTAG boundary scan test signals TRDY: target ready 64 bit expansion n AD 63 -AD 32: 32 address and data pins form the expansion of the multiplexed PCI address and data bus C/BE 7#-C/BE 4# PAR 64: even parity for the 64 bit expansion

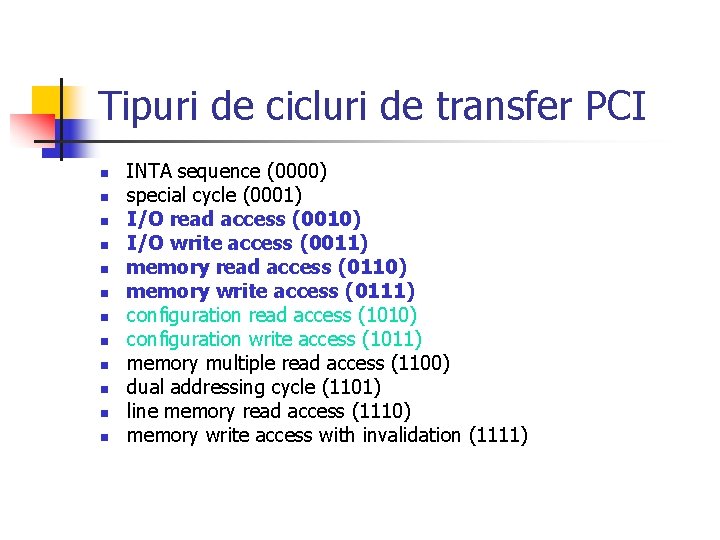

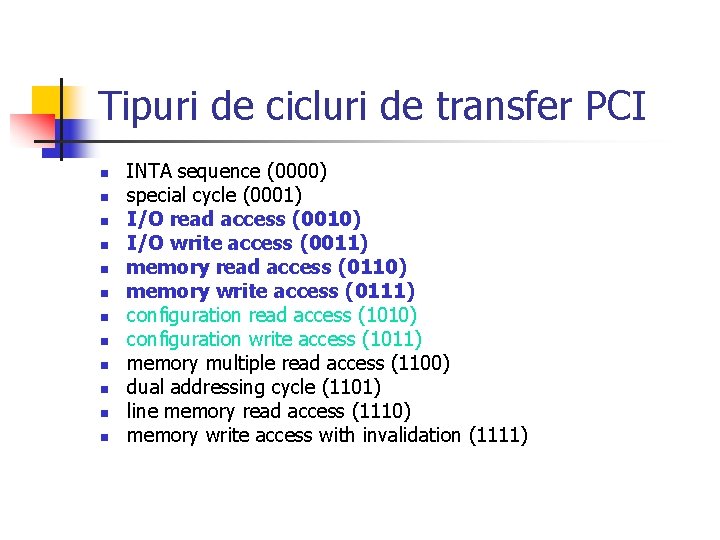

Tipuri de cicluri de transfer PCI n n n INTA sequence (0000) special cycle (0001) I/O read access (0010) I/O write access (0011) memory read access (0110) memory write access (0111) configuration read access (1010) configuration write access (1011) memory multiple read access (1100) dual addressing cycle (1101) line memory read access (1110) memory write access with invalidation (1111)

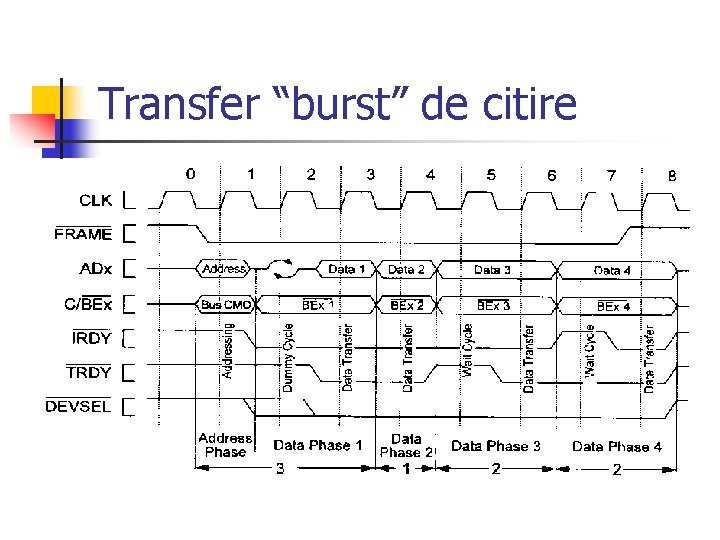

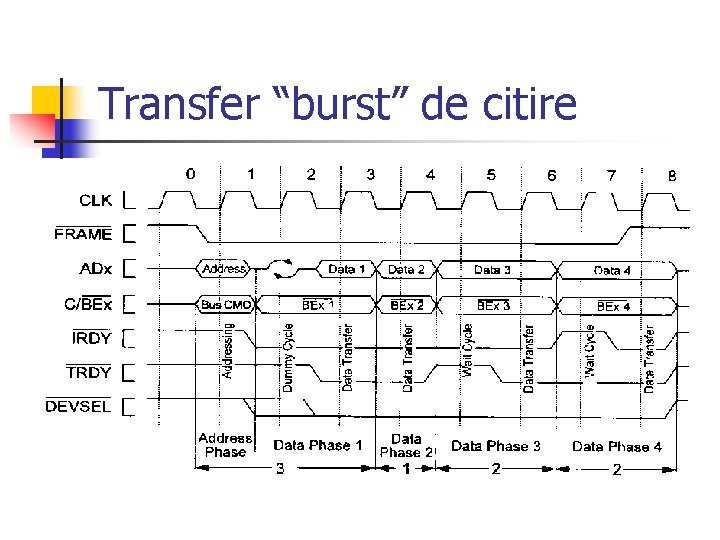

Transfer “burst” de citire

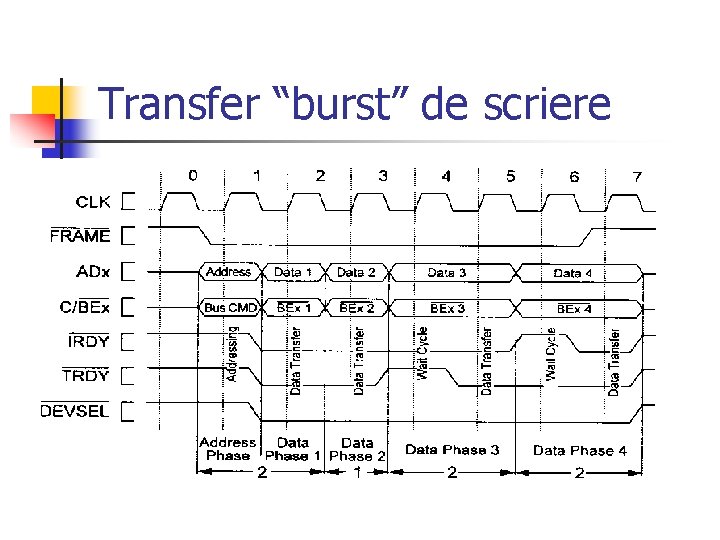

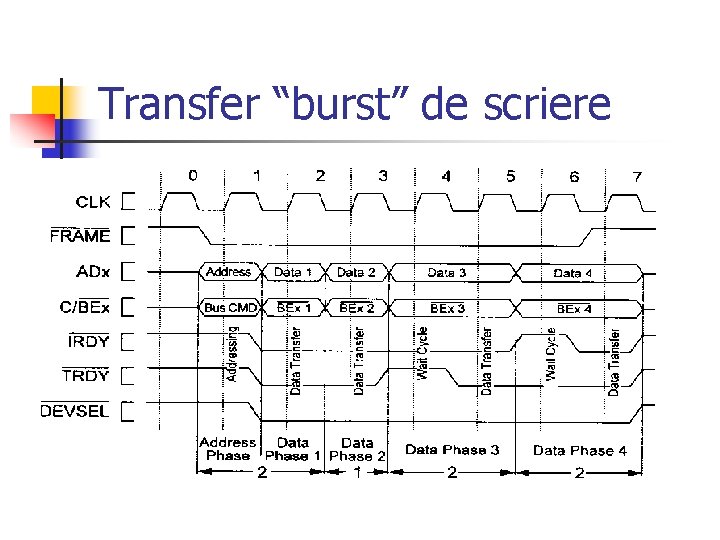

Transfer “burst” de scriere

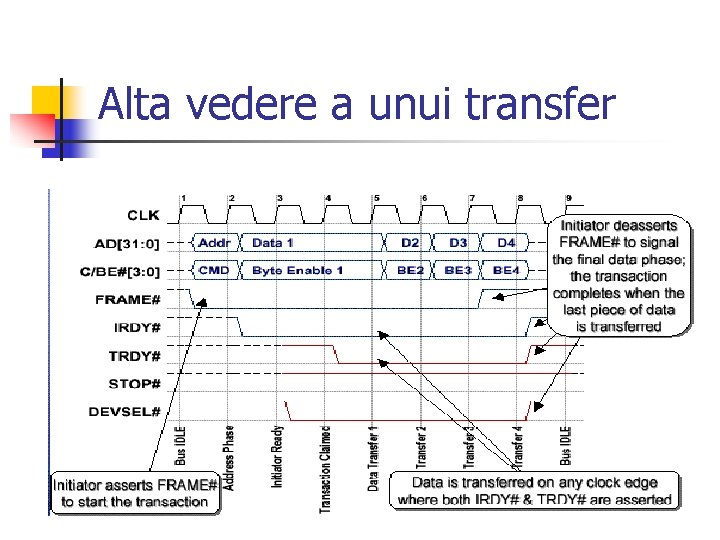

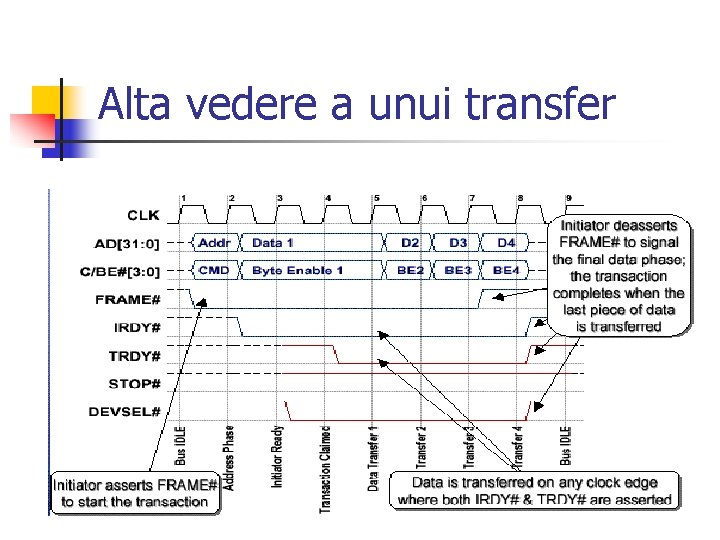

Alta vedere a unui transfer

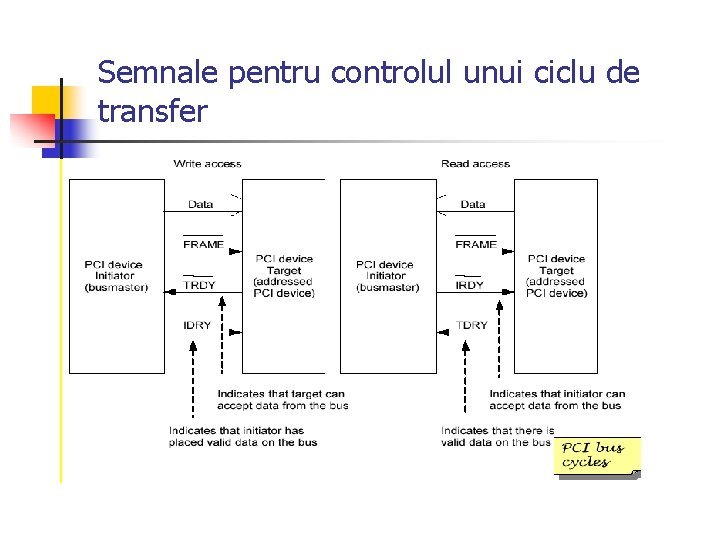

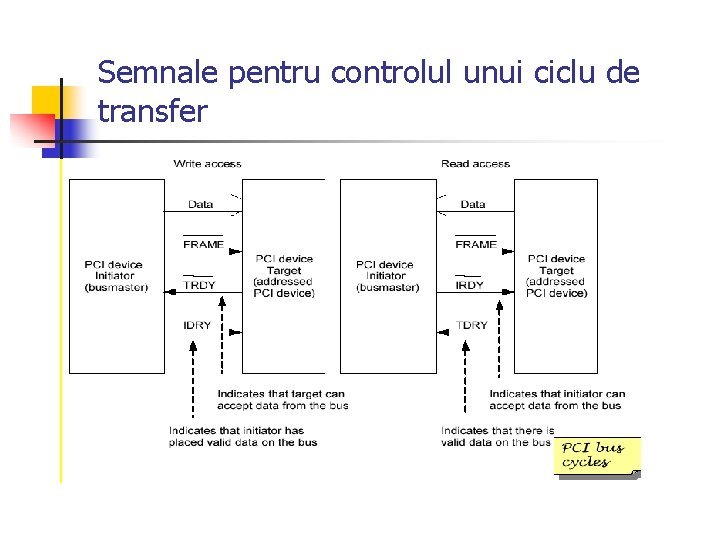

Semnale pentru controlul unui ciclu de transfer

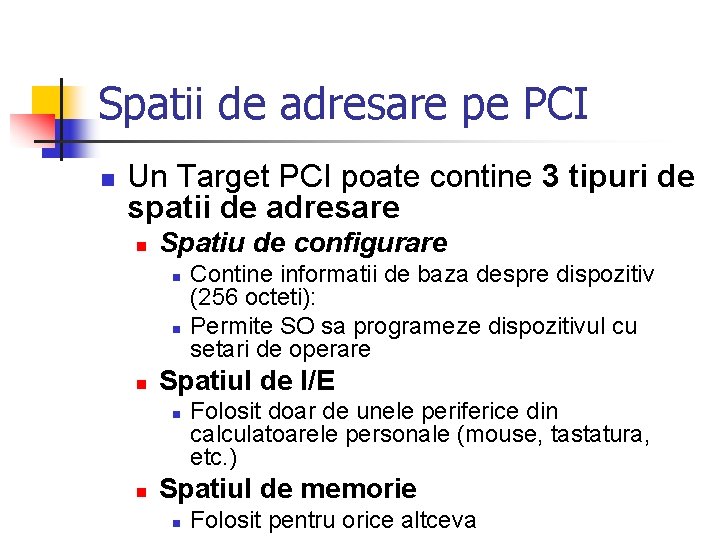

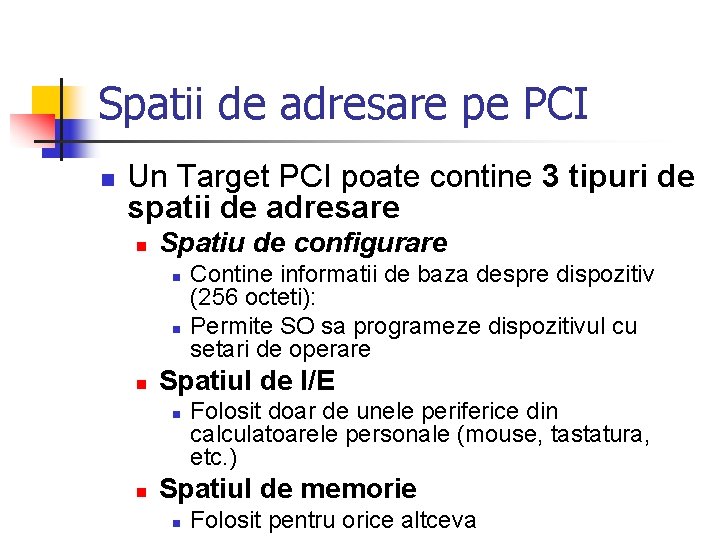

Spatii de adresare pe PCI n Un Target PCI poate contine 3 tipuri de spatii de adresare n Spatiu de configurare n n n Spatiul de I/E n n Contine informatii de baza despre dispozitiv (256 octeti): Permite SO sa programeze dispozitivul cu setari de operare Folosit doar de unele periferice din calculatoarele personale (mouse, tastatura, etc. ) Spatiul de memorie n Folosit pentru orice altceva

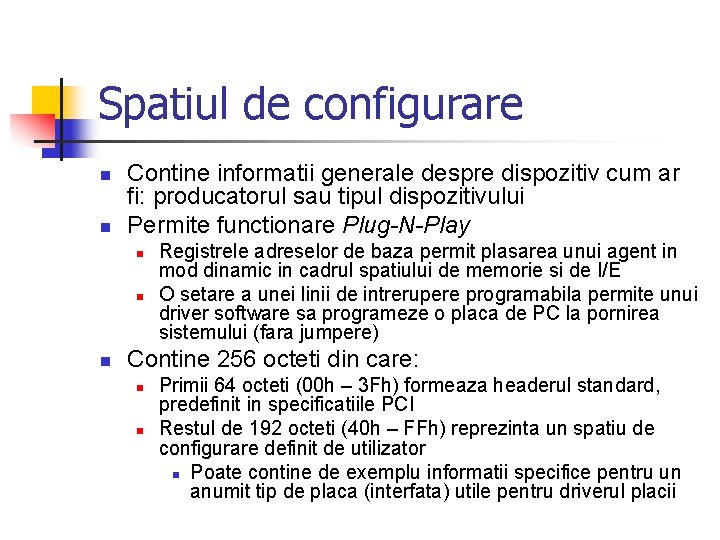

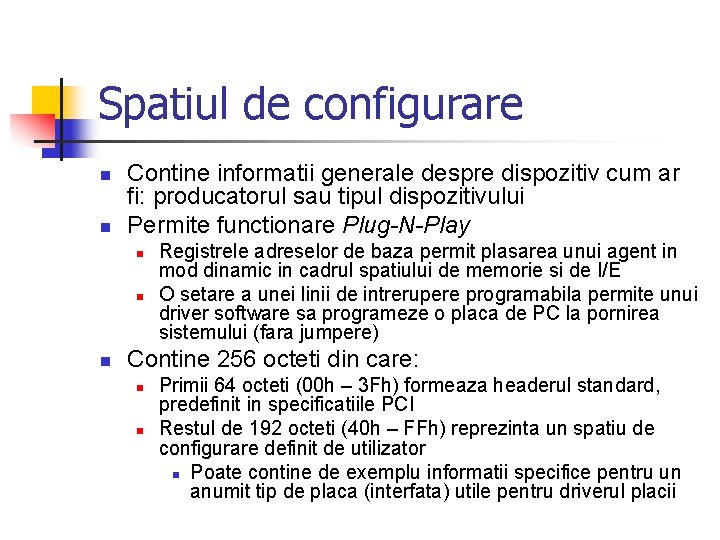

Spatiul de configurare n n Contine informatii generale despre dispozitiv cum ar fi: producatorul sau tipul dispozitivului Permite functionare Plug-N-Play n n n Registrele adreselor de baza permit plasarea unui agent in mod dinamic in cadrul spatiului de memorie si de I/E O setare a unei linii de intrerupere programabila permite unui driver software sa programeze o placa de PC la pornirea sistemului (fara jumpere) Contine 256 octeti din care: n n Primii 64 octeti (00 h – 3 Fh) formeaza headerul standard, predefinit in specificatiile PCI Restul de 192 octeti (40 h – FFh) reprezinta un spatiu de configurare definit de utilizator n Poate contine de exemplu informatii specifice pentru un anumit tip de placa (interfata) utile pentru driverul placii

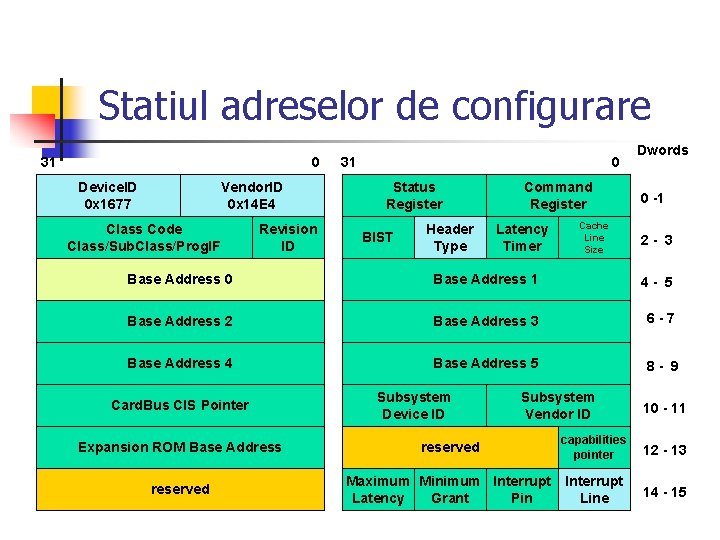

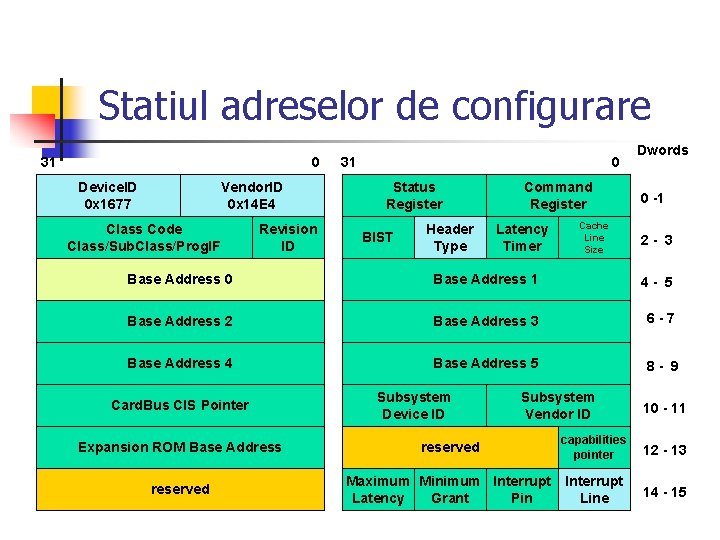

Statiul adreselor de configurare 31 0 Device. ID 0 x 1677 Vendor. ID 0 x 14 E 4 Class Code Class/Sub. Class/Prog. IF Revision ID 31 0 Status Register BIST Header Type Command Register Latency Timer Cache Line Size Dwords 0 -1 2 - 3 Base Address 0 Base Address 1 4 - 5 Base Address 2 Base Address 3 6 -7 Base Address 4 Base Address 5 8 - 9 Card. Bus CIS Pointer Subsystem Device ID Subsystem Vendor ID 10 - 11 Expansion ROM Base Address reserved capabilities pointer 12 - 13 reserved Maximum Minimum Interrupt Latency Grant Pin Interrupt Line 14 - 15

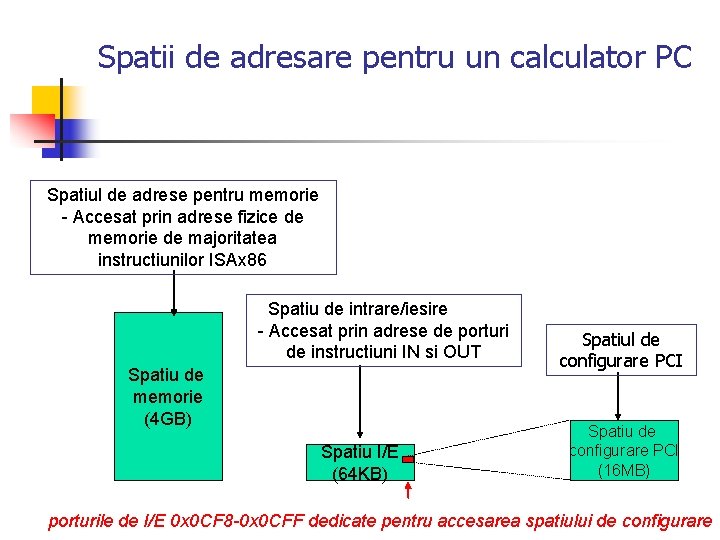

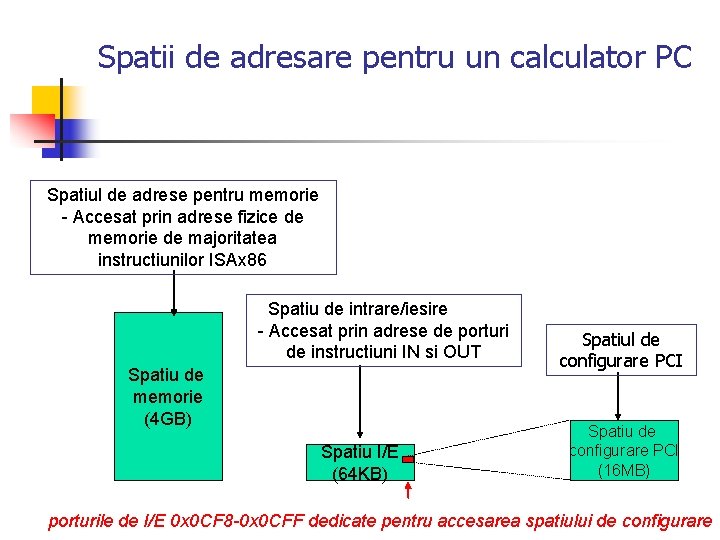

Spatii de adresare pentru un calculator PC Spatiul de adrese pentru memorie - Accesat prin adrese fizice de memorie de majoritatea instructiunilor ISAx 86 Spatiu de intrare/iesire - Accesat prin adrese de porturi de instructiuni IN si OUT Spatiu de memorie (4 GB) Spatiu I/E (64 KB) Spatiul de configurare PCI Spatiu de configurare PCI (16 MB) porturile de I/E 0 x 0 CF 8 -0 x 0 CFF dedicate pentru accesarea spatiului de configurare

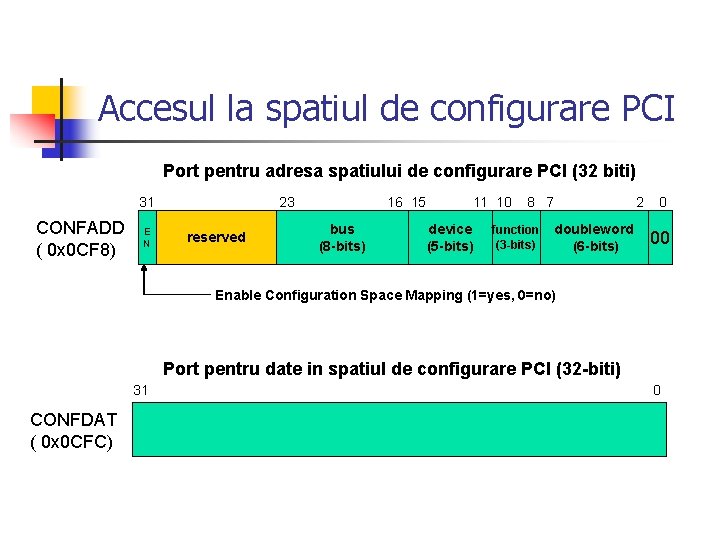

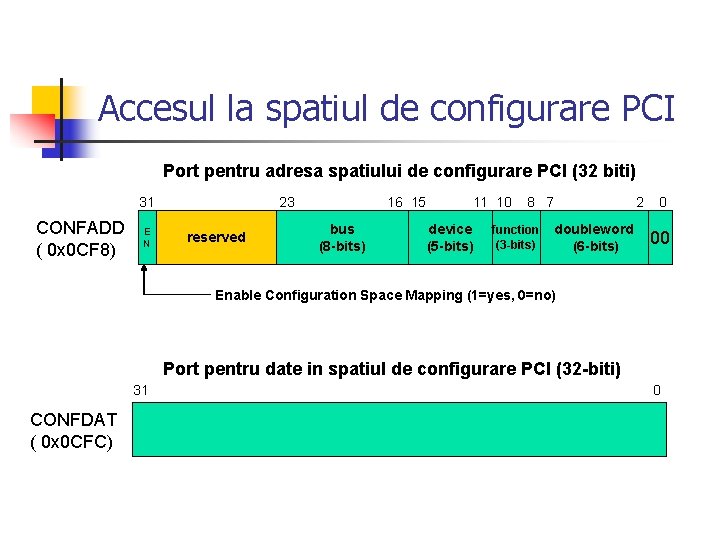

Accesul la spatiul de configurare PCI Port pentru adresa spatiului de configurare PCI (32 biti) 31 CONFADD ( 0 x 0 CF 8) E N 23 reserved 16 15 bus (8 -bits) 11 10 device (5 -bits) 8 7 function (3 -bits) doubleword (6 -bits) 2 0 00 Enable Configuration Space Mapping (1=yes, 0=no) Port pentru date in spatiul de configurare PCI (32 -biti) 31 CONFDAT ( 0 x 0 CFC) 0

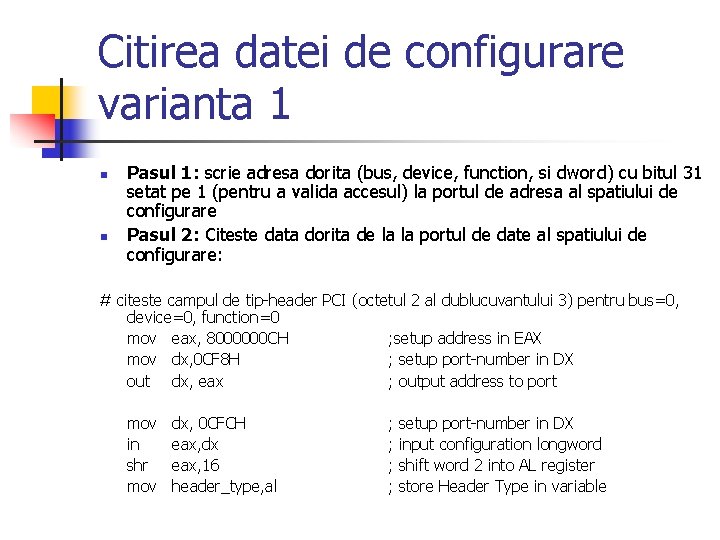

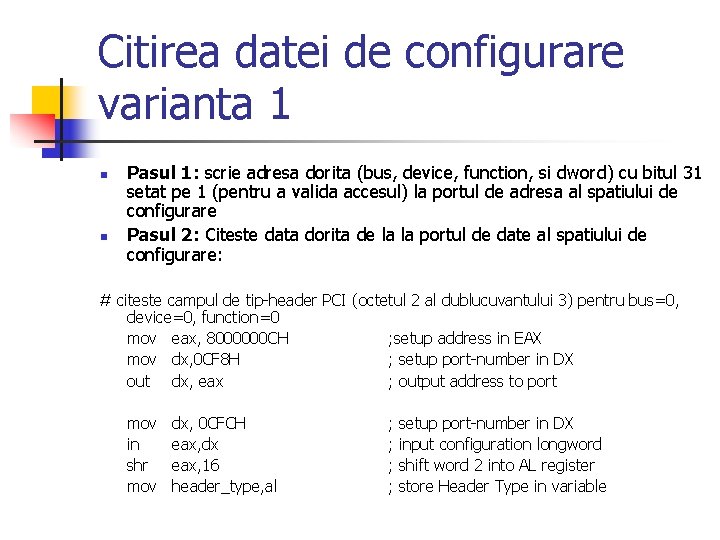

Citirea datei de configurare varianta 1 n n Pasul 1: scrie adresa dorita (bus, device, function, si dword) cu bitul 31 setat pe 1 (pentru a valida accesul) la portul de adresa al spatiului de configurare Pasul 2: Citeste data dorita de la la portul de date al spatiului de configurare: # citeste campul de tip-header PCI (octetul 2 al dublucuvantului 3) pentru bus=0, device=0, function=0 mov eax, 8000000 CH ; setup address in EAX mov dx, 0 CF 8 H ; setup port-number in DX out dx, eax ; output address to port mov in shr mov dx, 0 CFCH eax, dx eax, 16 header_type, al ; ; setup port-number in DX input configuration longword shift word 2 into AL register store Header Type in variable

Citirea datei de configurare varianta 2 (pentru sisteme PC) n 4 k de adrese de I/E intre c 000 h si cfffh

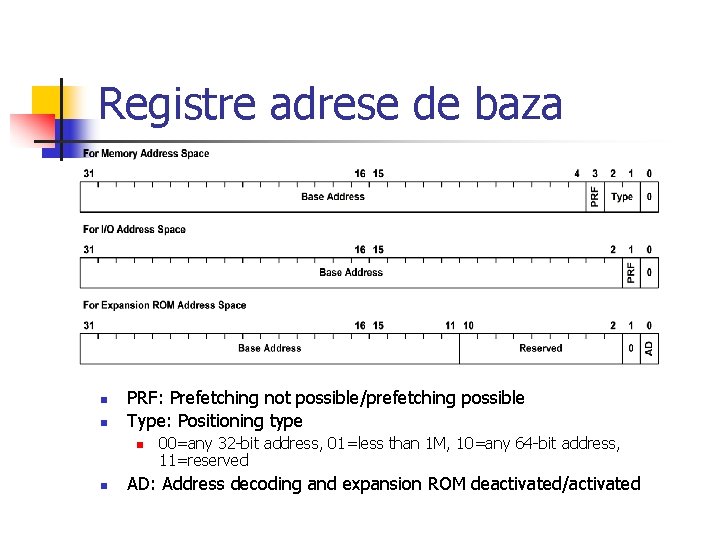

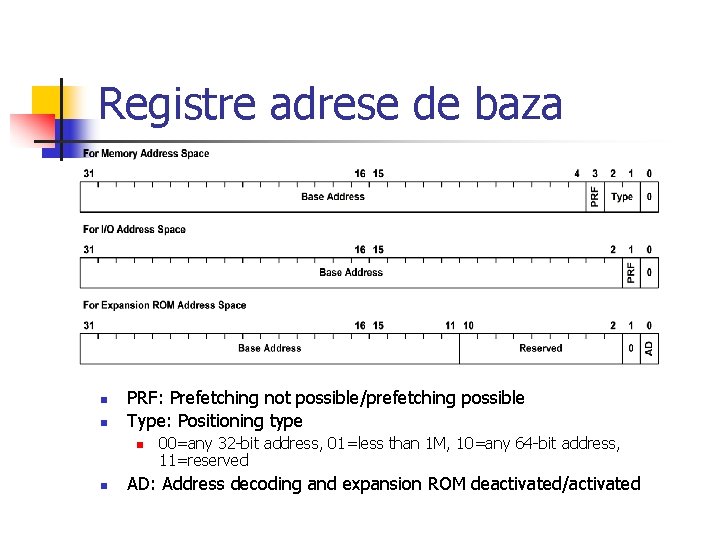

Registre adrese de baza n n PRF: Prefetching not possible/prefetching possible Type: Positioning type n n 00=any 32 -bit address, 01=less than 1 M, 10=any 64 -bit address, 11=reserved AD: Address decoding and expansion ROM deactivated/activated

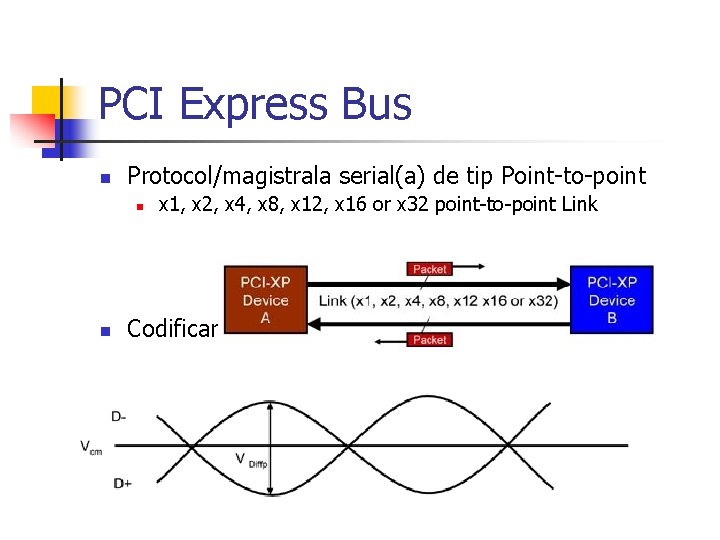

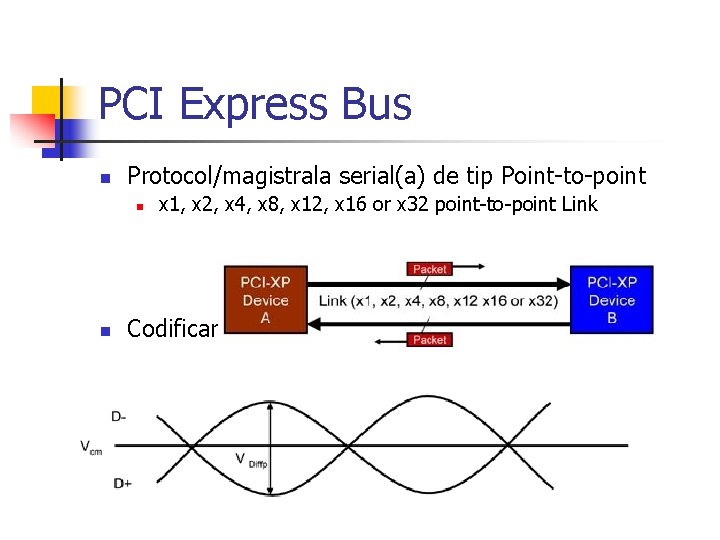

PCI Express Bus n Protocol/magistrala serial(a) de tip Point-to-point n n x 1, x 2, x 4, x 8, x 12, x 16 or x 32 point-to-point Link Codificare diferentiala

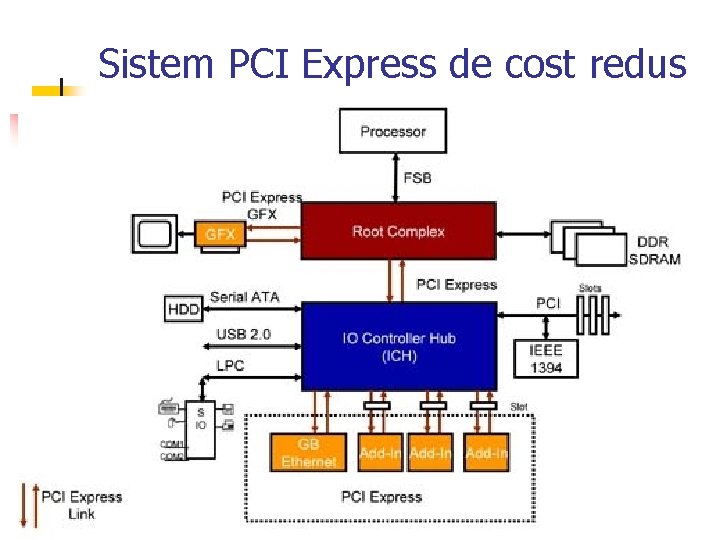

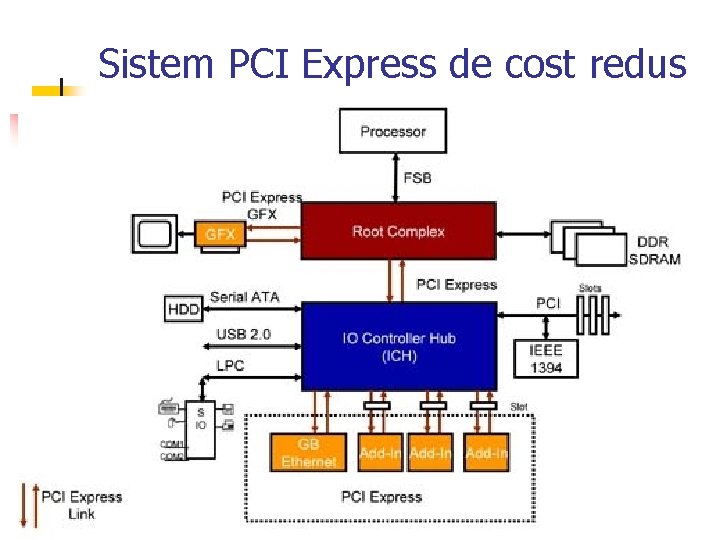

Sistem PCI Express de cost redus

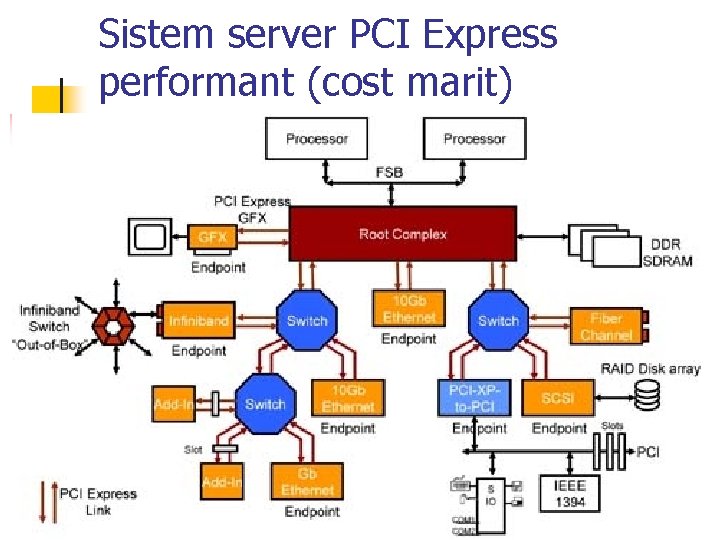

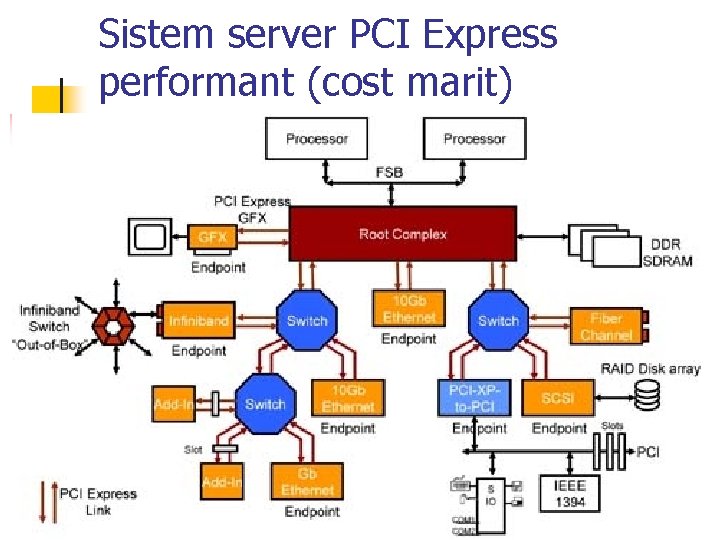

Sistem server PCI Express performant (cost marit)

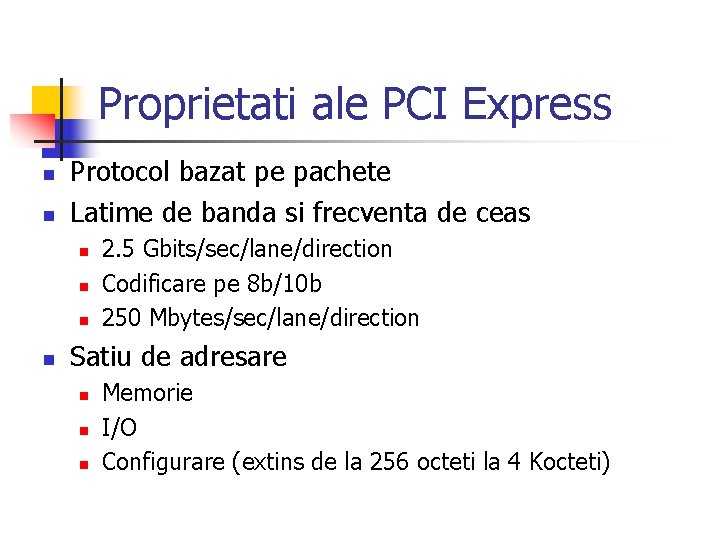

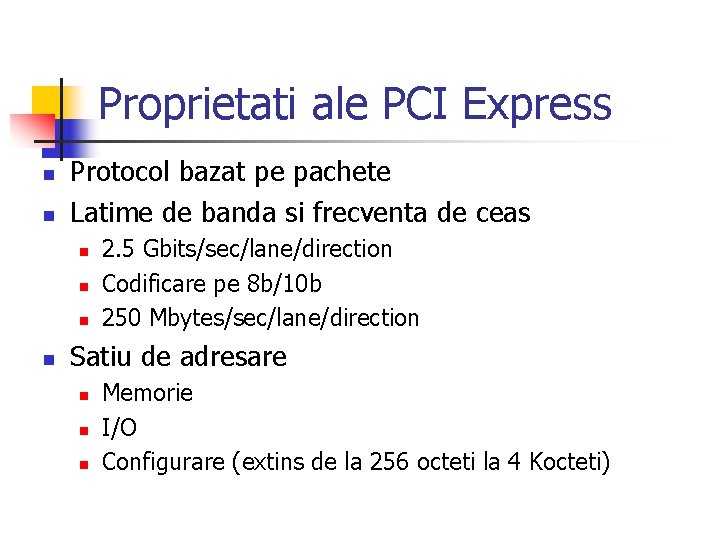

Proprietati ale PCI Express n n Protocol bazat pe pachete Latime de banda si frecventa de ceas n n 2. 5 Gbits/sec/lane/direction Codificare pe 8 b/10 b 250 Mbytes/sec/lane/direction Satiu de adresare n n n Memorie I/O Configurare (extins de la 256 octeti la 4 Kocteti)

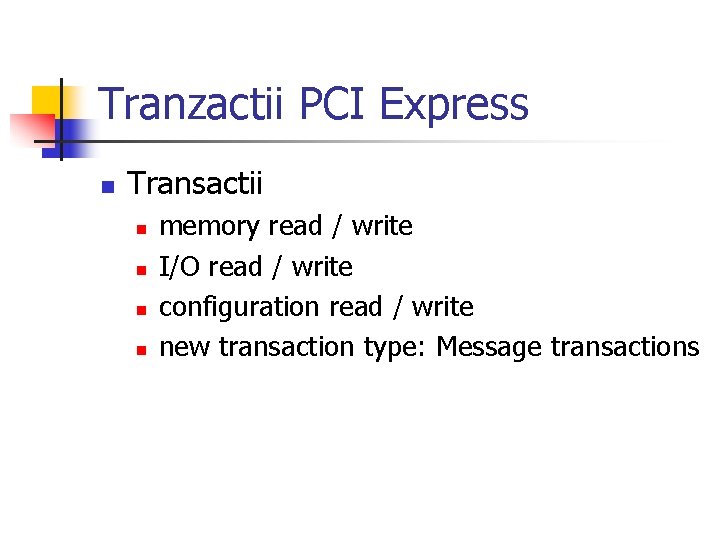

Tranzactii PCI Express n Transactii n n memory read / write I/O read / write configuration read / write new transaction type: Message transactions

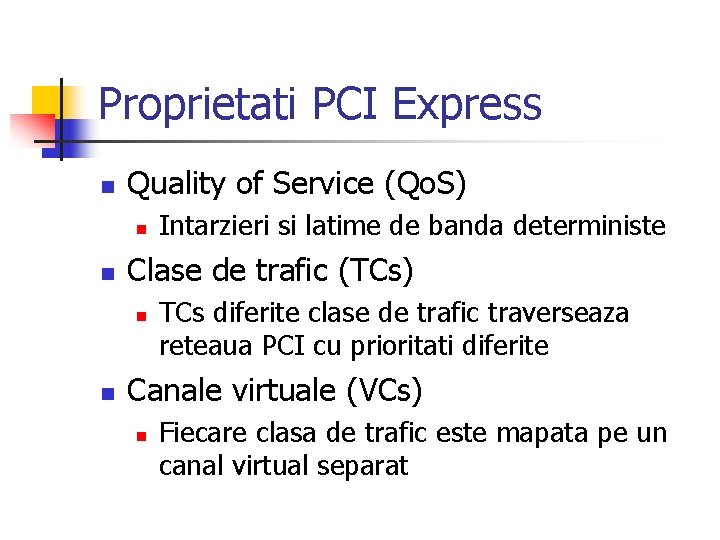

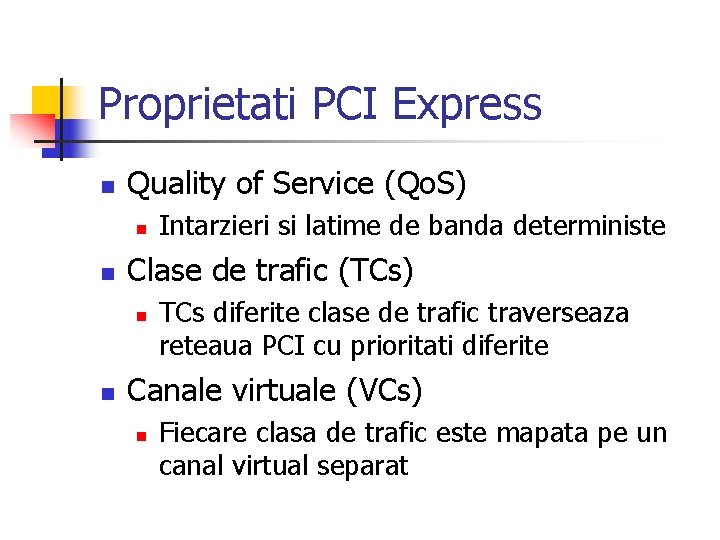

Proprietati PCI Express n Quality of Service (Qo. S) n n Clase de trafic (TCs) n n Intarzieri si latime de banda deterministe TCs diferite clase de trafic traverseaza reteaua PCI cu prioritati diferite Canale virtuale (VCs) n Fiecare clasa de trafic este mapata pe un canal virtual separat

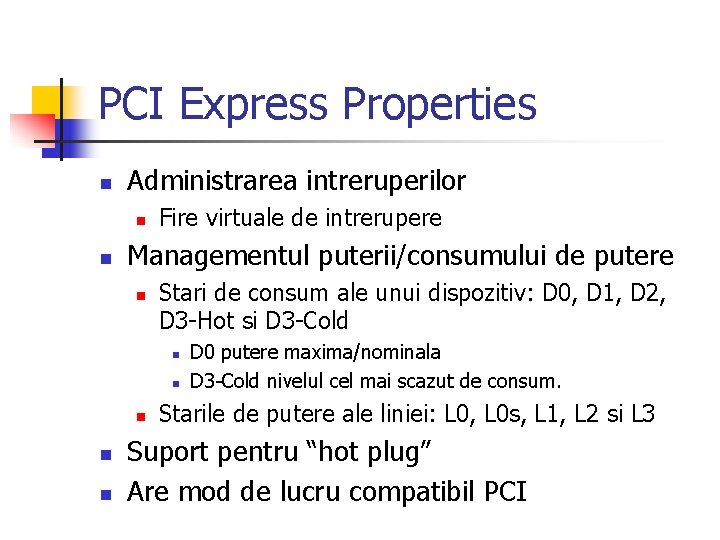

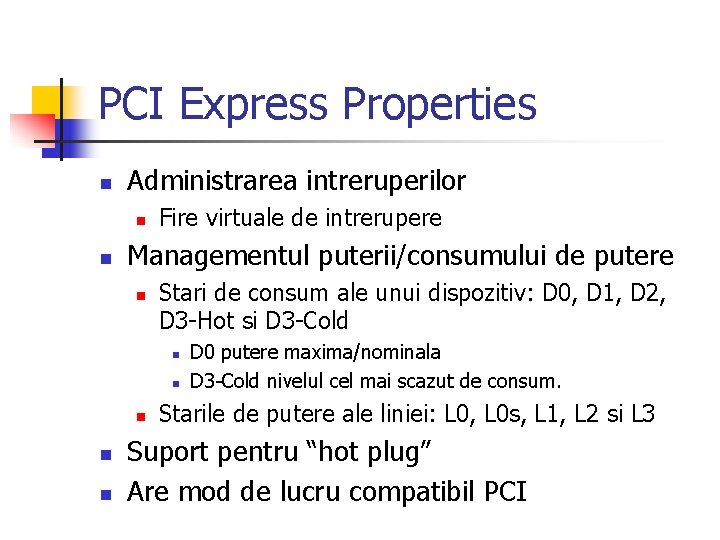

PCI Express Properties n Administrarea intreruperilor n n Fire virtuale de intrerupere Managementul puterii/consumului de putere n Stari de consum ale unui dispozitiv: D 0, D 1, D 2, D 3 -Hot si D 3 -Cold n n n D 0 putere maxima/nominala D 3 -Cold nivelul cel mai scazut de consum. Starile de putere ale liniei: L 0, L 0 s, L 1, L 2 si L 3 Suport pentru “hot plug” Are mod de lucru compatibil PCI

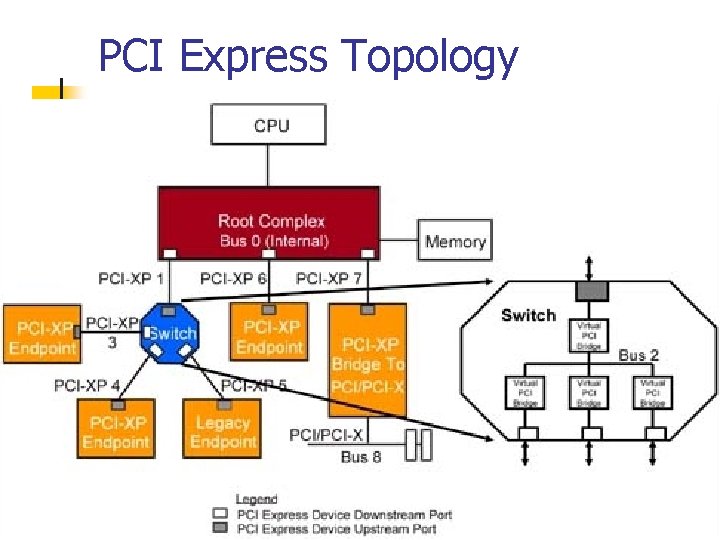

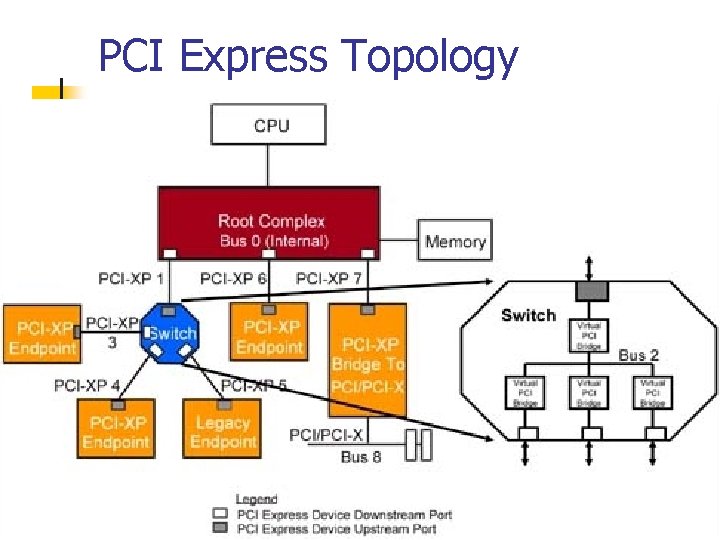

PCI Express Topology

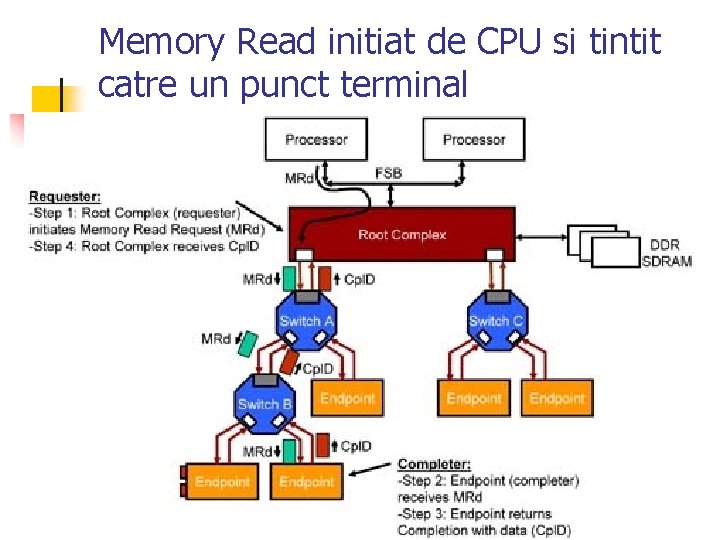

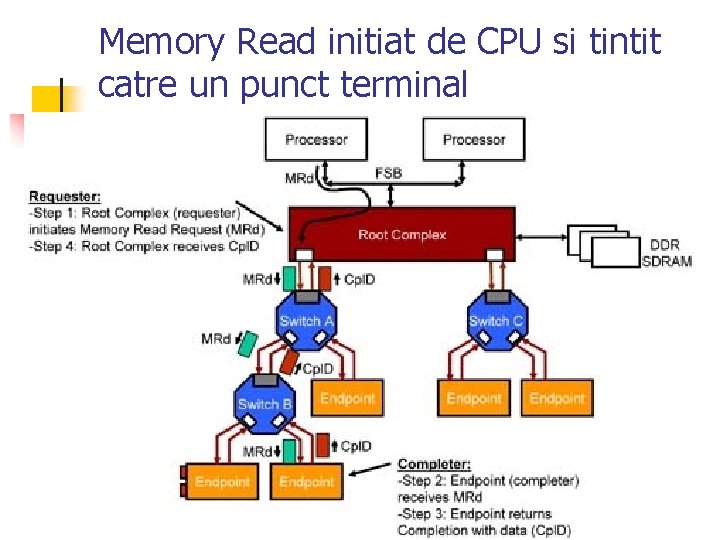

Memory Read initiat de CPU si tintit catre un punct terminal

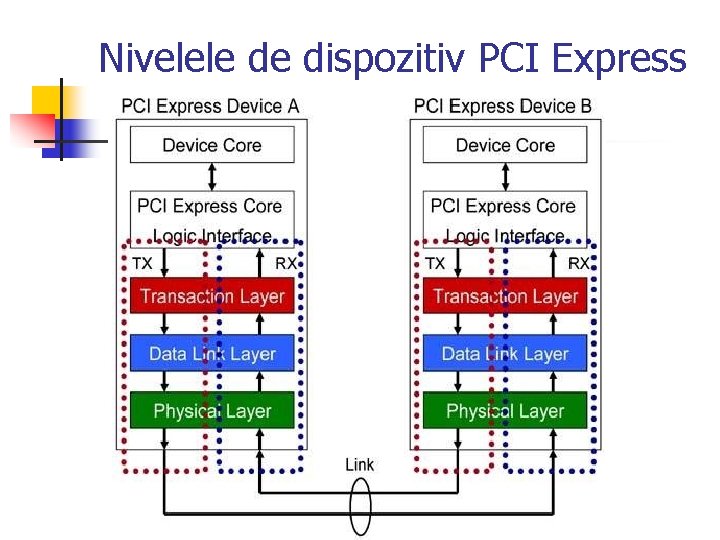

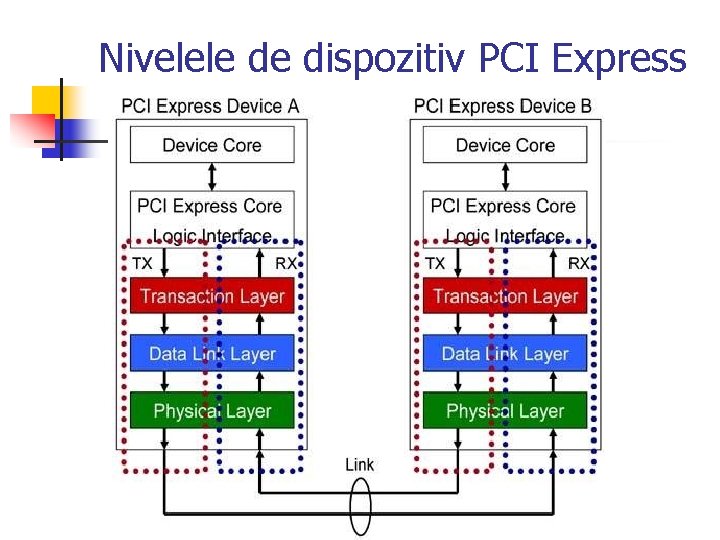

Nivelele de dispozitiv PCI Express

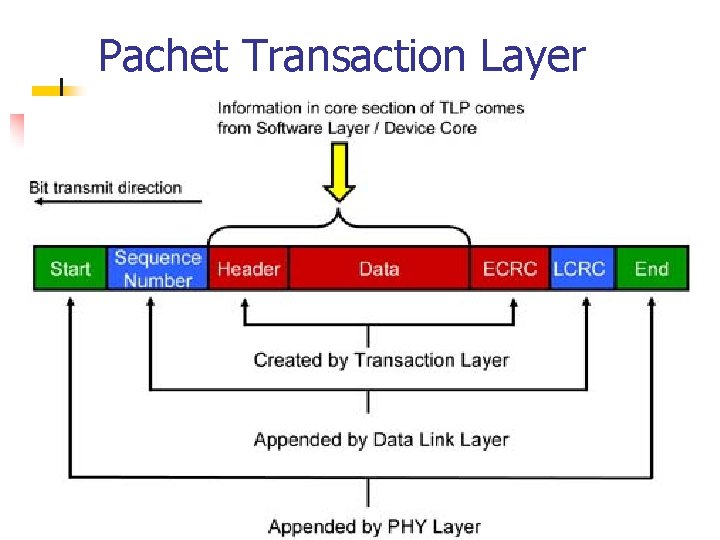

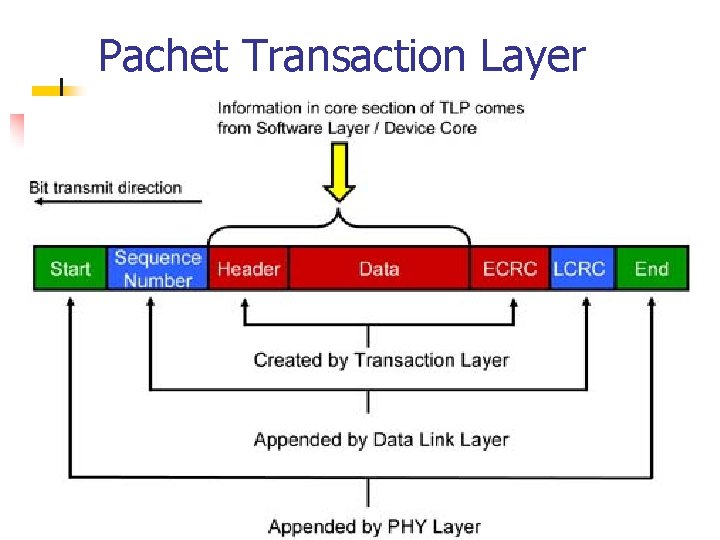

Pachet Transaction Layer