Progr na poziomie sprztowym powtrka dr in Mariusz

- Slides: 67

Progr. na poziomie sprzętowym - powtórka dr inż. Mariusz Kapruziak mkapruziak@wi. ps. pl pok. 107, tel. 449 55 44 1/67 Programowanie na poziomie sprzętowym, x 86 + powtórka ASK

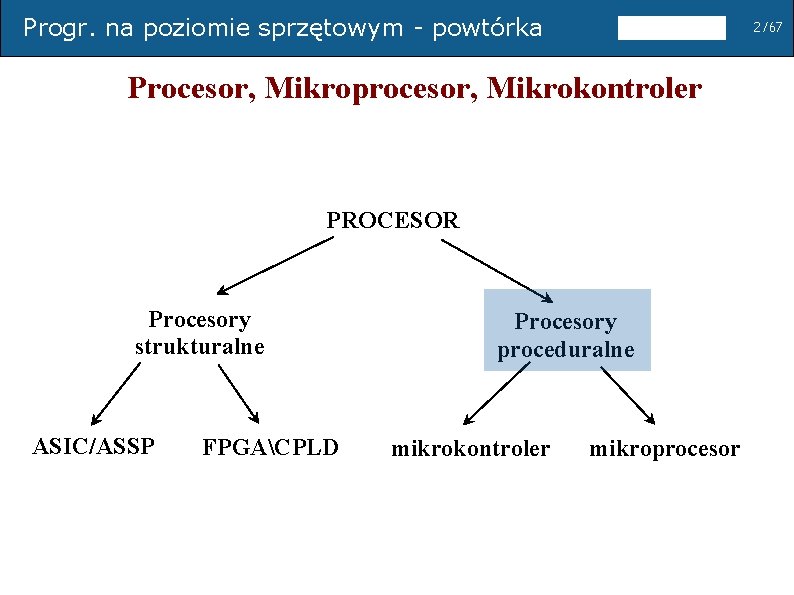

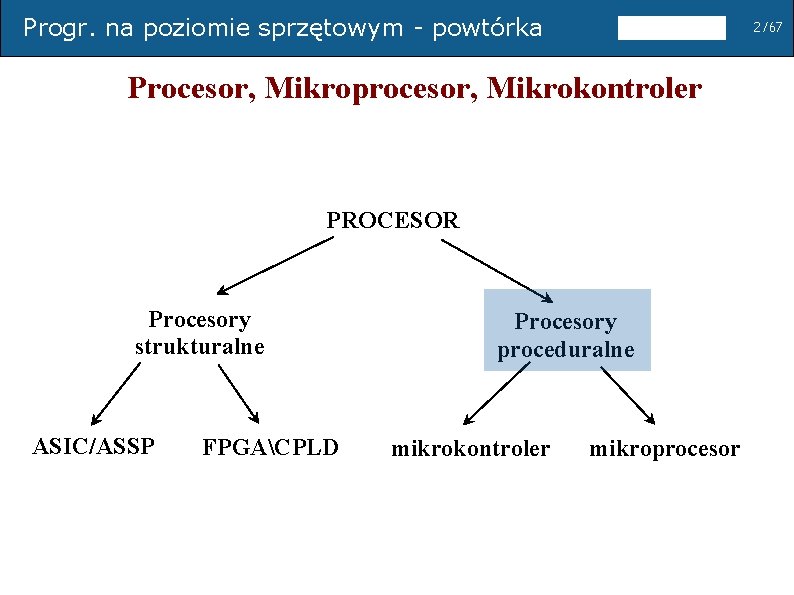

Progr. na poziomie sprzętowym - powtórka 2/67 Procesor, Mikroprocesor, Mikrokontroler PROCESOR Procesory strukturalne ASIC/ASSP FPGACPLD Procesory proceduralne mikrokontroler mikroprocesor

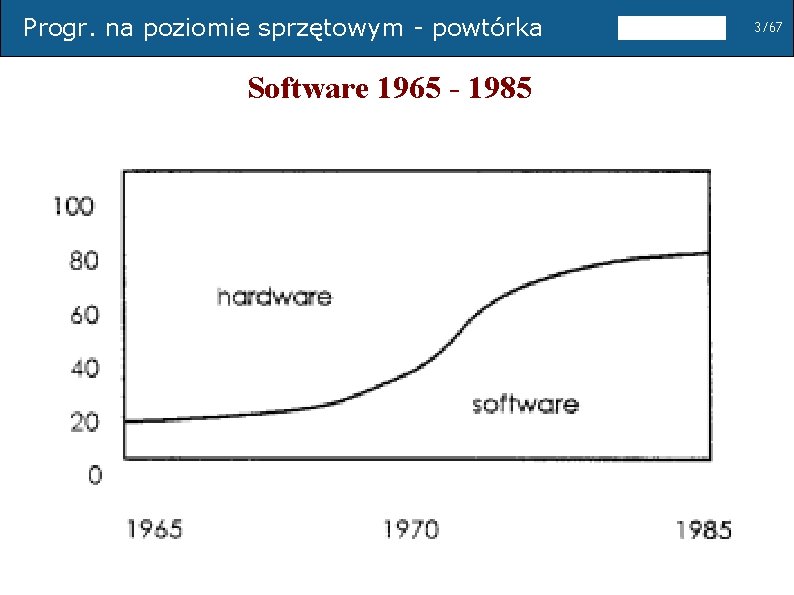

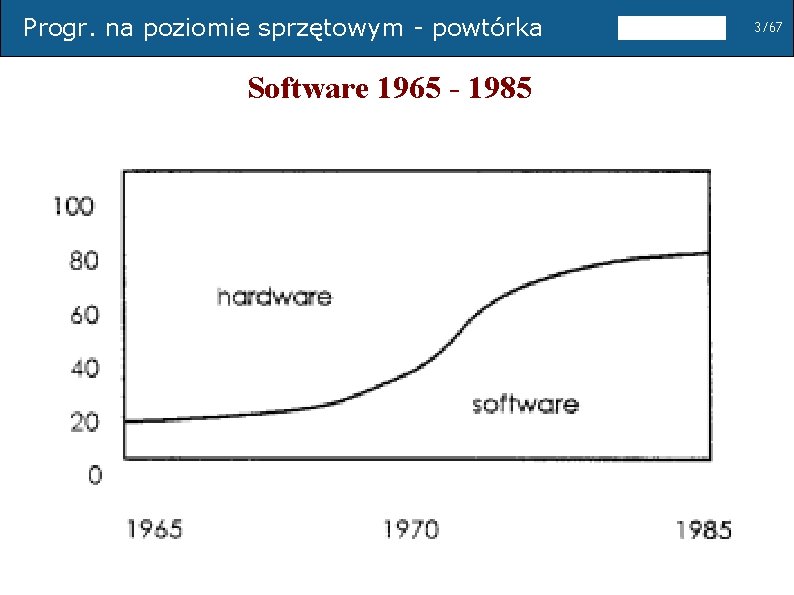

Progr. na poziomie sprzętowym - powtórka Software 1965 - 1985 3/67

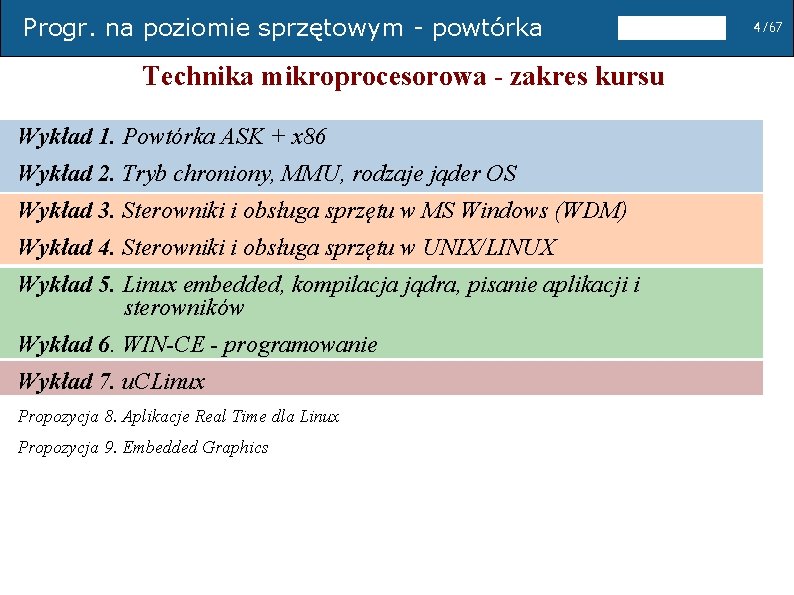

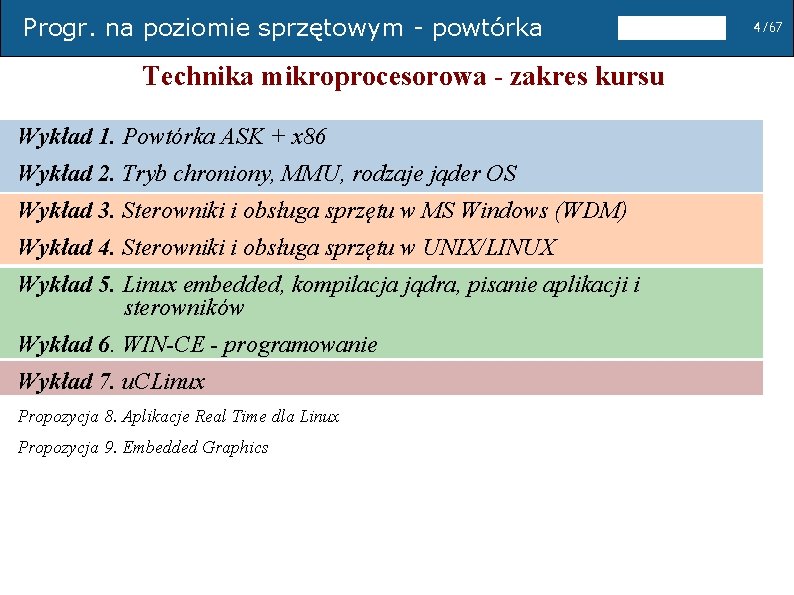

Progr. na poziomie sprzętowym - powtórka Technika mikroprocesorowa - zakres kursu Wykład 1. Powtórka ASK + x 86 Wykład 2. Tryb chroniony, MMU, rodzaje jąder OS Wykład 3. Sterowniki i obsługa sprzętu w MS Windows (WDM) Wykład 4. Sterowniki i obsługa sprzętu w UNIX/LINUX Wykład 5. Linux embedded, kompilacja jądra, pisanie aplikacji i sterowników Wykład 6. WIN-CE - programowanie Wykład 7. u. CLinux Propozycja 8. Aplikacje Real Time dla Linux Propozycja 9. Embedded Graphics 4/67

1. Architektura von Neumanna 1 2 3 4 5 5/67 Architektura von Neumana i jej znaczenie 1. specjalizowana funkcja składana jest z sekwencyjnie wykonywanych uniwersalnych operacji (program) 2. program i dane są logicznie rozdzielone 3. program i dane zndajdują się fizycznie w tej samej pamięci 4. pamięć zawierajaca zarówno program jak i dane łączy się z procesorem jedną wspólną szyną John von Neumann Komputer von Neumanna: maszyna automatyczna do wykonywania operacji pobiarania instrukcji i wykonywania instrukcji na przemian (fetch-execute mechine) P. E. Ceruzzi, A History of Modern Computing, MIT Press 2003

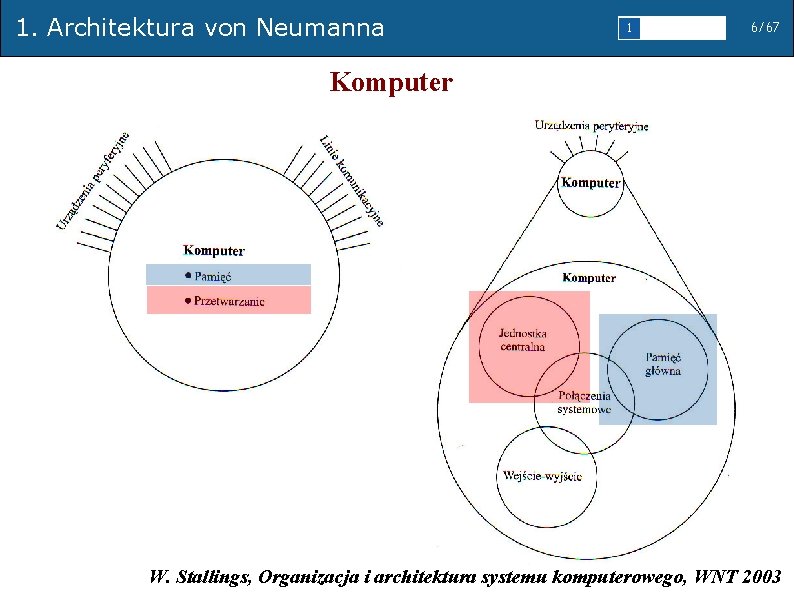

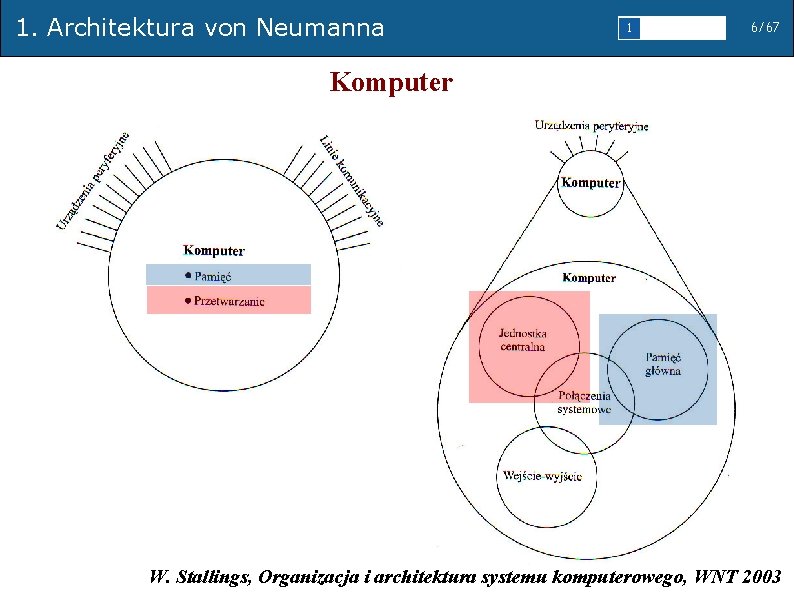

1. Architektura von Neumanna 1 2 3 4 5 6/67 Komputer W. Stallings, Organizacja i architektura systemu komputerowego, WNT 2003

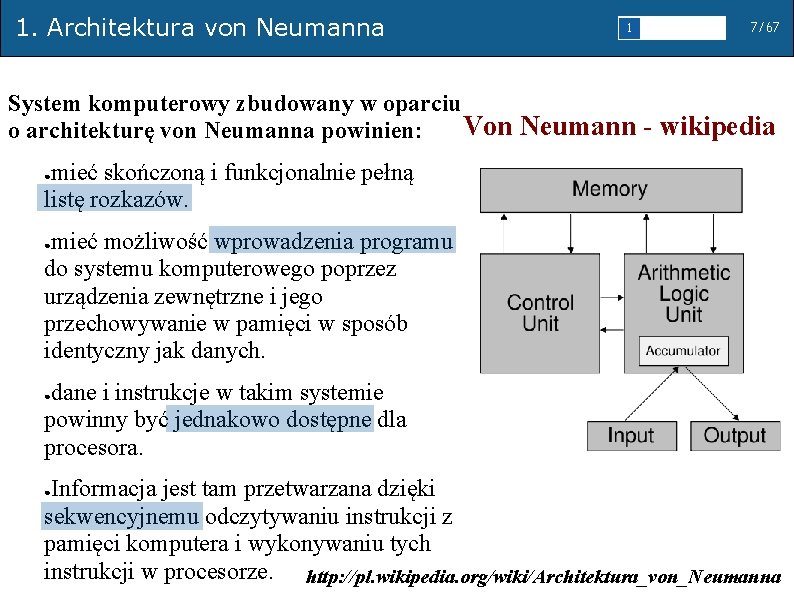

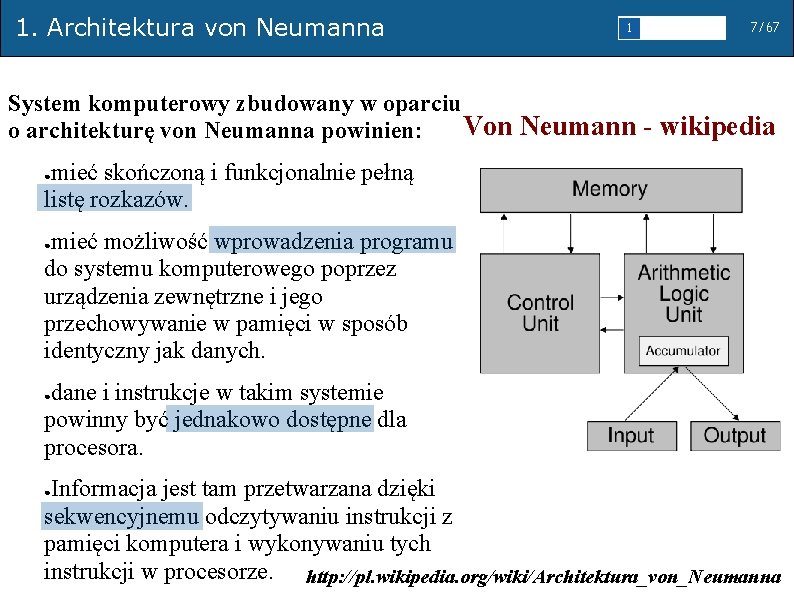

1. Architektura von Neumanna 1 2 3 4 5 7/67 System komputerowy zbudowany w oparciu Von Neumann - wikipedia o architekturę von Neumanna powinien: mieć skończoną i funkcjonalnie pełną listę rozkazów. ● mieć możliwość wprowadzenia programu do systemu komputerowego poprzez urządzenia zewnętrzne i jego przechowywanie w pamięci w sposób identyczny jak danych. ● dane i instrukcje w takim systemie powinny być jednakowo dostępne dla procesora. ● Informacja jest tam przetwarzana dzięki sekwencyjnemu odczytywaniu instrukcji z pamięci komputera i wykonywaniu tych instrukcji w procesorze. http: //pl. wikipedia. org/wiki/Architektura_von_Neumanna ●

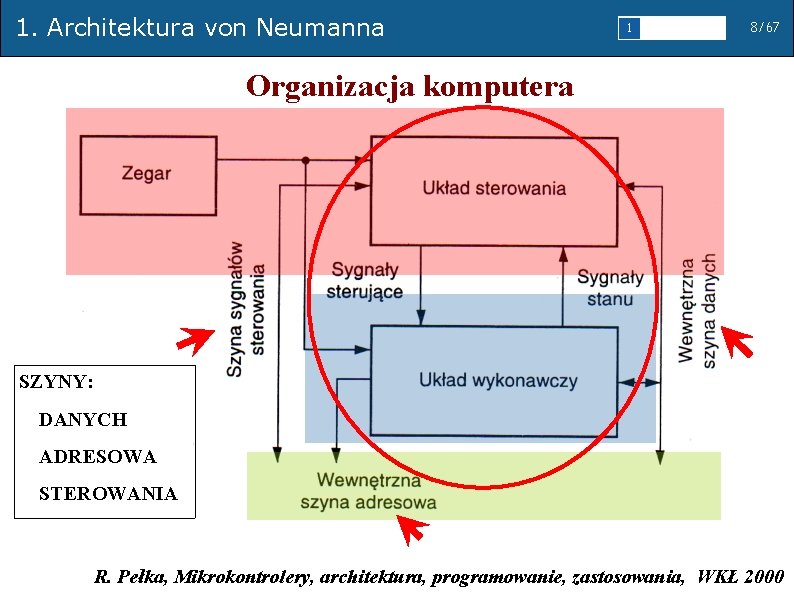

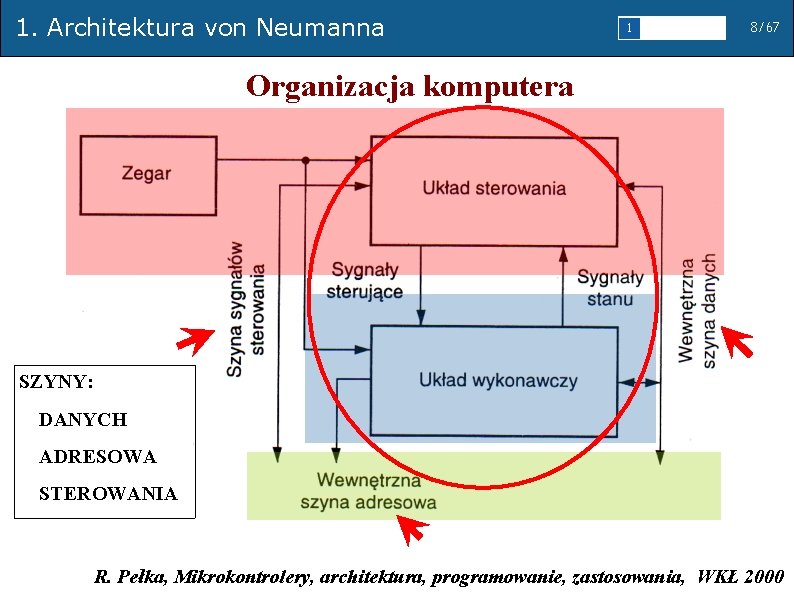

1. Architektura von Neumanna 1 2 3 4 5 8/67 Organizacja komputera SZYNY: DANYCH ADRESOWA STEROWANIA R. Pełka, Mikrokontrolery, architektura, programowanie, zastosowania, WKŁ 2000

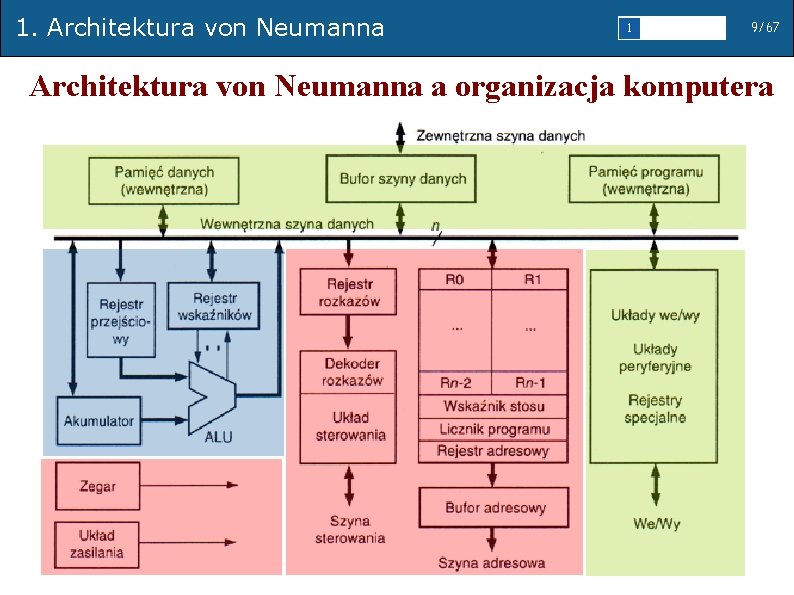

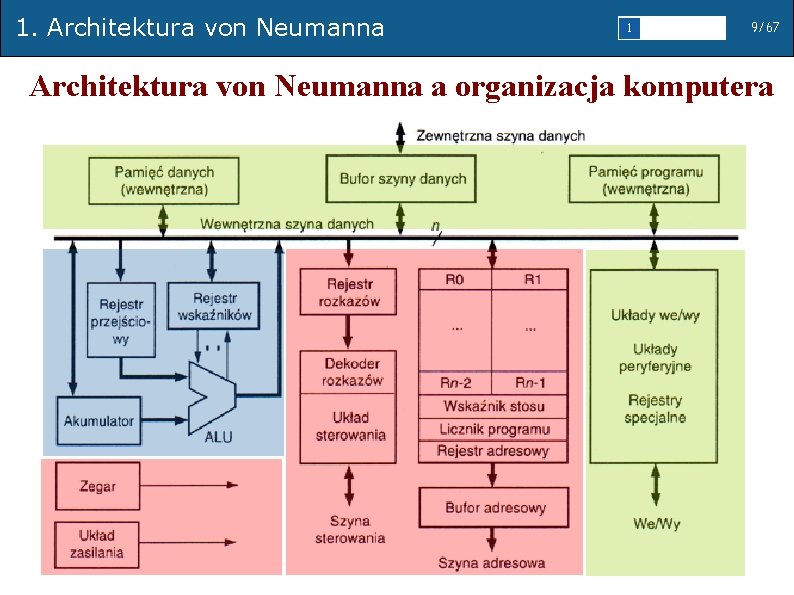

1. Architektura von Neumanna 1 2 3 4 5 9/67 Architektura von Neumanna a organizacja komputera

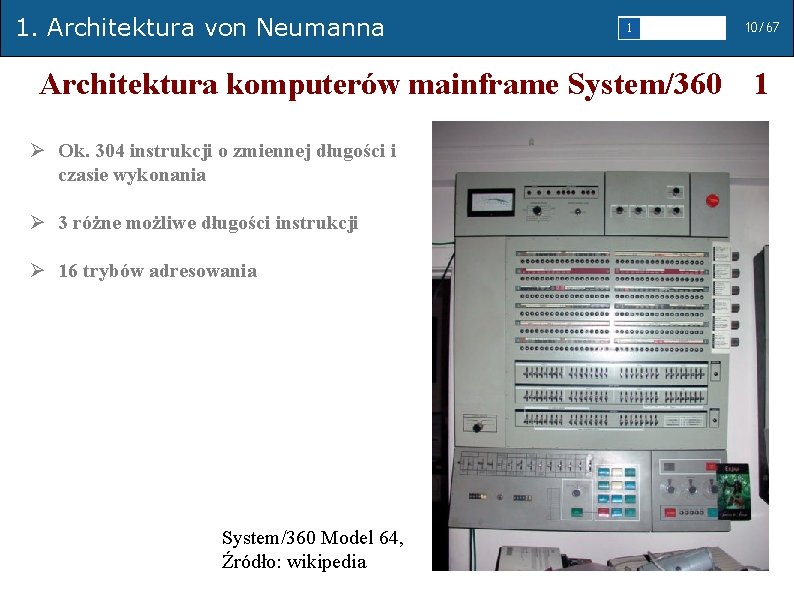

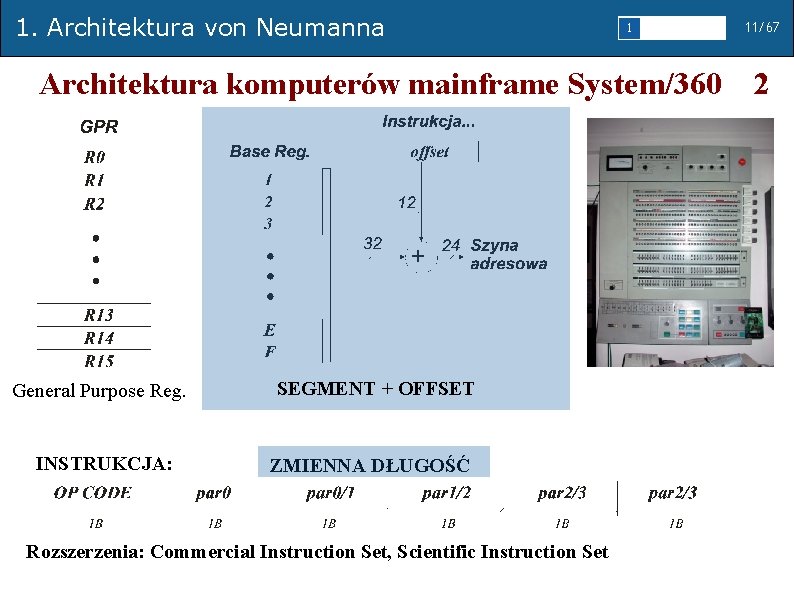

1. Architektura von Neumanna 1 2 3 4 5 Architektura komputerów mainframe System/360 Ø Ok. 304 instrukcji o zmiennej długości i czasie wykonania Ø 3 różne możliwe długości instrukcji Ø 16 trybów adresowania System/360 Model 64, Źródło: wikipedia 10/67 1

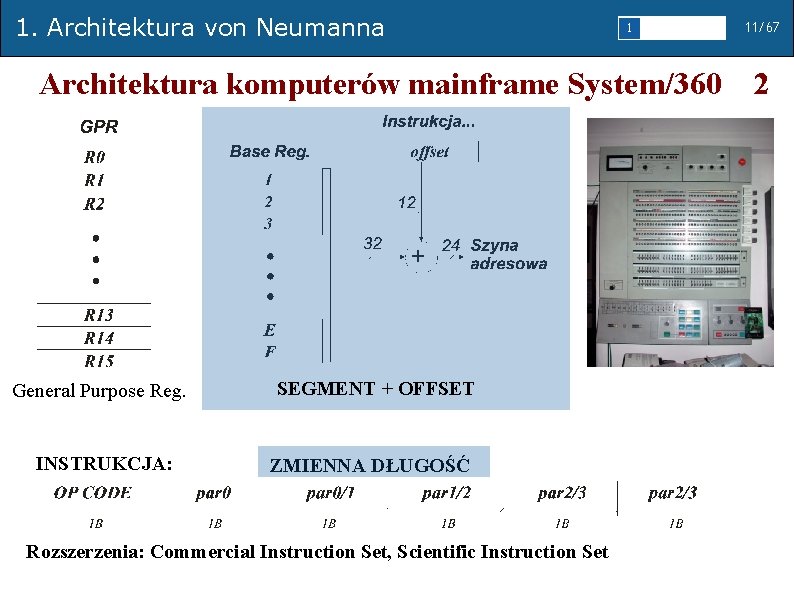

1. Architektura von Neumanna 1 2 3 4 5 Architektura komputerów mainframe System/360 General Purpose Reg. INSTRUKCJA: SEGMENT + OFFSET ZMIENNA DŁUGOŚĆ Rozszerzenia: Commercial Instruction Set, Scientific Instruction Set 11/67 2

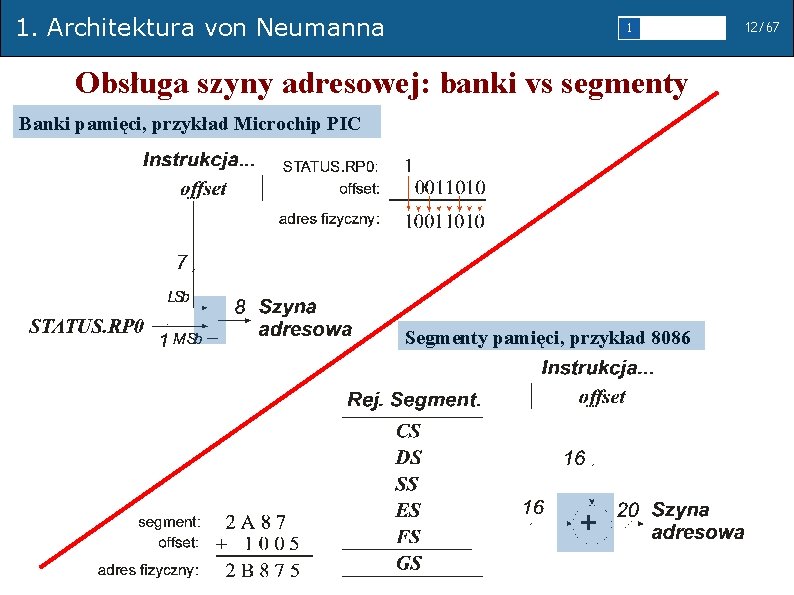

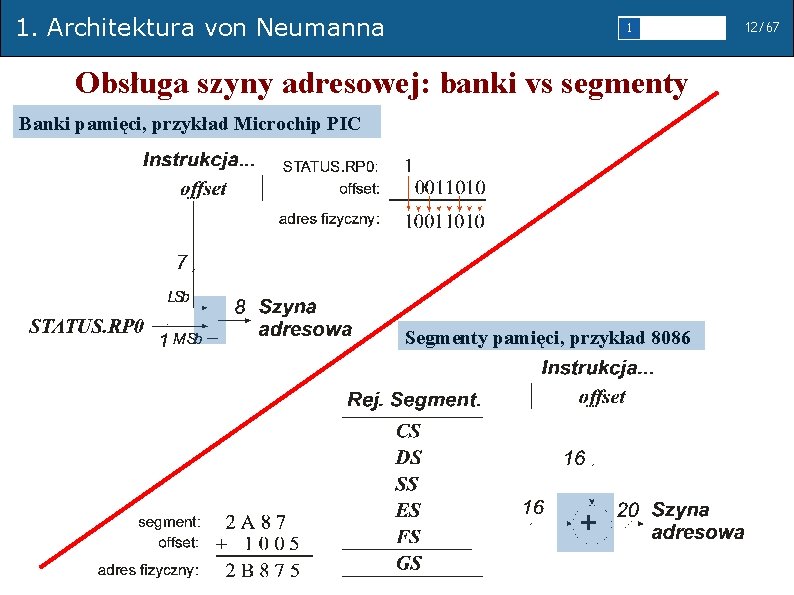

1. Architektura von Neumanna 1 2 3 4 Obsługa szyny adresowej: banki vs segmenty Banki pamięci, przykład Microchip PIC Segmenty pamięci, przykład 8086 5 12/67

1. Architektura von Neumanna 1 2 3 4 5 Architektura komputerów mainframe System/360 System operacyjny: BOS/360 –Basic Operating System / 360 DOS/360 – Disk Operating System / 360 OS/360 MVT – Operating System 13/67 4

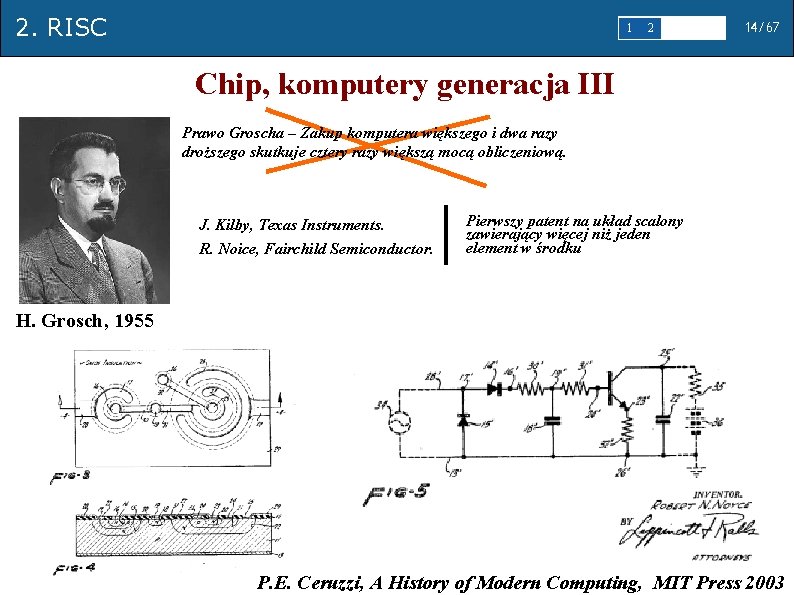

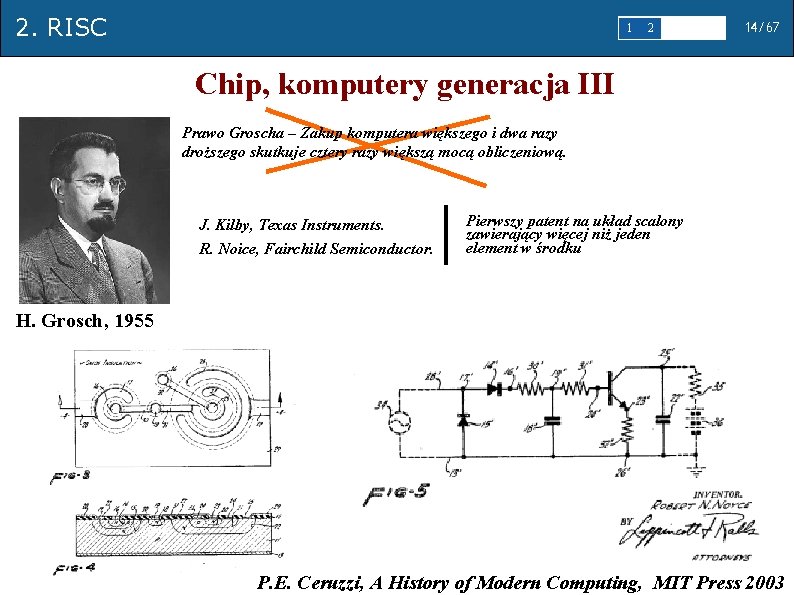

2. RISC 1 2 3 4 5 14/67 Chip, komputery generacja III Prawo Groscha – Zakup komputera większego i dwa razy droższego skutkuje cztery razy większą mocą obliczeniową. J. Kilby, Texas Instruments. R. Noice, Fairchild Semiconductor. Pierwszy patent na układ scalony zawierający więcej niż jeden element w środku H. Grosch, 1955 P. E. Ceruzzi, A History of Modern Computing, MIT Press 2003

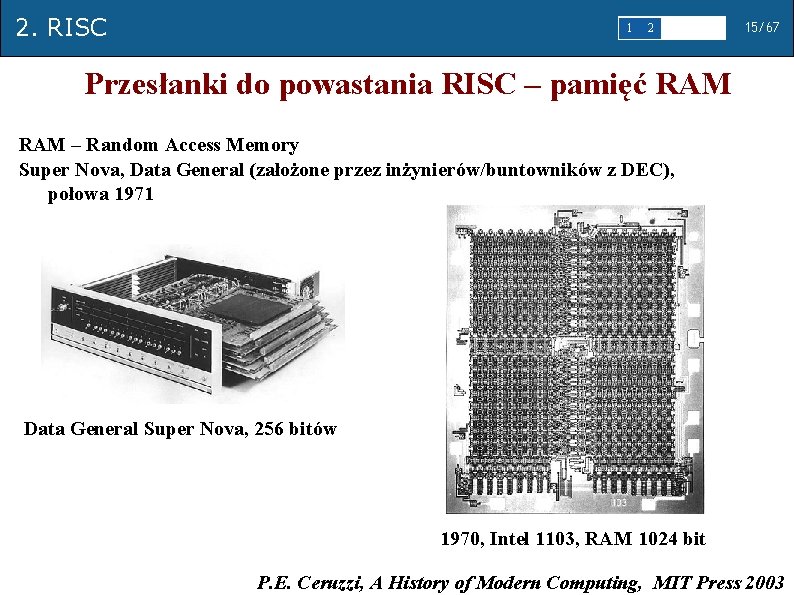

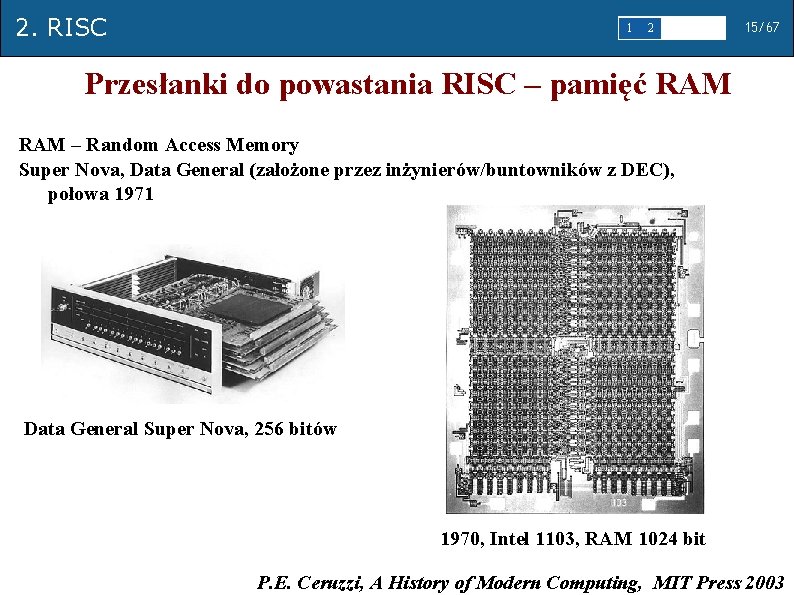

2. RISC 1 2 3 4 5 15/67 Przesłanki do powastania RISC – pamięć RAM – Random Access Memory Super Nova, Data General (założone przez inżynierów/buntowników z DEC), połowa 1971 Data General Super Nova, 256 bitów 1970, Intel 1103, RAM 1024 bit P. E. Ceruzzi, A History of Modern Computing, MIT Press 2003

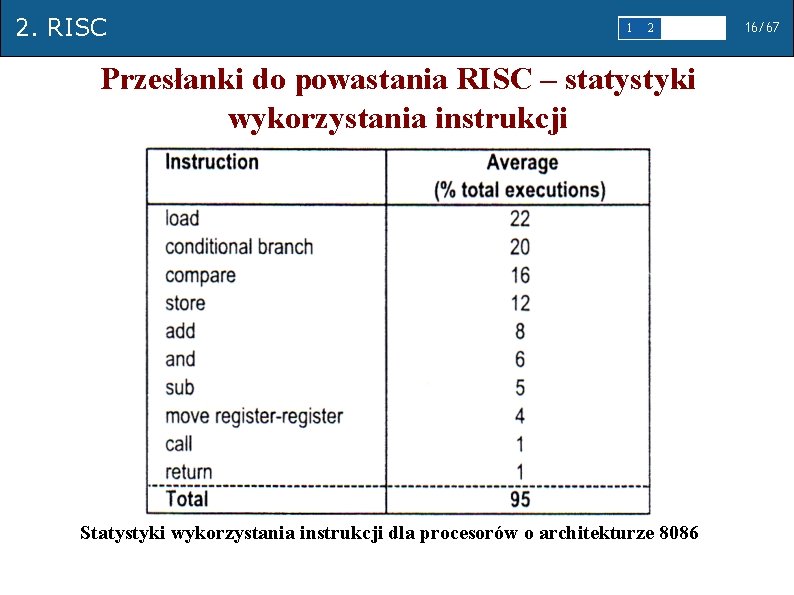

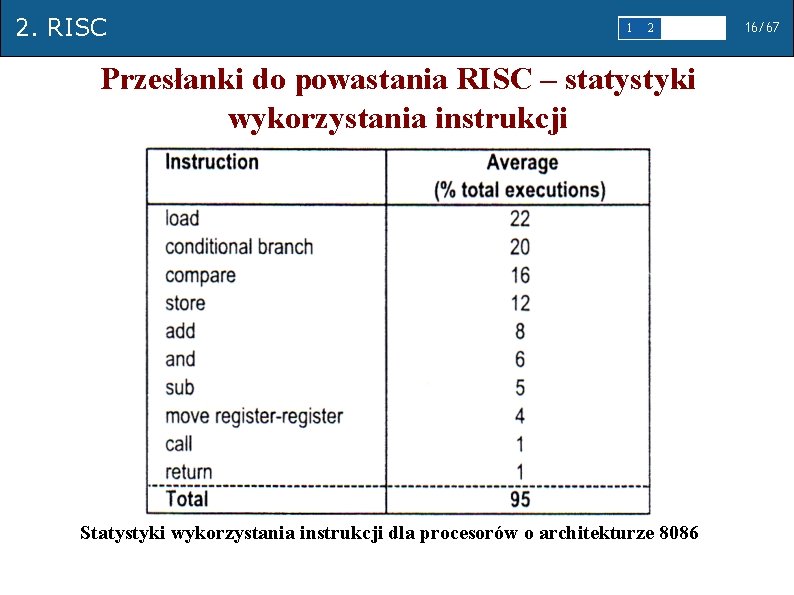

2. RISC 1 2 3 4 Przesłanki do powastania RISC – statystyki wykorzystania instrukcji Statystyki wykorzystania instrukcji dla procesorów o architekturze 8086 5 16/67

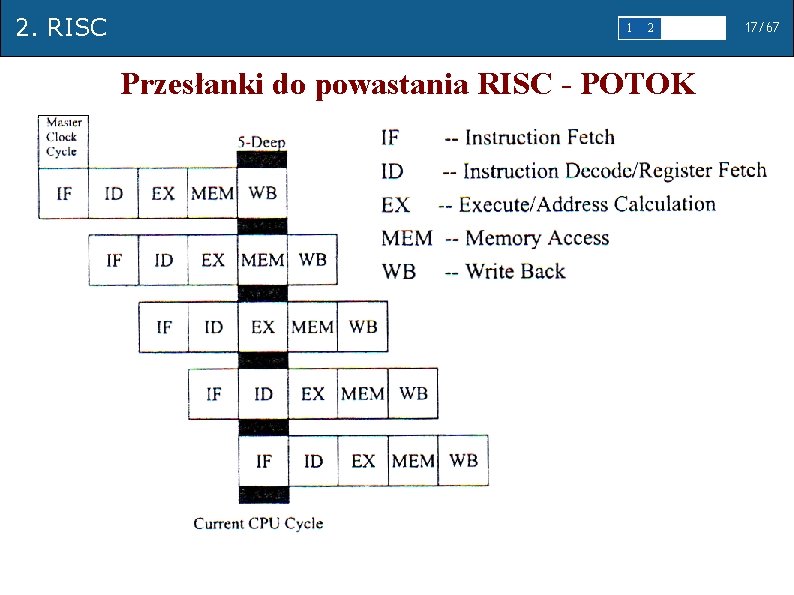

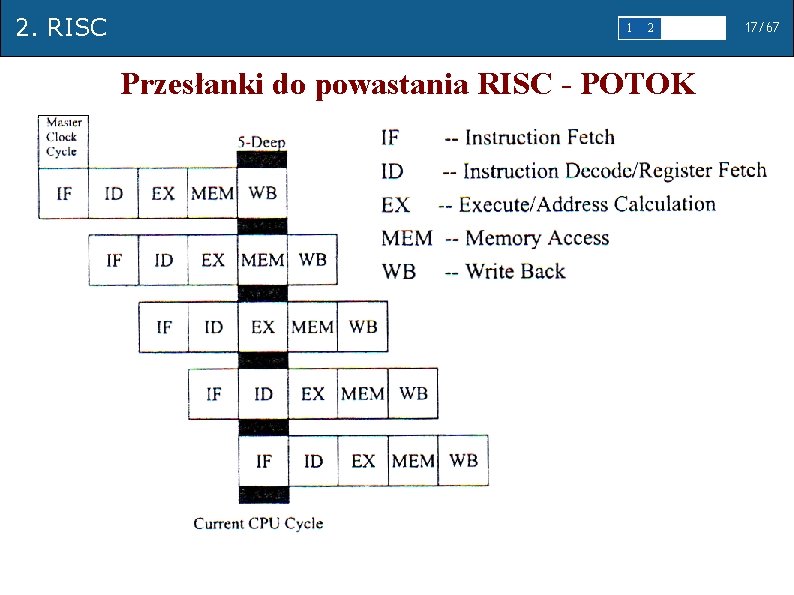

2. RISC 1 2 3 4 Przesłanki do powastania RISC - POTOK 5 17/67

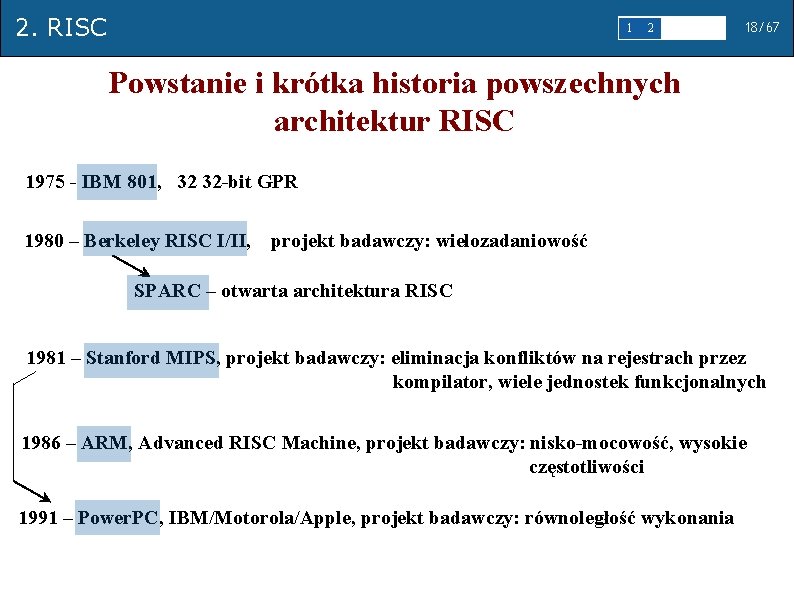

2. RISC 1 2 3 4 5 18/67 Powstanie i krótka historia powszechnych architektur RISC 1975 - IBM 801, 32 32 -bit GPR 1980 – Berkeley RISC I/II, projekt badawczy: wielozadaniowość SPARC – otwarta architektura RISC 1981 – Stanford MIPS, projekt badawczy: eliminacja konfliktów na rejestrach przez kompilator, wiele jednostek funkcjonalnych 1986 – ARM, Advanced RISC Machine, projekt badawczy: nisko-mocowość, wysokie częstotliwości 1991 – Power. PC, IBM/Motorola/Apple, projekt badawczy: równoległość wykonania

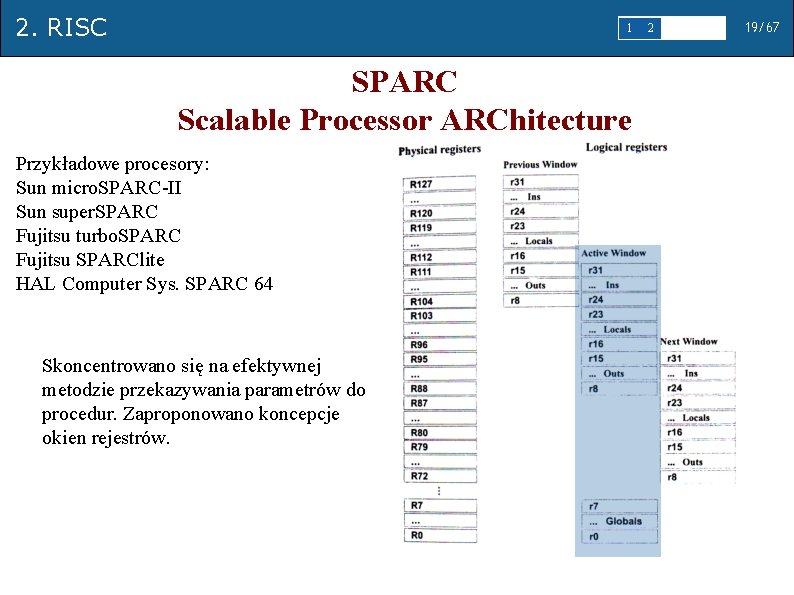

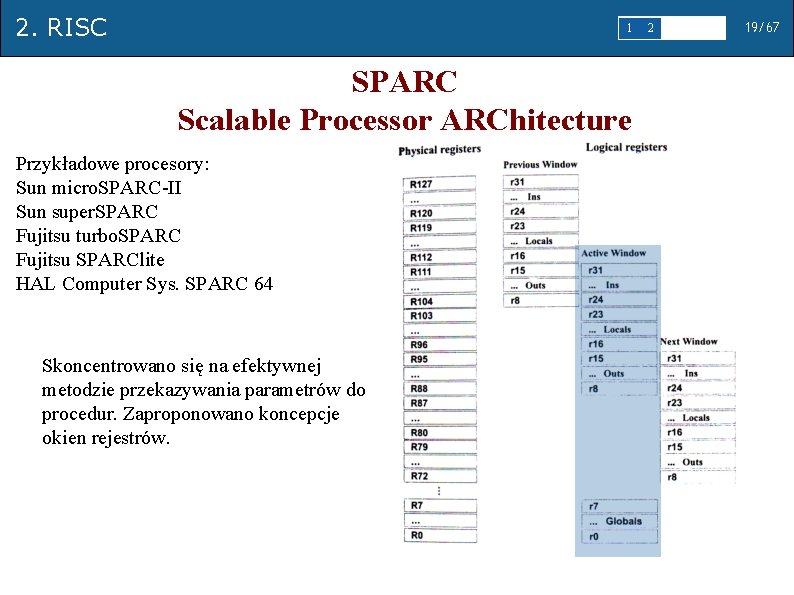

2. RISC 1 SPARC Scalable Processor ARChitecture Przykładowe procesory: Sun micro. SPARC-II Sun super. SPARC Fujitsu turbo. SPARC Fujitsu SPARClite HAL Computer Sys. SPARC 64 Skoncentrowano się na efektywnej metodzie przekazywania parametrów do procedur. Zaproponowano koncepcje okien rejestrów. 2 3 4 5 19/67

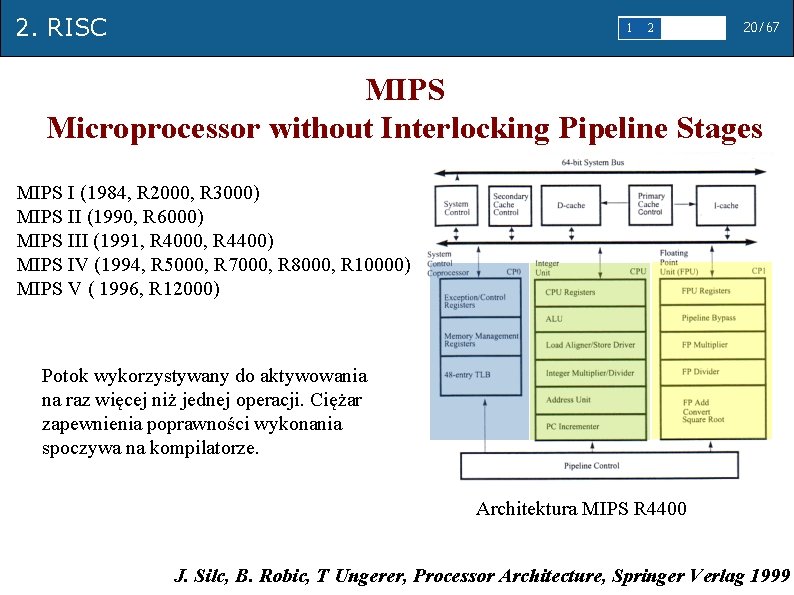

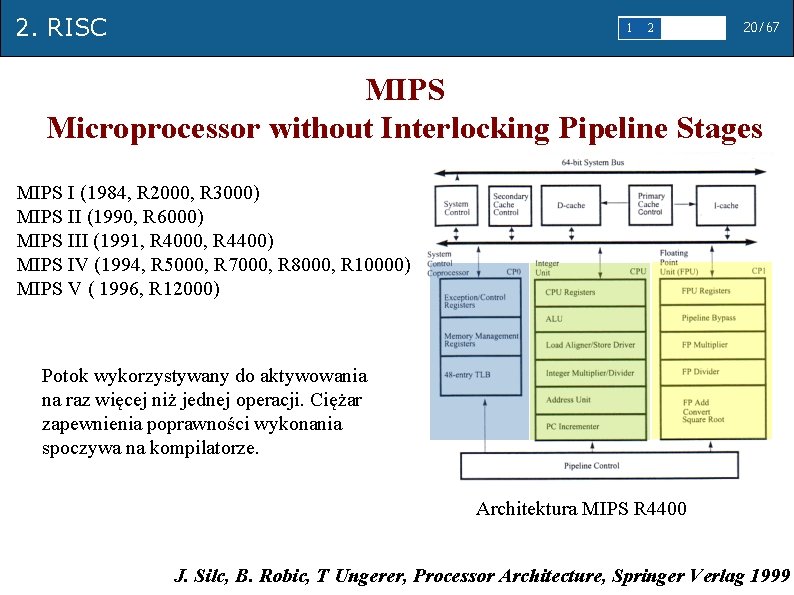

2. RISC 1 2 3 4 5 20/67 MIPS Microprocessor without Interlocking Pipeline Stages MIPS I (1984, R 2000, R 3000) MIPS II (1990, R 6000) MIPS III (1991, R 4000, R 4400) MIPS IV (1994, R 5000, R 7000, R 8000, R 10000) MIPS V ( 1996, R 12000) Potok wykorzystywany do aktywowania na raz więcej niż jednej operacji. Ciężar zapewnienia poprawności wykonania spoczywa na kompilatorze. Architektura MIPS R 4400 J. Silc, B. Robic, T Ungerer, Processor Architecture, Springer Verlag 1999

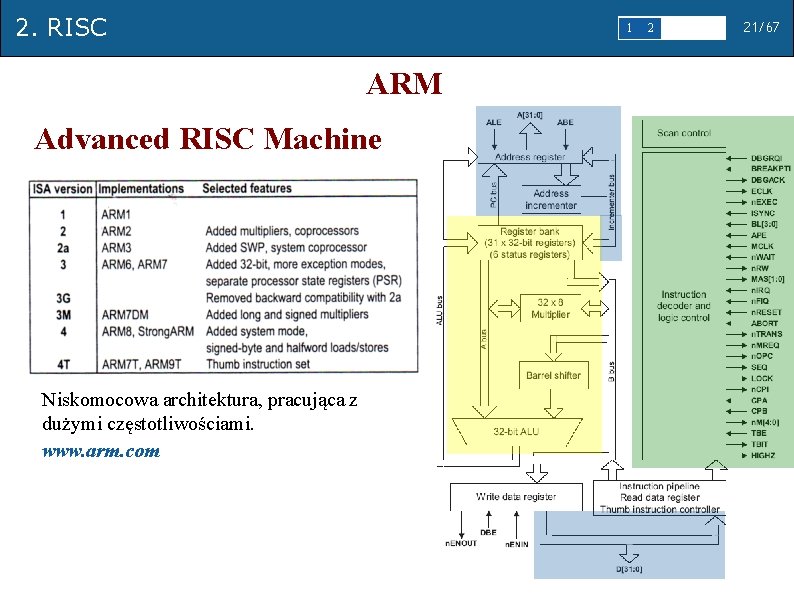

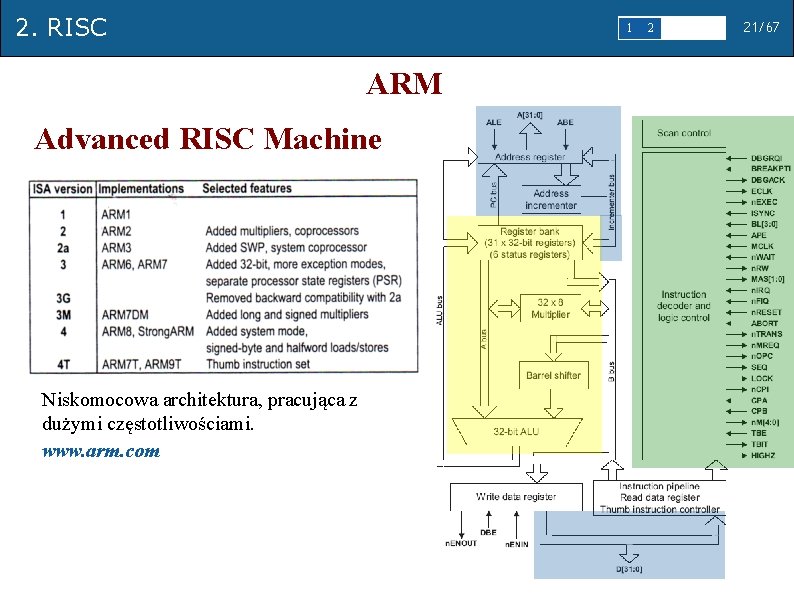

2. RISC 1 ARM Advanced RISC Machine Niskomocowa architektura, pracująca z dużymi częstotliwościami. www. arm. com 2 3 4 5 21/67

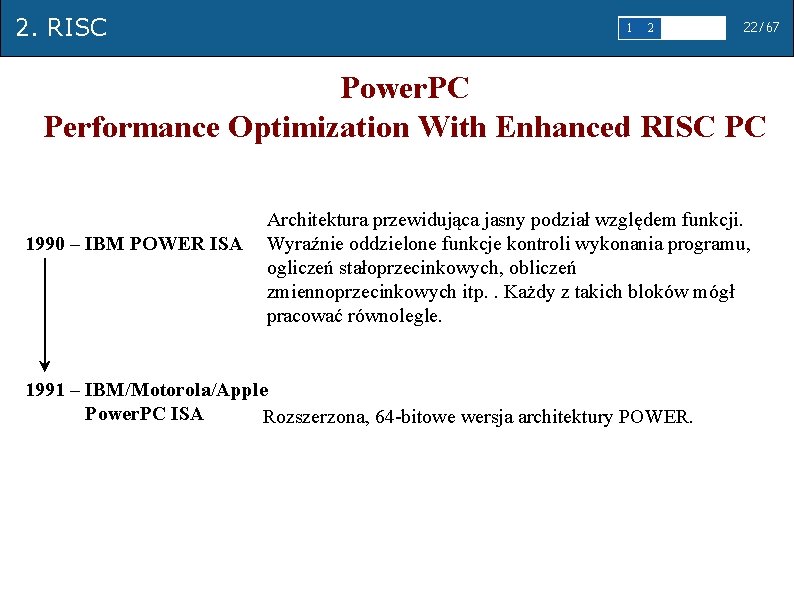

2. RISC 1 2 3 4 5 22/67 Power. PC Performance Optimization With Enhanced RISC PC 1990 – IBM POWER ISA Architektura przewidująca jasny podział względem funkcji. Wyraźnie oddzielone funkcje kontroli wykonania programu, ogliczeń stałoprzecinkowych, obliczeń zmiennoprzecinkowych itp. . Każdy z takich bloków mógł pracować równolegle. 1991 – IBM/Motorola/Apple Power. PC ISA Rozszerzona, 64 -bitowe wersja architektury POWER.

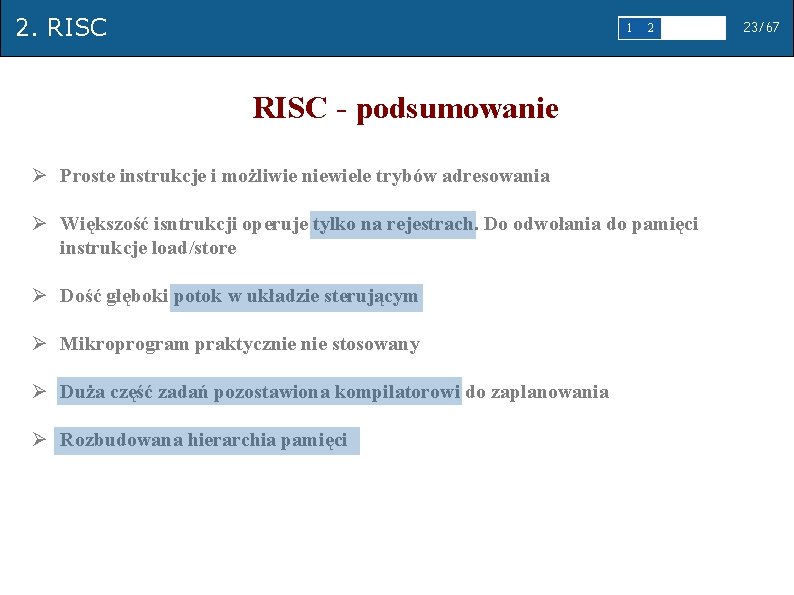

2. RISC 1 2 3 4 RISC - podsumowanie Ø Proste instrukcje i możliwie niewiele trybów adresowania Ø Większość isntrukcji operuje tylko na rejestrach. Do odwołania do pamięci instrukcje load/store Ø Dość głęboki potok w układzie sterującym Ø Mikroprogram praktycznie stosowany Ø Duża część zadań pozostawiona kompilatorowi do zaplanowania Ø Rozbudowana hierarchia pamięci 5 23/67

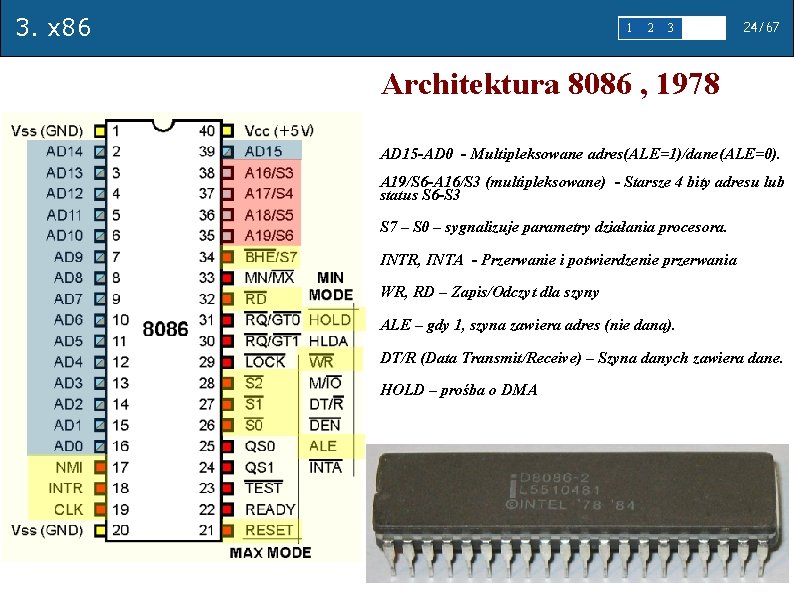

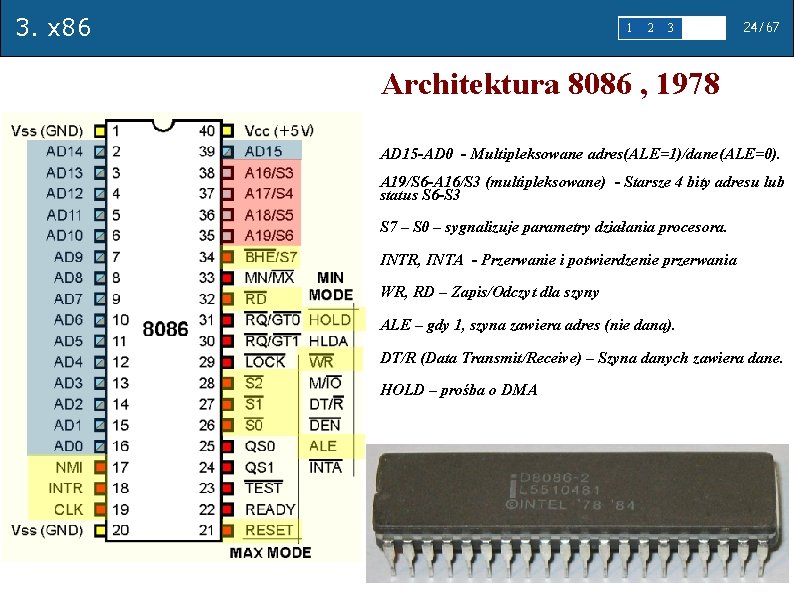

3. x 86 1 2 3 4 5 24/67 Architektura 8086 , 1978 AD 15 -AD 0 - Multipleksowane adres(ALE=1)/dane(ALE=0). A 19/S 6 -A 16/S 3 (multipleksowane) - Starsze 4 bity adresu lub status S 6 -S 3 S 7 – S 0 – sygnalizuje parametry działania procesora. INTR, INTA - Przerwanie i potwierdzenie przerwania WR, RD – Zapis/Odczyt dla szyny ALE – gdy 1, szyna zawiera adres (nie daną). DT/R (Data Transmit/Receive) – Szyna danych zawiera dane. HOLD – prośba o DMA

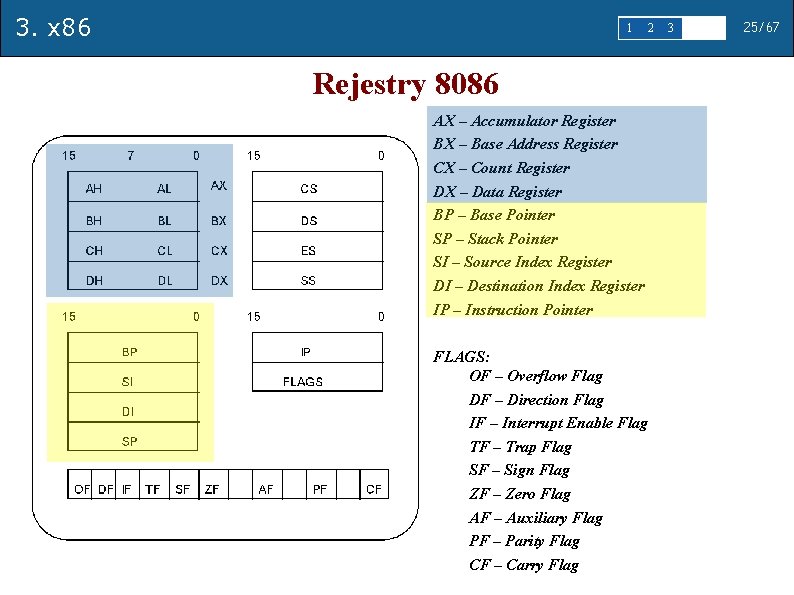

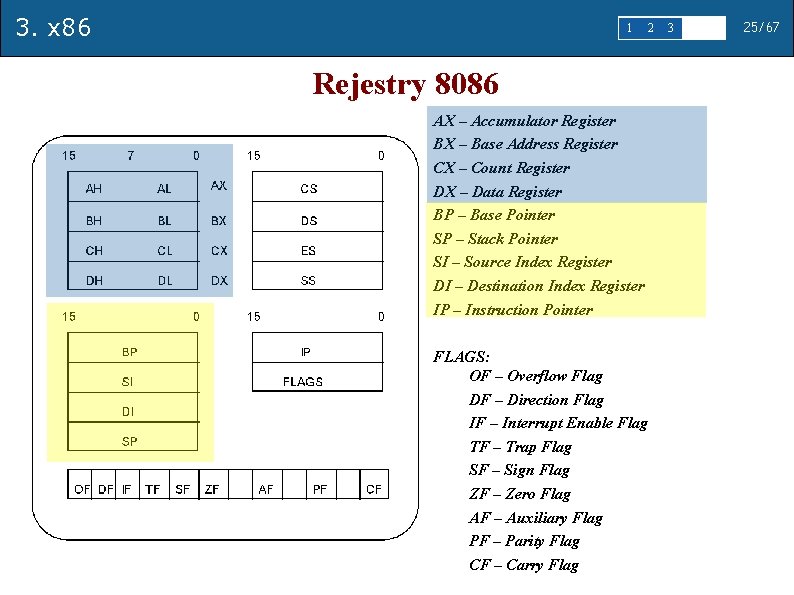

3. x 86 1 2 Rejestry 8086 AX – Accumulator Register BX – Base Address Register CX – Count Register DX – Data Register BP – Base Pointer SP – Stack Pointer SI – Source Index Register DI – Destination Index Register IP – Instruction Pointer FLAGS: OF – Overflow Flag DF – Direction Flag IF – Interrupt Enable Flag TF – Trap Flag SF – Sign Flag ZF – Zero Flag AF – Auxiliary Flag PF – Parity Flag CF – Carry Flag 3 4 5 25/67

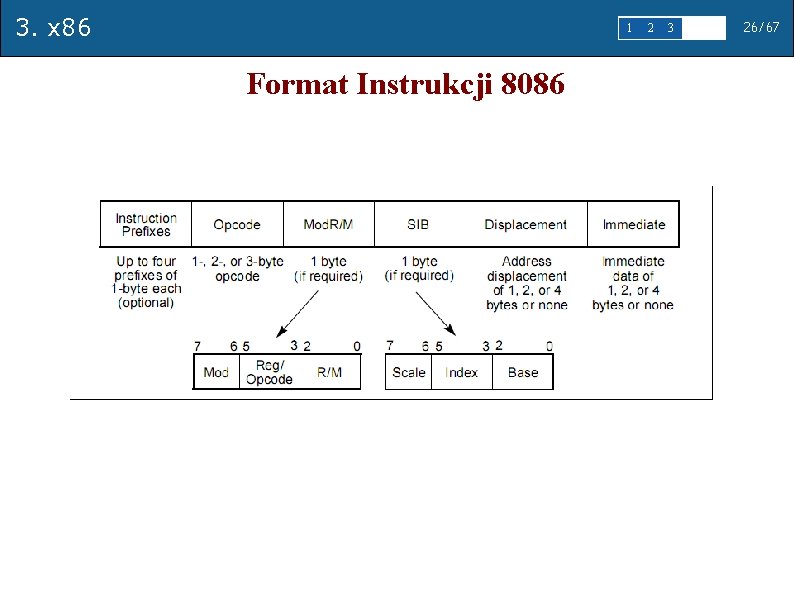

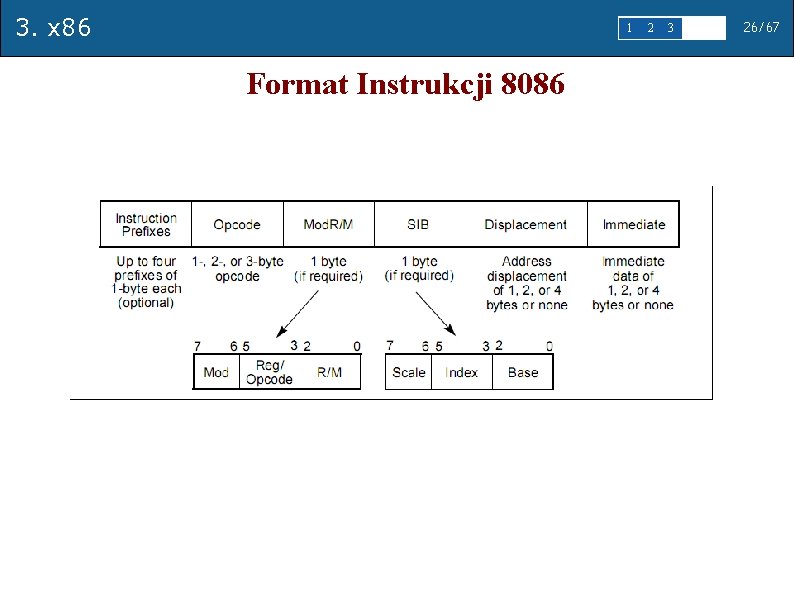

3. x 86 1 Format Instrukcji 8086 2 3 4 5 26/67

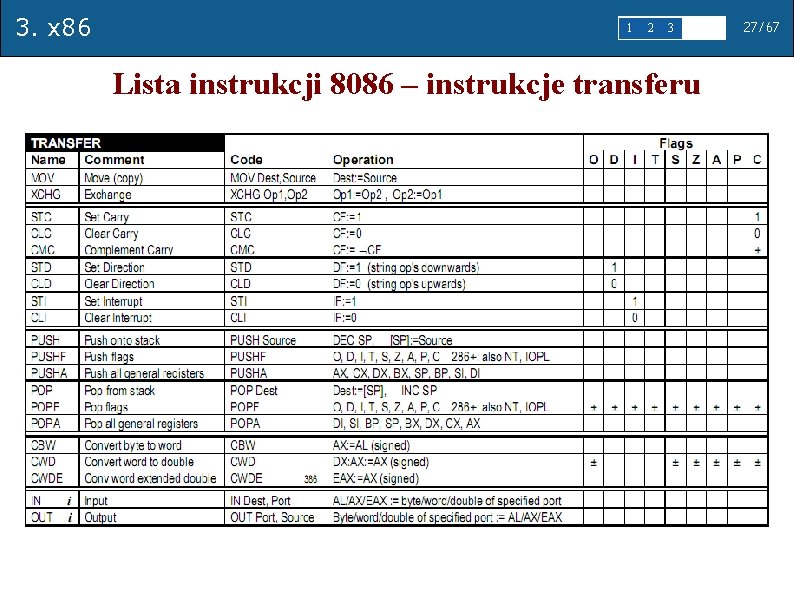

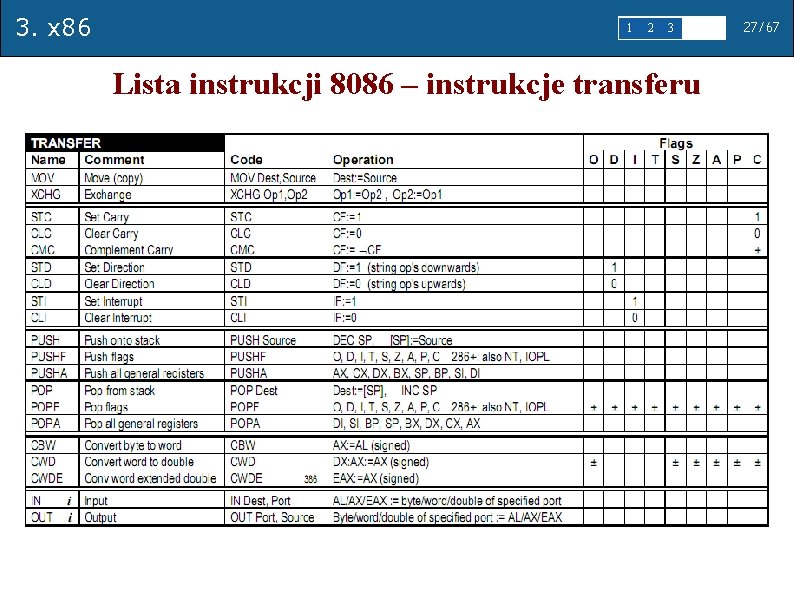

3. x 86 1 2 3 4 Lista instrukcji 8086 – instrukcje transferu 5 27/67

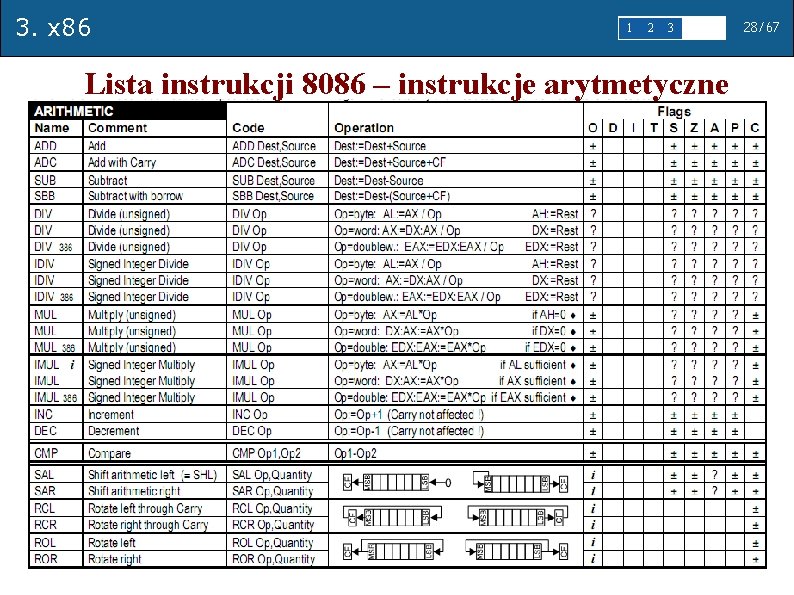

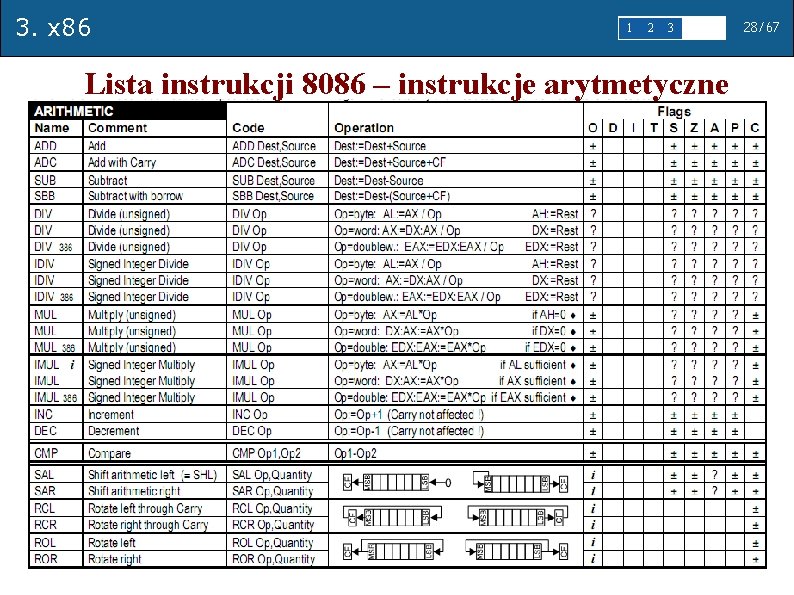

3. x 86 1 2 3 4 5 Lista instrukcji 8086 – instrukcje arytmetyczne 28/67

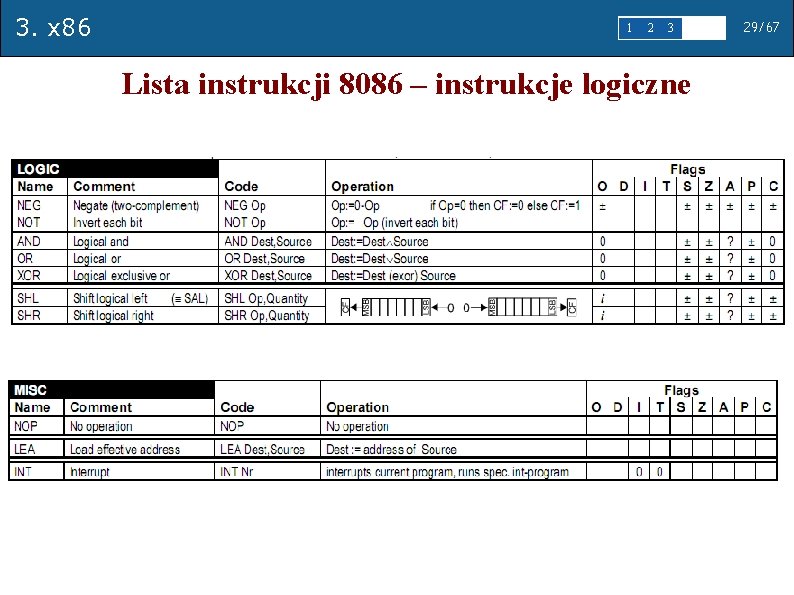

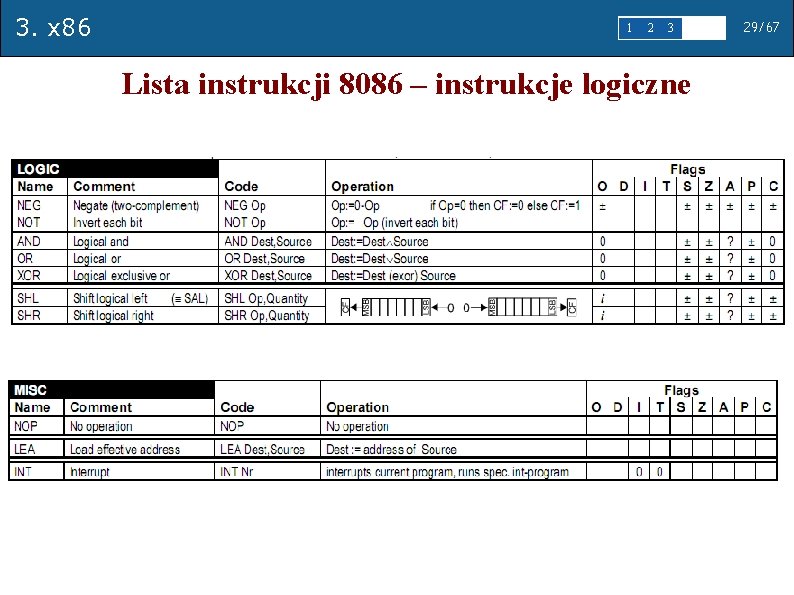

3. x 86 1 2 3 4 Lista instrukcji 8086 – instrukcje logiczne 5 29/67

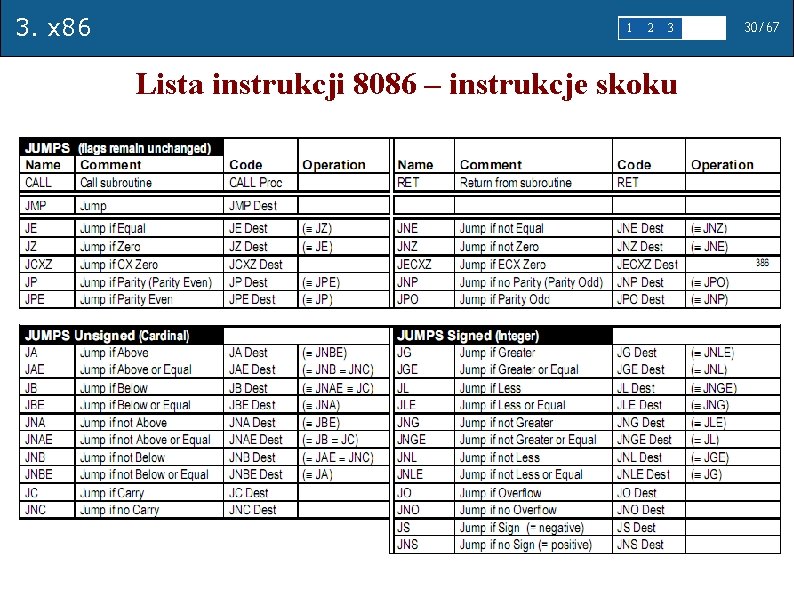

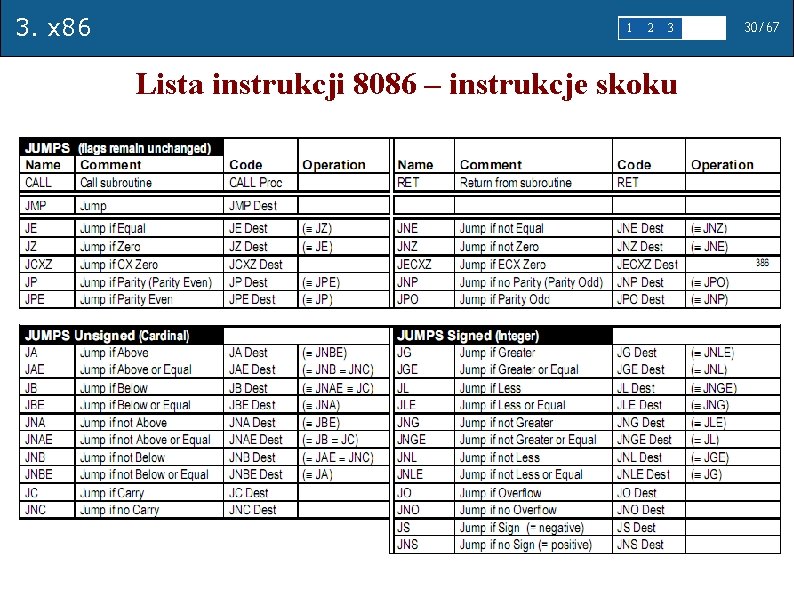

3. x 86 1 2 3 Lista instrukcji 8086 – instrukcje skoku 4 5 30/67

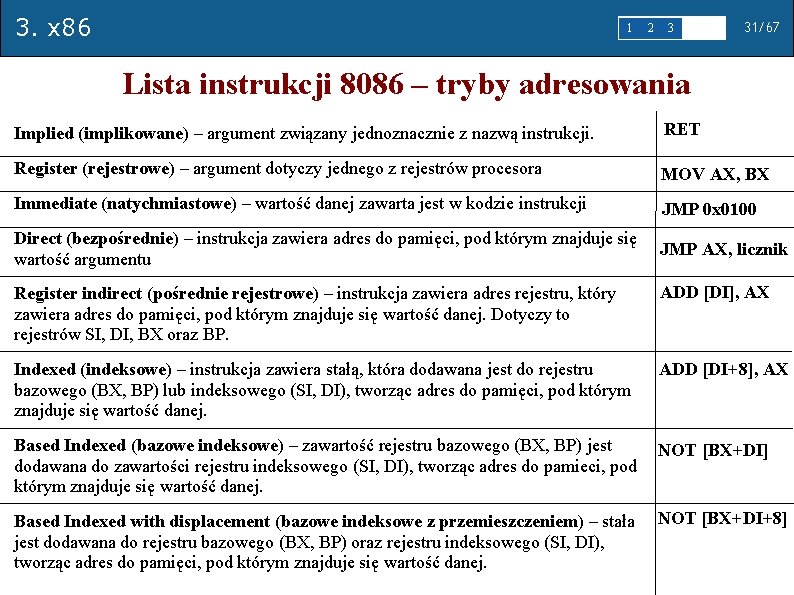

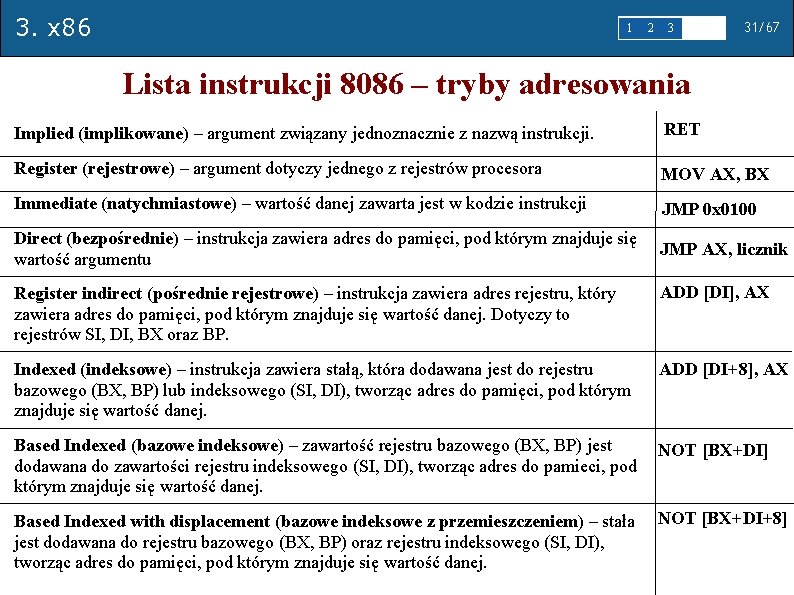

3. x 86 1 2 3 4 5 31/67 Lista instrukcji 8086 – tryby adresowania Implied (implikowane) – argument związany jednoznacznie z nazwą instrukcji. RET Register (rejestrowe) – argument dotyczy jednego z rejestrów procesora MOV AX, BX Immediate (natychmiastowe) – wartość danej zawarta jest w kodzie instrukcji JMP 0 x 0100 Direct (bezpośrednie) – instrukcja zawiera adres do pamięci, pod którym znajduje się wartość argumentu JMP AX, licznik Register indirect (pośrednie rejestrowe) – instrukcja zawiera adres rejestru, który zawiera adres do pamięci, pod którym znajduje się wartość danej. Dotyczy to rejestrów SI, DI, BX oraz BP. ADD [DI], AX Indexed (indeksowe) – instrukcja zawiera stałą, która dodawana jest do rejestru bazowego (BX, BP) lub indeksowego (SI, DI), tworząc adres do pamięci, pod którym znajduje się wartość danej. ADD [DI+8], AX Based Indexed (bazowe indeksowe) – zawartość rejestru bazowego (BX, BP) jest NOT [BX+DI] dodawana do zawartości rejestru indeksowego (SI, DI), tworząc adres do pamieci, pod którym znajduje się wartość danej. Based Indexed with displacement (bazowe indeksowe z przemieszczeniem) – stała jest dodawana do rejestru bazowego (BX, BP) oraz rejestru indeksowego (SI, DI), tworząc adres do pamięci, pod którym znajduje się wartość danej. NOT [BX+DI+8]

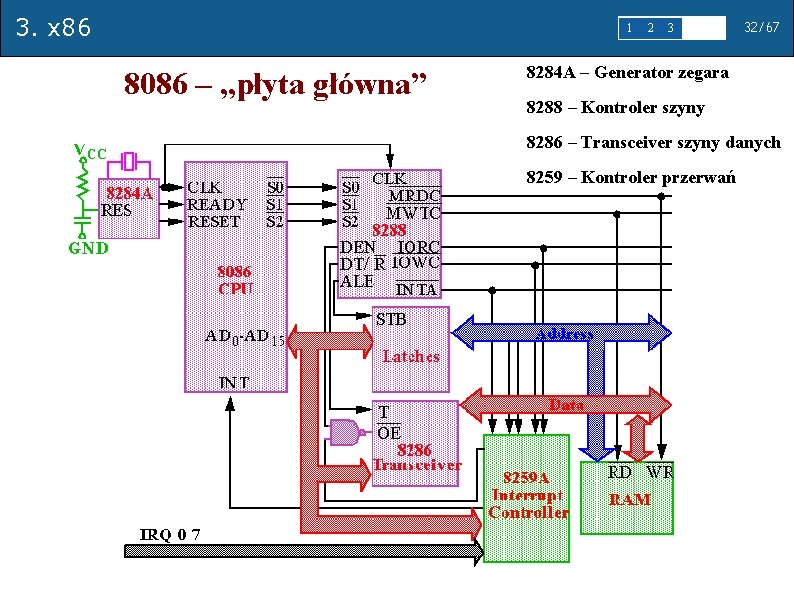

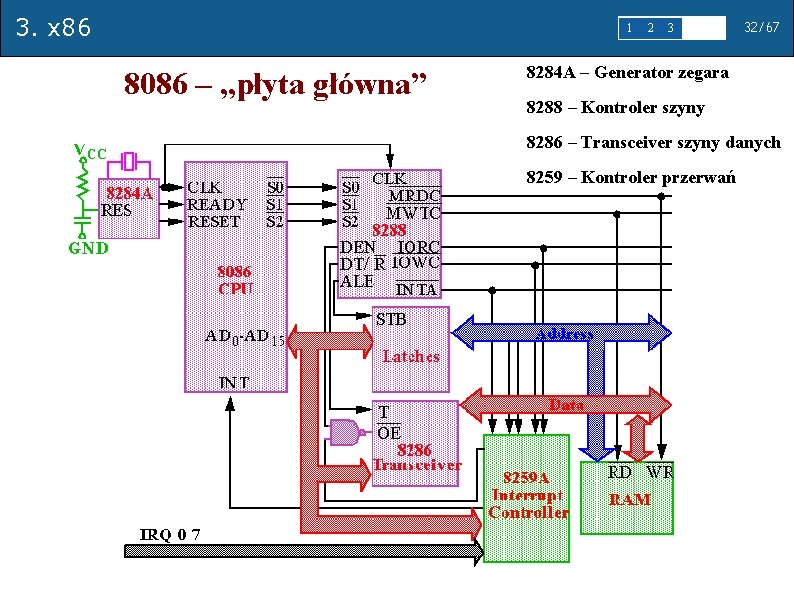

3. x 86 1 8086 – „płyta główna” 2 3 4 5 32/67 8284 A – Generator zegara 8288 – Kontroler szyny 8286 – Transceiver szyny danych 8259 – Kontroler przerwań

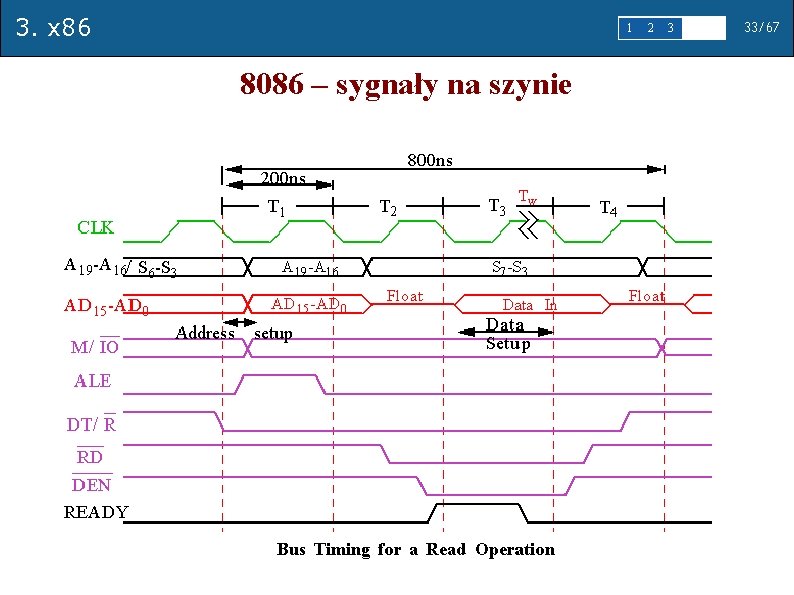

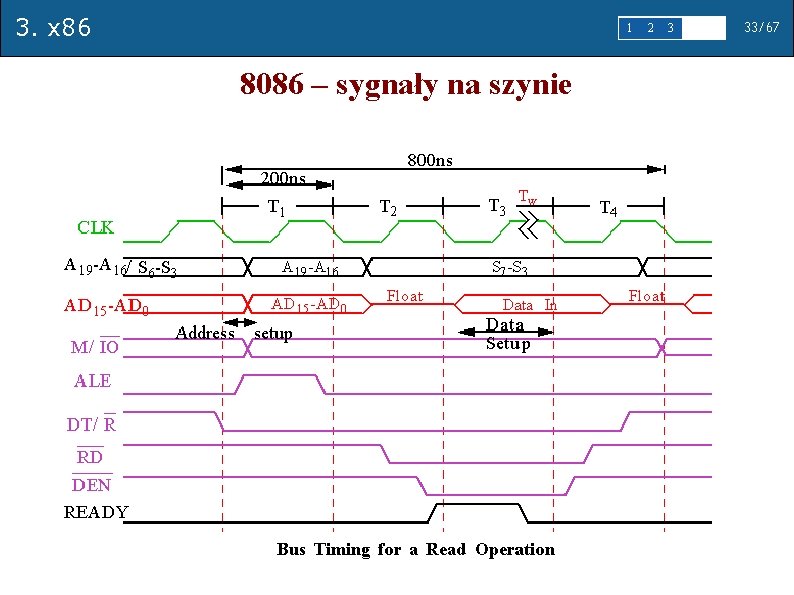

3. x 86 1 8086 – sygnały na szynie 2 3 4 5 33/67

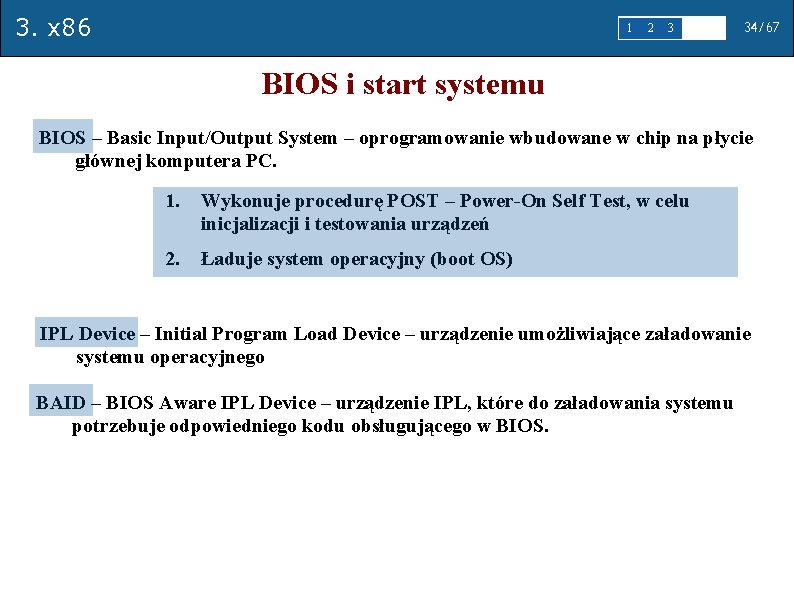

3. x 86 1 2 3 4 5 34/67 BIOS i start systemu BIOS – Basic Input/Output System – oprogramowanie wbudowane w chip na płycie głównej komputera PC. 1. Wykonuje procedurę POST – Power-On Self Test, w celu inicjalizacji i testowania urządzeń 2. Ładuje system operacyjny (boot OS) IPL Device – Initial Program Load Device – urządzenie umożliwiające załadowanie systemu operacyjnego BAID – BIOS Aware IPL Device – urządzenie IPL, które do załadowania systemu potrzebuje odpowiedniego kodu obsługującego w BIOS.

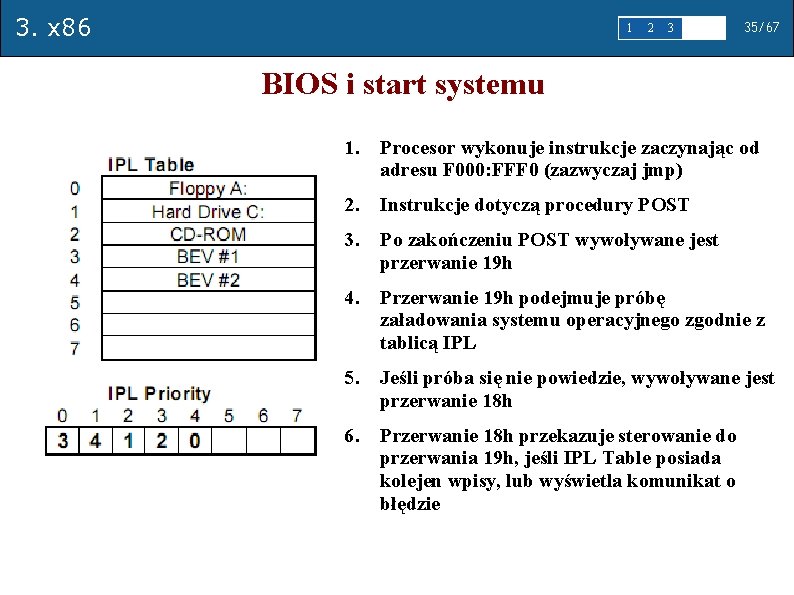

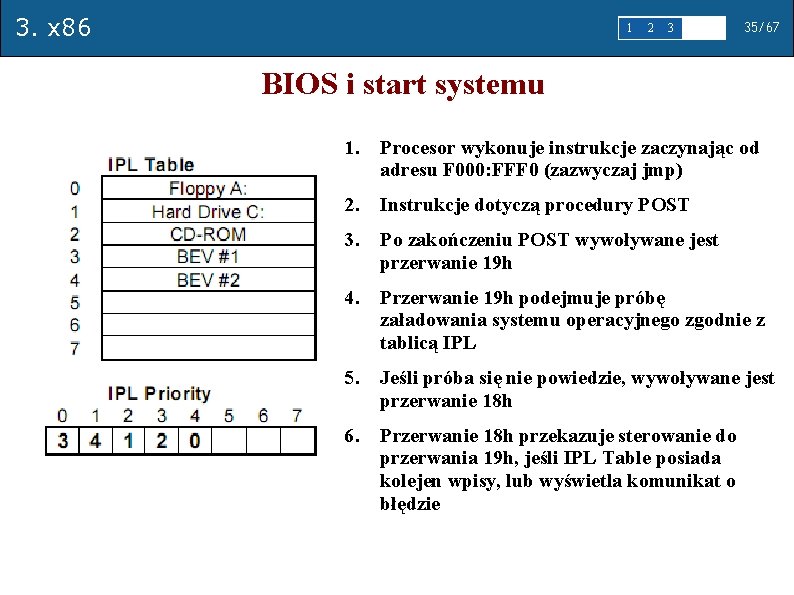

3. x 86 1 2 3 4 5 35/67 BIOS i start systemu 1. Procesor wykonuje instrukcje zaczynając od adresu F 000: FFF 0 (zazwyczaj jmp) 2. Instrukcje dotyczą procedury POST 3. Po zakończeniu POST wywoływane jest przerwanie 19 h 4. Przerwanie 19 h podejmuje próbę załadowania systemu operacyjnego zgodnie z tablicą IPL 5. Jeśli próba się nie powiedzie, wywoływane jest przerwanie 18 h 6. Przerwanie 18 h przekazuje sterowanie do przerwania 19 h, jeśli IPL Table posiada kolejen wpisy, lub wyświetla komunikat o błędzie

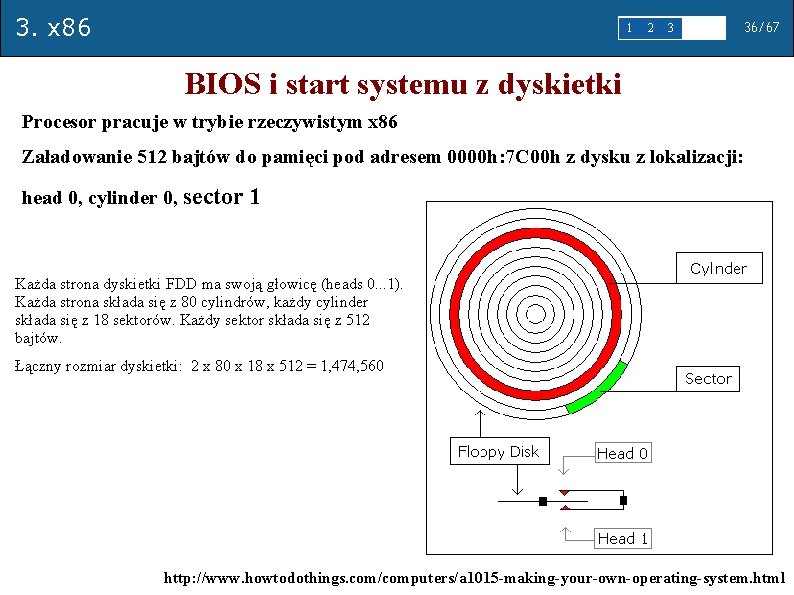

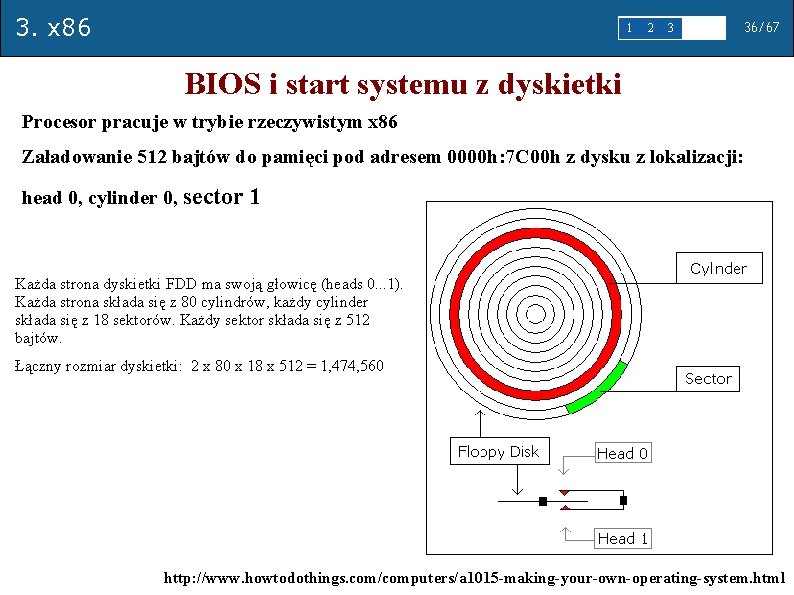

3. x 86 1 2 3 4 5 36/67 BIOS i start systemu z dyskietki Procesor pracuje w trybie rzeczywistym x 86 Załadowanie 512 bajtów do pamięci pod adresem 0000 h: 7 C 00 h z dysku z lokalizacji: head 0, cylinder 0, sector 1 Każda strona dyskietki FDD ma swoją głowicę (heads 0. . . 1). Każda strona składa się z 80 cylindrów, każdy cylinder składa się z 18 sektorów. Każdy sektor składa się z 512 bajtów. Łączny rozmiar dyskietki: 2 x 80 x 18 x 512 = 1, 474, 560 http: //www. howtodothings. com/computers/a 1015 -making-your-own-operating-system. html

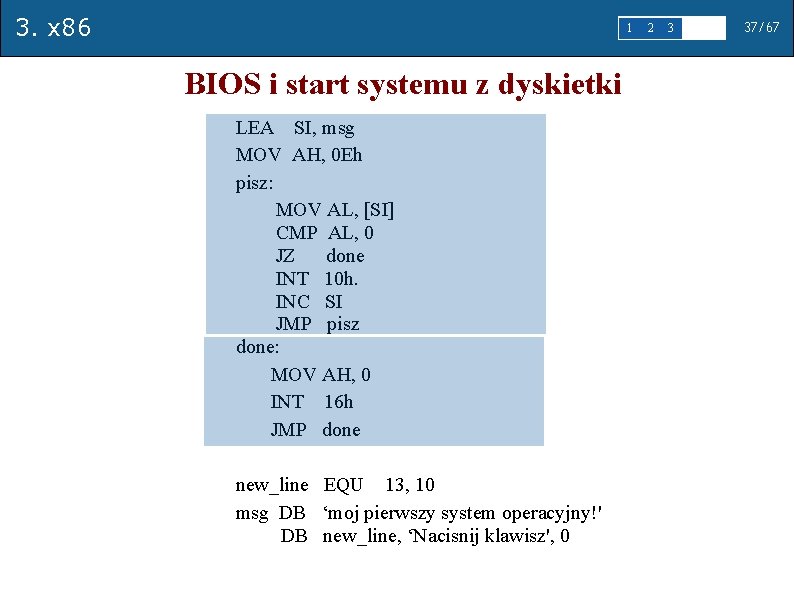

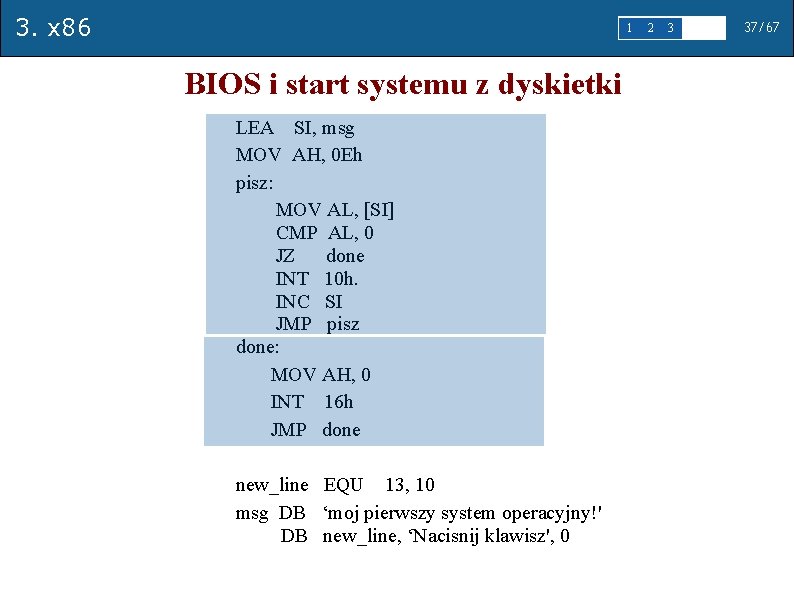

3. x 86 1 BIOS i start systemu z dyskietki LEA SI, msg MOV AH, 0 Eh pisz: MOV AL, [SI] CMP AL, 0 JZ done INT 10 h. INC SI JMP pisz done: MOV AH, 0 INT 16 h JMP done new_line EQU 13, 10 msg DB ‘moj pierwszy system operacyjny!' DB new_line, ‘Nacisnij klawisz', 0 2 3 4 5 37/67

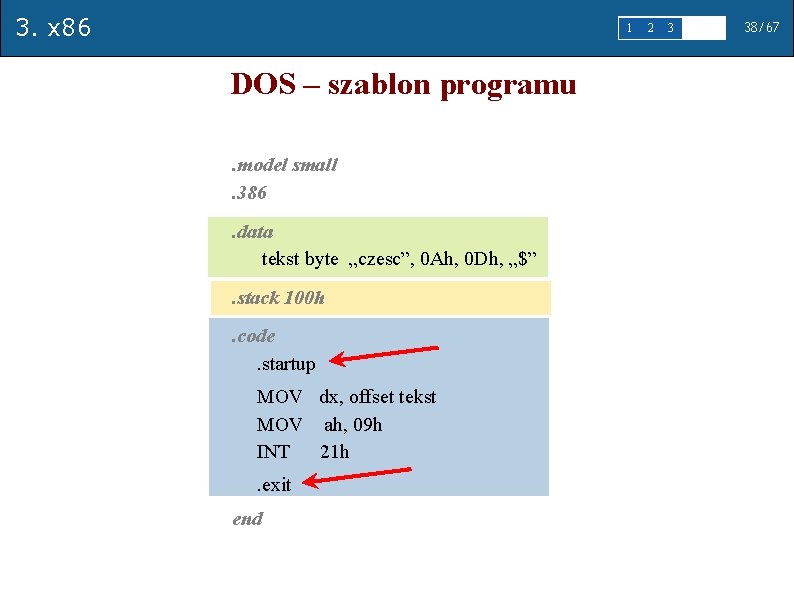

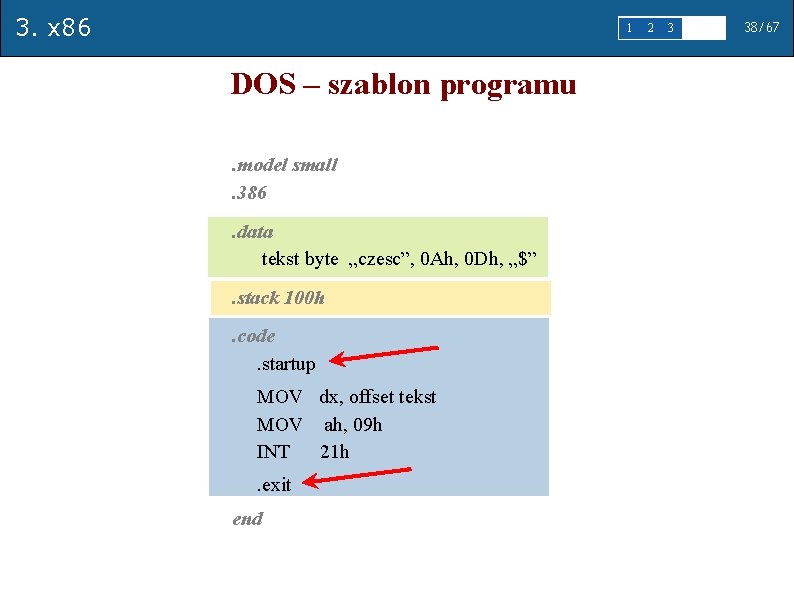

3. x 86 1 DOS – szablon programu. model small. 386. data tekst byte „czesc”, 0 Ah, 0 Dh, „$”. stack 100 h. code . startup MOV dx, offset tekst MOV ah, 09 h INT 21 h . exit end 2 3 4 5 38/67

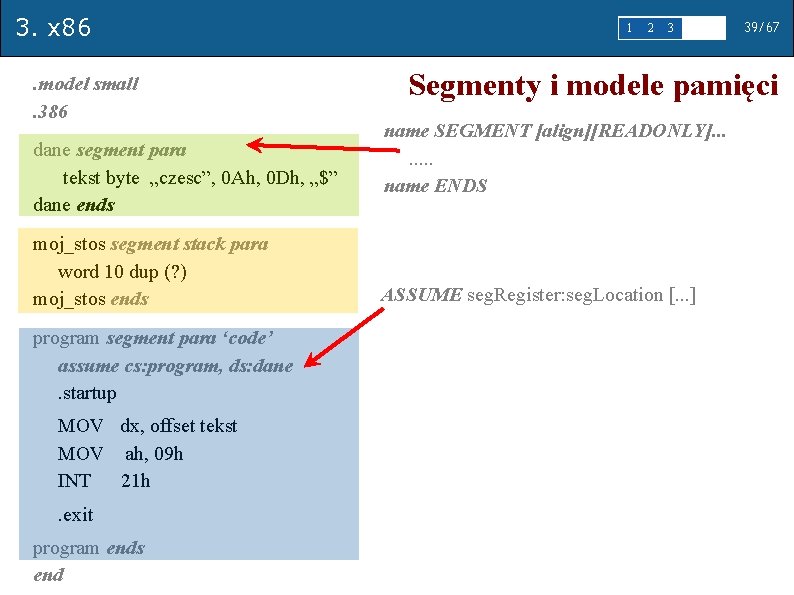

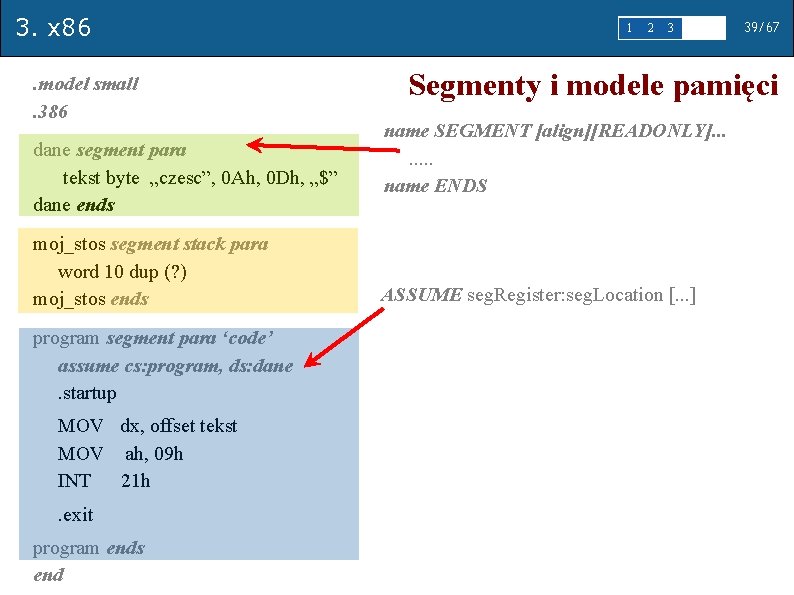

3. x 86. model small. 386 dane segment para tekst byte „czesc”, 0 Ah, 0 Dh, „$” dane ends moj_stos segment stack para word 10 dup (? ) moj_stos ends program segment para ‘code’ assume cs: program, ds: dane . startup MOV dx, offset tekst MOV ah, 09 h INT 21 h . exit program ends end 1 2 3 4 5 39/67 Segmenty i modele pamięci name SEGMENT [align][READONLY]. . . . name ENDS ASSUME seg. Register: seg. Location [. . . ]

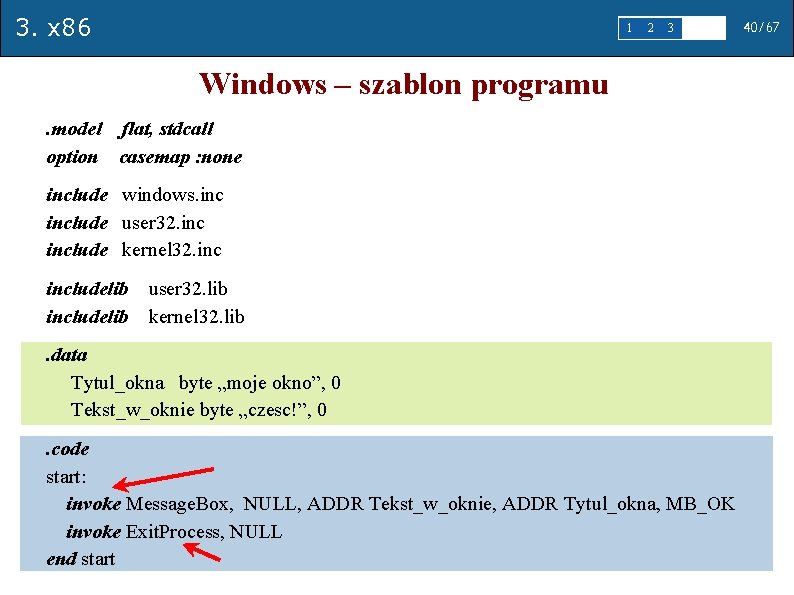

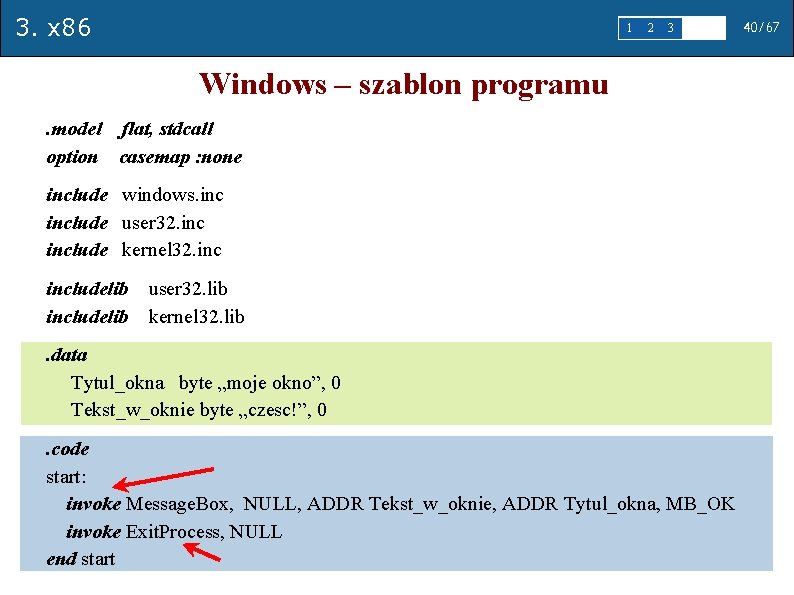

3. x 86 1 2 3 4 5 Windows – szablon programu. model flat, stdcall option casemap : none include windows. include user 32. include kernel 32. includelib user 32. lib kernel 32. lib . data Tytul_okna byte „moje okno”, 0 Tekst_w_oknie byte „czesc!”, 0. code start: invoke Message. Box, NULL, ADDR Tekst_w_oknie, ADDR Tytul_okna, MB_OK invoke Exit. Process, NULL end start 40/67

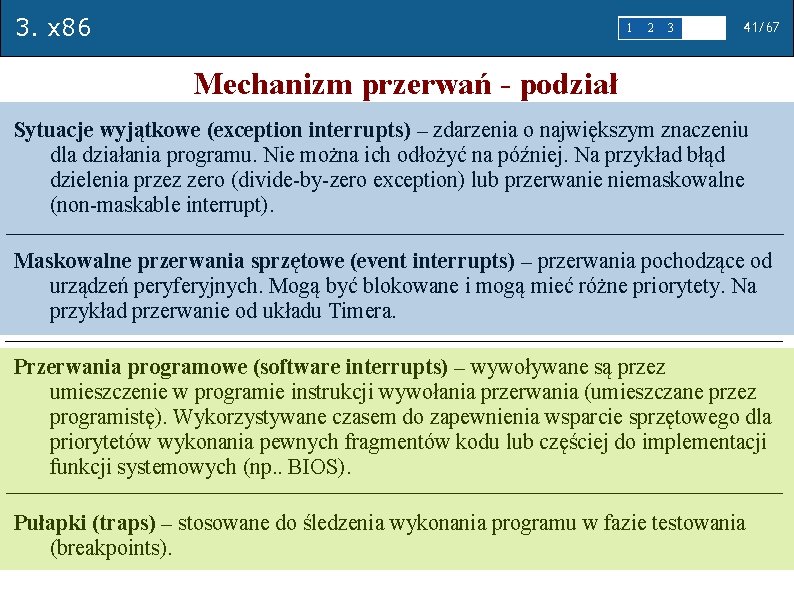

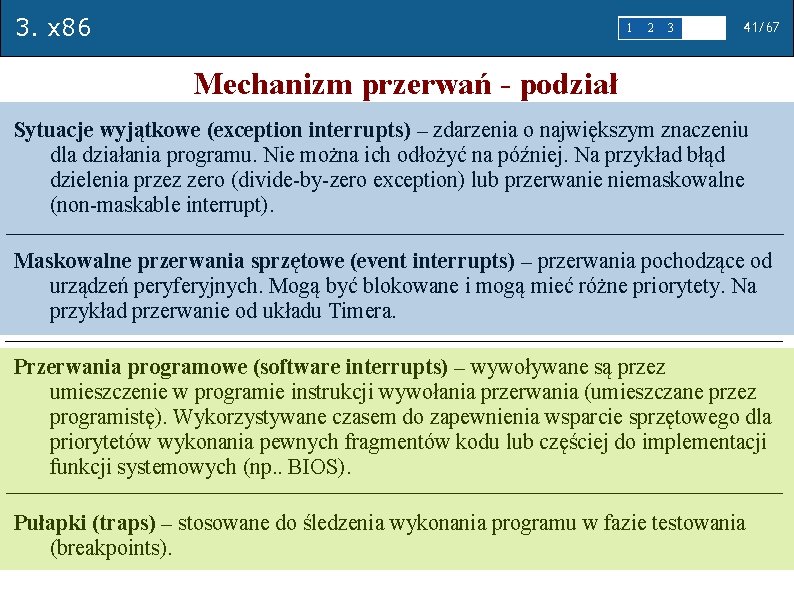

3. x 86 1 2 3 4 5 41/67 Mechanizm przerwań - podział Sytuacje wyjątkowe (exception interrupts) – zdarzenia o największym znaczeniu dla działania programu. Nie można ich odłożyć na później. Na przykład błąd dzielenia przez zero (divide-by-zero exception) lub przerwanie niemaskowalne (non-maskable interrupt). Maskowalne przerwania sprzętowe (event interrupts) – przerwania pochodzące od urządzeń peryferyjnych. Mogą być blokowane i mogą mieć różne priorytety. Na przykład przerwanie od układu Timera. Przerwania programowe (software interrupts) – wywoływane są przez umieszczenie w programie instrukcji wywołania przerwania (umieszczane przez programistę). Wykorzystywane czasem do zapewnienia wsparcie sprzętowego dla priorytetów wykonania pewnych fragmentów kodu lub częściej do implementacji funkcji systemowych (np. . BIOS). Pułapki (traps) – stosowane do śledzenia wykonania programu w fazie testowania (breakpoints).

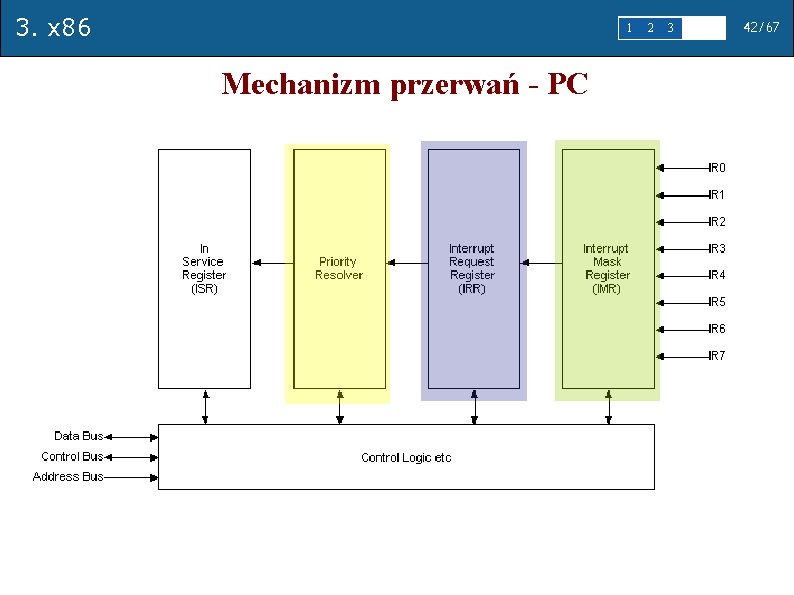

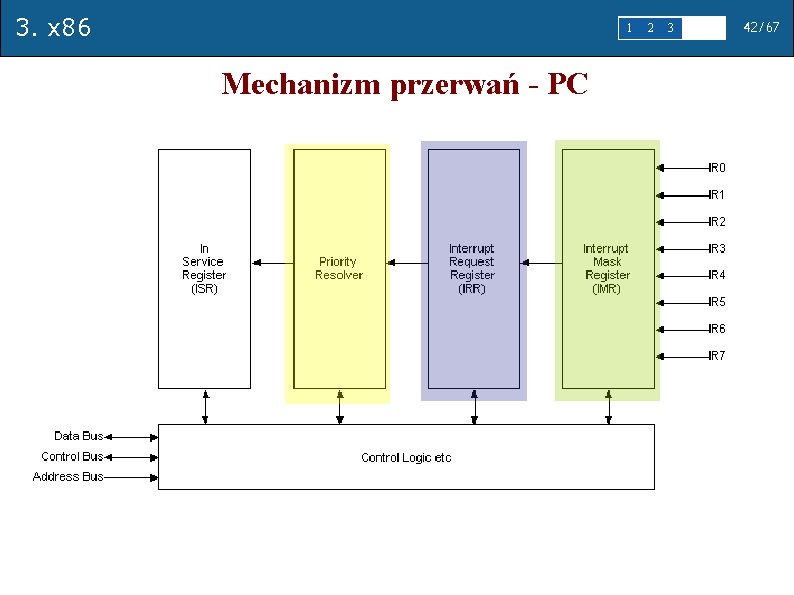

3. x 86 1 Mechanizm przerwań - PC 2 3 4 5 42/67

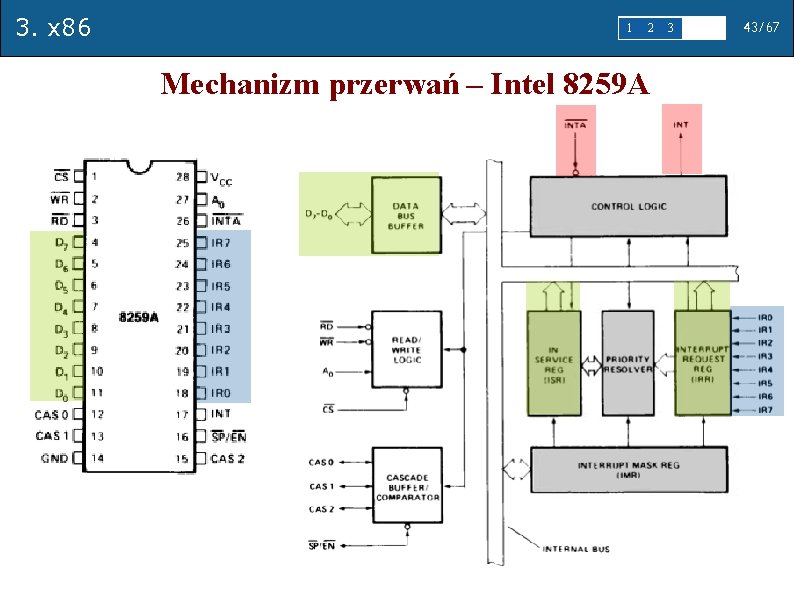

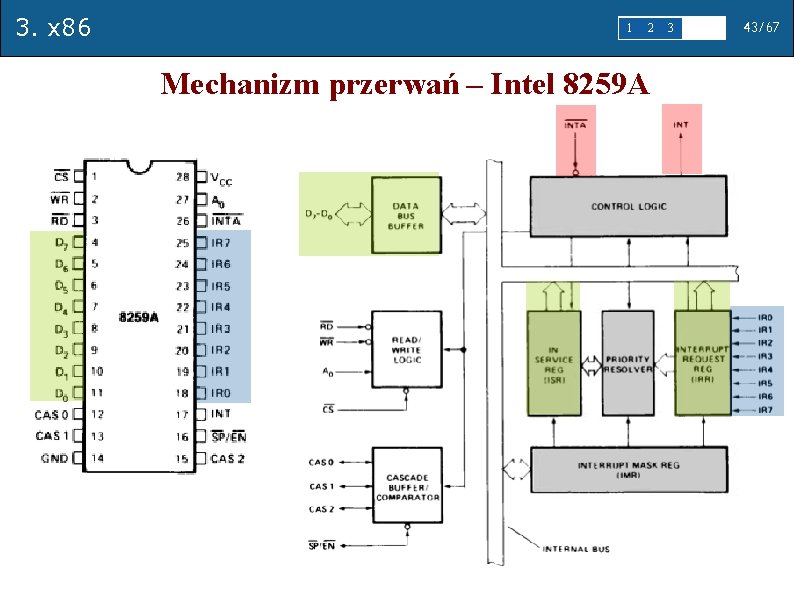

3. x 86 1 2 Mechanizm przerwań – Intel 8259 A 3 4 5 43/67

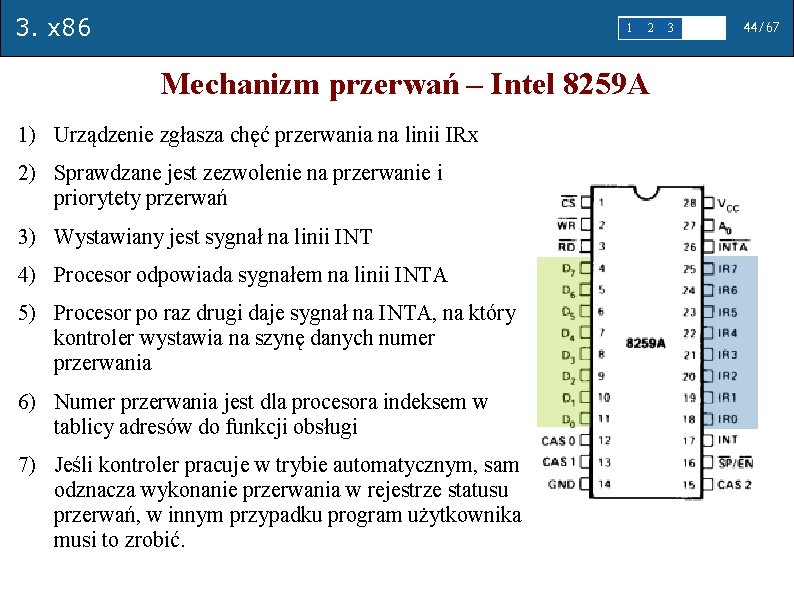

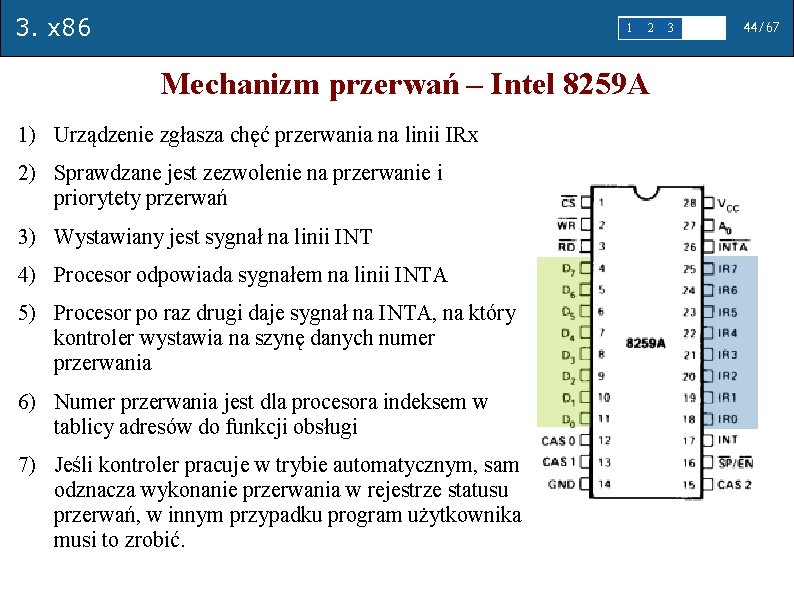

3. x 86 1 2 Mechanizm przerwań – Intel 8259 A 1) Urządzenie zgłasza chęć przerwania na linii IRx 2) Sprawdzane jest zezwolenie na przerwanie i priorytety przerwań 3) Wystawiany jest sygnał na linii INT 4) Procesor odpowiada sygnałem na linii INTA 5) Procesor po raz drugi daje sygnał na INTA, na który kontroler wystawia na szynę danych numer przerwania 6) Numer przerwania jest dla procesora indeksem w tablicy adresów do funkcji obsługi 7) Jeśli kontroler pracuje w trybie automatycznym, sam odznacza wykonanie przerwania w rejestrze statusu przerwań, w innym przypadku program użytkownika musi to zrobić. 3 4 5 44/67

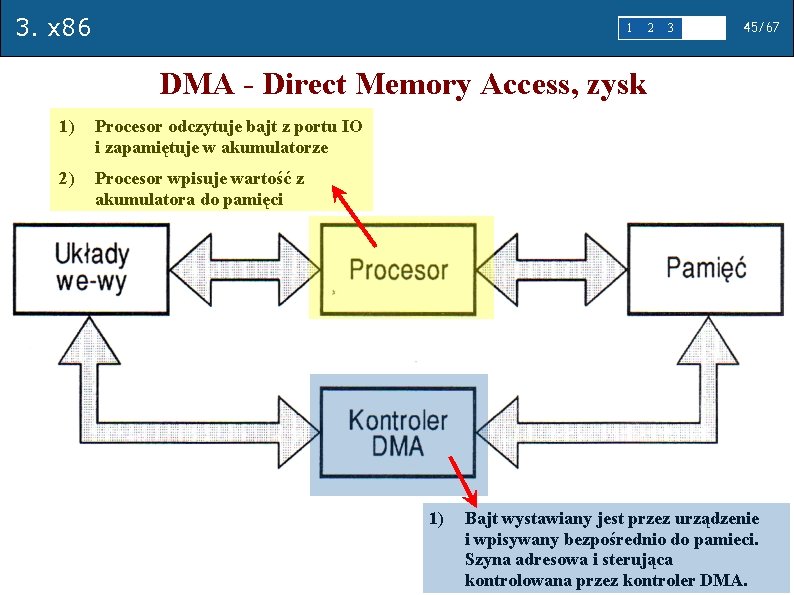

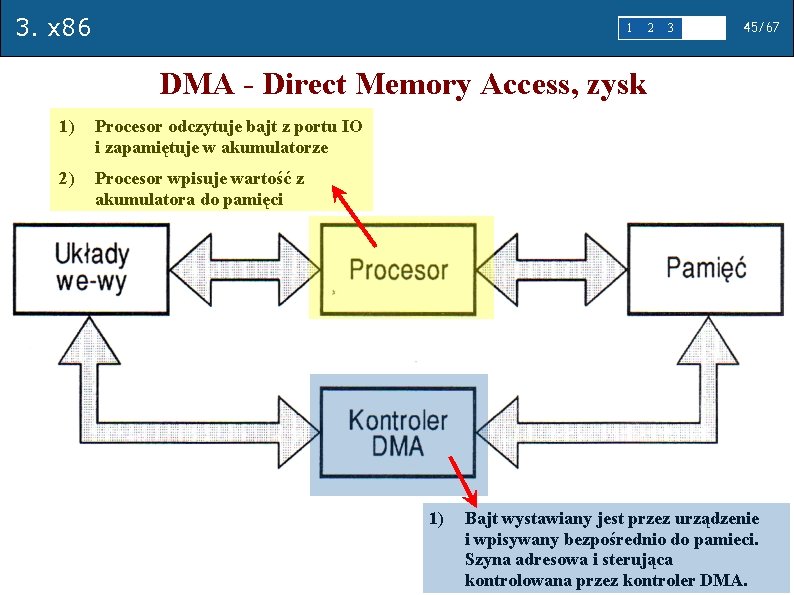

3. x 86 1 2 3 4 5 45/67 DMA - Direct Memory Access, zysk 1) Procesor odczytuje bajt z portu IO i zapamiętuje w akumulatorze 2) Procesor wpisuje wartość z akumulatora do pamięci 1) Bajt wystawiany jest przez urządzenie i wpisywany bezpośrednio do pamieci. Szyna adresowa i sterująca kontrolowana przez kontroler DMA.

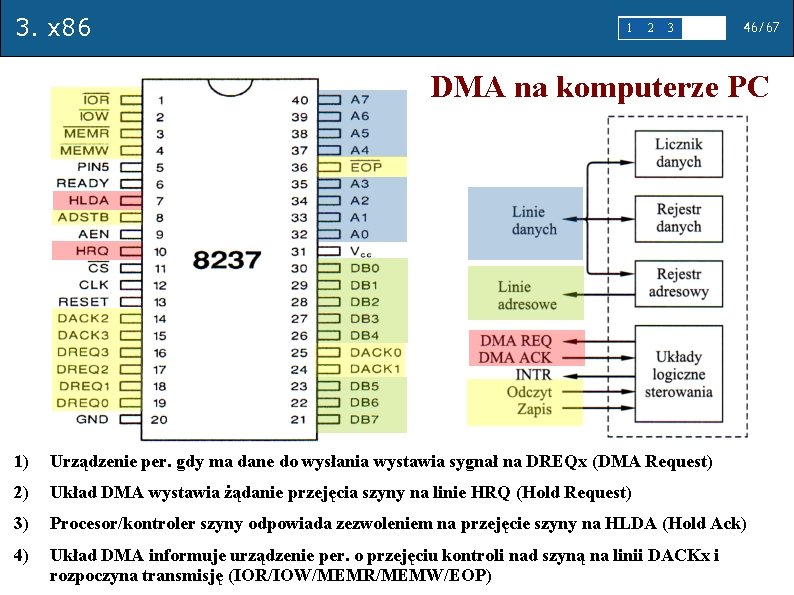

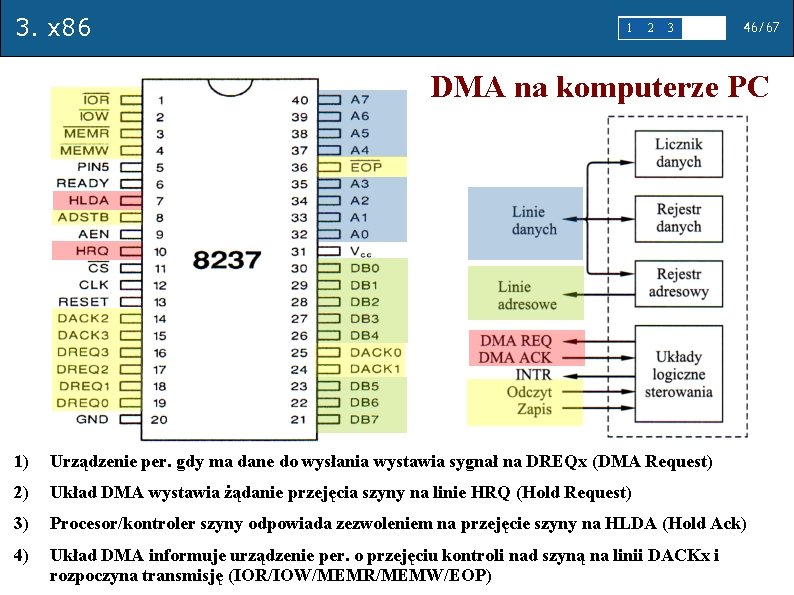

3. x 86 1 2 3 4 5 46/67 DMA na komputerze PC 1) Urządzenie per. gdy ma dane do wysłania wystawia sygnał na DREQx (DMA Request) 2) Układ DMA wystawia żądanie przejęcia szyny na linie HRQ (Hold Request) 3) Procesor/kontroler szyny odpowiada zezwoleniem na przejęcie szyny na HLDA (Hold Ack) 4) Układ DMA informuje urządzenie per. o przejęciu kontroli nad szyną na linii DACKx i rozpoczyna transmisję (IOR/IOW/MEMR/MEMW/EOP)

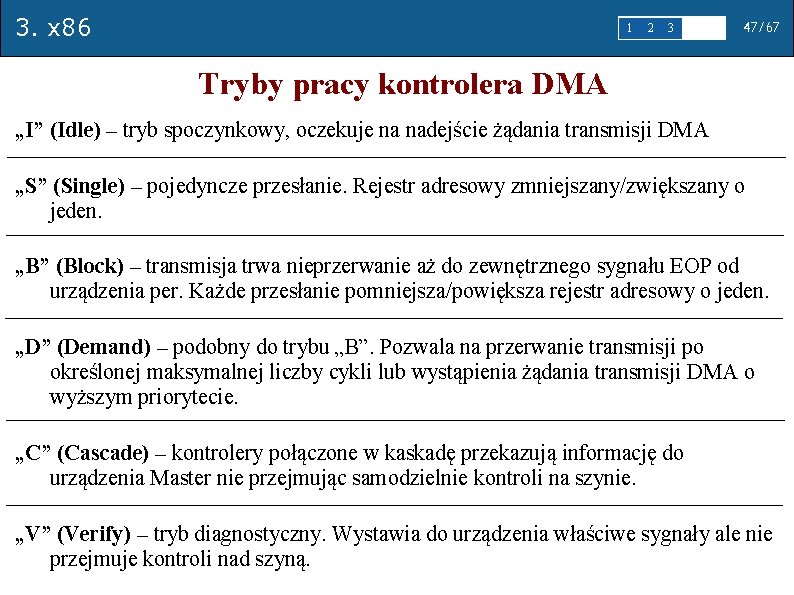

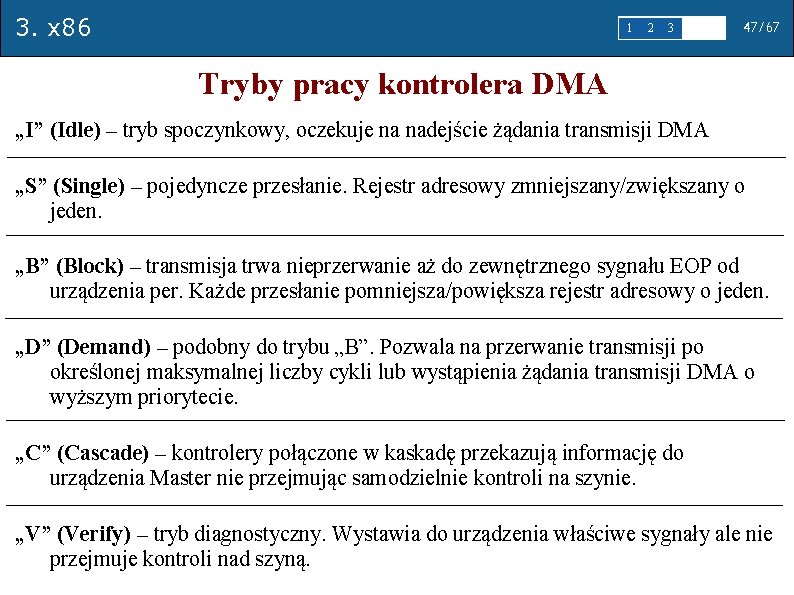

3. x 86 1 2 3 4 5 47/67 Tryby pracy kontrolera DMA „I” (Idle) – tryb spoczynkowy, oczekuje na nadejście żądania transmisji DMA „S” (Single) – pojedyncze przesłanie. Rejestr adresowy zmniejszany/zwiększany o jeden. „B” (Block) – transmisja trwa nieprzerwanie aż do zewnętrznego sygnału EOP od urządzenia per. Każde przesłanie pomniejsza/powiększa rejestr adresowy o jeden. „D” (Demand) – podobny do trybu „B”. Pozwala na przerwanie transmisji po określonej maksymalnej liczby cykli lub wystąpienia żądania transmisji DMA o wyższym priorytecie. „C” (Cascade) – kontrolery połączone w kaskadę przekazują informację do urządzenia Master nie przejmując samodzielnie kontroli na szynie. „V” (Verify) – tryb diagnostyczny. Wystawia do urządzenia właściwe sygnały ale nie przejmuje kontroli nad szyną.

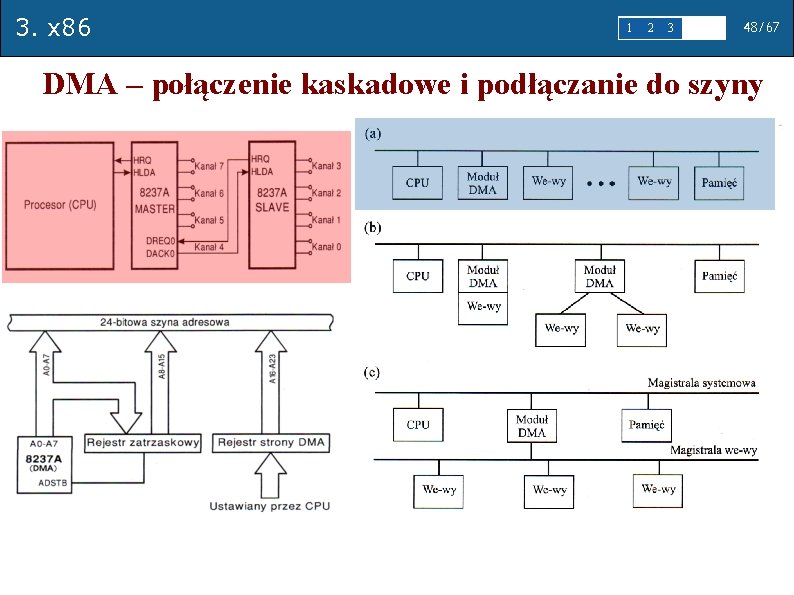

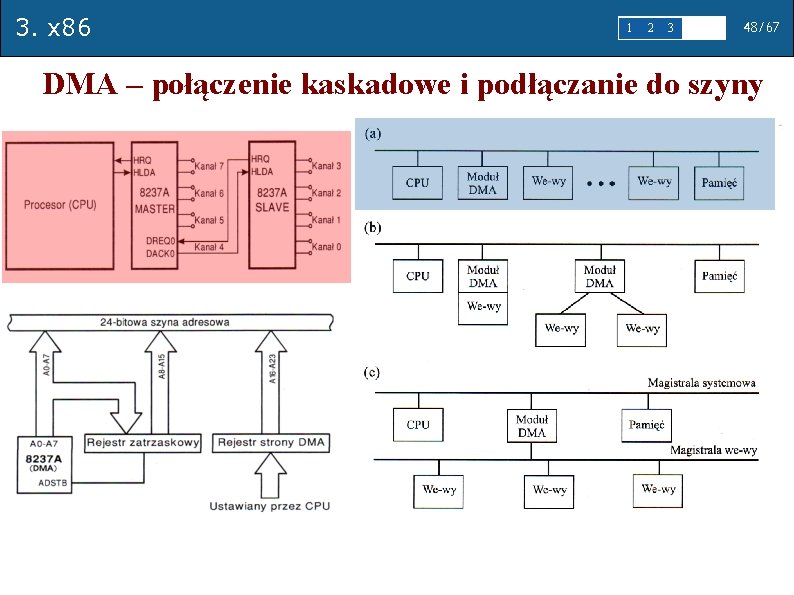

3. x 86 1 2 3 4 5 48/67 DMA – połączenie kaskadowe i podłączanie do szyny

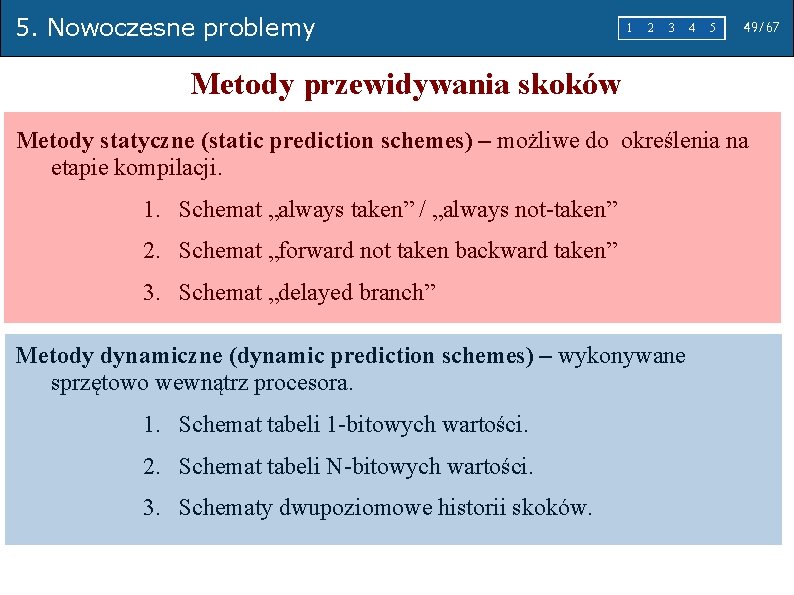

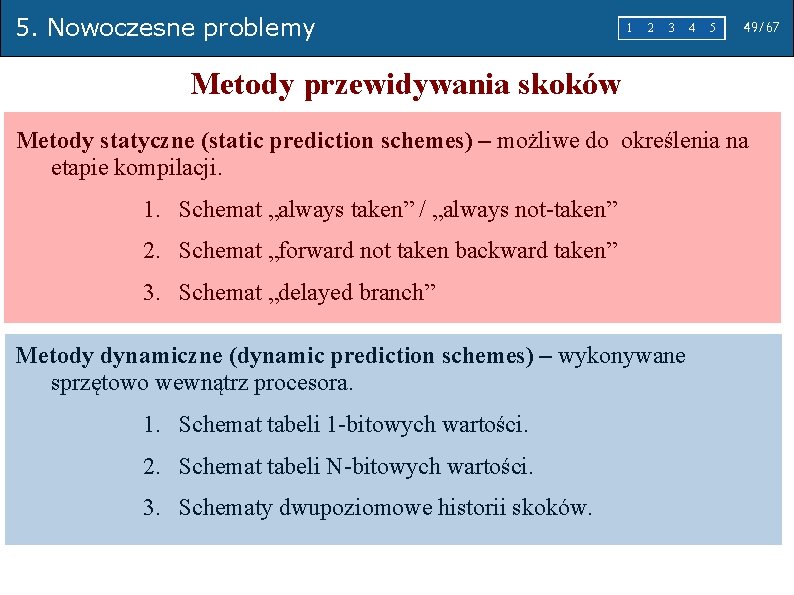

5. Nowoczesne problemy 1 2 3 4 5 49/67 Metody przewidywania skoków Metody statyczne (static prediction schemes) – możliwe do określenia na etapie kompilacji. 1. Schemat „always taken” / „always not-taken” 2. Schemat „forward not taken backward taken” 3. Schemat „delayed branch” Metody dynamiczne (dynamic prediction schemes) – wykonywane sprzętowo wewnątrz procesora. 1. Schemat tabeli 1 -bitowych wartości. 2. Schemat tabeli N-bitowych wartości. 3. Schematy dwupoziomowe historii skoków.

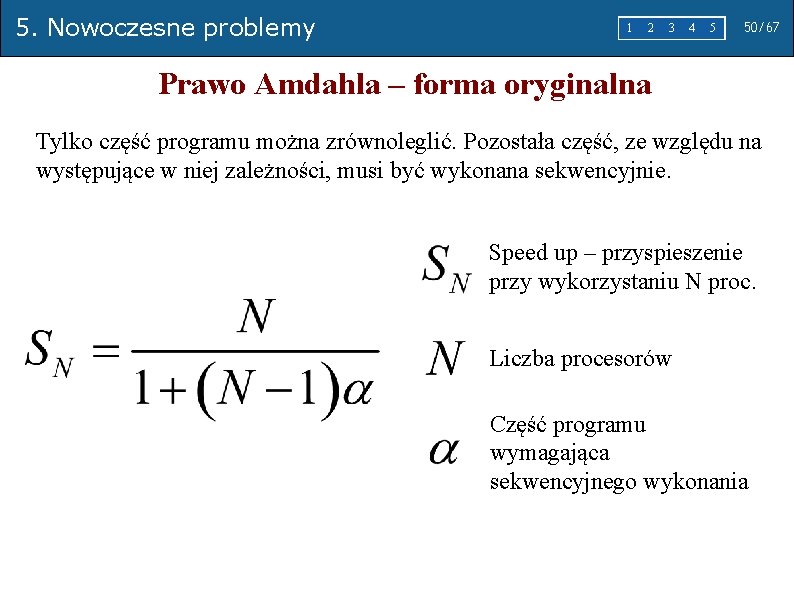

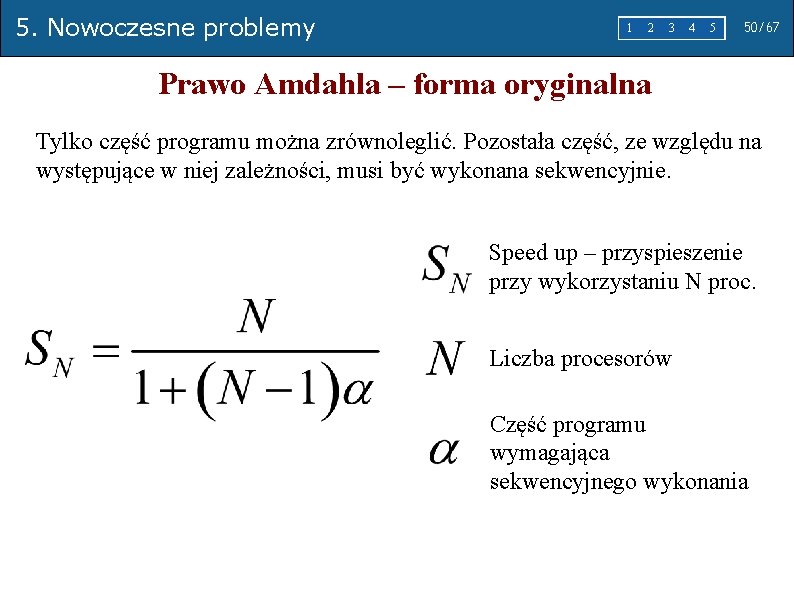

5. Nowoczesne problemy 1 2 3 4 5 50/67 Prawo Amdahla – forma oryginalna Tylko część programu można zrównoleglić. Pozostała część, ze względu na występujące w niej zależności, musi być wykonana sekwencyjnie. Speed up – przyspieszenie przy wykorzystaniu N proc. Liczba procesorów Część programu wymagająca sekwencyjnego wykonania

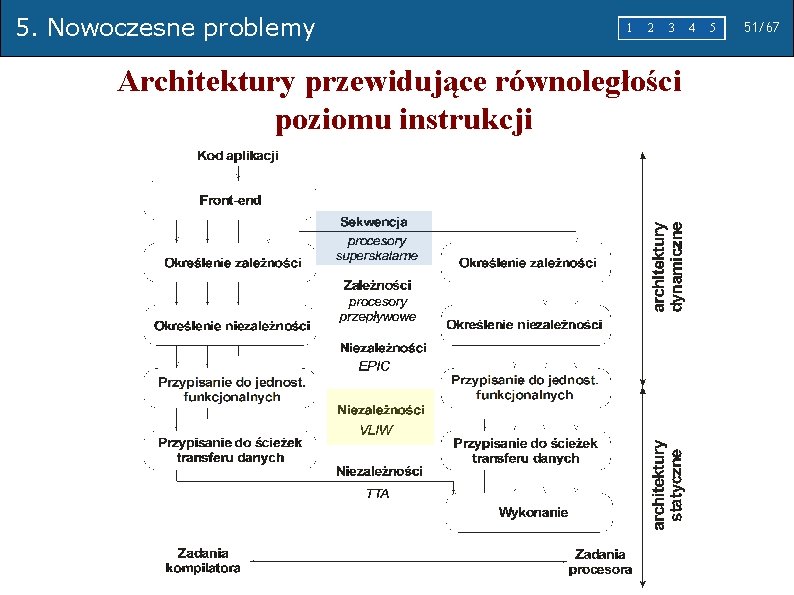

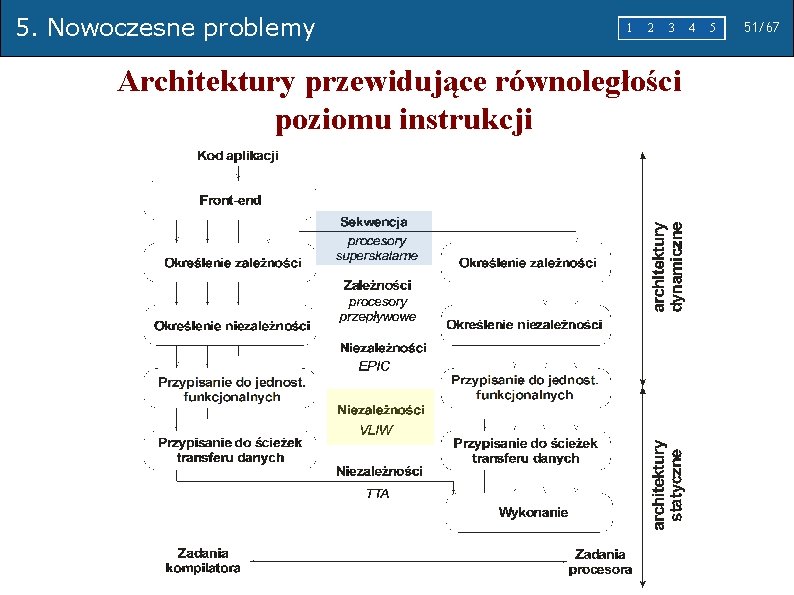

5. Nowoczesne problemy 1 2 3 Architektury przewidujące równoległości poziomu instrukcji 4 5 51/67

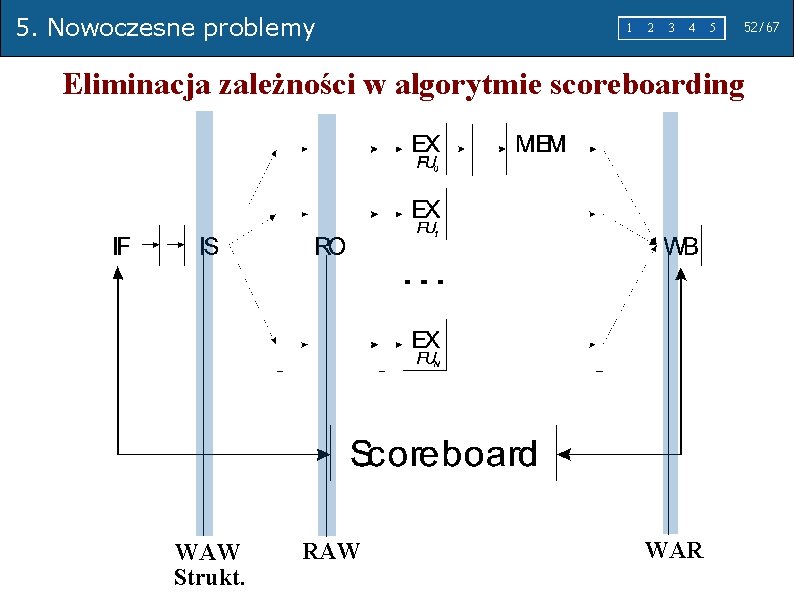

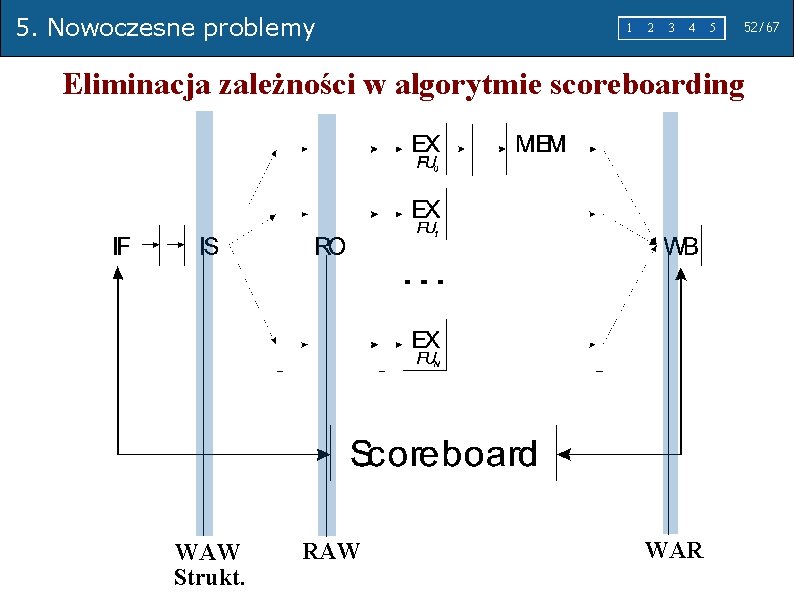

5. Nowoczesne problemy 1 2 3 4 5 52/67 Eliminacja zależności w algorytmie scoreboarding WAW Strukt. RAW WAR

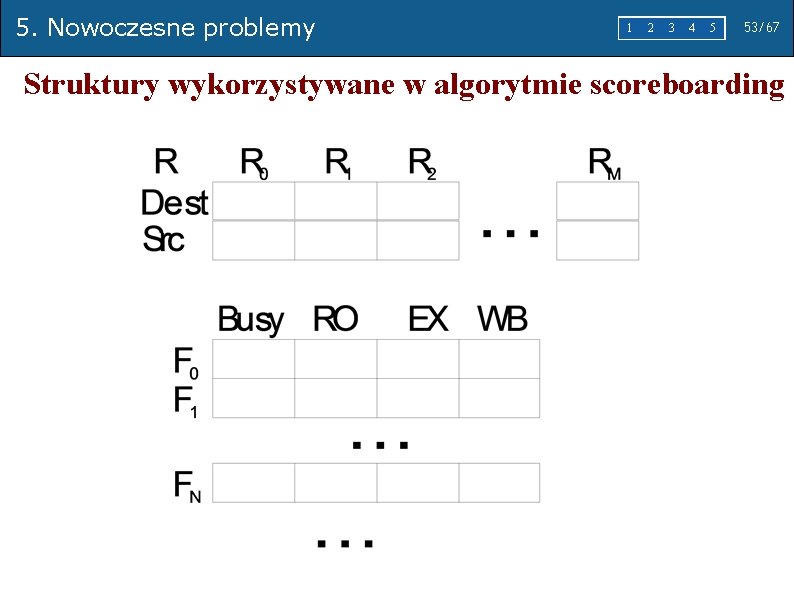

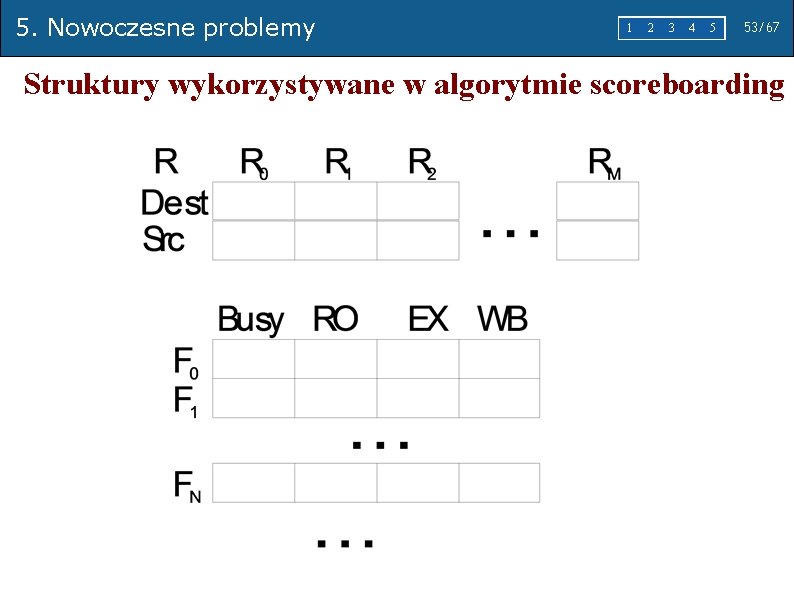

5. Nowoczesne problemy 1 2 3 4 5 53/67 Struktury wykorzystywane w algorytmie scoreboarding

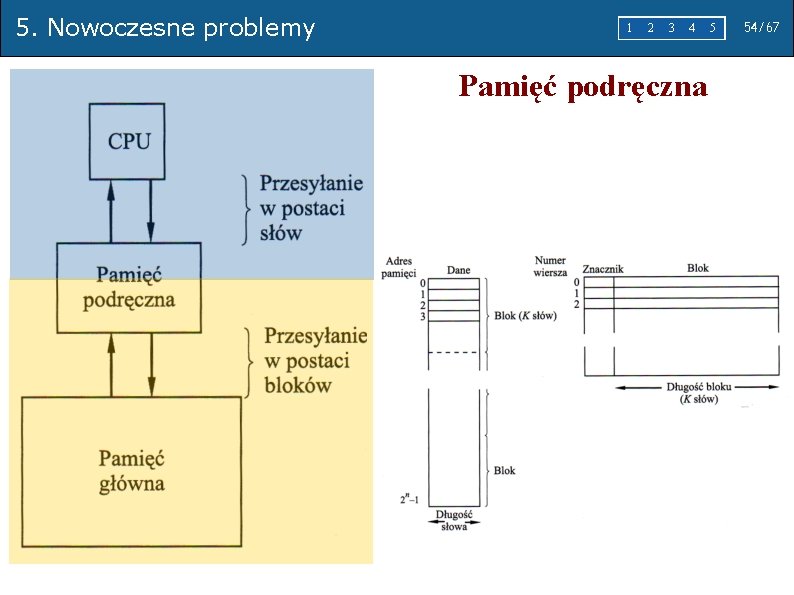

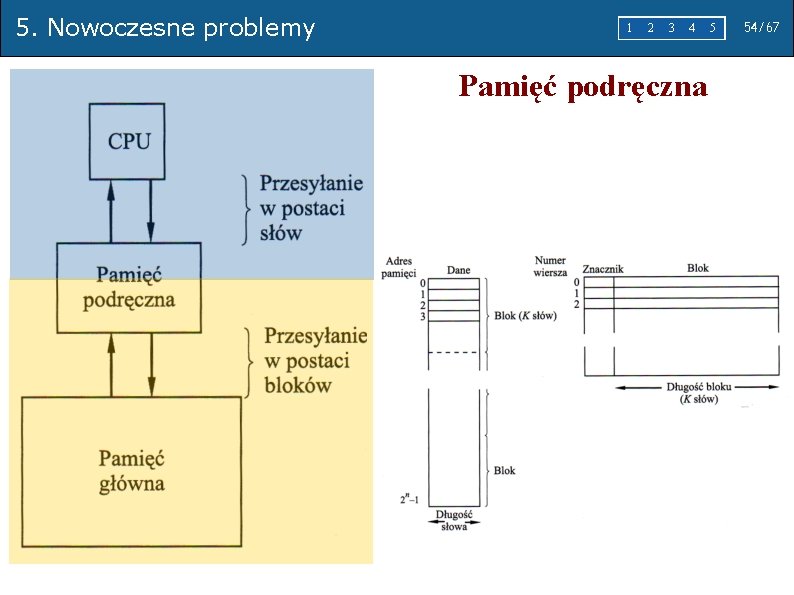

5. Nowoczesne problemy 1 2 3 4 Pamięć podręczna 5 54/67

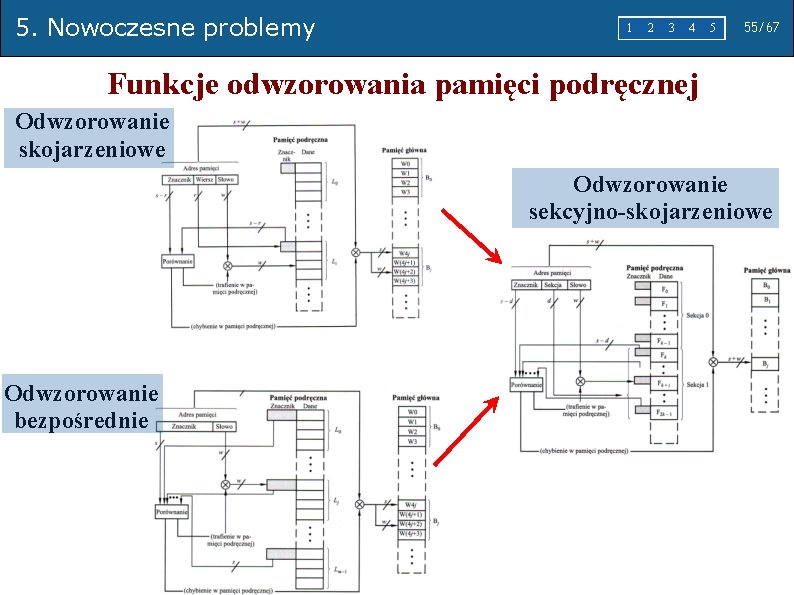

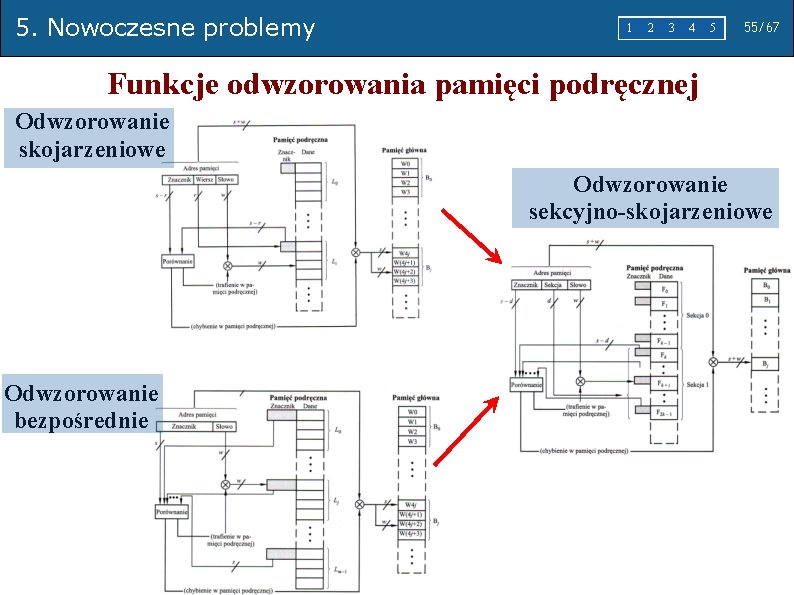

5. Nowoczesne problemy 1 2 3 4 5 55/67 Funkcje odwzorowania pamięci podręcznej Odwzorowanie skojarzeniowe Odwzorowanie sekcyjno-skojarzeniowe Odwzorowanie bezpośrednie

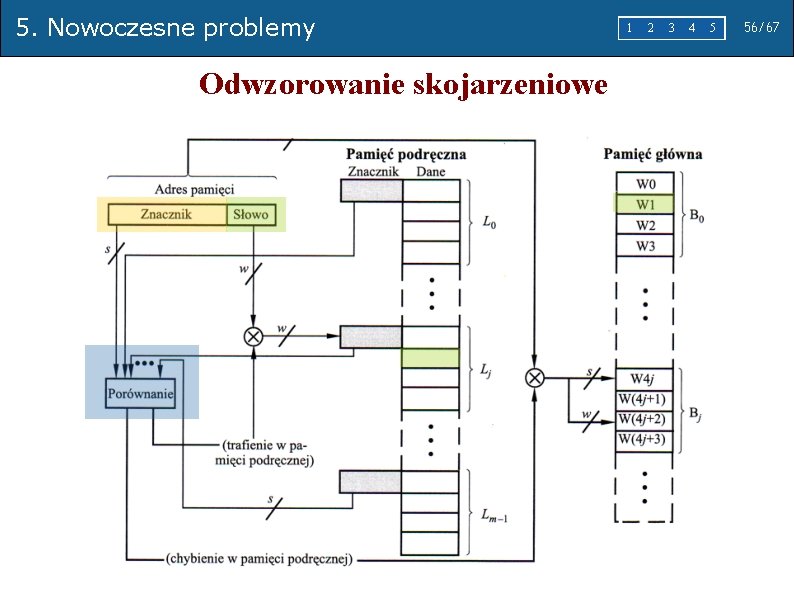

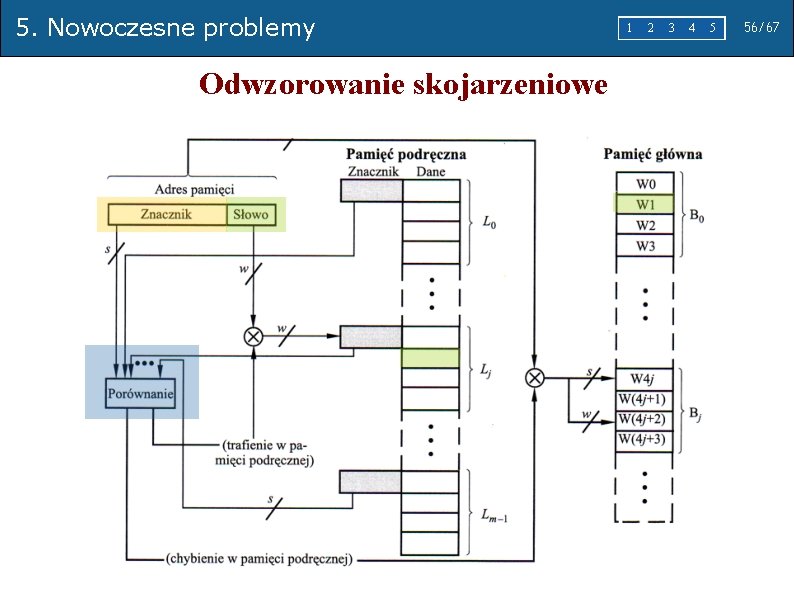

5. Nowoczesne problemy Odwzorowanie skojarzeniowe 1 2 3 4 5 56/67

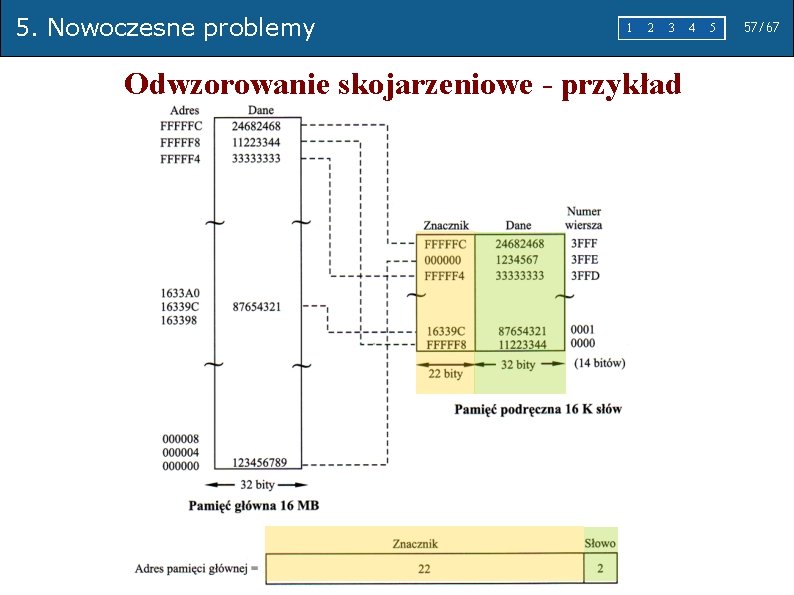

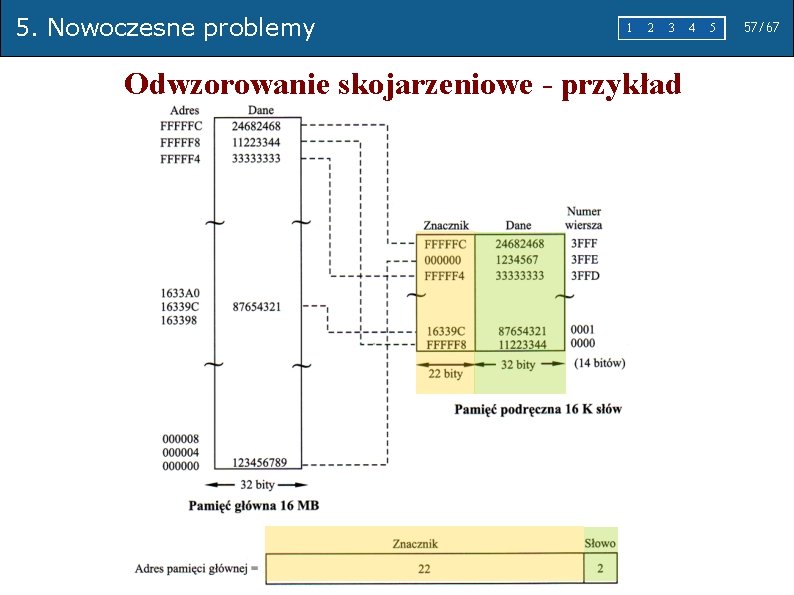

5. Nowoczesne problemy 1 2 3 Odwzorowanie skojarzeniowe - przykład 4 5 57/67

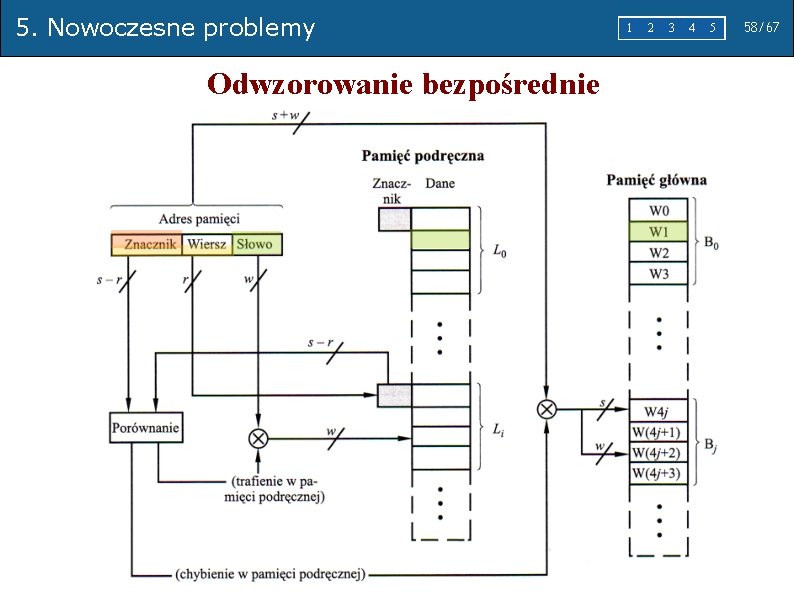

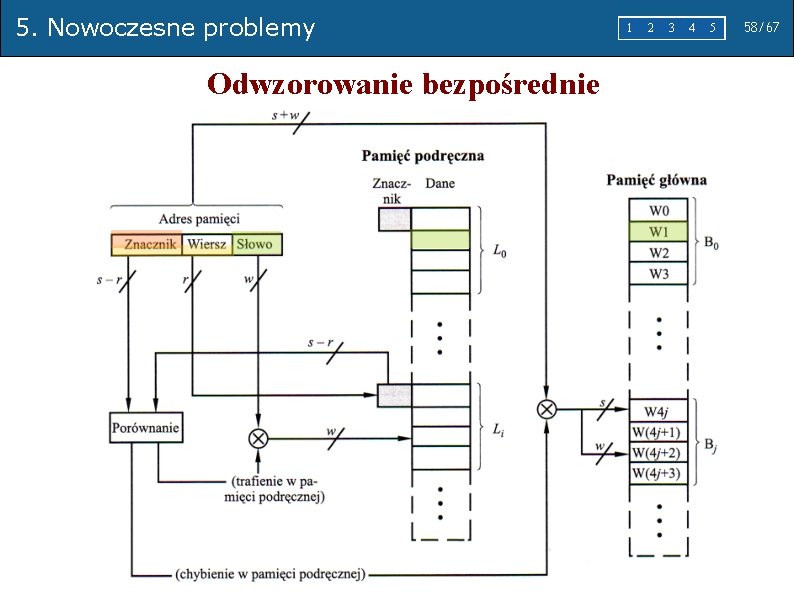

5. Nowoczesne problemy Odwzorowanie bezpośrednie 1 2 3 4 5 58/67

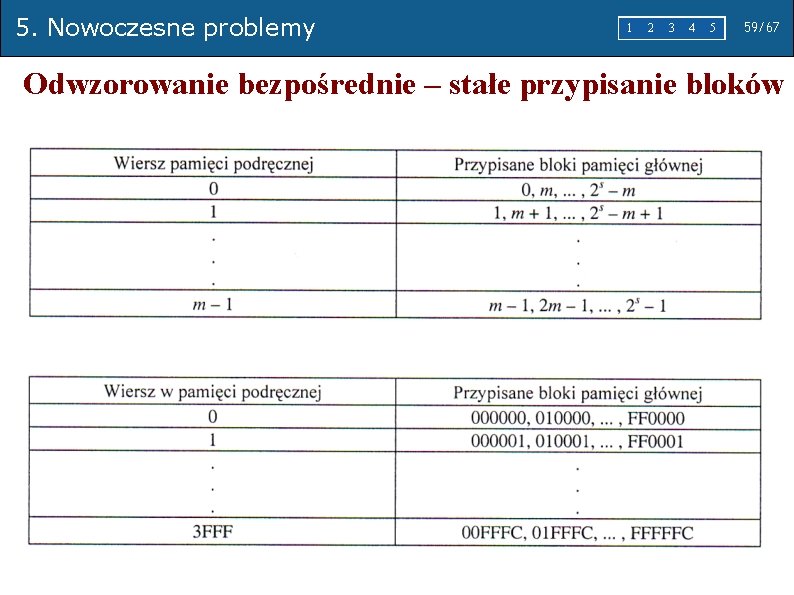

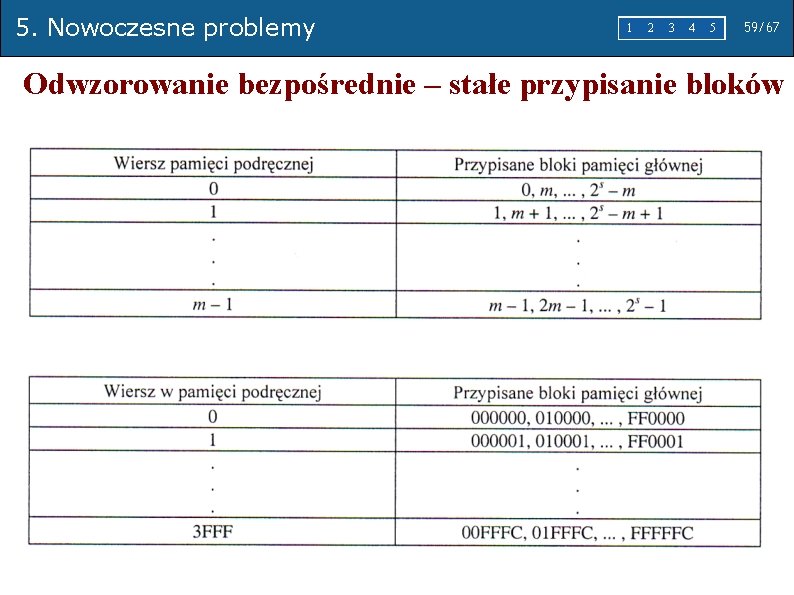

5. Nowoczesne problemy 1 2 3 4 5 59/67 Odwzorowanie bezpośrednie – stałe przypisanie bloków

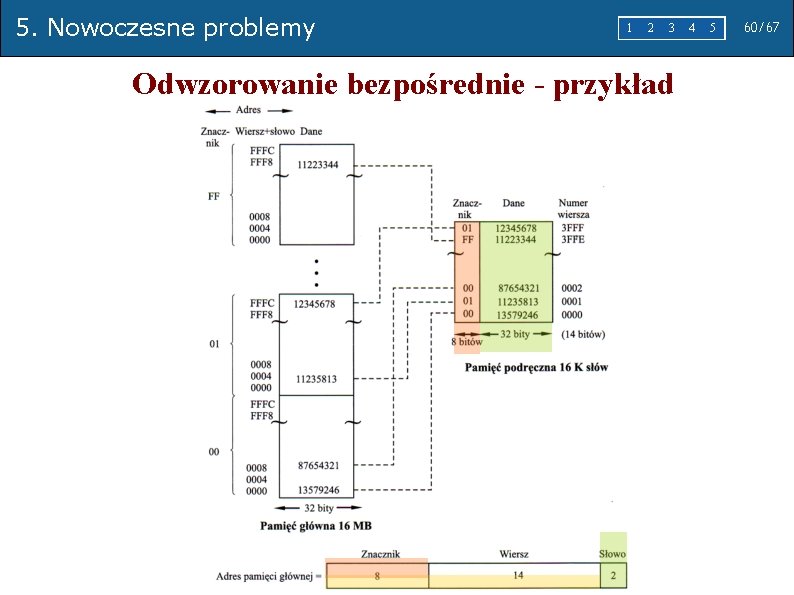

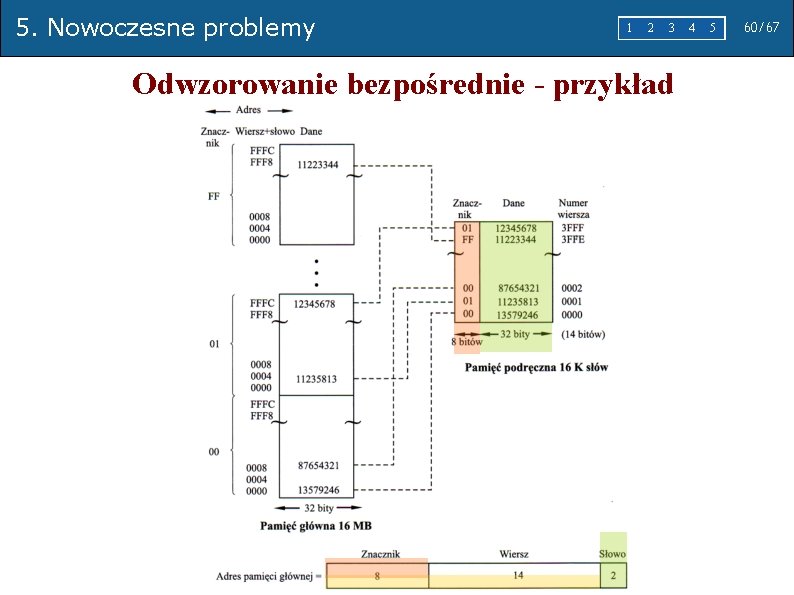

5. Nowoczesne problemy 1 2 3 Odwzorowanie bezpośrednie - przykład 4 5 60/67

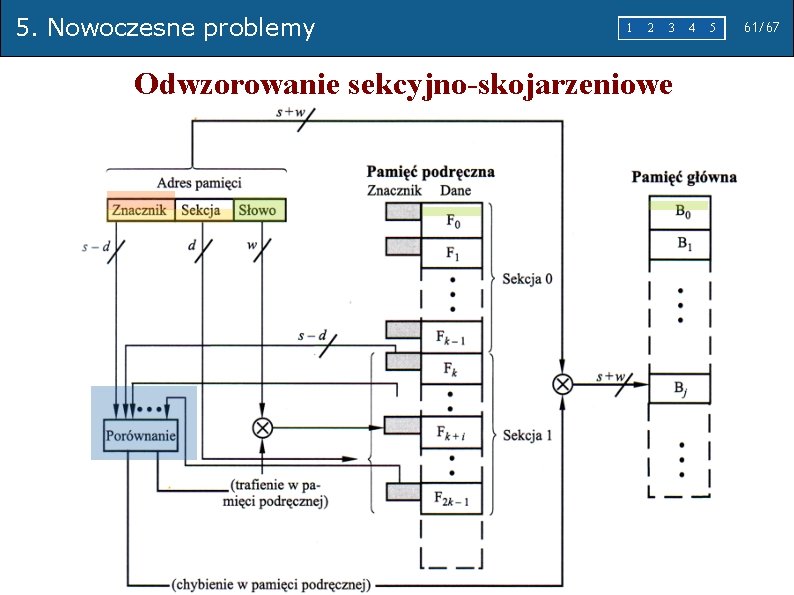

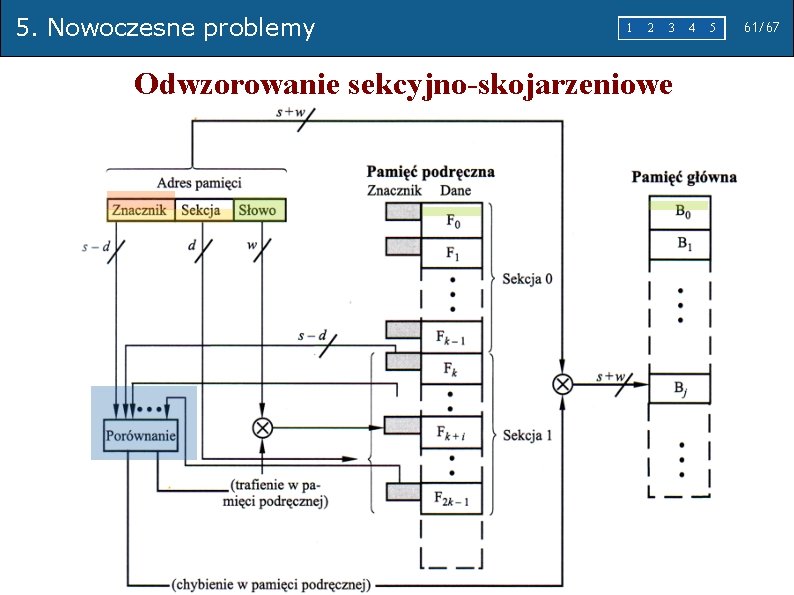

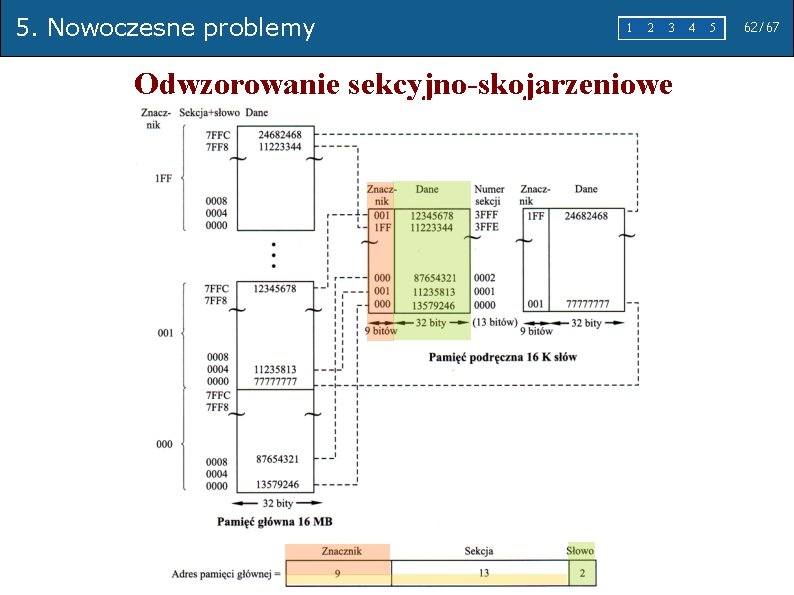

5. Nowoczesne problemy 1 2 3 Odwzorowanie sekcyjno-skojarzeniowe 4 5 61/67

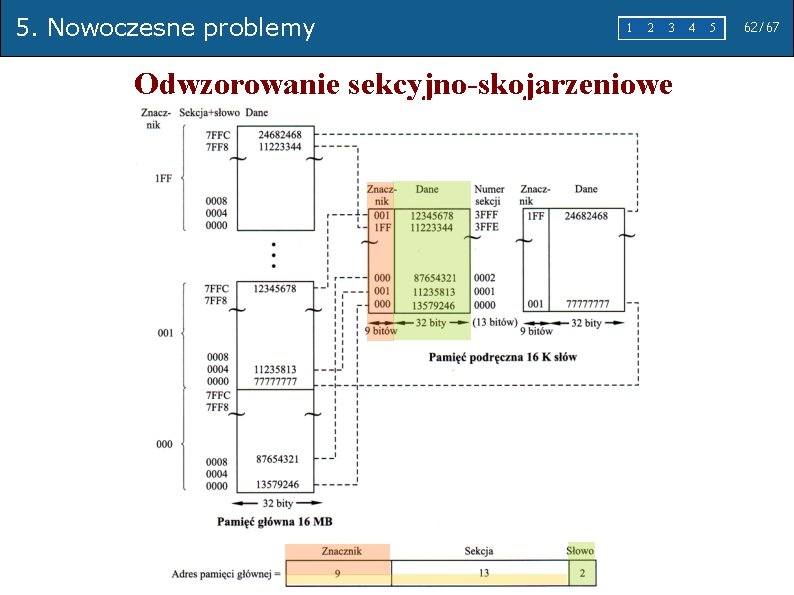

5. Nowoczesne problemy 1 2 3 Odwzorowanie sekcyjno-skojarzeniowe 4 5 62/67

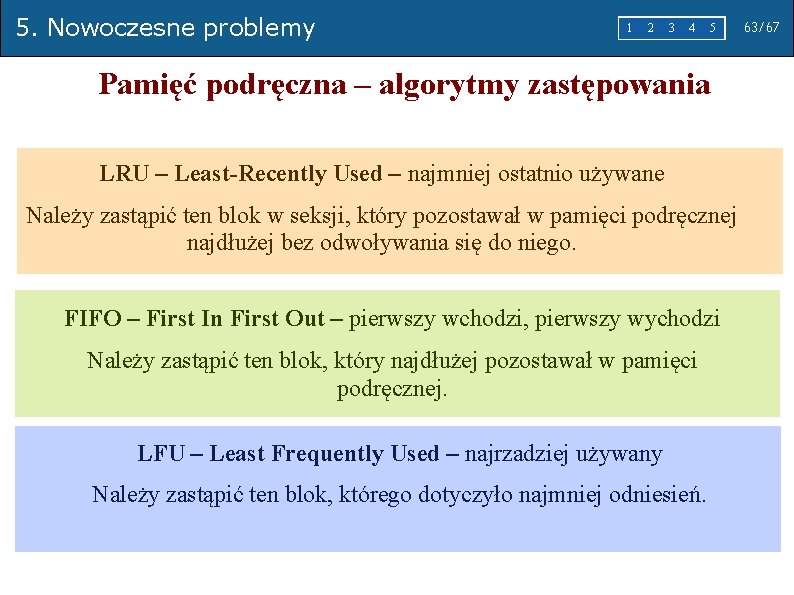

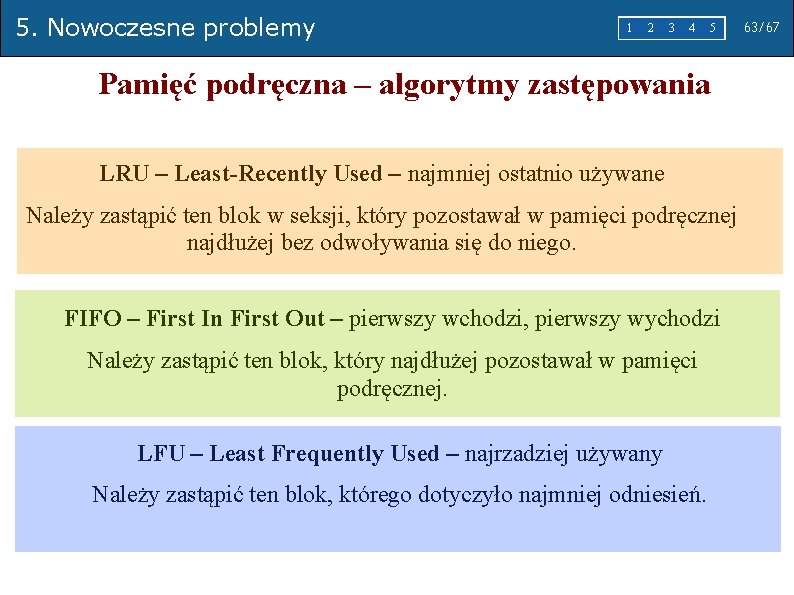

5. Nowoczesne problemy 1 2 3 4 5 Pamięć podręczna – algorytmy zastępowania LRU – Least-Recently Used – najmniej ostatnio używane Należy zastąpić ten blok w seksji, który pozostawał w pamięci podręcznej najdłużej bez odwoływania się do niego. FIFO – First In First Out – pierwszy wchodzi, pierwszy wychodzi Należy zastąpić ten blok, który najdłużej pozostawał w pamięci podręcznej. LFU – Least Frequently Used – najrzadziej używany Należy zastąpić ten blok, którego dotyczyło najmniej odniesień. 63/67

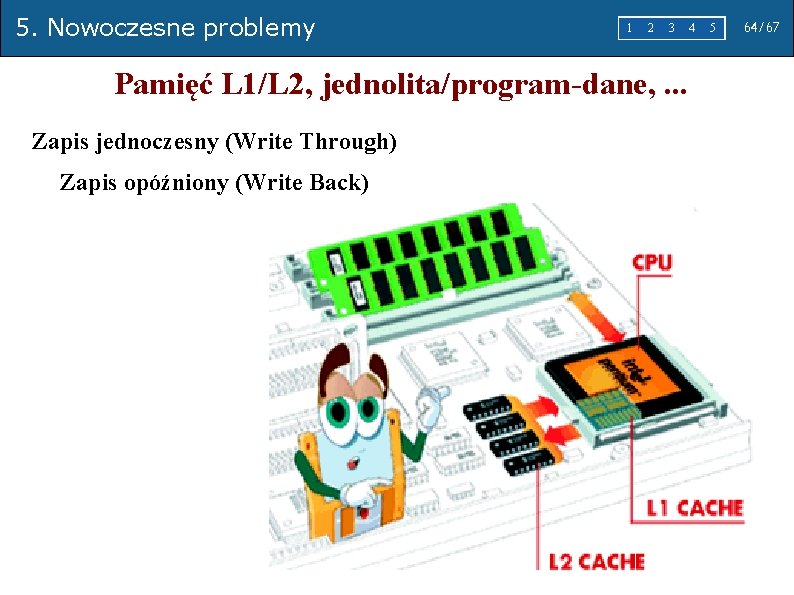

5. Nowoczesne problemy 1 2 3 Pamięć L 1/L 2, jednolita/program-dane, . . . Zapis jednoczesny (Write Through) Zapis opóźniony (Write Back) 4 5 64/67

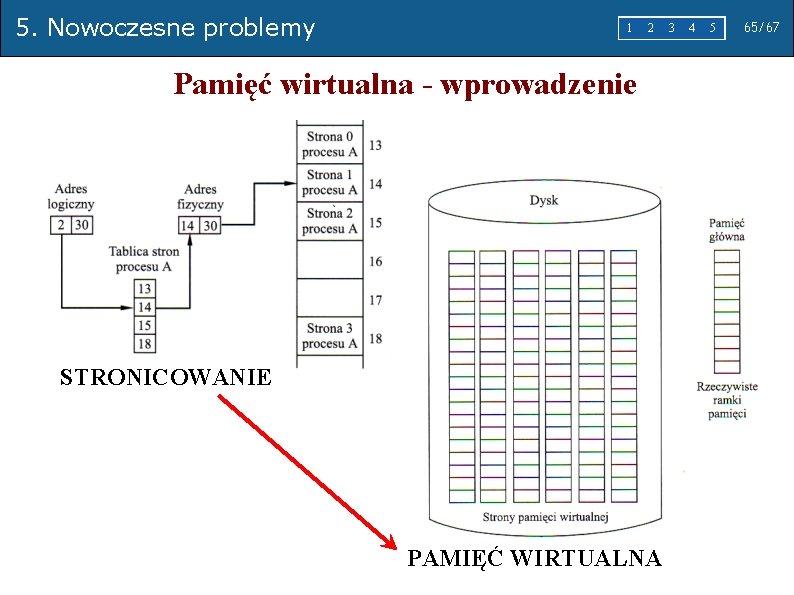

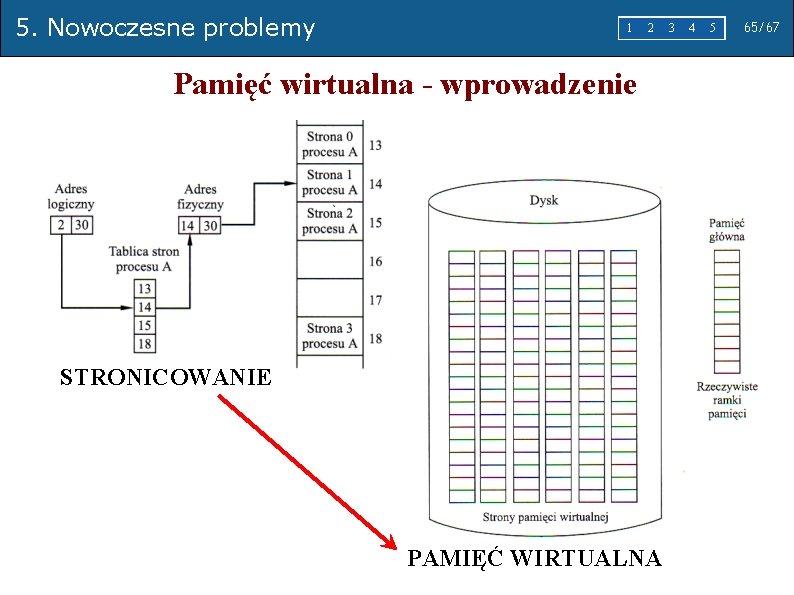

5. Nowoczesne problemy 1 2 Pamięć wirtualna - wprowadzenie STRONICOWANIE PAMIĘĆ WIRTUALNA 3 4 5 65/67

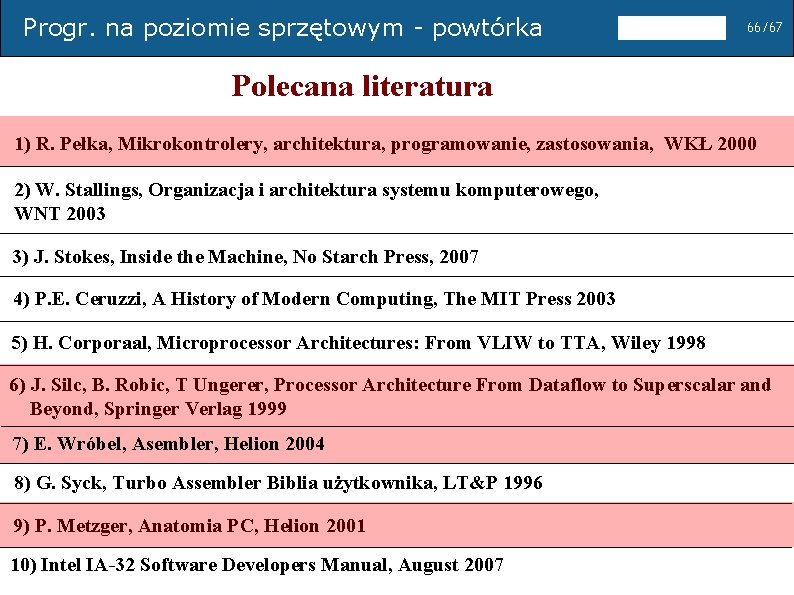

Progr. na poziomie sprzętowym - powtórka 66/67 Polecana literatura 1) R. Pełka, Mikrokontrolery, architektura, programowanie, zastosowania, WKŁ 2000 2) W. Stallings, Organizacja i architektura systemu komputerowego, WNT 2003 3) J. Stokes, Inside the Machine, No Starch Press, 2007 4) P. E. Ceruzzi, A History of Modern Computing, The MIT Press 2003 5) H. Corporaal, Microprocessor Architectures: From VLIW to TTA, Wiley 1998 6) J. Silc, B. Robic, T Ungerer, Processor Architecture From Dataflow to Superscalar and Beyond, Springer Verlag 1999 7) E. Wróbel, Asembler, Helion 2004 8) G. Syck, Turbo Assembler Biblia użytkownika, LT&P 1996 9) P. Metzger, Anatomia PC, Helion 2001 10) Intel IA-32 Software Developers Manual, August 2007

Progr. na poziomie sprzętowym - powtórka dr inż. Mariusz Kapruziak mkapruziak@wi. ps. pl pok. 107, tel. 449 55 44 KONIEC 67/67