Progetto Rete Sequenziale Asincrona Testo Si vuole realizzare

- Slides: 15

Progetto Rete Sequenziale Asincrona

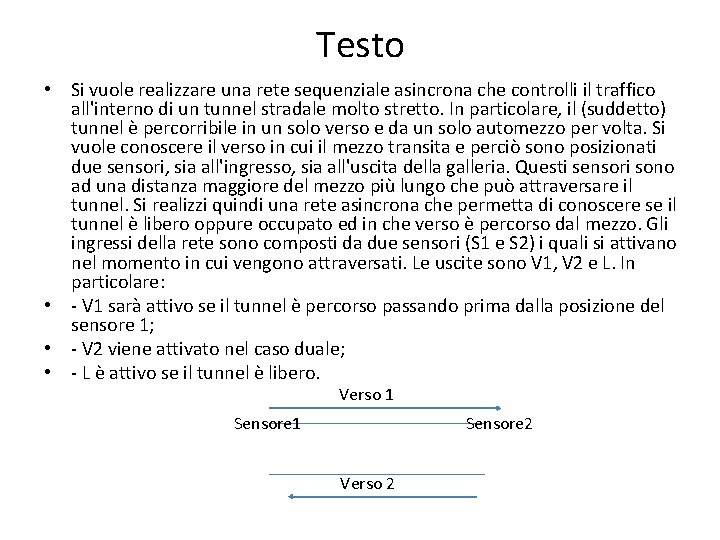

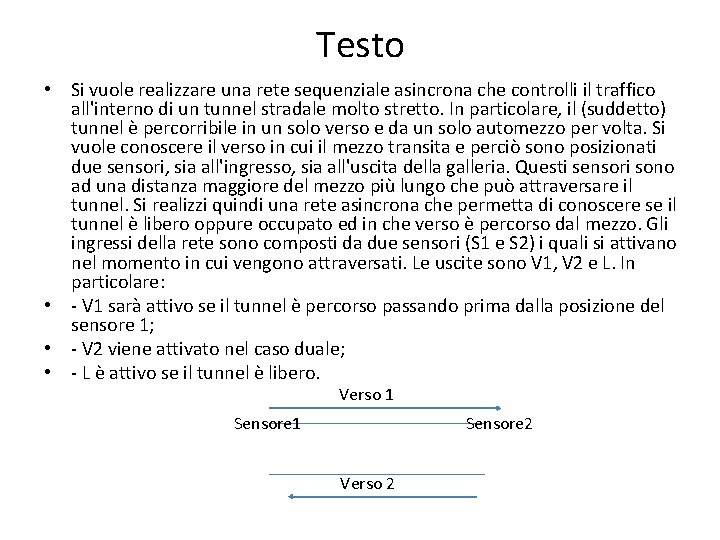

Testo • Si vuole realizzare una rete sequenziale asincrona che controlli il traffico all'interno di un tunnel stradale molto stretto. In particolare, il (suddetto) tunnel è percorribile in un solo verso e da un solo automezzo per volta. Si vuole conoscere il verso in cui il mezzo transita e perciò sono posizionati due sensori, sia all'ingresso, sia all'uscita della galleria. Questi sensori sono ad una distanza maggiore del mezzo più lungo che può attraversare il tunnel. Si realizzi quindi una rete asincrona che permetta di conoscere se il tunnel è libero oppure occupato ed in che verso è percorso dal mezzo. Gli ingressi della rete sono composti da due sensori (S 1 e S 2) i quali si attivano nel momento in cui vengono attraversati. Le uscite sono V 1, V 2 e L. In particolare: • - V 1 sarà attivo se il tunnel è percorso passando prima dalla posizione del sensore 1; • - V 2 viene attivato nel caso duale; • - L è attivo se il tunnel è libero. Verso 1 Sensore 2 Verso 2

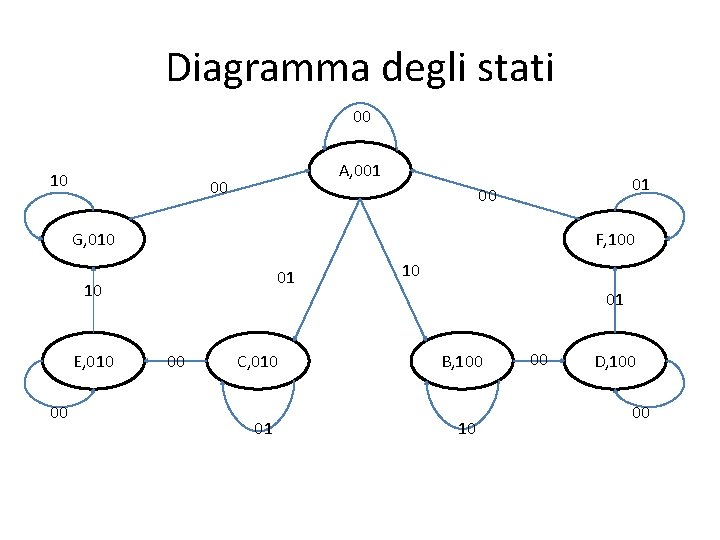

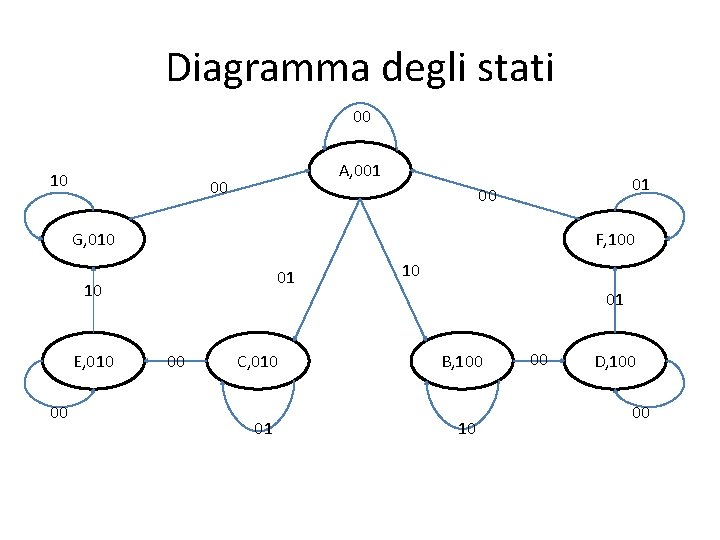

Diagramma degli stati 00 10 A, 001 00 G, 010 F, 100 01 10 E, 010 00 00 C, 010 01 B, 100 10 00 D, 100 00

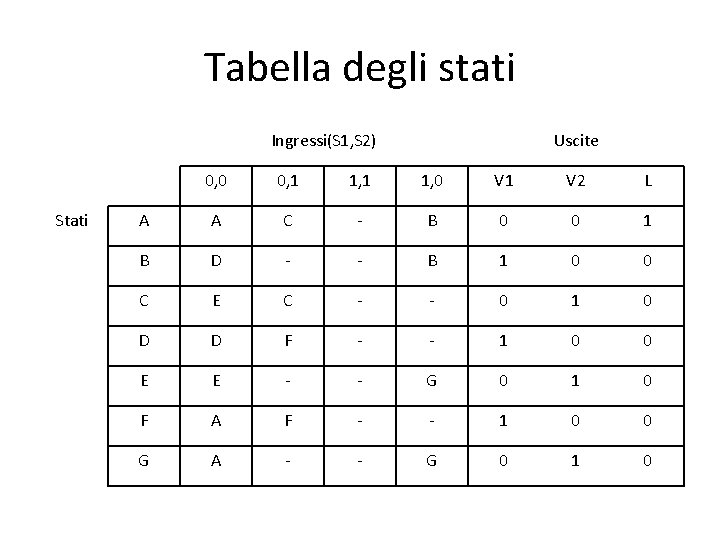

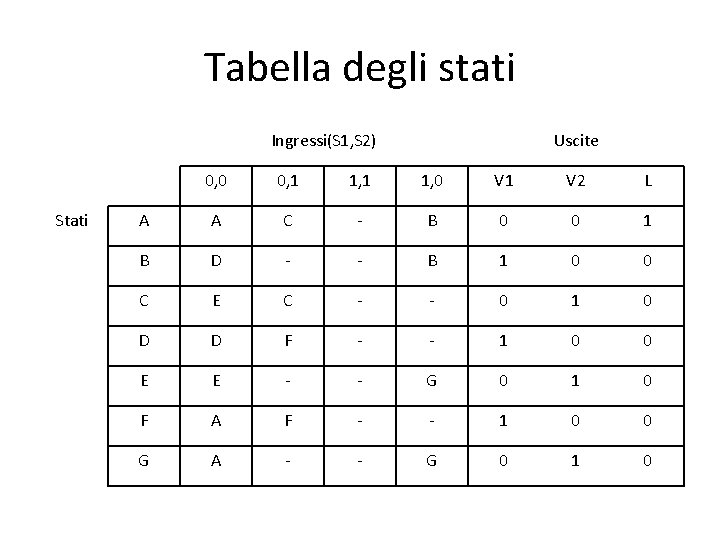

Tabella degli stati Ingressi(S 1, S 2) Stati Uscite 0, 0 0, 1 1, 0 V 1 V 2 L A A C - B 0 0 1 B D - - B 1 0 0 C E C - - 0 1 0 D D F - - 1 0 0 E E - - G 0 1 0 F A F - - 1 0 0 G A - - G 0 1 0

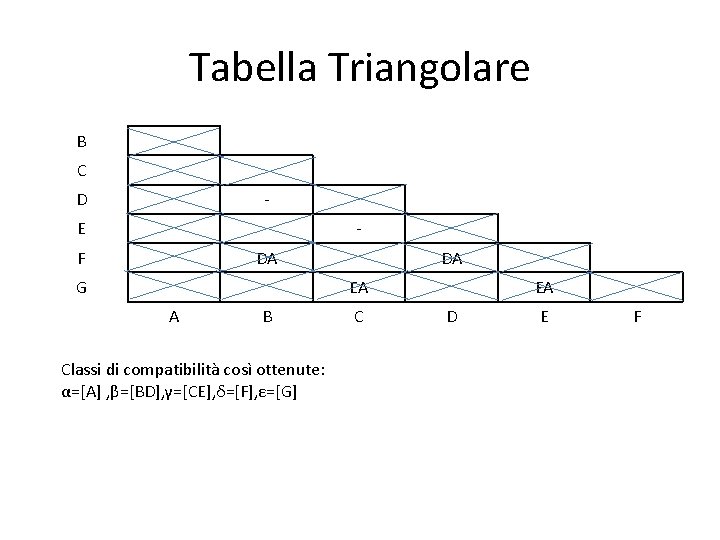

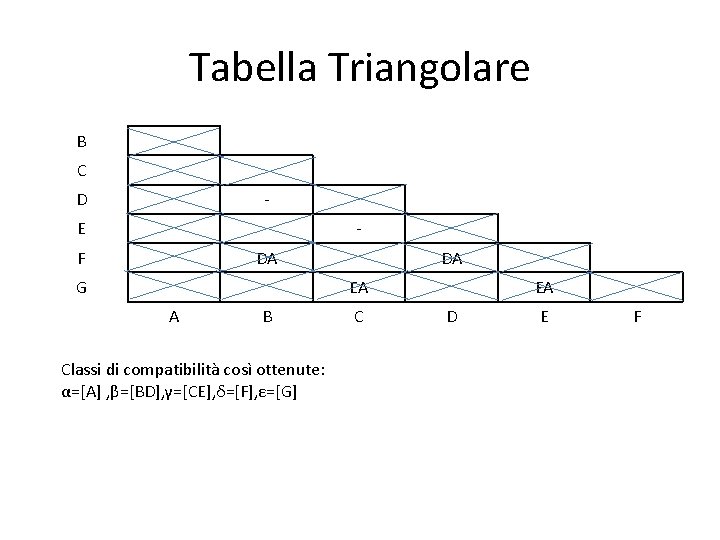

Tabella Triangolare B C D - E - F DA G DA EA A B Classi di compatibilità così ottenute: α=[A] , β=[BD], γ=[CE], δ=[F], ε=[G] C EA D E F

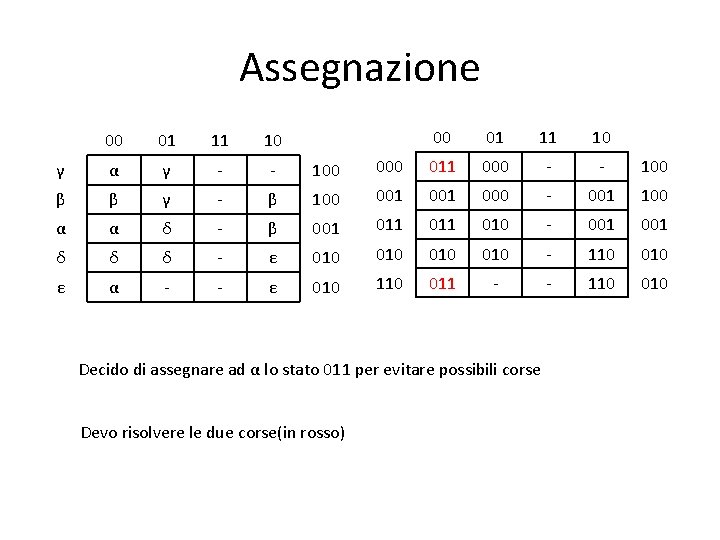

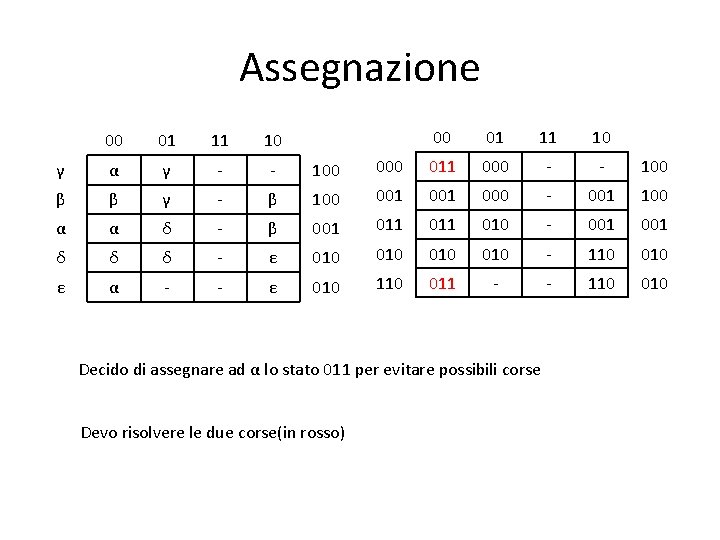

Assegnazione 00 01 11 10 000 011 000 - - 100 001 000 - 001 100 β 001 011 010 - 001 - ε 010 010 - 110 010 - ε 010 110 011 - - 110 00 01 11 10 γ α γ - - 100 β β γ - β α α δ - δ δ δ ε α - Decido di assegnare ad α lo stato 011 per evitare possibili corse Devo risolvere le due corse(in rosso)

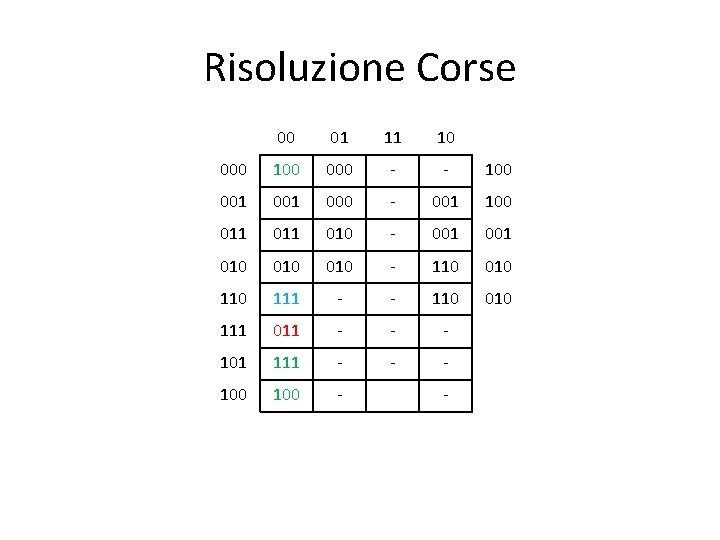

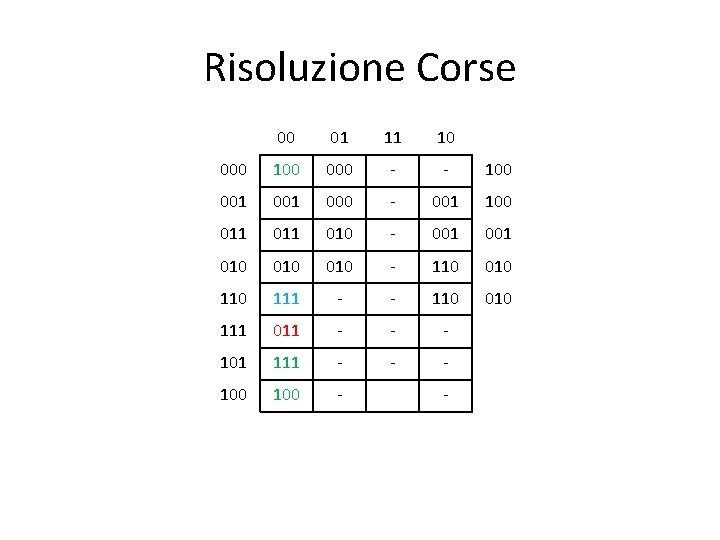

Risoluzione Corse 00 01 11 10 000 100 000 - - 100 001 000 - 001 100 011 010 - 001 010 010 - 110 010 111 - - 110 010 111 011 - - - 101 111 - - - 100 - -

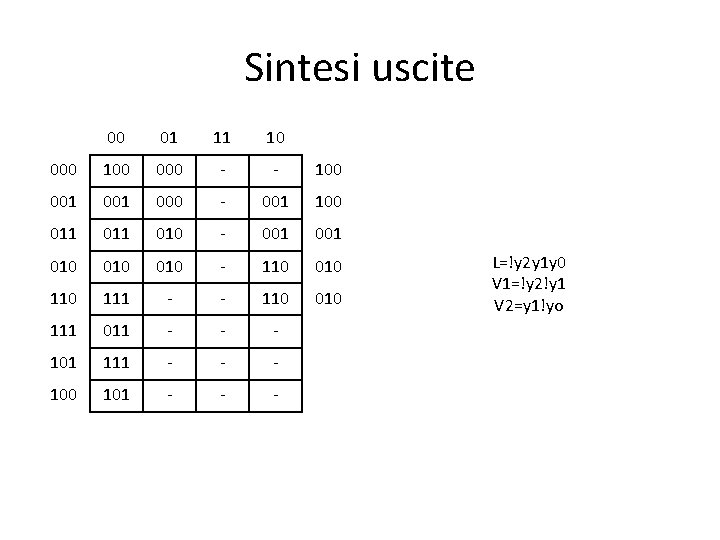

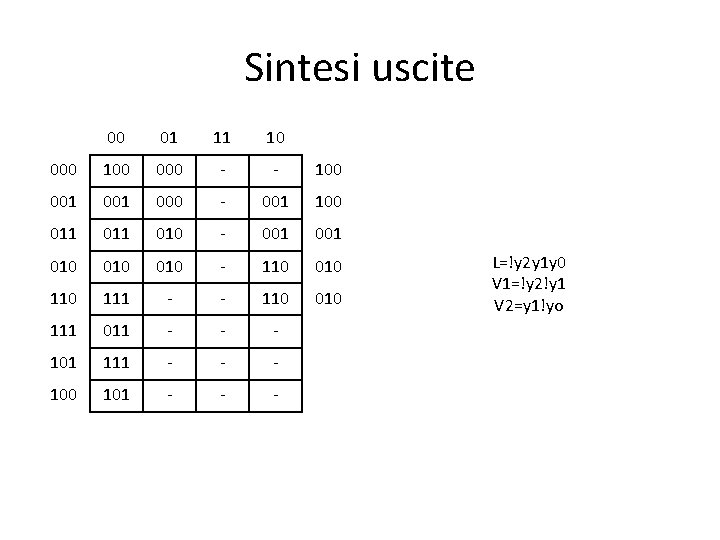

Sintesi uscite 00 01 11 10 000 100 000 - - 100 001 000 - 001 100 011 010 - 001 010 010 - 110 010 111 - - 110 010 111 011 - - - 101 111 - - - 100 101 - - - L=!y 2 y 1 y 0 V 1=!y 2!y 1 V 2=y 1!yo

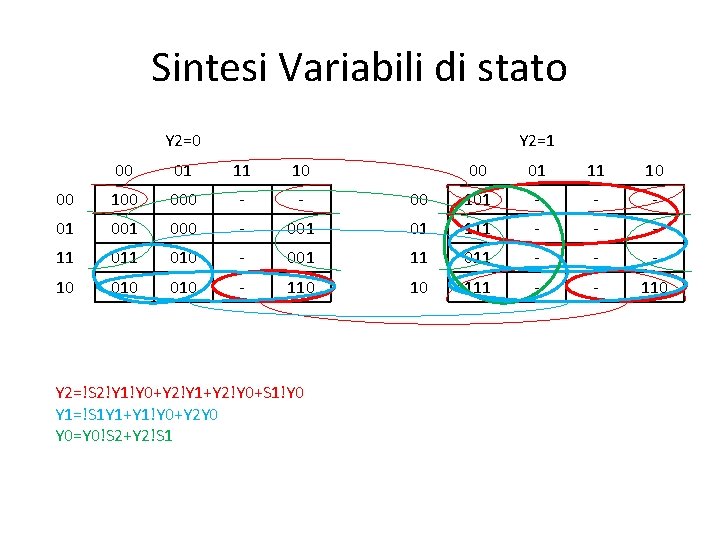

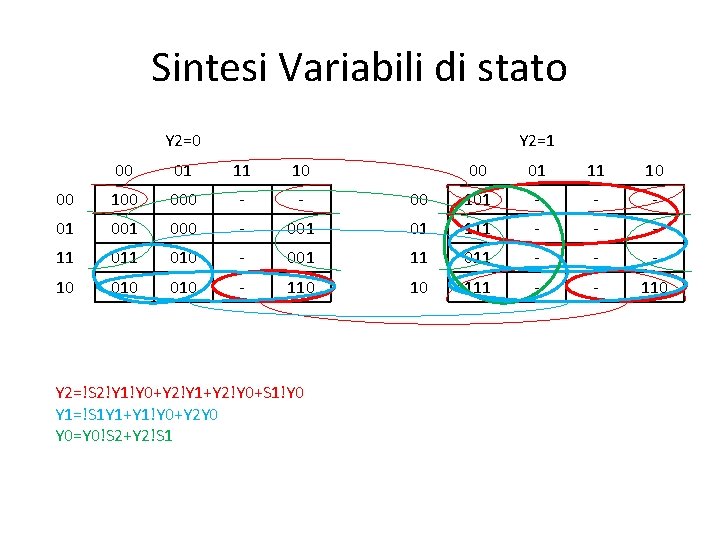

Sintesi Variabili di stato Y 2=0 Y 2=1 00 01 11 10 00 100 000 - - 00 101 - - - 01 000 - 001 01 111 - - - 11 010 - 001 11 011 - - - 10 010 - 110 10 111 - - 110 Y 2=!S 2!Y 1!Y 0+Y 2!Y 1+Y 2!Y 0+S 1!Y 0 Y 1=!S 1 Y 1+Y 1!Y 0+Y 2 Y 0 Y 0=Y 0!S 2+Y 2!S 1

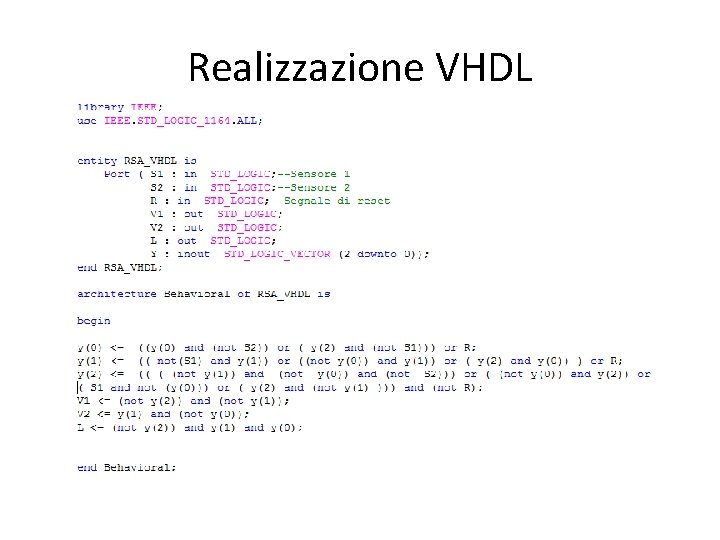

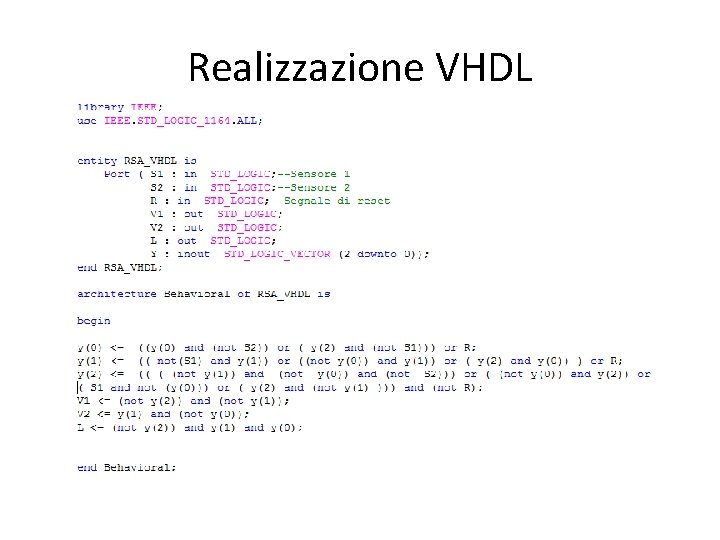

Realizzazione VHDL

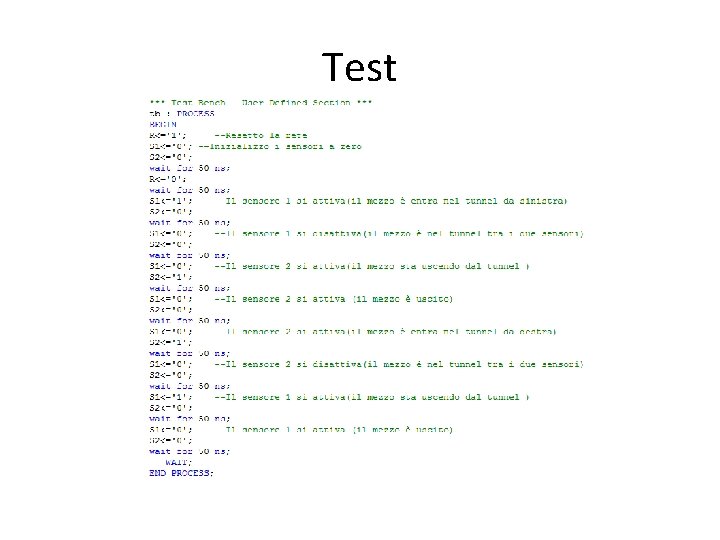

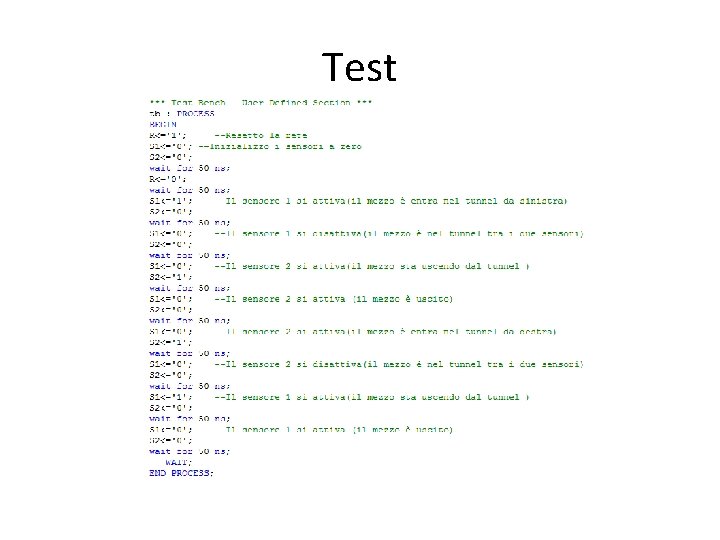

Test

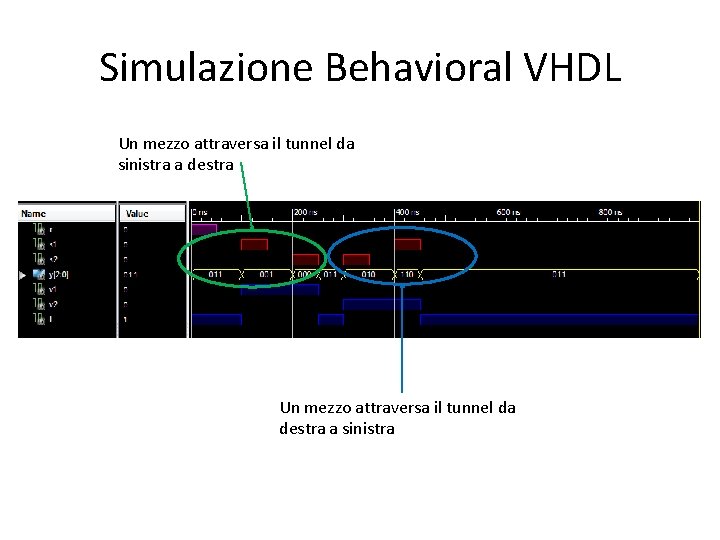

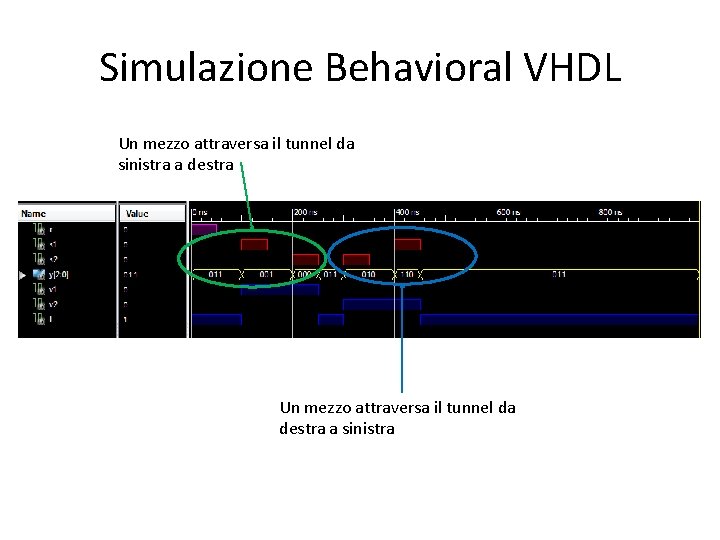

Simulazione Behavioral VHDL Un mezzo attraversa il tunnel da sinistra a destra Un mezzo attraversa il tunnel da destra a sinistra

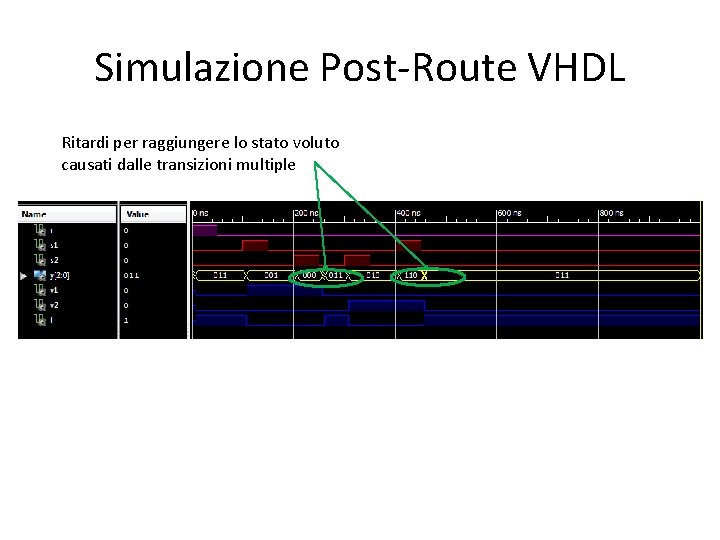

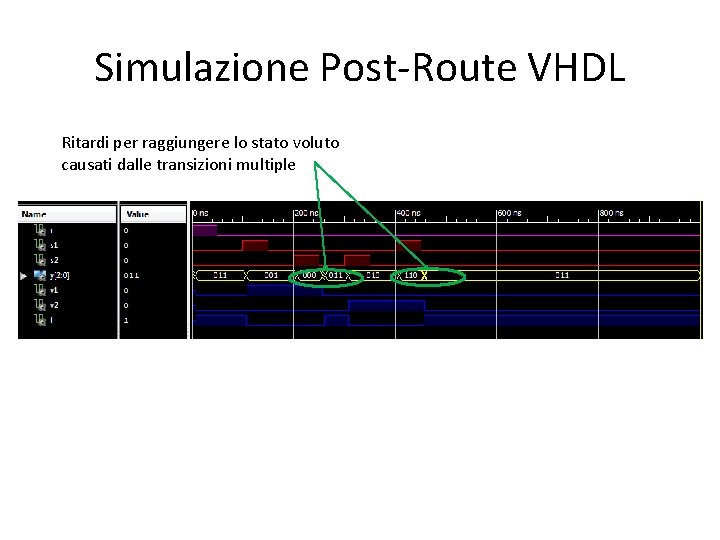

Simulazione Post-Route VHDL Ritardi per raggiungere lo stato voluto causati dalle transizioni multiple

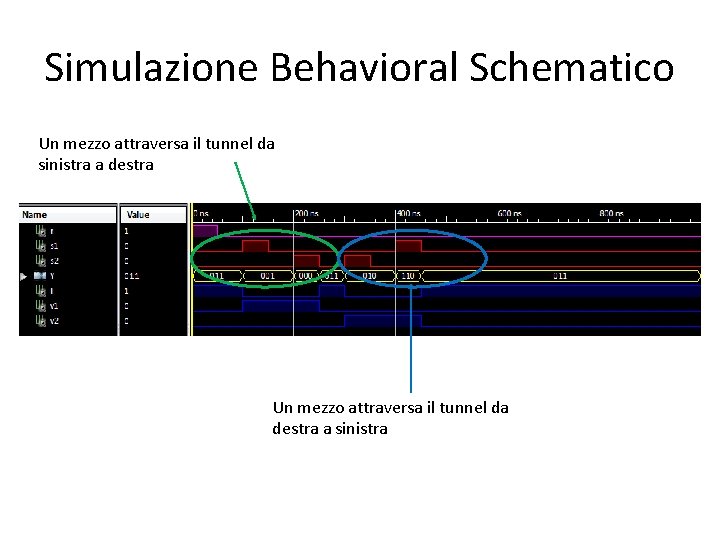

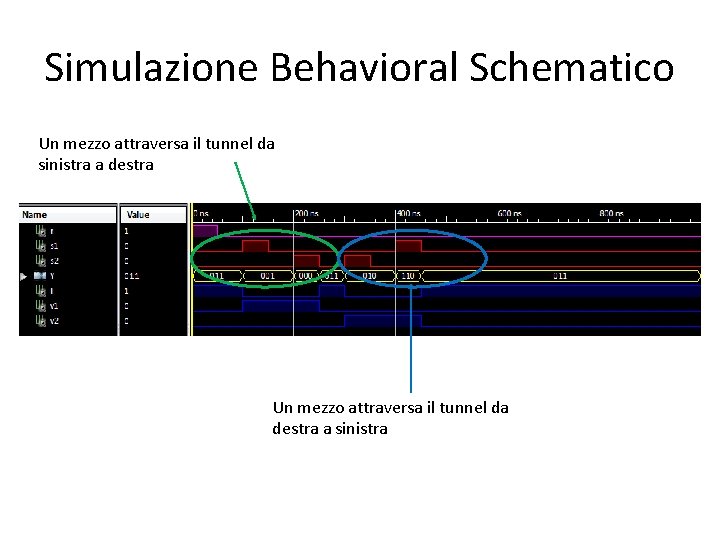

Simulazione Behavioral Schematico Un mezzo attraversa il tunnel da sinistra a destra Un mezzo attraversa il tunnel da destra a sinistra

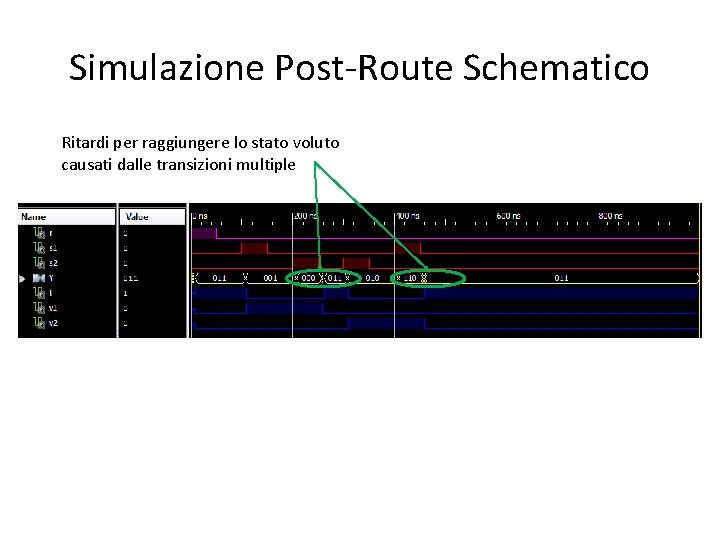

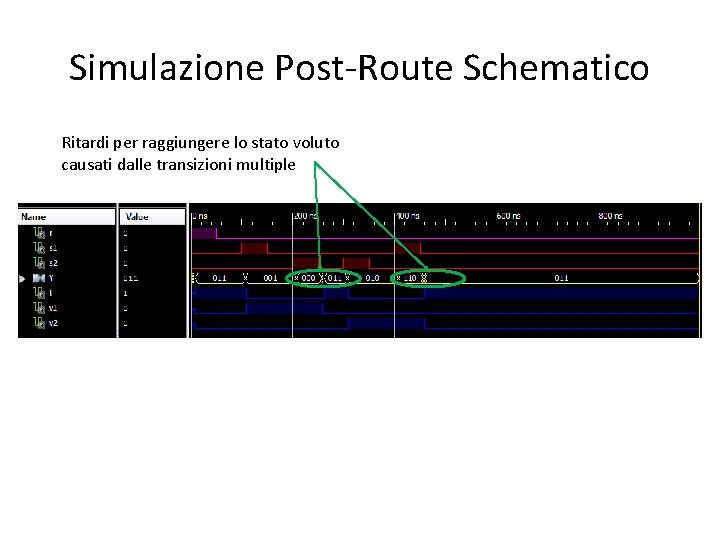

Simulazione Post-Route Schematico Ritardi per raggiungere lo stato voluto causati dalle transizioni multiple