Prof Valeria Bertacco Computer Engineering Lab Computer Science

Prof. Valeria Bertacco Computer Engineering Lab Computer Science and Engineering Division University of Michigan 1

Once upon a time, computers looked all the same…. 2

Today, computing systems are everywhere 3

What’s inside ¡ ¡ ¡ Silicon chips Lots of software Sensors, actuators, motors, etc. 4

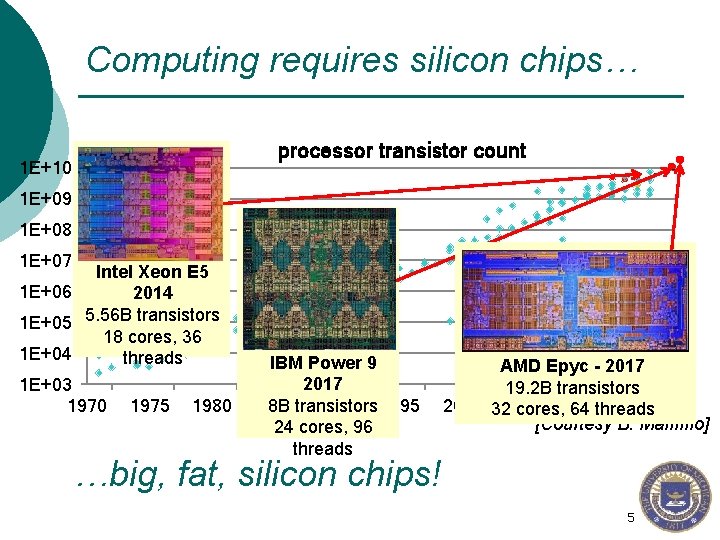

Computing requires silicon chips… processor transistor count 1 E+10 1 E+09 1 E+08 1 E+07 Intel Xeon E 5 1 E+06 2014 1 E+05 5. 56 B transistors 18 cores, 36 1 E+04 threads 1 E+03 1970 1975 1980 IBM Power 9 2017 8 B transistors 1985 1990 1995 24 cores, 96 threads AMD Epyc - 2017 19. 2 B transistors 2000 322005 2015 cores, 2010 64 threads [Courtesy B. Mammo] …big, fat, silicon chips! 5

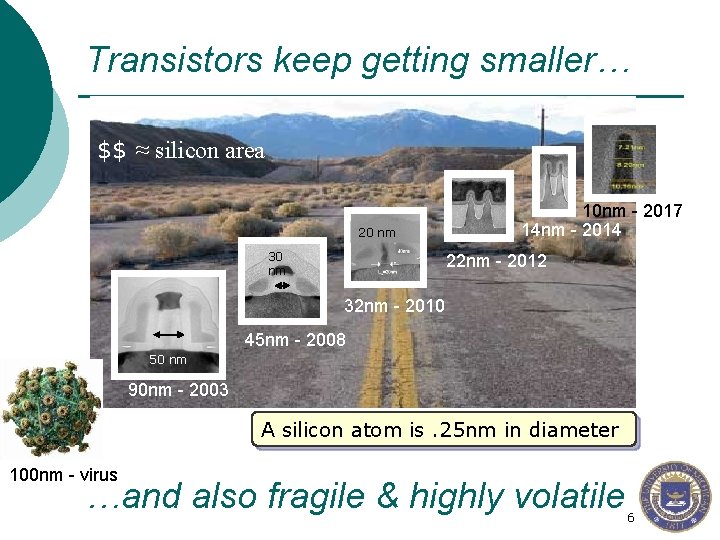

Transistors keep getting smaller… $$ ≈ silicon area 20 nm 30 nm 10 nm - 2017 14 nm - 2014 22 nm - 2012 32 nm - 2010 45 nm - 2008 50 nm 90 nm - 2003 A silicon atom is. 25 nm in diameter 100 nm - virus …and also fragile & highly volatile 6

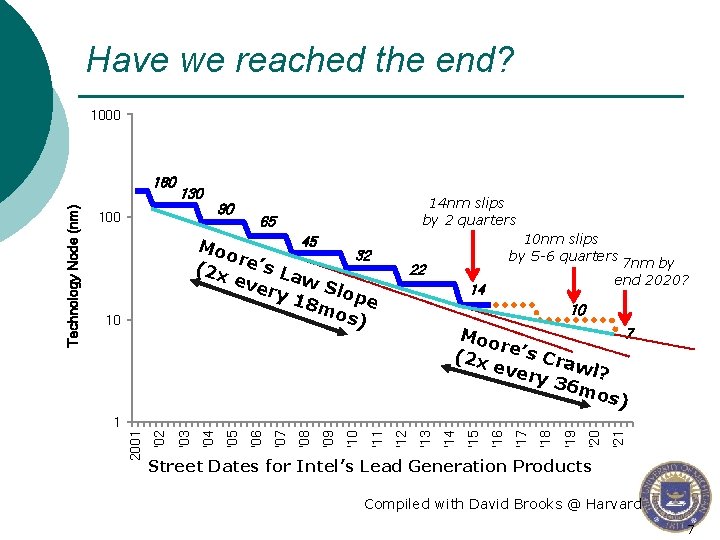

Have we reached the end? 1000 14 nm slips by 2 quarters 65 10 nm slips by 5 -6 quarters 7 nm by end 2020? 22 14 10 '21 '20 '19 '18 '17 '16 '15 '14 7 Moo re’s (2 x Craw eve ry 3 l? 6 mo s) '12 '11 '10 '09 '08 '07 '06 '05 '03 '02 '04 45 Mo ore 32 ’s L (2 x eve aw S lo ry 1 8 m pe os) 10 1 90 '13 130 100 2001 Technology Node (nm) 180 Street Dates for Intel’s Lead Generation Products Compiled with David Brooks @ Harvard 7

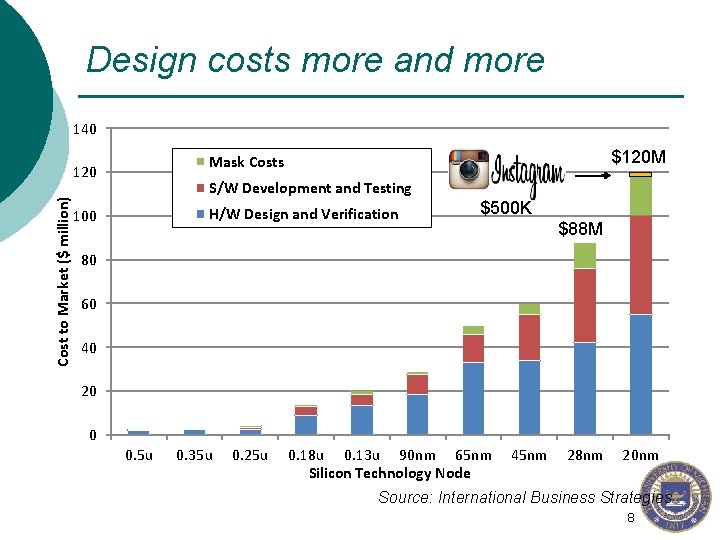

Design costs more and more 140 120 Cost to Market ($ million) $120 M Mask Costs S/W Development and Testing H/W Design and Verification 100 $500 K $88 M 80 60 40 20 0 0. 5 u 0. 35 u 0. 25 u 0. 18 u 0. 13 u 90 nm 65 nm Silicon Technology Node 45 nm 28 nm 20 nm Source: International Business Strategies 8

Technology value creation The electronics industry needs new propulsion Unbearable design costs Silicon transistor scaling 9

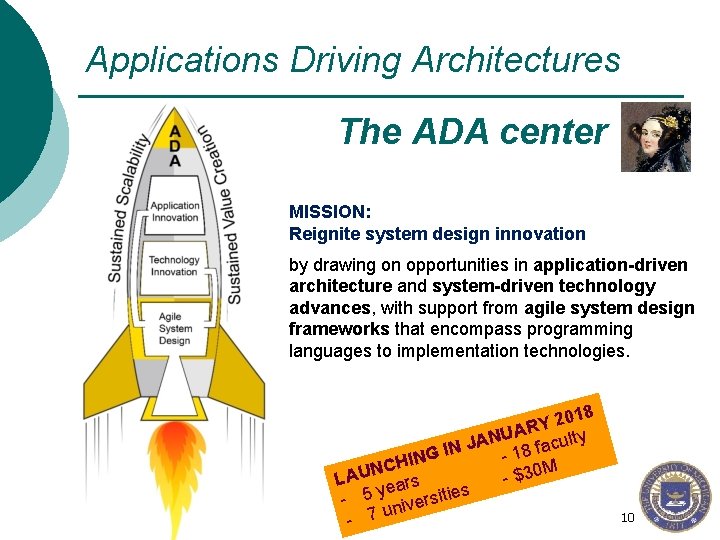

Applications Driving Architectures The ADA center MISSION: Reignite system design innovation by drawing on opportunities in application-driven architecture and system-driven technology advances, with support from agile system design frameworks that encompass programming languages to implementation technologies. 018 2 Y UAR ulty N A N J - 18 fac I G CHIN N U 30 M $ LA s year sities 5 iver n u - 7 10

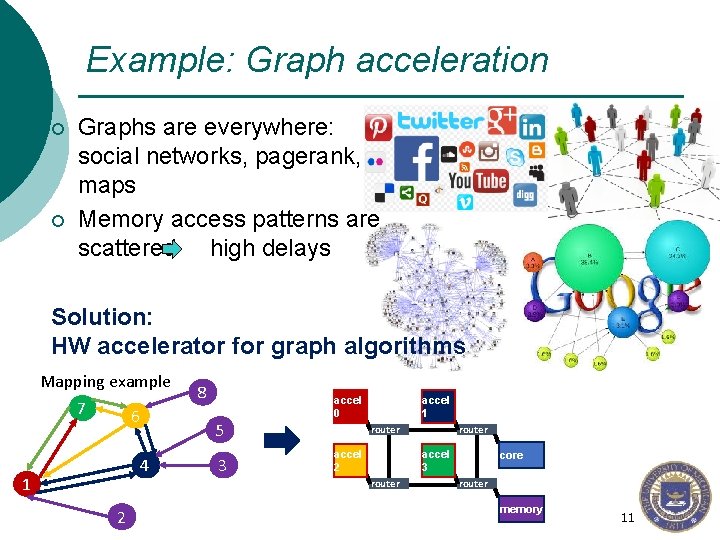

Example: Graph acceleration ¡ ¡ Graphs are everywhere: social networks, pagerank, maps Memory access patterns are scattered high delays Solution: HW accelerator for graph algorithms Mapping example 7 6 5 4 1 8 3 accel 0 accel 1 router accel 2 accel 3 router 2 router core router memory 11

The BLAB 2015 2017 12

- Slides: 12