Processors Year The Intel 86 Family of Processors

- Slides: 9

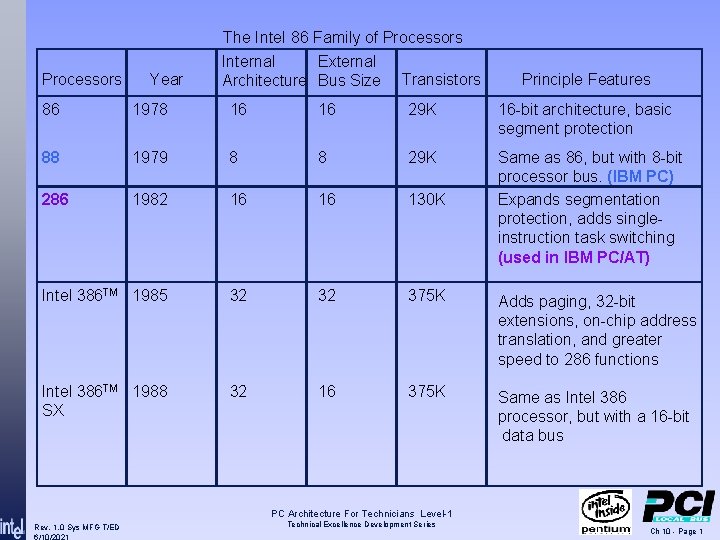

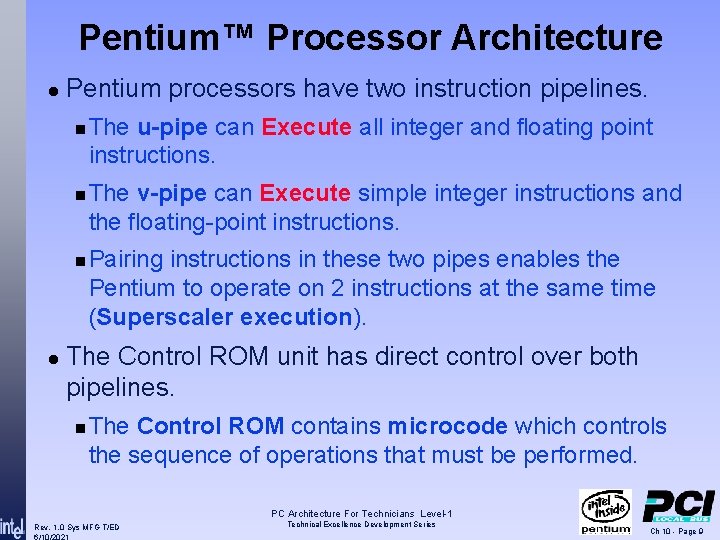

Processors Year The Intel 86 Family of Processors External Internal Architecture Bus Size Transistors Principle Features 86 1978 16 16 29 K 16 -bit architecture, basic segment protection 88 1979 8 8 29 K 286 1982 16 16 130 K Same as 86, but with 8 -bit processor bus. (IBM PC) Expands segmentation protection, adds singleinstruction task switching (used in IBM PC/AT) Intel 386 TM 1985 32 32 375 K Adds paging, 32 -bit extensions, on-chip address translation, and greater speed to 286 functions Intel 386 TM 1988 SX 32 16 375 K Same as Intel 386 processor, but with a 16 -bit data bus PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 1

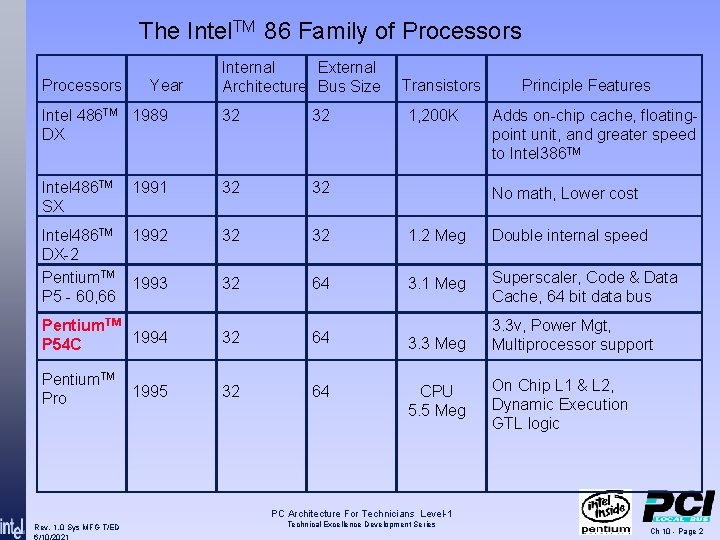

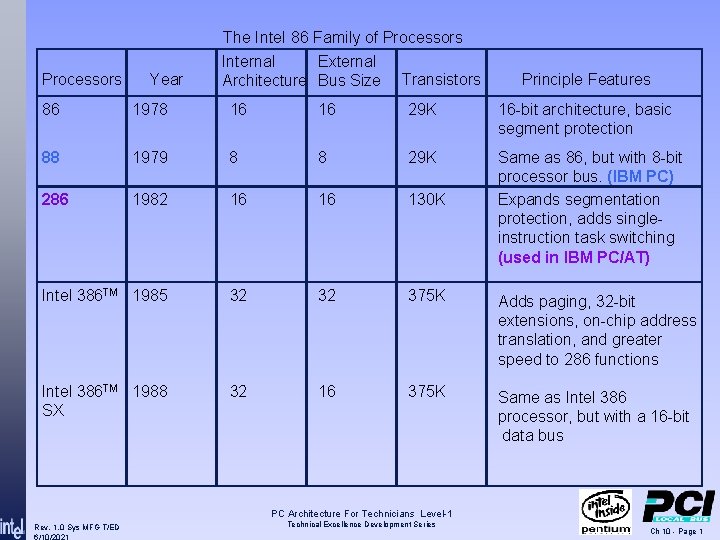

The Intel. TM 86 Family of Processors Year External Internal Architecture Bus Size Transistors Principle Features Intel 486 TM 1989 DX 32 32 Intel 486 TM SX 1991 32 32 Intel 486 TM DX-2 Pentium. TM P 5 - 60, 66 1992 32 32 1. 2 Meg Double internal speed 1993 32 64 3. 1 Meg Superscaler, Code & Data Cache, 64 bit data bus Pentium. TM 1994 P 54 C 32 64 3. 3 Meg Pentium. TM Pro 32 64 CPU 5. 5 Meg 1995 1, 200 K Adds on-chip cache, floatingpoint unit, and greater speed to Intel 386 TM No math, Lower cost 3. 3 v, Power Mgt, Multiprocessor support On Chip L 1 & L 2, Dynamic Execution GTL logic PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 2

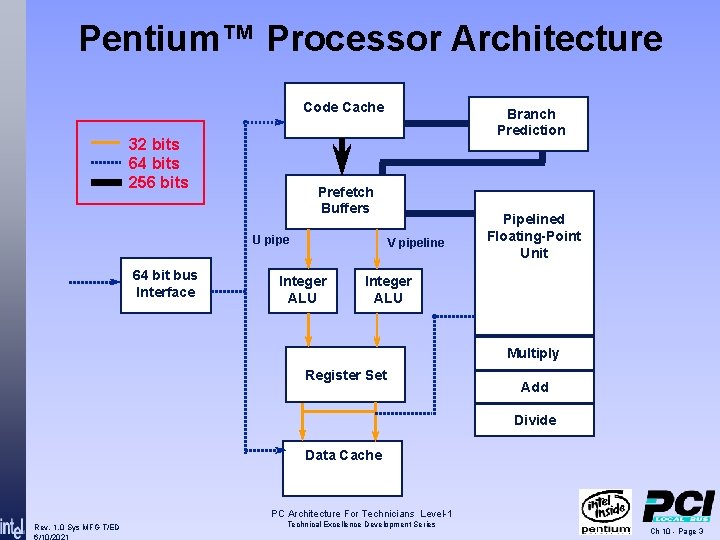

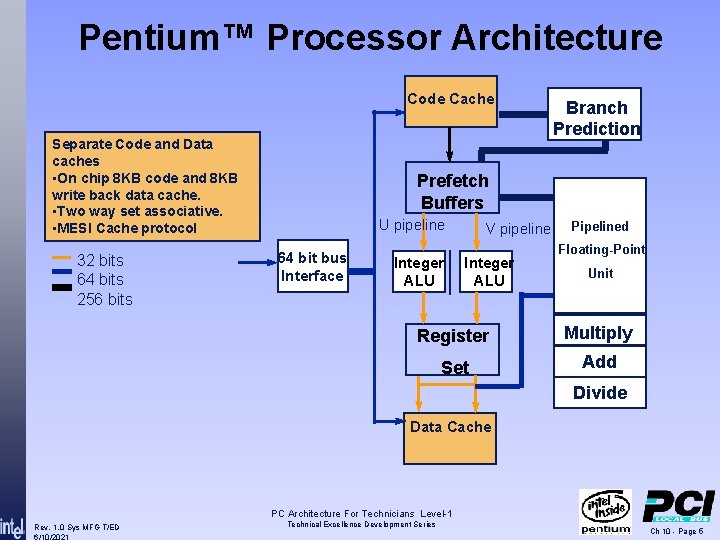

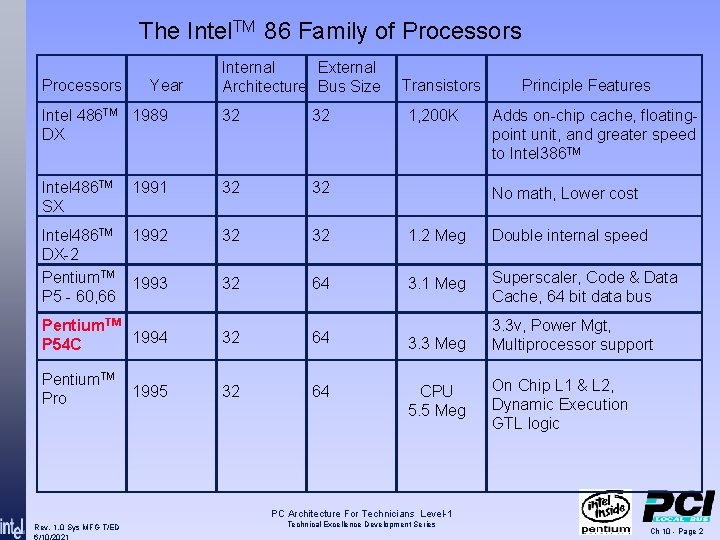

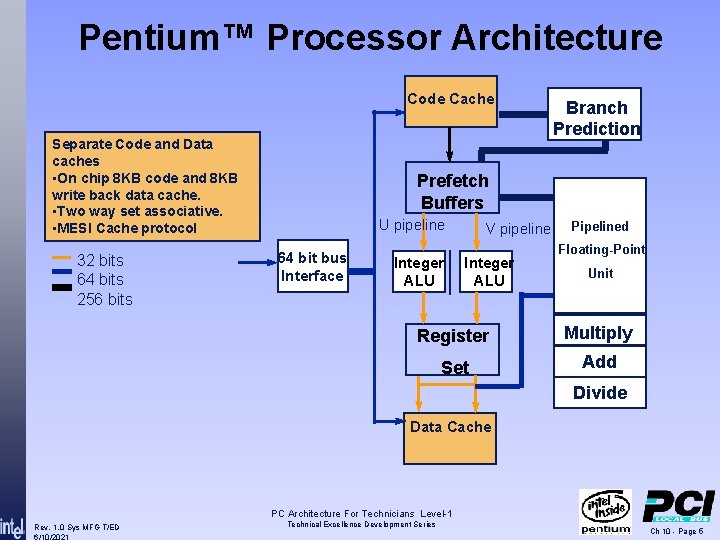

Pentium™ Processor Architecture Code Cache 32 bits 64 bits 256 bits Prefetch Buffers U pipe 64 bit bus Interface Branch Prediction V pipeline Integer ALU Pipelined Floating-Point Unit Integer ALU Multiply Register Set Add Divide Data Cache PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 3

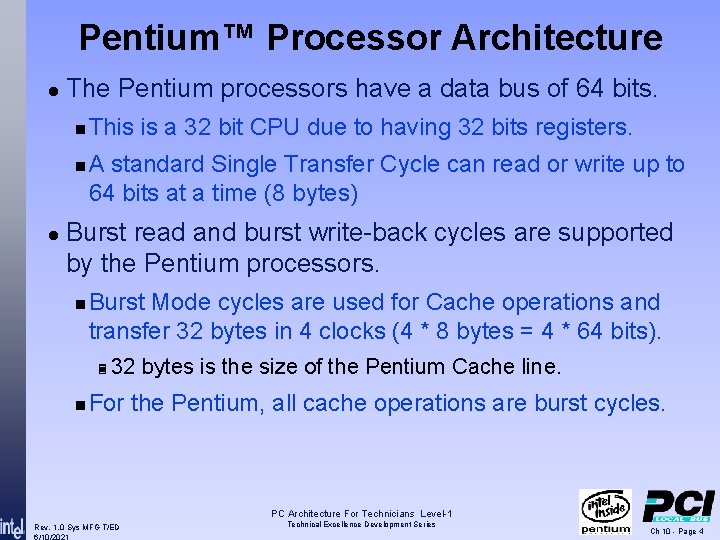

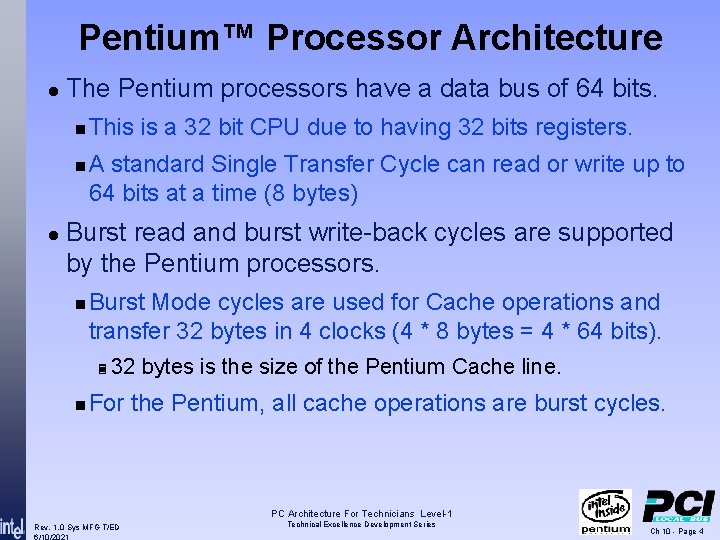

Pentium™ Processor Architecture l The Pentium processors have a data bus of 64 bits. n n l This is a 32 bit CPU due to having 32 bits registers. A standard Single Transfer Cycle can read or write up to 64 bits at a time (8 bytes) Burst read and burst write-back cycles are supported by the Pentium processors. n Burst Mode cycles are used for Cache operations and transfer 32 bytes in 4 clocks (4 * 8 bytes = 4 * 64 bits). 3 n 32 bytes is the size of the Pentium Cache line. For the Pentium, all cache operations are burst cycles. PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 4

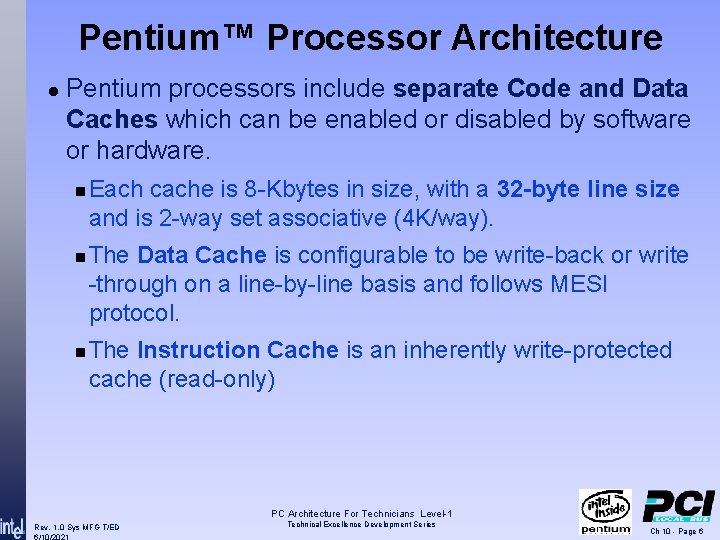

Pentium™ Processor Architecture Code Cache Separate Code and Data caches • On chip 8 KB code and 8 KB write back data cache. • Two way set associative. • MESI Cache protocol 32 bits 64 bits 256 bits Branch Prediction Prefetch Buffers U pipeline 64 bit bus Interface Integer ALU V pipeline Integer ALU Pipelined Floating-Point Unit Register Multiply Set Add Divide Data Cache PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 5

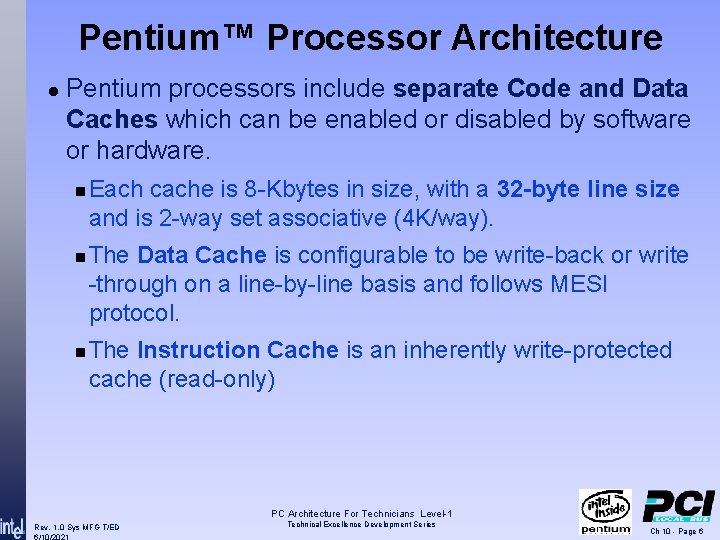

Pentium™ Processor Architecture l Pentium processors include separate Code and Data Caches which can be enabled or disabled by software or hardware. n n n Each cache is 8 -Kbytes in size, with a 32 -byte line size and is 2 -way set associative (4 K/way). The Data Cache is configurable to be write-back or write -through on a line-by-line basis and follows MESI protocol. The Instruction Cache is an inherently write-protected cache (read-only) PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 6

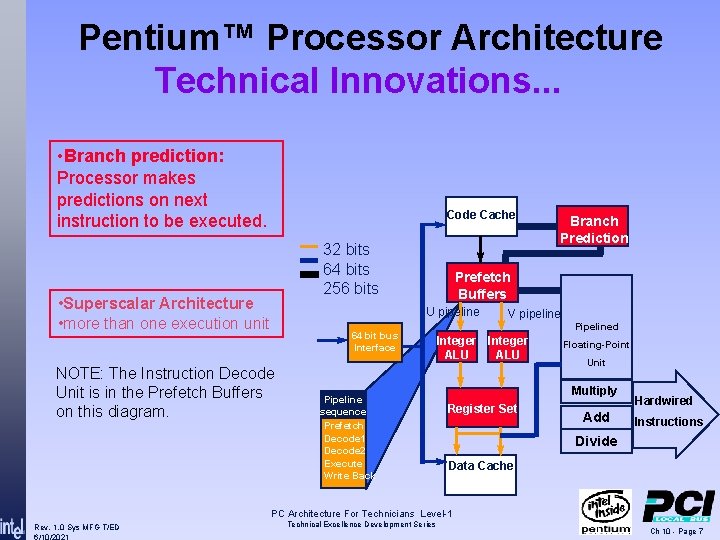

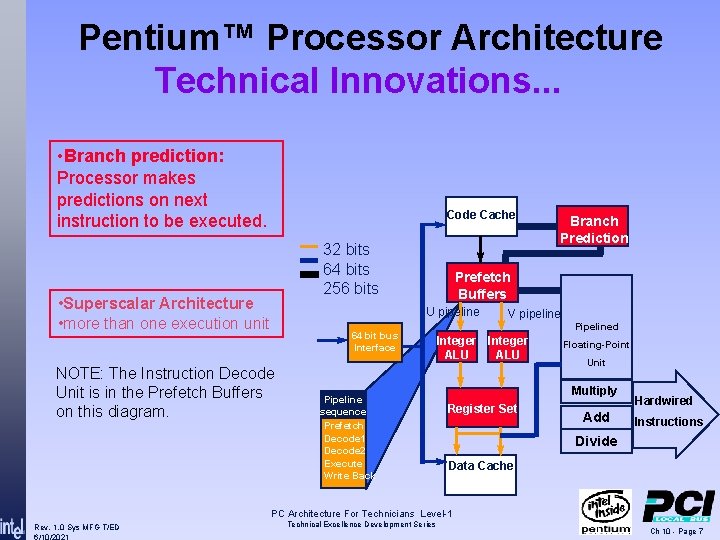

Pentium™ Processor Architecture Technical Innovations. . . • Branch prediction: Processor makes predictions on next instruction to be executed. Code Cache 32 bits 64 bits 256 bits • Superscalar Architecture • more than one execution unit Prefetch Buffers U pipeline 64 bit bus Interface NOTE: The Instruction Decode Unit is in the Prefetch Buffers on this diagram. Branch Prediction Pipeline sequence Prefetch Decode 1 Decode 2 Execute Write Back V pipeline Integer ALU Pipelined Floating-Point Unit Multiply Register Set Add Hardwired Instructions Divide Data Cache PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 7

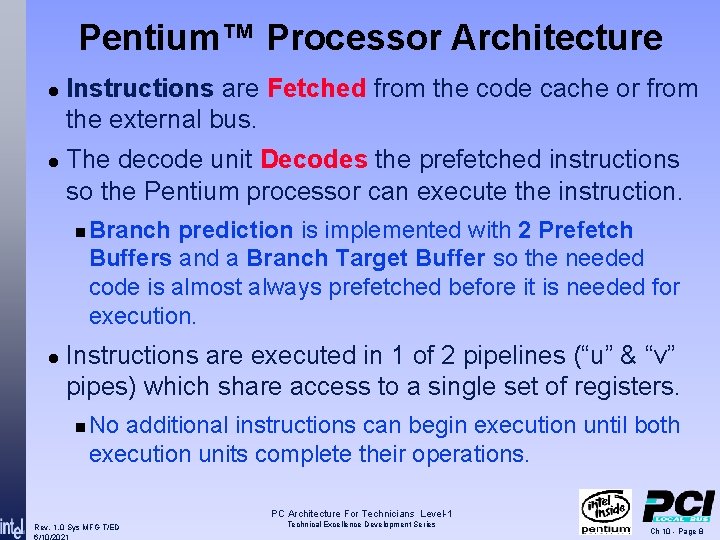

Pentium™ Processor Architecture l l Instructions are Fetched from the code cache or from the external bus. The decode unit Decodes the prefetched instructions so the Pentium processor can execute the instruction. n l Branch prediction is implemented with 2 Prefetch Buffers and a Branch Target Buffer so the needed code is almost always prefetched before it is needed for execution. Instructions are executed in 1 of 2 pipelines (“u” & “v” pipes) which share access to a single set of registers. n No additional instructions can begin execution until both execution units complete their operations. PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 8

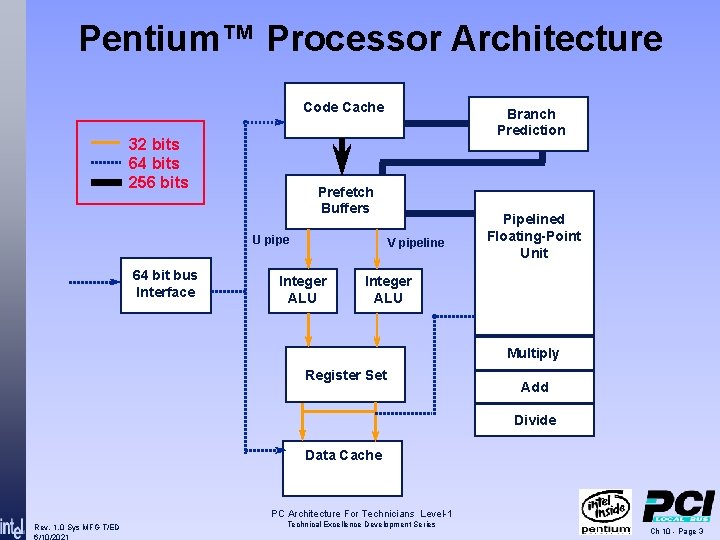

Pentium™ Processor Architecture l Pentium processors have two instruction pipelines. n n n l The u-pipe can Execute all integer and floating point instructions. The v-pipe can Execute simple integer instructions and the floating-point instructions. Pairing instructions in these two pipes enables the Pentium to operate on 2 instructions at the same time (Superscaler execution). The Control ROM unit has direct control over both pipelines. n The Control ROM contains microcode which controls the sequence of operations that must be performed. PC Architecture For Technicians Level-1 Rev. 1. 0 Sys MFG T/ED Technical Excellence Development Series Ch 10 - Page 9