Processor Processor characterized by 01 Oct01 register set

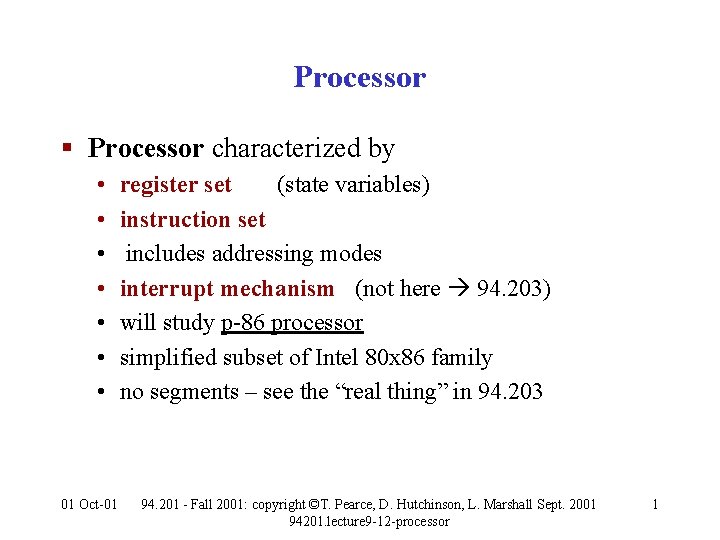

Processor § Processor characterized by • • 01 Oct-01 register set (state variables) instruction set includes addressing modes interrupt mechanism (not here 94. 203) will study p-86 processor simplified subset of Intel 80 x 86 family no segments – see the “real thing” in 94. 203 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 1

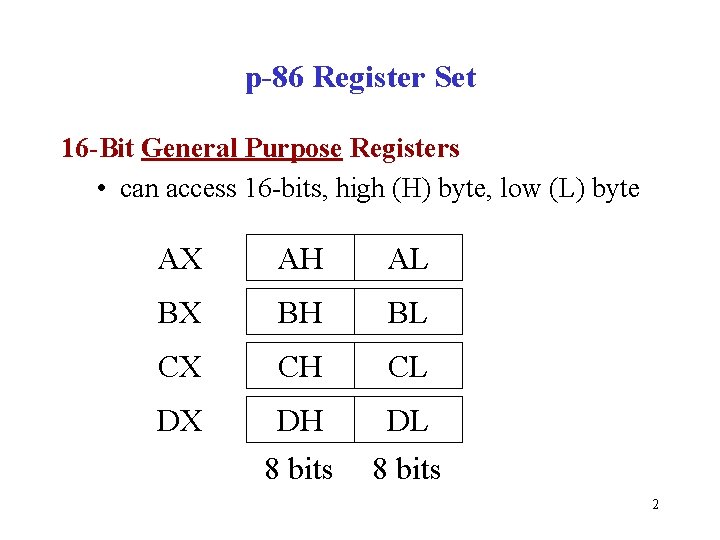

p-86 Register Set 16 -Bit General Purpose Registers • can access 16 -bits, high (H) byte, low (L) byte AX AH AL BX BH BL CX CH CL DX DH 8 bits DL 8 bits 2

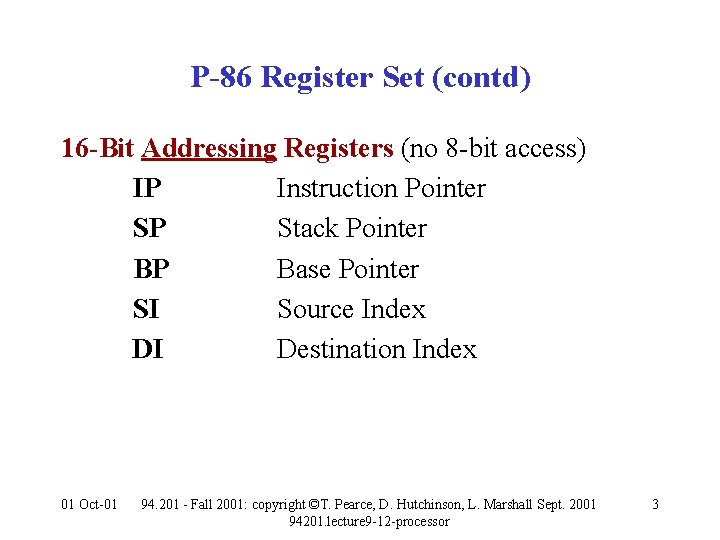

P-86 Register Set (contd) 16 -Bit Addressing Registers (no 8 -bit access) IP Instruction Pointer SP Stack Pointer BP Base Pointer SI Source Index DI Destination Index 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 3

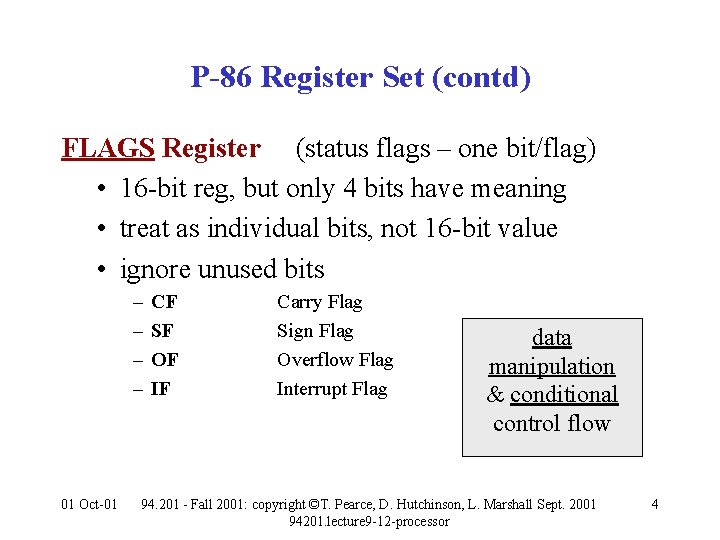

P-86 Register Set (contd) FLAGS Register (status flags – one bit/flag) • 16 -bit reg, but only 4 bits have meaning • treat as individual bits, not 16 -bit value • ignore unused bits – – 01 Oct-01 CF SF OF IF Carry Flag Sign Flag Overflow Flag Interrupt Flag data manipulation & conditional control flow 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 4

P-86 Register Set (contd) Other Registers in Programmer’s Model • • IR 01 Oct-01 support the execution of instructions cannot be accessed directly by programmers often larger than 16 -bits temporary reg’s (scratchpad values) Instruction Register 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 5

P-86 Execution Cycle Processor executes instructions by repeating: do { IR : = mem[ IP ] & adjust IP to point to next sequential instruction Execute instruction in IR } until HLT instruction has been executed 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 6

P-86 Execution Cycle (contd) § § IP contains address of next instruction to execute IR holds instruction in processor instruction fetch from memory load 1 st byte; from encoding: decide how many more are needed (may need 2 nd byte too!) § IP is adjusted as bytes are loaded 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 7

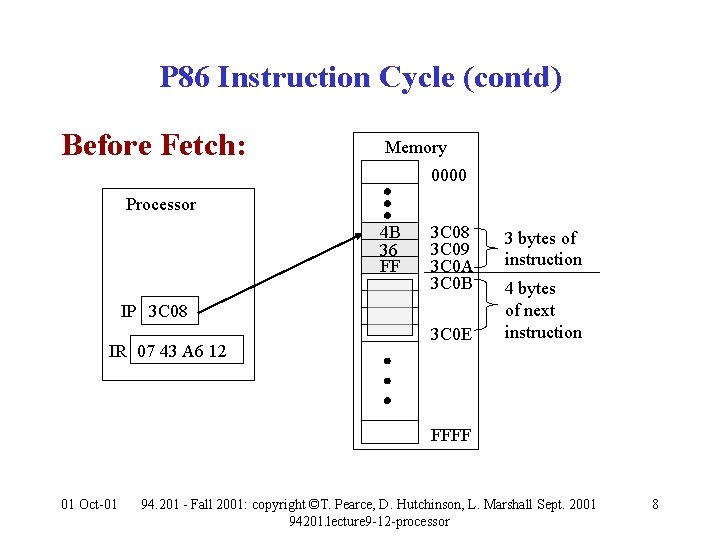

P 86 Instruction Cycle (contd) Before Fetch: Memory 0000 Processor 4 B 36 FF 3 C 08 3 C 09 3 C 0 A 3 C 0 B IP 3 C 08 IR 07 43 A 6 12 3 C 0 E 3 bytes of instruction 4 bytes of next instruction FFFF 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 8

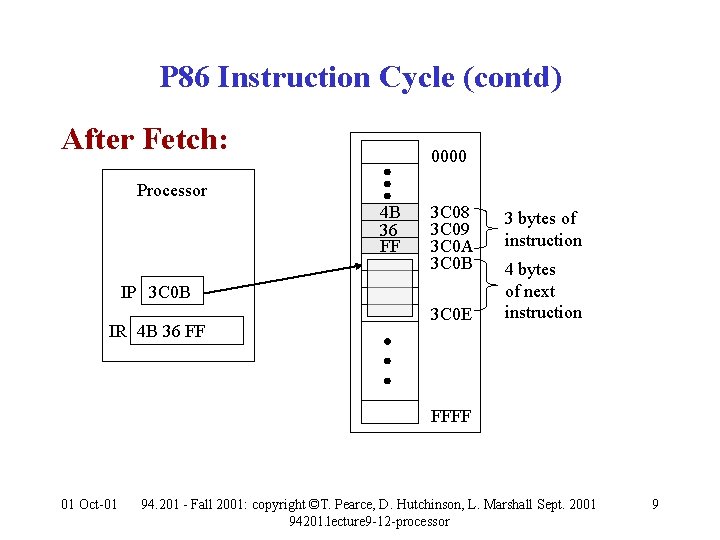

P 86 Instruction Cycle (contd) After Fetch: 0000 Processor 4 B 36 FF 3 C 08 3 C 09 3 C 0 A 3 C 0 B IP 3 C 0 B IR 4 B 36 FF 3 C 0 E 3 bytes of instruction 4 bytes of next instruction FFFF 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 9

Instruction Operations, Operands operation: how to use state variable values operands: which state variables to use e. g. C = A + B operations: addition (+) and assignment (=) operands: state variables A, B & C source operands: provide values to use (inputs) C = A + B; A= A + A destination operands: receive results (outputs) C = A + B; A = A + A 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 10

Instruction Operations, Operands (contd) § human-oriented mnemonics for operations e. g. : • MOV • SUB • JMP (move) (subtract) (jump) § addressing modes: ways to specify operands • simple modes: register, immediate, direct • more powerful: indirect § instruction encoding includes both operation and operand information 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 11

Instruction Categories § data transfer: copies data among state variables • do not modify FLAGS § data manipulation: modify state variable values – including FLAGS § control-flow: determine “next” instruction to execute – allow non-sequential execution 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 12

Data Transfer Example MOV (Move) Instruction syntax: MOV dest , src semantics: dest : = src § copy src value to dest state variable § register and memory operands only (I/O ? ? ) 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 13

Register Addressing Mode § allows a register to be an operand • as source: copy register value • as destination: write value to register e. g. MOV AX, DX ; value in DX is copied to AX : = DX § register addressing mode for both dest and src § dest and src must be compatible (same size) • MOV 01 Oct-01 AH, CL AL, CX ; This is OK ; This is not OK 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 14

Immediate Addressing Mode § allows constant to be specified as source • source value assembled into the instruction • loaded into IR as part of instruction • value obtained from IR as instruction executed e. g. MOV AL, 5 ; AL is 8 bit dest • instruction encoding includes 8 -bit value 05 h § what about: MOV AX, 5 • 16 -bit dest: encoding includes 16 -bit value 0005 h § what about MOV 4, BH ; lets be ridiculous • dest as immediate value ? 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 15

Direct Addressing Mode § specify the address of a memory operand • specify address as a constant value • address gets encoded as part of instruction • must be known when program is assembled ! § potential ambiguity? MOV AX, 3 FC 0 H • is 3 FC 0 H an immediate constant or address? • need syntax to clarify intention! • use square brackets “[” and “]” § [A] means A is the address of the operand MOV AX, 3 FC 0 H ; AX : = 3 FC 0 H MOV AX, [ 3 FC 0 H ] ; AX: = contents of cell 3 FC 0 H 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 16

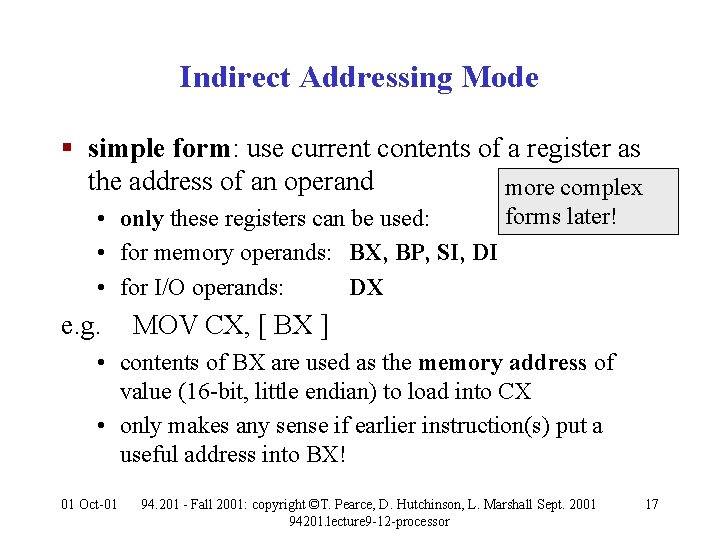

Indirect Addressing Mode § simple form: use current contents of a register as the address of an operand more complex forms later! • only these registers can be used: • for memory operands: BX, BP, SI, DI • for I/O operands: DX e. g. MOV CX, [ BX ] • contents of BX are used as the memory address of value (16 -bit, little endian) to load into CX • only makes any sense if earlier instruction(s) put a useful address into BX! 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 17

![Indirect Addressing Mode (contd) § potential ambiguity? MOV CX, [ BX ] v. s. Indirect Addressing Mode (contd) § potential ambiguity? MOV CX, [ BX ] v. s.](http://slidetodoc.com/presentation_image/e0a3a348833561e8f2c4c9f6aeb27bd5/image-18.jpg)

Indirect Addressing Mode (contd) § potential ambiguity? MOV CX, [ BX ] v. s. MOV CX, BX • • • 01 Oct-01 register, immediate and direct are static modes operand bound to instruction at assemble-time indirect is a dynamic mode operand bound to instruction at run-time depends on values at time instruction executed more powerful! more complicated! 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 18

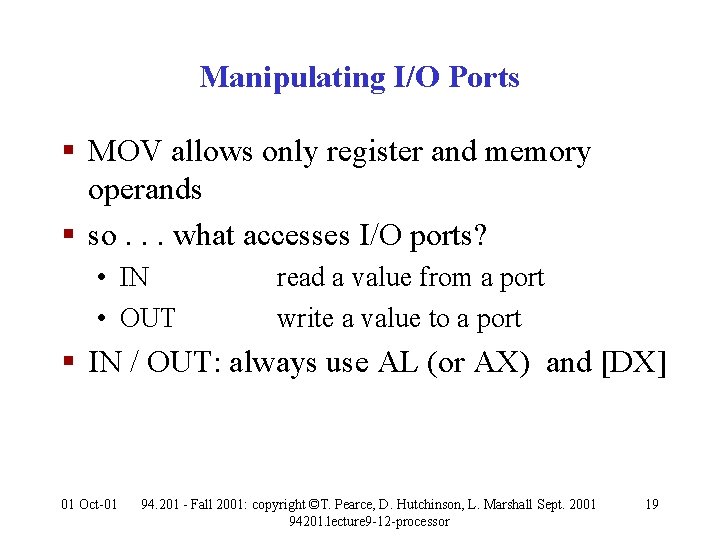

Manipulating I/O Ports § MOV allows only register and memory operands § so. . . what accesses I/O ports? • IN • OUT read a value from a port write a value to a port § IN / OUT: always use AL (or AX) and [DX] 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 19

![I/O Port Example § For now: OUT [DX], AL • the 8 -bit value I/O Port Example § For now: OUT [DX], AL • the 8 -bit value](http://slidetodoc.com/presentation_image/e0a3a348833561e8f2c4c9f6aeb27bd5/image-20.jpg)

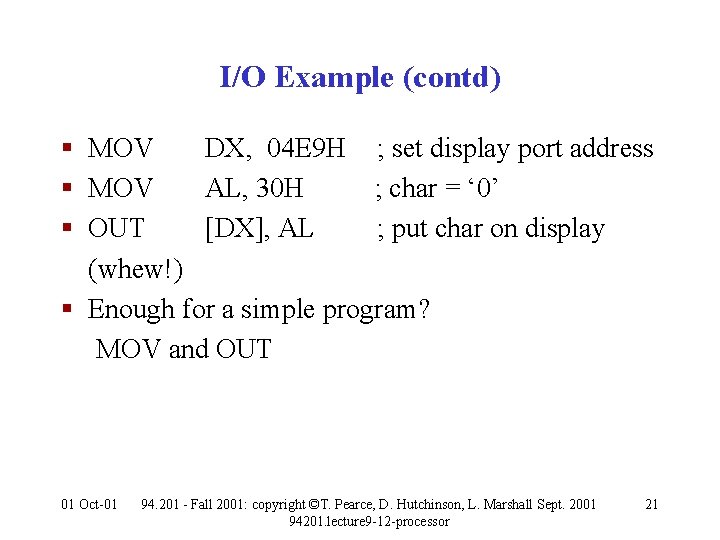

I/O Port Example § For now: OUT [DX], AL • the 8 -bit value in AL is written to the I/O port addressed by the contents of DX (indirect mode!) § Display character at the “current” cursor position: • write 7 -bit ASCII encoded char to port 04 E 9 H • must set up DX to point to I/O port • must set up AL to contain char • write: display char and “advance” cursor 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 20

I/O Example (contd) § MOV DX, 04 E 9 H ; set display port address § MOV AL, 30 H ; char = ‘ 0’ § OUT [DX], AL ; put char on display (whew!) § Enough for a simple program? MOV and OUT 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 21

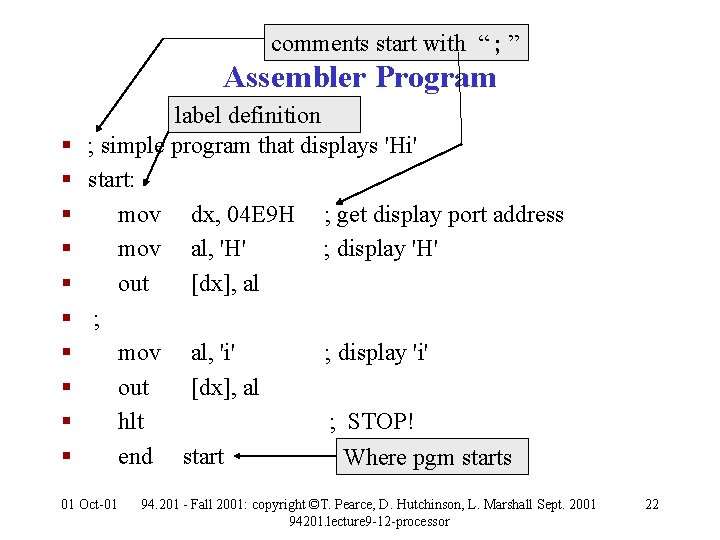

comments start with “ ; ” Assembler Program § § § § § label definition ; simple program that displays 'Hi' start: mov dx, 04 E 9 H ; get display port address mov al, 'H' ; display 'H' out [dx], al ; mov al, 'i' ; display 'i' out [dx], al hlt ; STOP! end start Where pgm starts 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 22

Assembler Program § above is “source” code – human-oriented § must be converted to binary values for loading into memory § ASSEMBLER is a program that encodes / translates this sort of repr. of a program into the internal repr. required to run it. § CROSS ASSEMBLERS translate into internal repr. for different machines 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 23

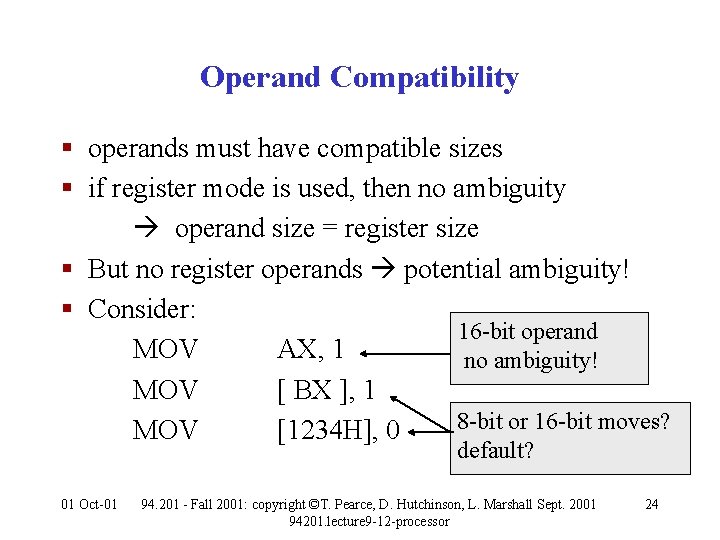

Operand Compatibility § operands must have compatible sizes § if register mode is used, then no ambiguity operand size = register size § But no register operands potential ambiguity! § Consider: 16 -bit operand MOV AX, 1 no ambiguity! MOV [ BX ], 1 8 -bit or 16 -bit moves? MOV [1234 H], 0 default? 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 24

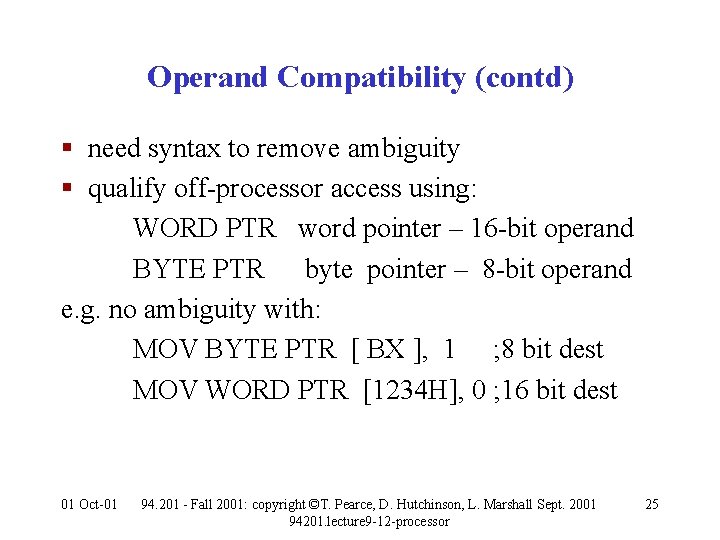

Operand Compatibility (contd) § need syntax to remove ambiguity § qualify off-processor access using: WORD PTR word pointer – 16 -bit operand BYTE PTR byte pointer – 8 -bit operand e. g. no ambiguity with: MOV BYTE PTR [ BX ], 1 ; 8 bit dest MOV WORD PTR [1234 H], 0 ; 16 bit dest 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 25

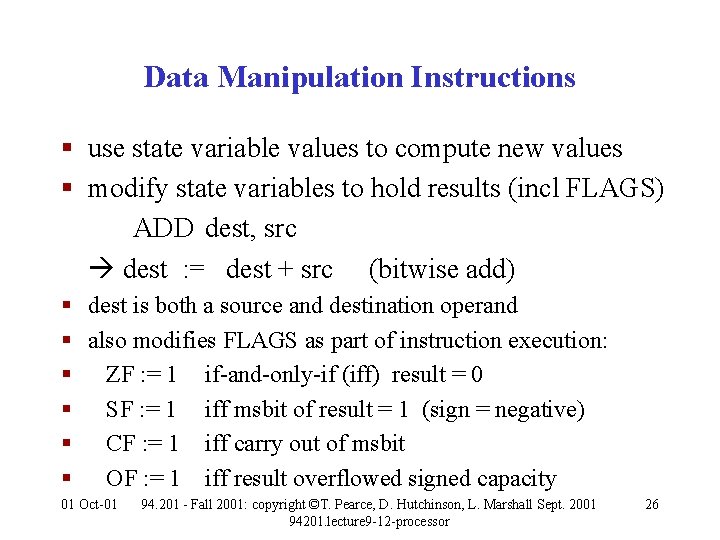

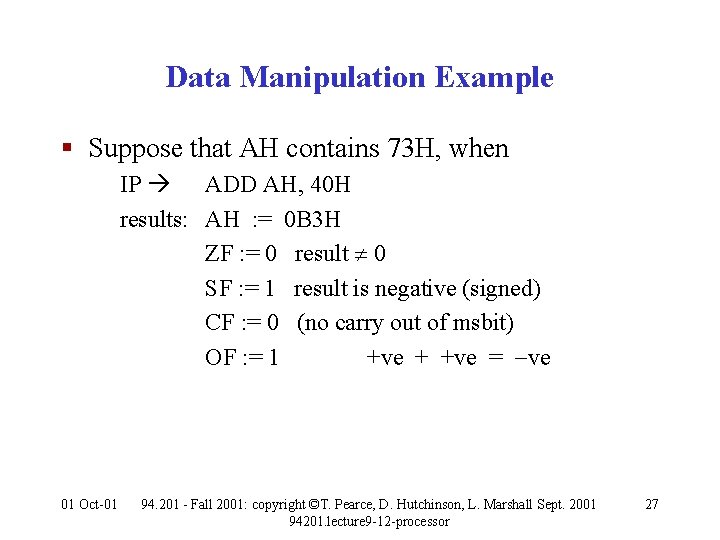

Data Manipulation Instructions § use state variable values to compute new values § modify state variables to hold results (incl FLAGS) ADD dest, src dest : = dest + src (bitwise add) § § § dest is both a source and destination operand also modifies FLAGS as part of instruction execution: ZF : = 1 if-and-only-if (iff) result = 0 SF : = 1 iff msbit of result = 1 (sign = negative) CF : = 1 iff carry out of msbit OF : = 1 iff result overflowed signed capacity 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 26

Data Manipulation Example § Suppose that AH contains 73 H, when IP ADD AH, 40 H results: AH : = 0 B 3 H ZF : = 0 result 0 SF : = 1 result is negative (signed) CF : = 0 (no carry out of msbit) OF : = 1 +ve + +ve = ve 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 27

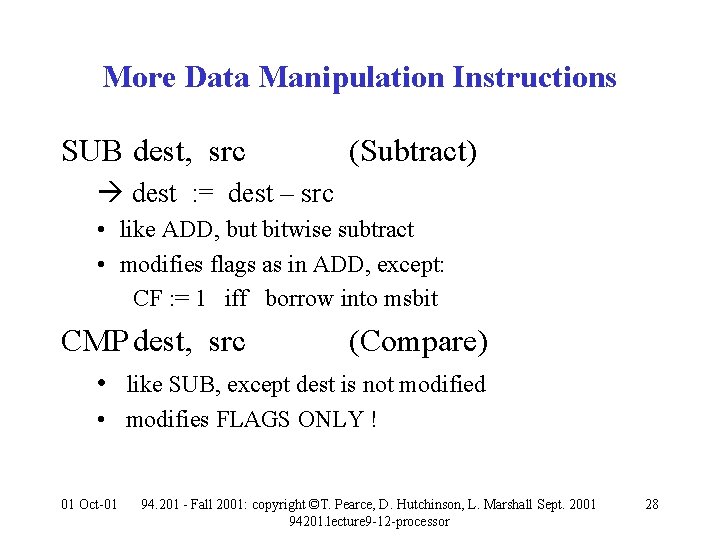

More Data Manipulation Instructions SUB dest, src (Subtract) dest : = dest – src • like ADD, but bitwise subtract • modifies flags as in ADD, except: CF : = 1 iff borrow into msbit CMP dest, src (Compare) • like SUB, except dest is not modified • modifies FLAGS ONLY ! 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 28

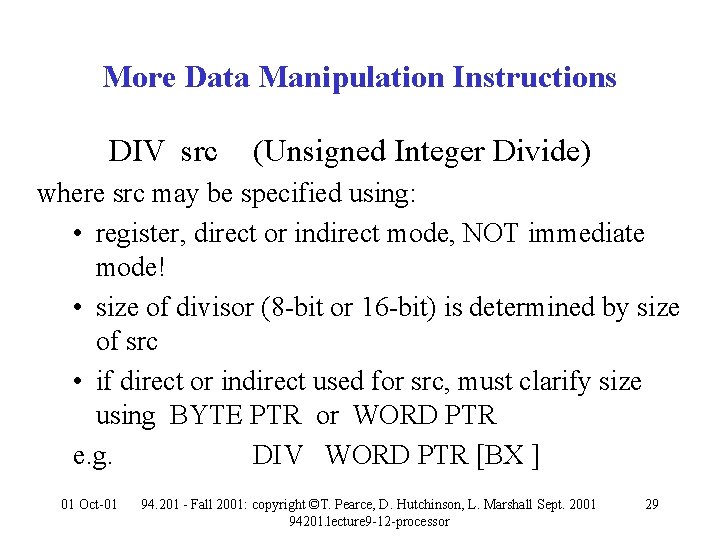

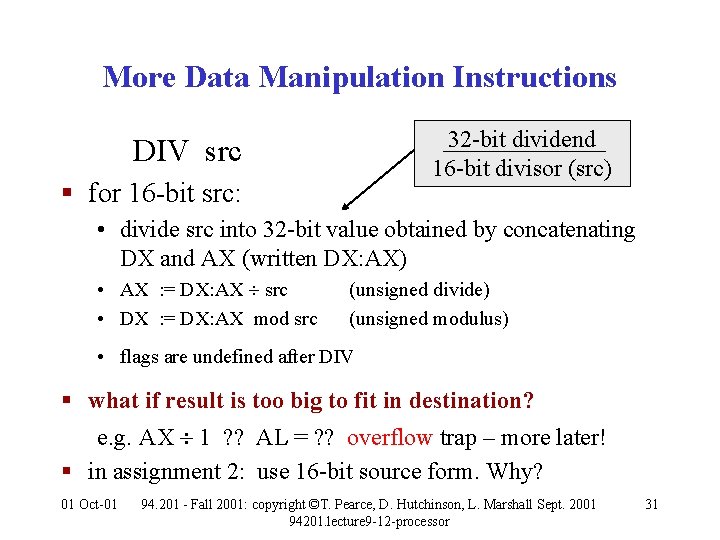

More Data Manipulation Instructions DIV src (Unsigned Integer Divide) where src may be specified using: • register, direct or indirect mode, NOT immediate mode! • size of divisor (8 -bit or 16 -bit) is determined by size of src • if direct or indirect used for src, must clarify size using BYTE PTR or WORD PTR e. g. DIV WORD PTR [BX ] 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 29

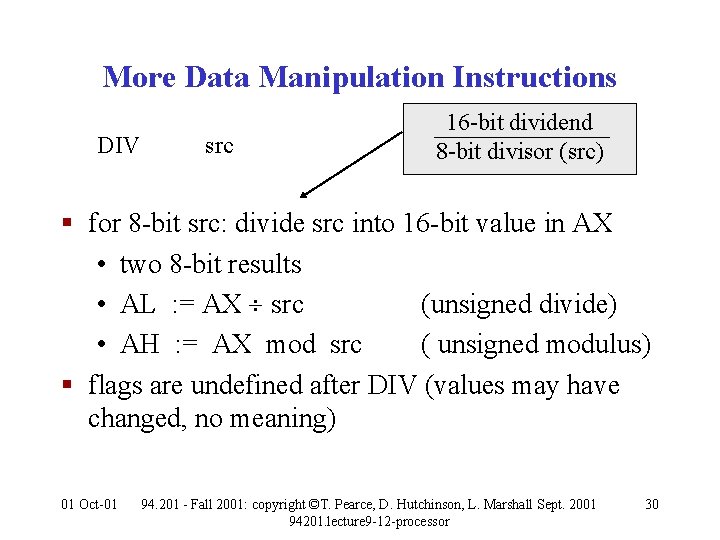

More Data Manipulation Instructions DIV src 16 -bit dividend 8 -bit divisor (src) § for 8 -bit src: divide src into 16 -bit value in AX • two 8 -bit results • AL : = AX src (unsigned divide) • AH : = AX mod src ( unsigned modulus) § flags are undefined after DIV (values may have changed, no meaning) 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 30

More Data Manipulation Instructions DIV src § for 16 -bit src: 32 -bit dividend 16 -bit divisor (src) • divide src into 32 -bit value obtained by concatenating DX and AX (written DX: AX) • AX : = DX: AX src (unsigned divide) • DX : = DX: AX mod src (unsigned modulus) • flags are undefined after DIV § what if result is too big to fit in destination? e. g. AX 1 ? ? AL = ? ? overflow trap – more later! § in assignment 2: use 16 -bit source form. Why? 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 31

Control Flow Instructions See Instruction Reference (posted) for more complete list of instructions – includes effects on FLAGS !! § execution may change value in IP § changes address for fetch of next instruction 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 32

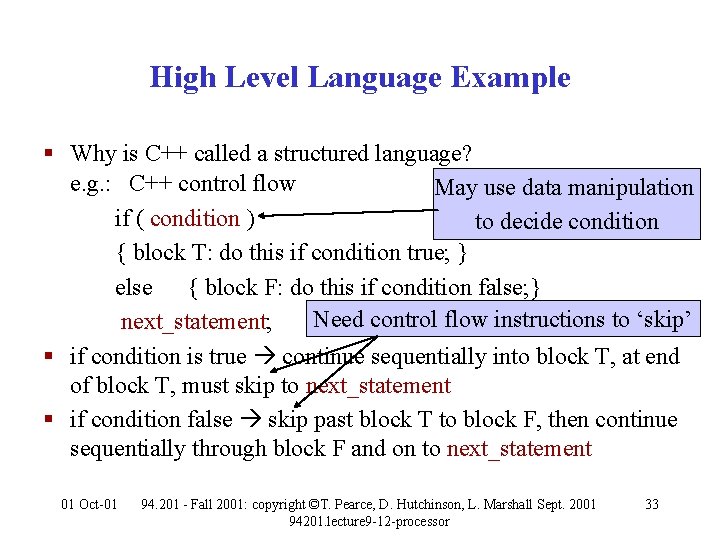

High Level Language Example § Why is C++ called a structured language? e. g. : C++ control flow May use data manipulation if ( condition ) to decide condition { block T: do this if condition true; } else { block F: do this if condition false; } next_statement; Need control flow instructions to ‘skip’ § if condition is true continue sequentially into block T, at end of block T, must skip to next_statement § if condition false skip past block T to block F, then continue sequentially through block F and on to next_statement 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 33

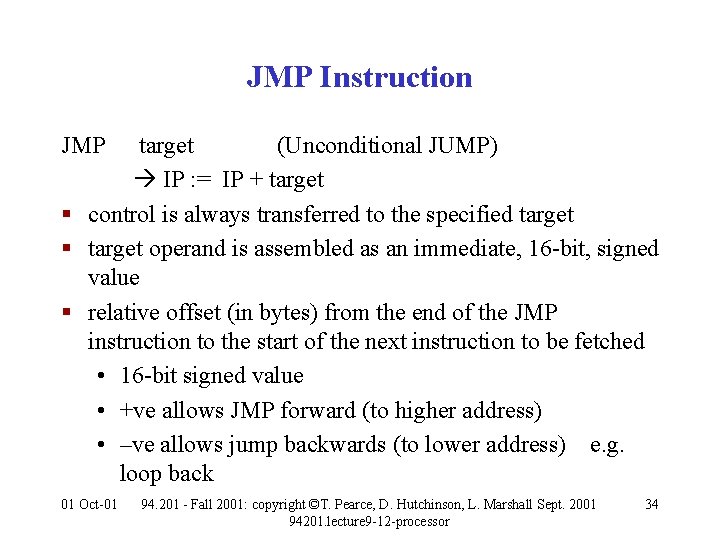

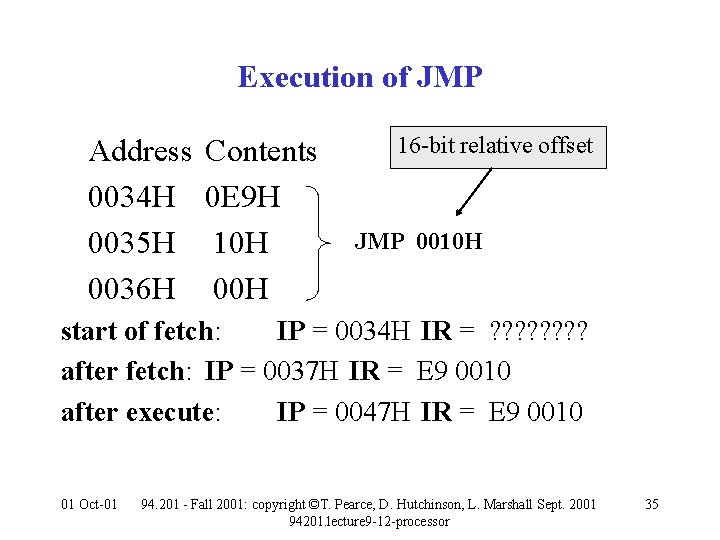

JMP Instruction JMP target (Unconditional JUMP) IP : = IP + target § control is always transferred to the specified target § target operand is assembled as an immediate, 16 -bit, signed value § relative offset (in bytes) from the end of the JMP instruction to the start of the next instruction to be fetched • 16 -bit signed value • +ve allows JMP forward (to higher address) • –ve allows jump backwards (to lower address) e. g. loop back 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 34

Execution of JMP Address 0034 H 0035 H 0036 H Contents 0 E 9 H 10 H 00 H 16 -bit relative offset JMP 0010 H start of fetch: IP = 0034 H IR = ? ? ? ? after fetch: IP = 0037 H IR = E 9 0010 after execute: IP = 0047 H IR = E 9 0010 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 35

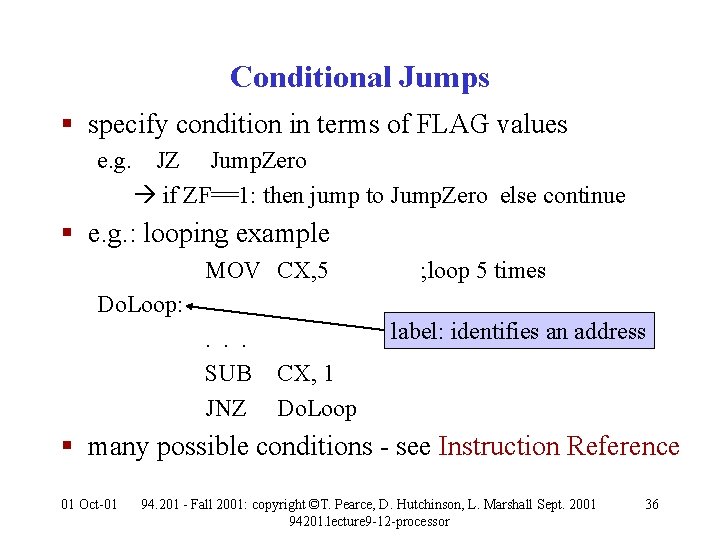

Conditional Jumps § specify condition in terms of FLAG values e. g. JZ Jump. Zero if ZF==1: then jump to Jump. Zero else continue § e. g. : looping example MOV CX, 5 ; loop 5 times Do. Loop: . . . SUB JNZ label: identifies an address CX, 1 Do. Loop § many possible conditions - see Instruction Reference 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 36

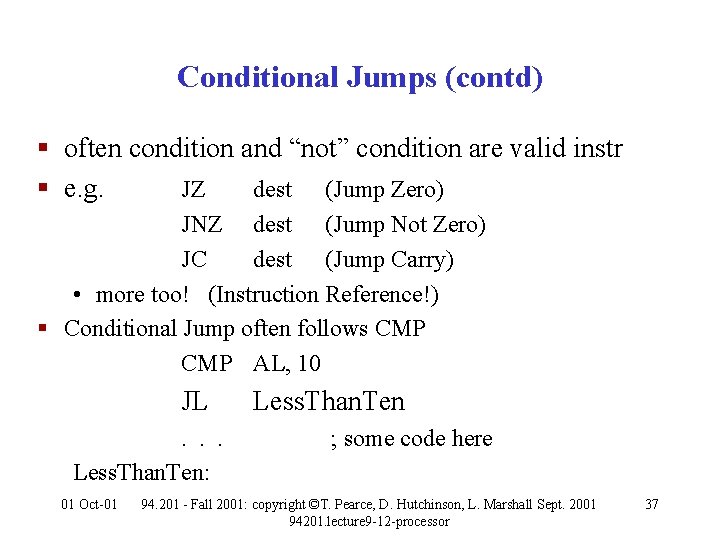

Conditional Jumps (contd) § often condition and “not” condition are valid instr § e. g. JZ dest (Jump Zero) JNZ dest (Jump Not Zero) JC dest (Jump Carry) • more too! (Instruction Reference!) § Conditional Jump often follows CMP AL, 10 JL Less. Than. Ten . . . Less. Than. Ten: 01 Oct-01 ; some code here 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 37

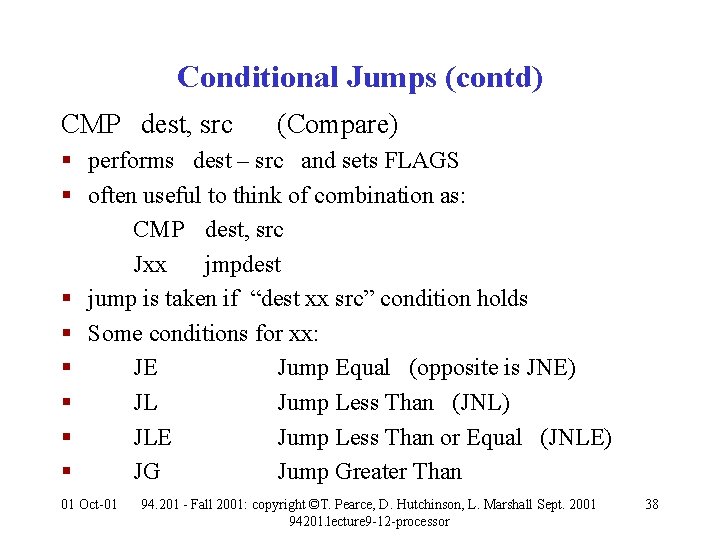

Conditional Jumps (contd) CMP dest, src (Compare) § performs dest – src and sets FLAGS § often useful to think of combination as: CMP dest, src Jxx jmpdest § jump is taken if “dest xx src” condition holds § Some conditions for xx: § JE Jump Equal (opposite is JNE) § JL Jump Less Than (JNL) § JLE Jump Less Than or Equal (JNLE) § JG Jump Greater Than 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 38

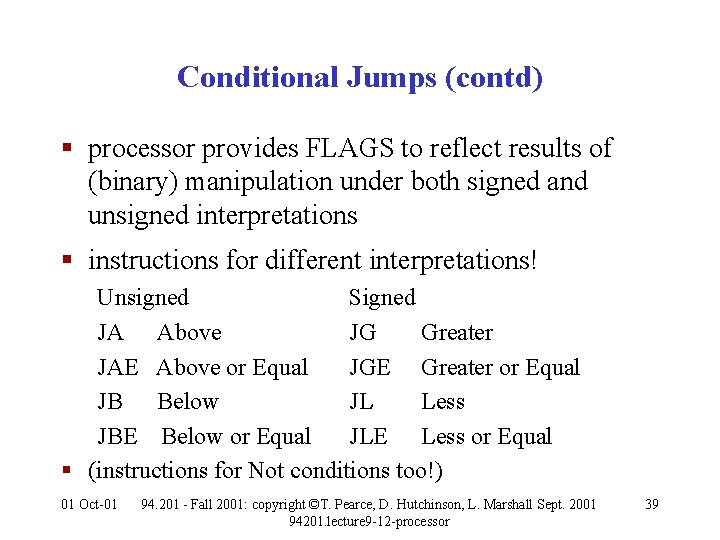

Conditional Jumps (contd) § processor provides FLAGS to reflect results of (binary) manipulation under both signed and unsigned interpretations § instructions for different interpretations! Unsigned Signed JA Above JG Greater JAE Above or Equal JGE Greater or Equal JB Below JL Less JBE Below or Equal JLE Less or Equal § (instructions for Not conditions too!) 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 39

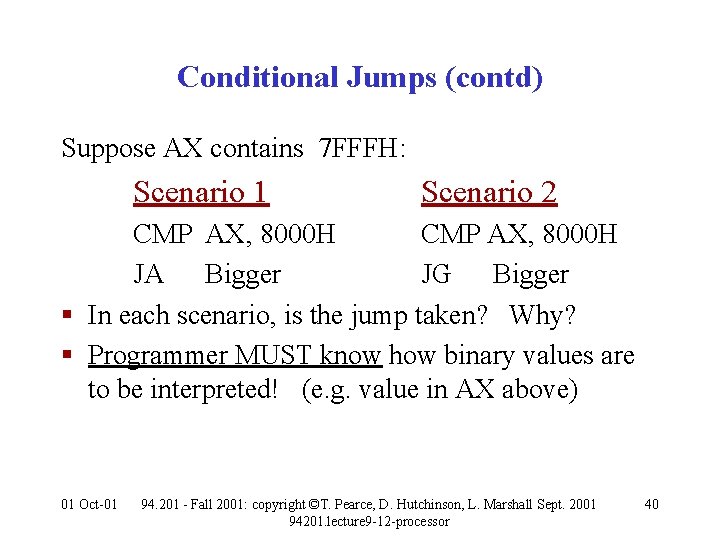

Conditional Jumps (contd) Suppose AX contains 7 FFFH: Scenario 1 Scenario 2 CMP AX, 8000 H JA Bigger JG Bigger § In each scenario, is the jump taken? Why? § Programmer MUST know how binary values are to be interpreted! (e. g. value in AX above) 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 40

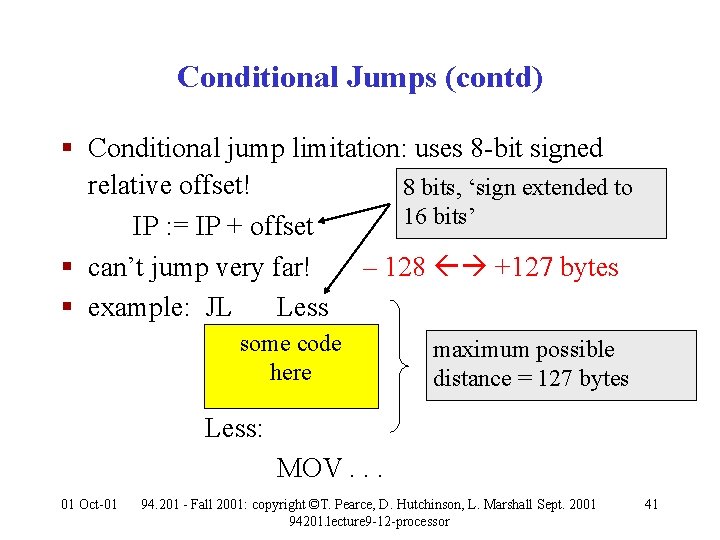

Conditional Jumps (contd) § Conditional jump limitation: uses 8 -bit signed relative offset! 8 bits, ‘sign extended to 16 bits’ IP : = IP + offset § can’t jump very far! – 128 +127 bytes § example: JL Less some code here maximum possible distance = 127 bytes Less: MOV. . . 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 41

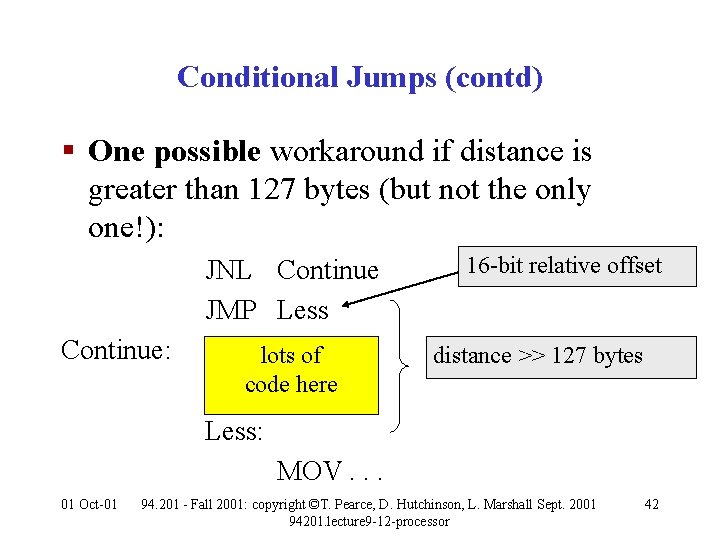

Conditional Jumps (contd) § One possible workaround if distance is greater than 127 bytes (but not the only one!): JNL Continue JMP Less Continue: lots of code here 16 -bit relative offset distance >> 127 bytes Less: MOV. . . 01 Oct-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94201. lecture 9 -12 -processor 42

- Slides: 42