Processor history 1 2 80868088 80286 1978 81

- Slides: 13

Processor history

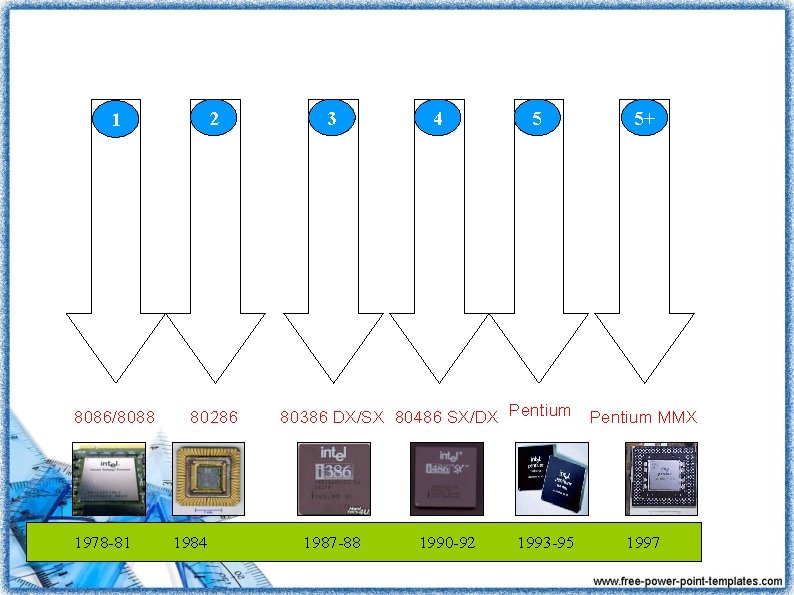

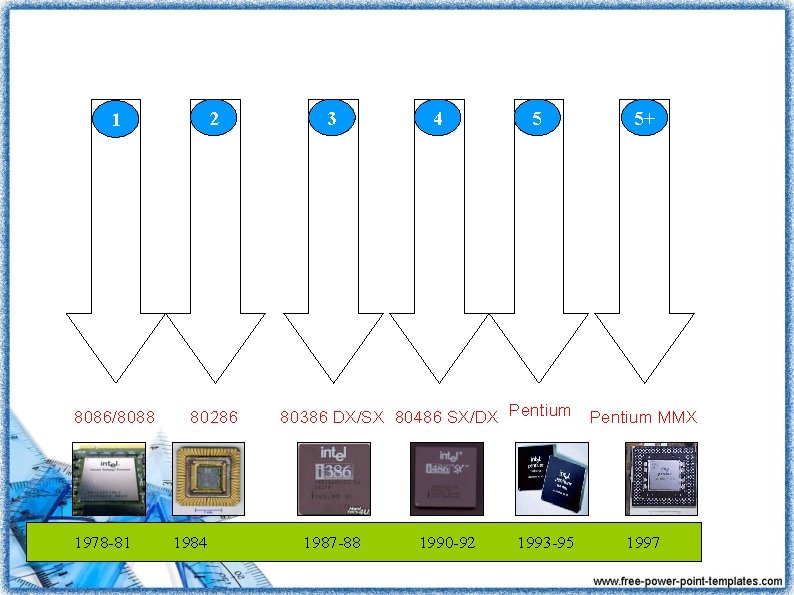

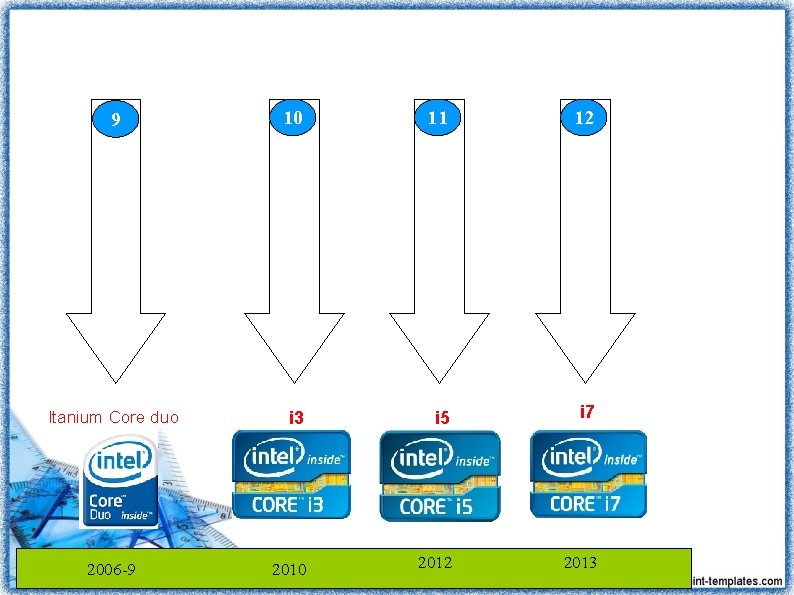

1 2 8086/8088 80286 1978 -81 1984 3 4 5 80386 DX/SX 80486 SX/DX Pentium 1987 -88 1990 -92 1993 -95 5+ Pentium MMX 1997

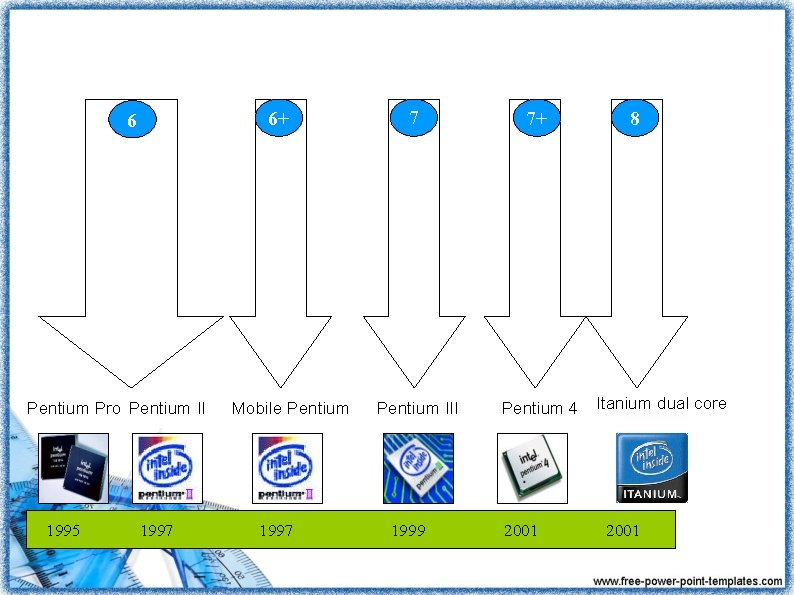

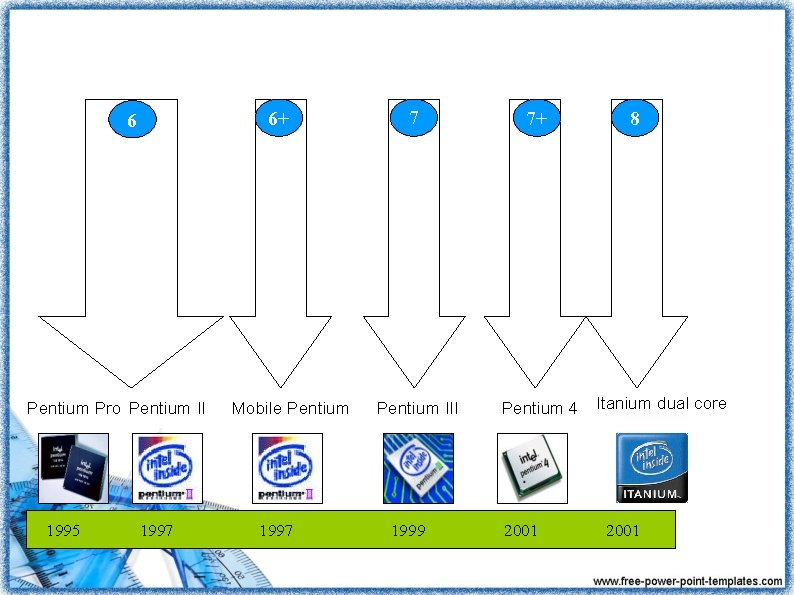

6+ 6 Pentium Pro Pentium II 1995 1997 Mobile Pentium 1997 7 7+ Pentium III Pentium 4 1999 2001 8 Itanium dual core 2001

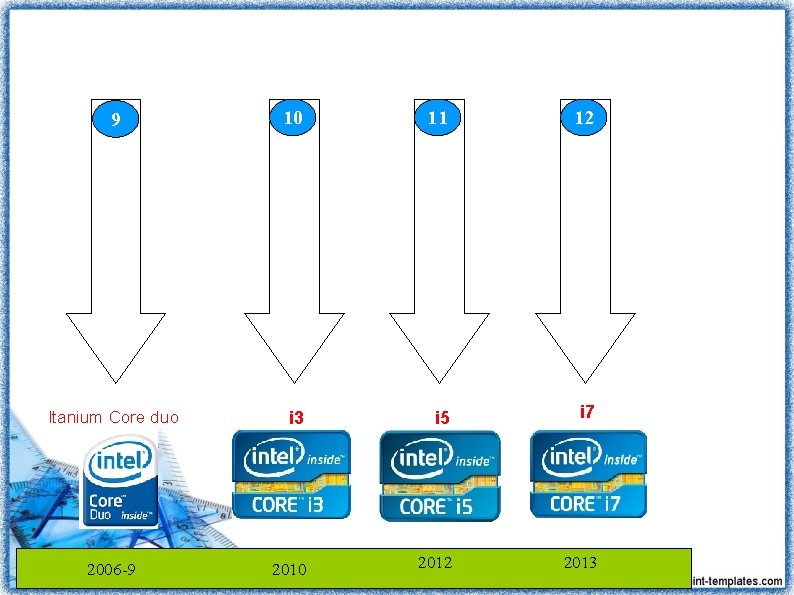

9 10 11 12 Itanium Core duo i 3 i 5 i 7 2010 2012 2013 2006 -9

i 3, i 5, i 7…. No. of cores- 2 – i 3 No. of cores- 4 – i 5. No. of cores- 4 – i 7

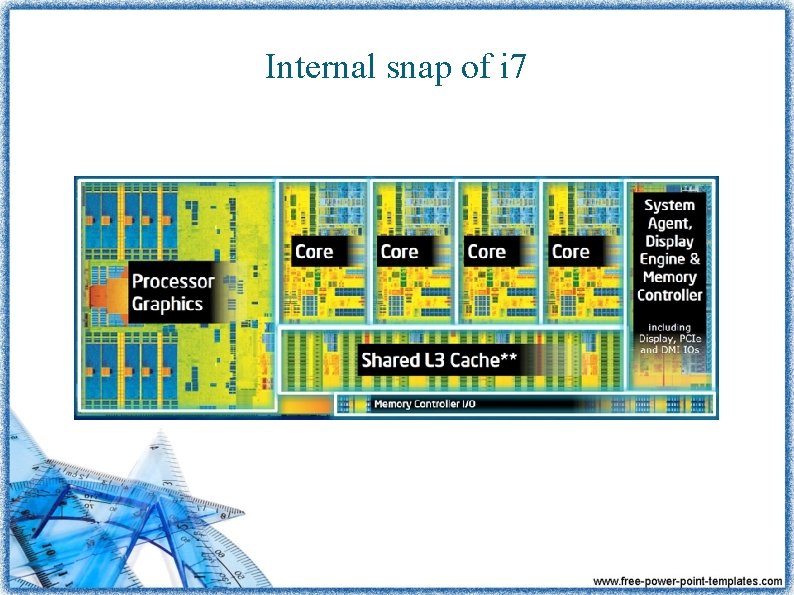

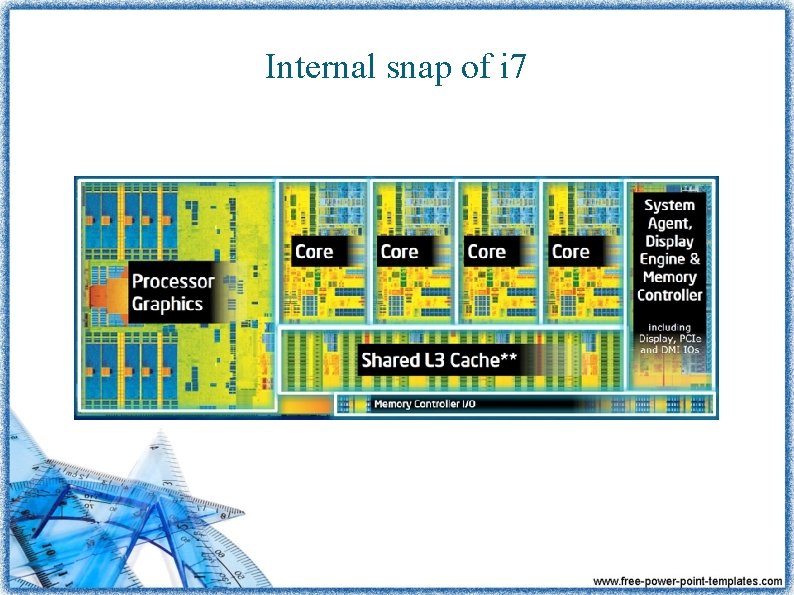

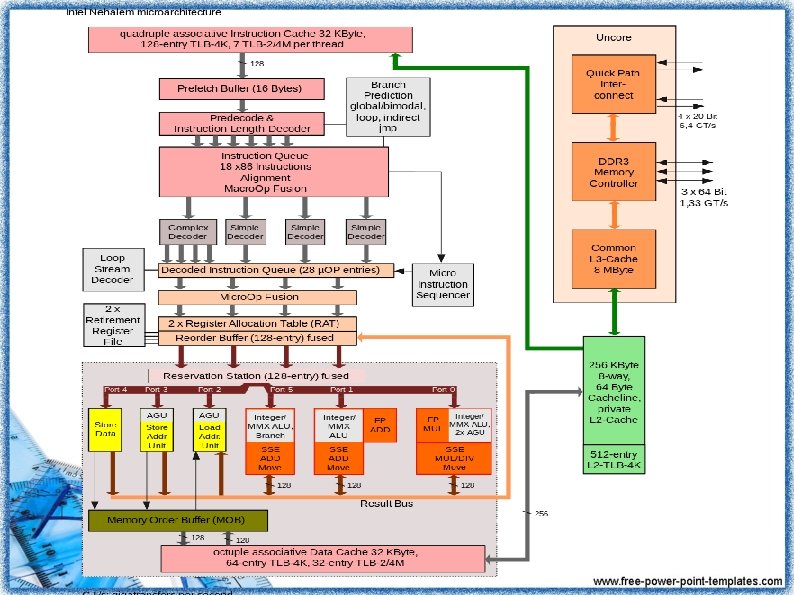

Internal snap of i 7

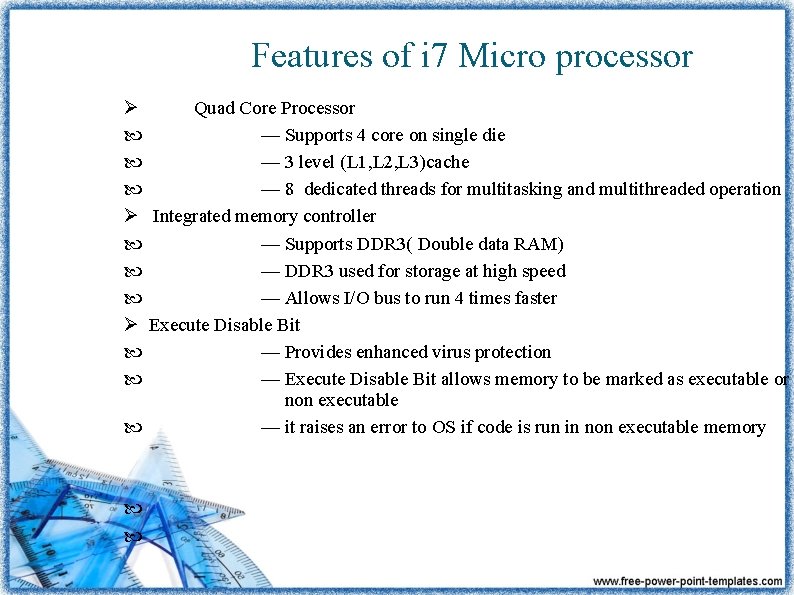

Features of i 7 Micro processor Ø Quad Core Processor — Supports 4 core on single die — 3 level (L 1, L 2, L 3)cache — 8 dedicated threads for multitasking and multithreaded operation Ø Integrated memory controller — Supports DDR 3( Double data RAM) — DDR 3 used for storage at high speed — Allows I/O bus to run 4 times faster Ø Execute Disable Bit — Provides enhanced virus protection — Execute Disable Bit allows memory to be marked as executable or non executable — it raises an error to OS if code is run in non executable memory

Features of i 7 Micro processor Ø Hyper threading technology — one physical processor seems like two logical processor — improves performance in multitasking — execution unit , caches, buses are shared —logical processor has data reg, segment reg, control reg, debug reg — i 7 processor can process 2 thread simultaneously — it appears to OS as 8 CPUs Ø Turbo Boost Technology — allows processor to run faster than base operating frequency — power of passives cores are provided to the active cores — it can increase frequency of all 4 cores till they can handle current payload — it does not require any hardware support — It can enable/disable by OS and BIOS

Features of i 7 Micro processor Ø Enhanced speed step technology — running processor at high clock speeds for better performance — If operating on low frequency, less heat generated then less power consumption Ø Intel Quick Path Interconnect(QPI) — used to link processor and system components — provide higher memory performance and flexibility — replaces front side bus — QPI high speed data transfer up to 25. 6 Gbps —Concurrent bi-directional traffic Ø Virtualization technology — one hardware platform to function a multiple virtual platform Ø Trusted Execution technology —hardware based mechanism to help protect against s/w based attacks —It helps to protect the confidentiality and integrity of data —by enabling trusted environment application can run in their own space

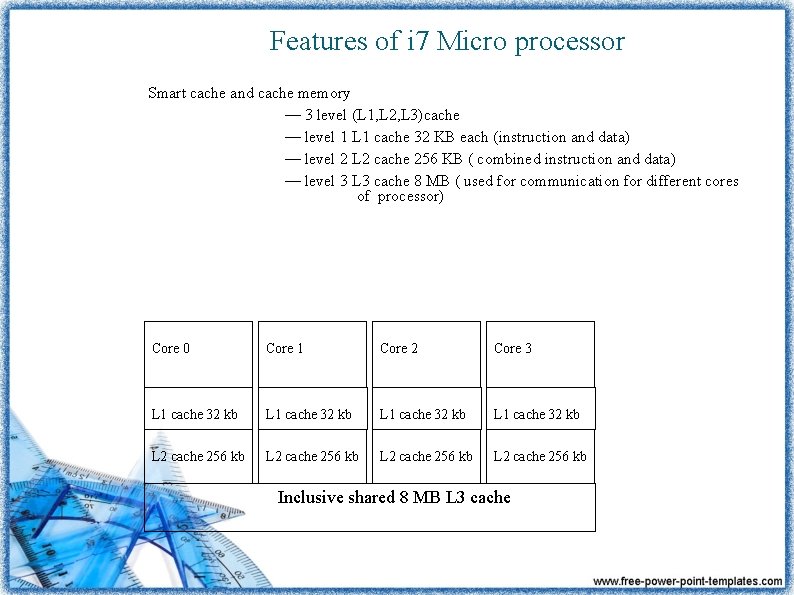

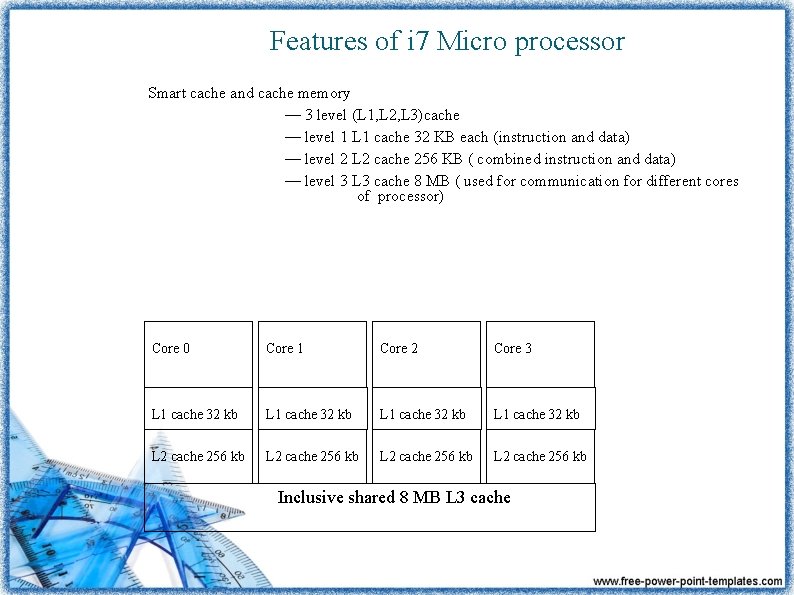

Features of i 7 Micro processor Smart cache and cache memory — 3 level (L 1, L 2, L 3)cache — level 1 L 1 cache 32 KB each (instruction and data) — level 2 L 2 cache 256 KB ( combined instruction and data) — level 3 L 3 cache 8 MB ( used for communication for different cores of processor) Core 0 Core 1 Core 2 Core 3 L 1 cache 32 kb L 2 cache 256 kb Inclusive shared 8 MB L 3 cache

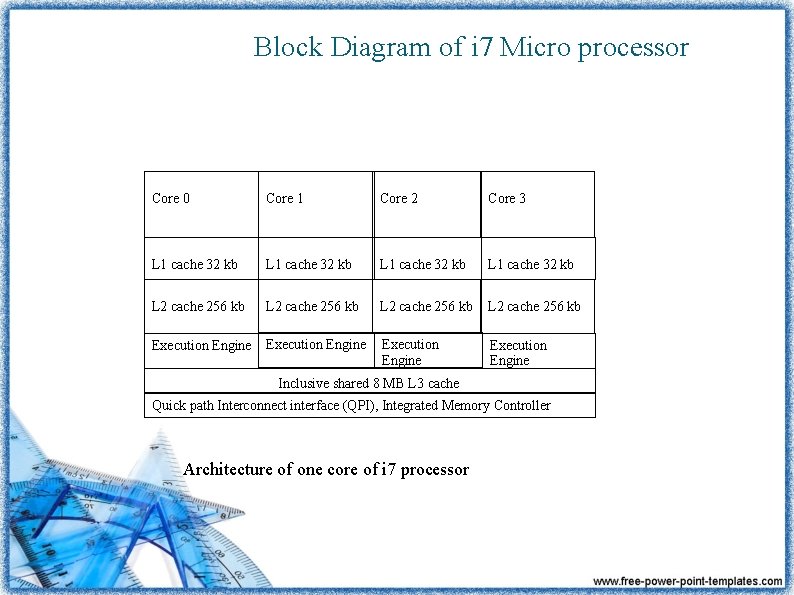

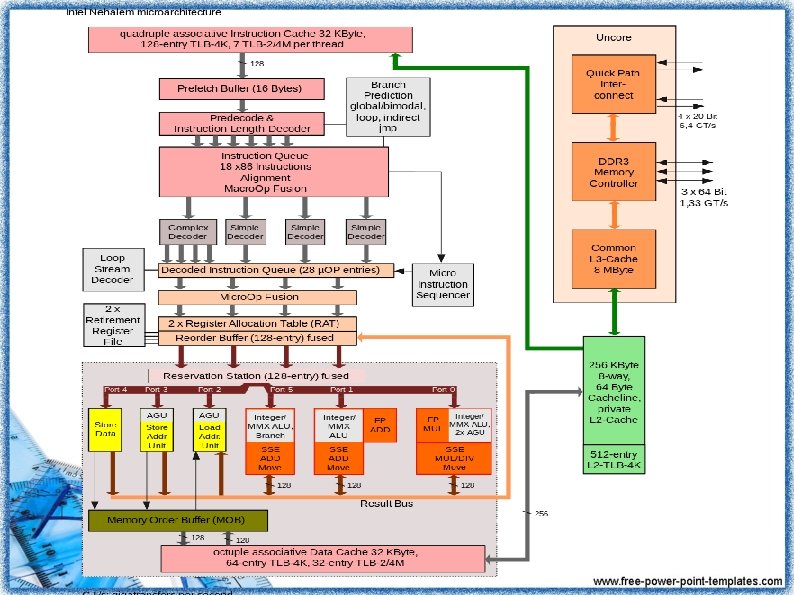

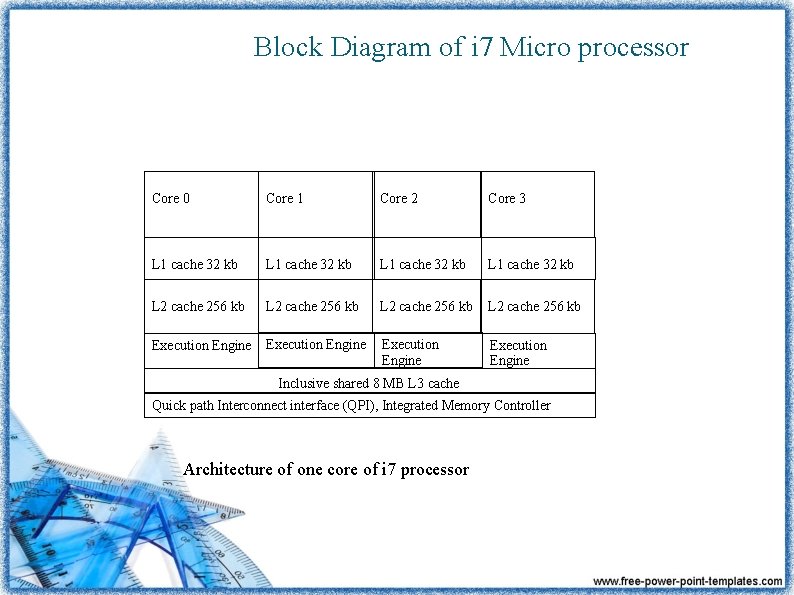

Block Diagram of i 7 Micro processor Core 0 Core 1 Core 2 Core 3 L 1 cache 32 kb L 2 cache 256 kb Execution Engine Inclusive shared 8 MB L 3 cache Quick path Interconnect interface (QPI), Integrated Memory Controller Architecture of one core of i 7 processor

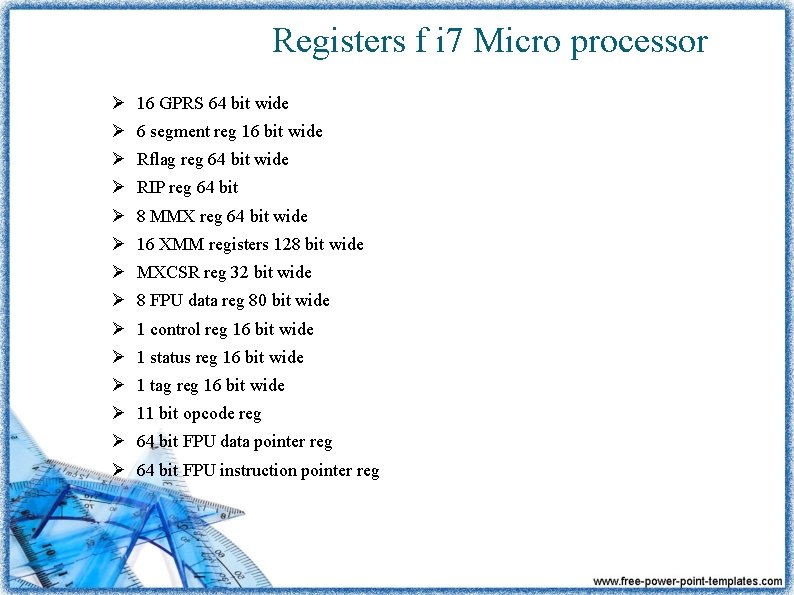

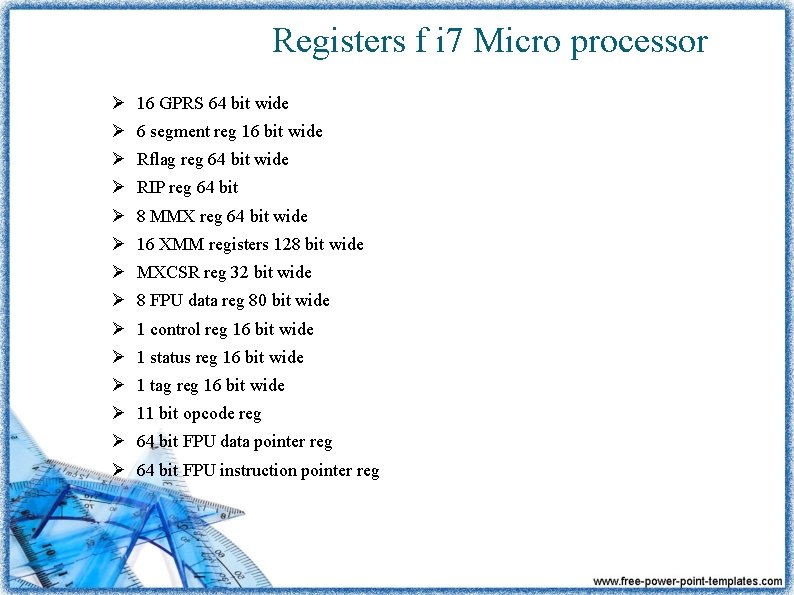

Registers f i 7 Micro processor Ø 16 GPRS 64 bit wide Ø 6 segment reg 16 bit wide Ø Rflag reg 64 bit wide Ø RIP reg 64 bit Ø 8 MMX reg 64 bit wide Ø 16 XMM registers 128 bit wide Ø MXCSR reg 32 bit wide Ø 8 FPU data reg 80 bit wide Ø 1 control reg 16 bit wide Ø 1 status reg 16 bit wide Ø 1 tag reg 16 bit wide Ø 11 bit opcode reg Ø 64 bit FPU data pointer reg Ø 64 bit FPU instruction pointer reg