Processor Data Paths ALU and Registers Incorporating the

- Slides: 22

Processor Data Paths ALU and Registers Incorporating the ALU into a Processor Data Path 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 1

L 4 – Incorporint ALU into data path o o o Building up the data path from the ALU Control of the data path Datapath Evolution 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 2

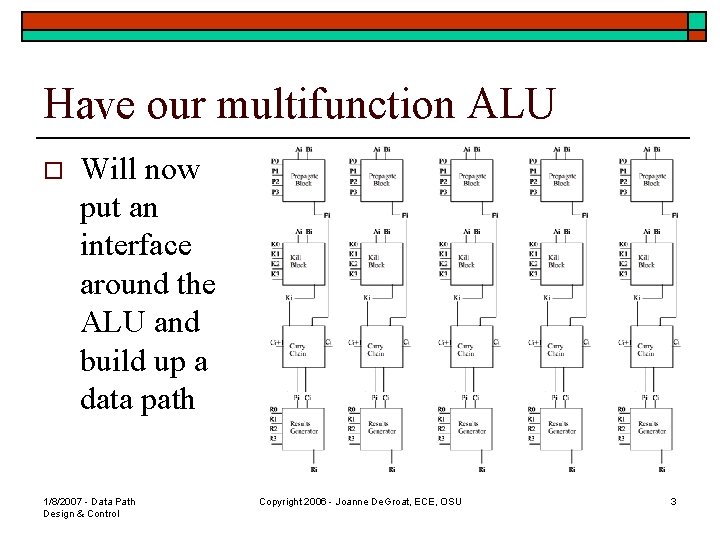

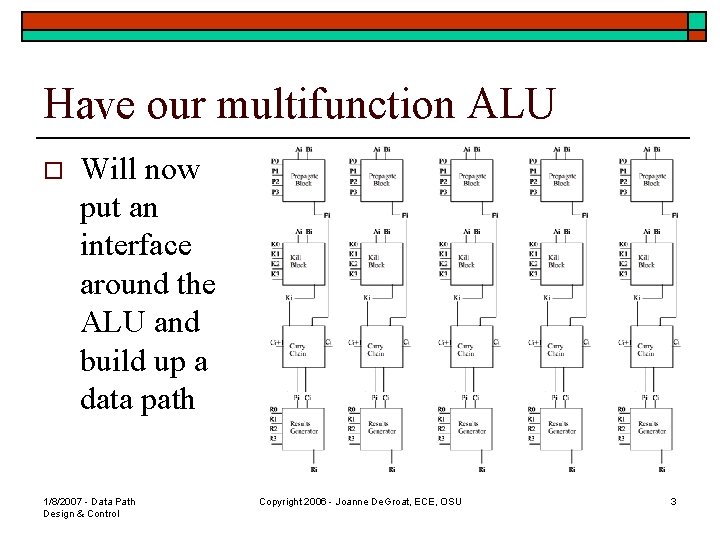

Have our multifunction ALU o Will now put an interface around the ALU and build up a data path 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 3

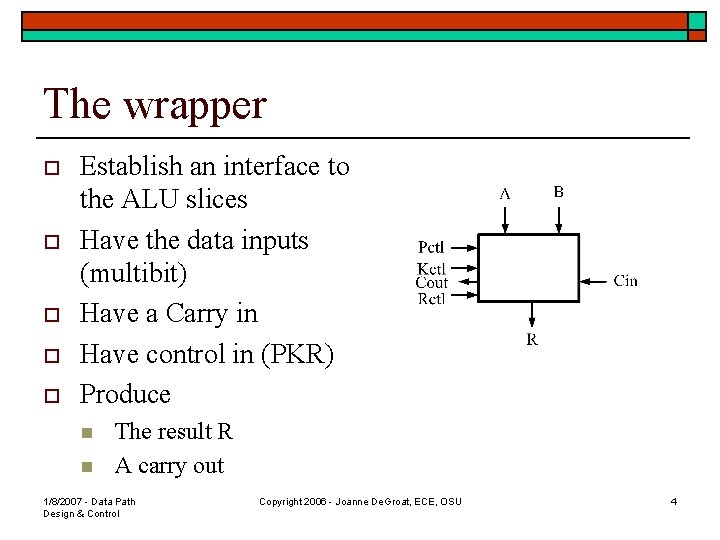

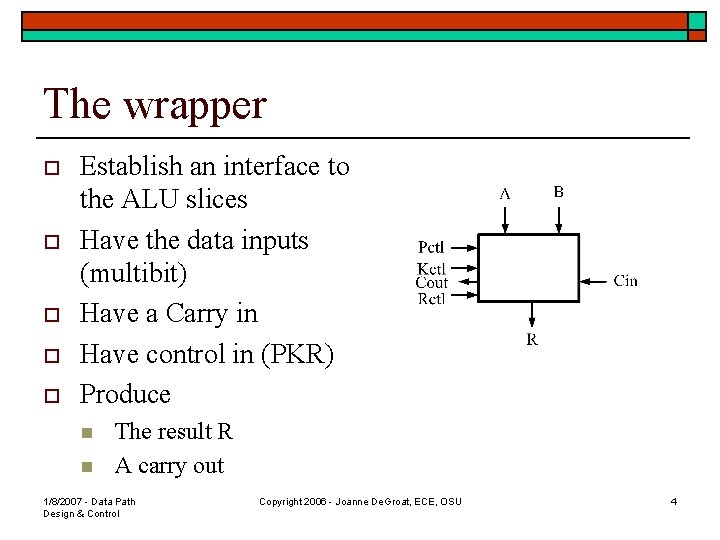

The wrapper o o o Establish an interface to the ALU slices Have the data inputs (multibit) Have a Carry in Have control in (PKR) Produce n n The result R A carry out 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 4

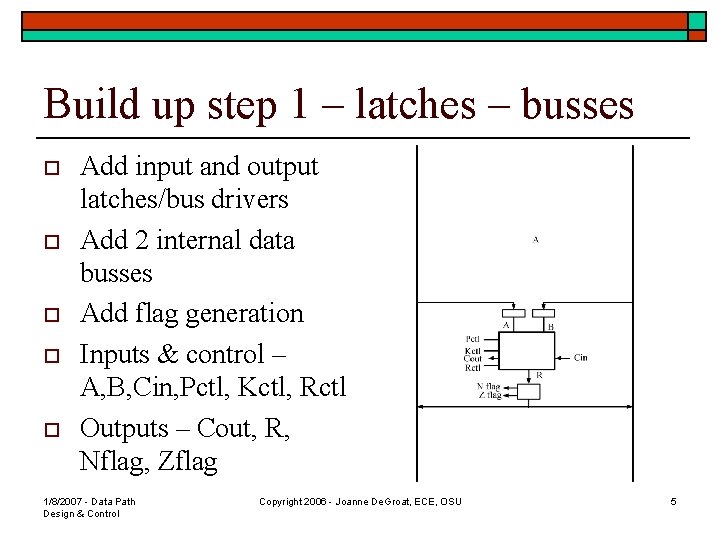

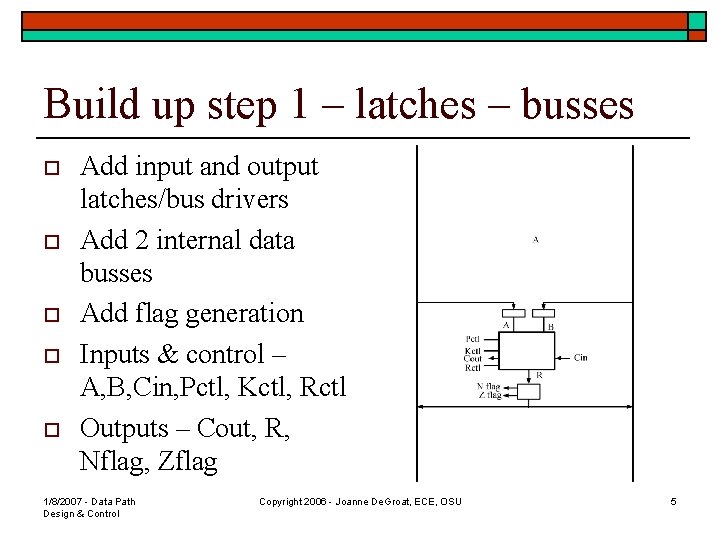

Build up step 1 – latches – busses o o o Add input and output latches/bus drivers Add 2 internal data busses Add flag generation Inputs & control – A, B, Cin, Pctl, Kctl, Rctl Outputs – Cout, R, Nflag, Zflag 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 5

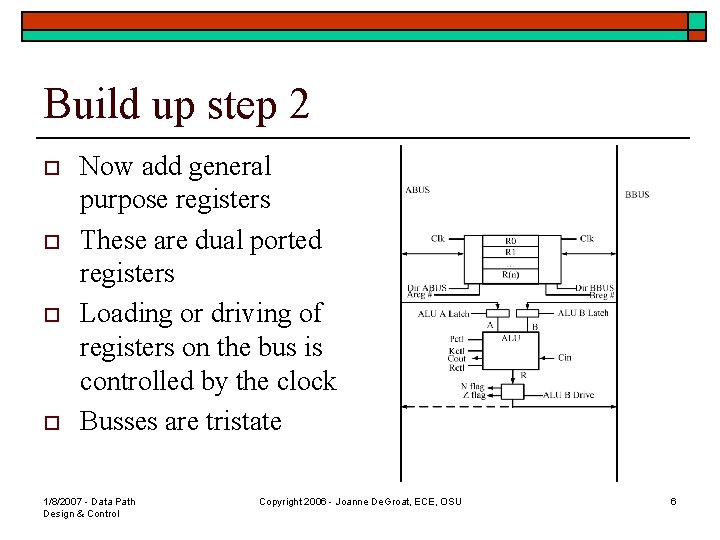

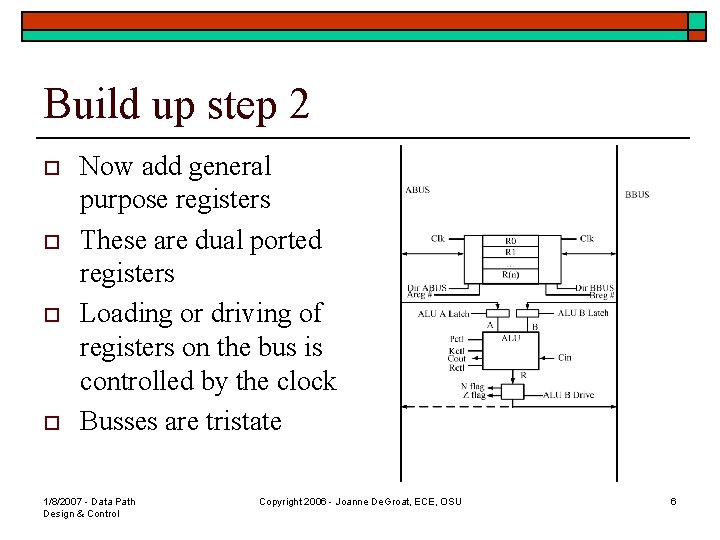

Build up step 2 o o Now add general purpose registers These are dual ported registers Loading or driving of registers on the bus is controlled by the clock Busses are tristate 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 6

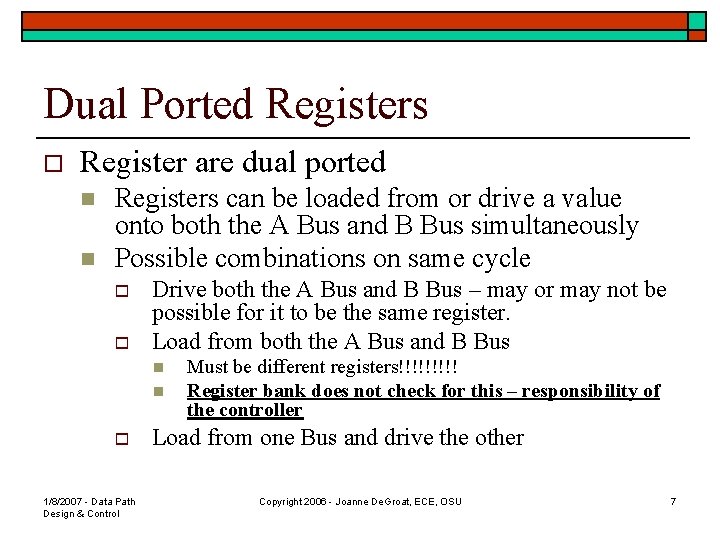

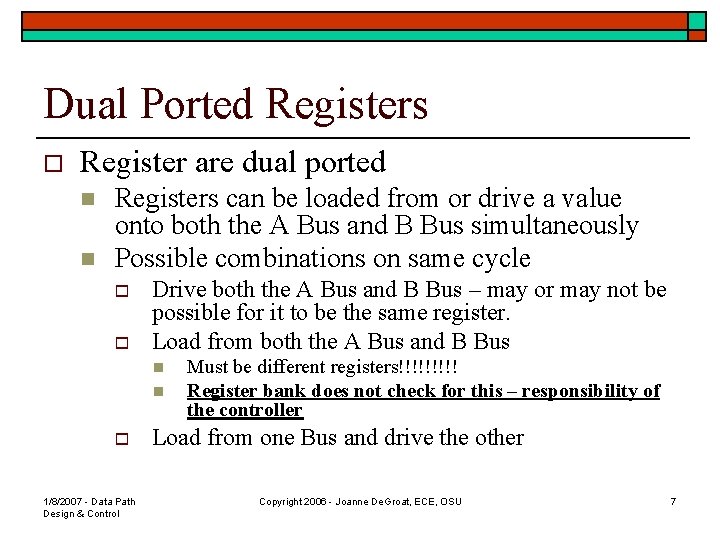

Dual Ported Registers o Register are dual ported n n Registers can be loaded from or drive a value onto both the A Bus and B Bus simultaneously Possible combinations on same cycle o o Drive both the A Bus and B Bus – may or may not be possible for it to be the same register. Load from both the A Bus and B Bus n n o 1/8/2007 - Data Path Design & Control Must be different registers!!!!! Register bank does not check for this – responsibility of the controller Load from one Bus and drive the other Copyright 2006 - Joanne De. Groat, ECE, OSU 7

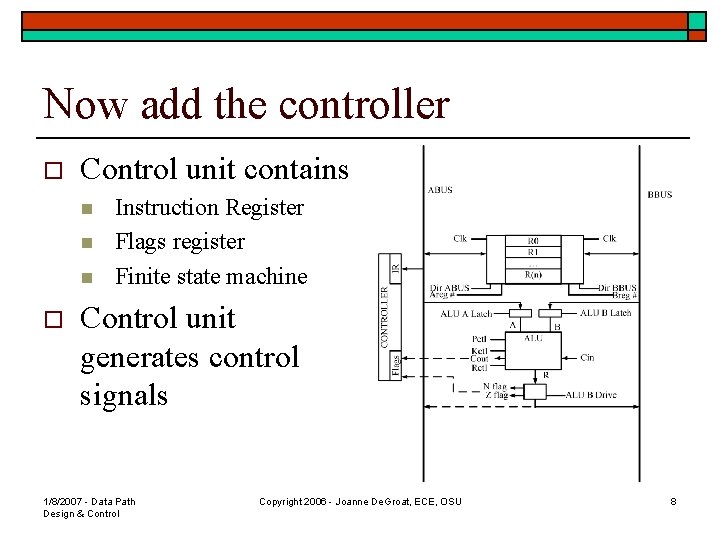

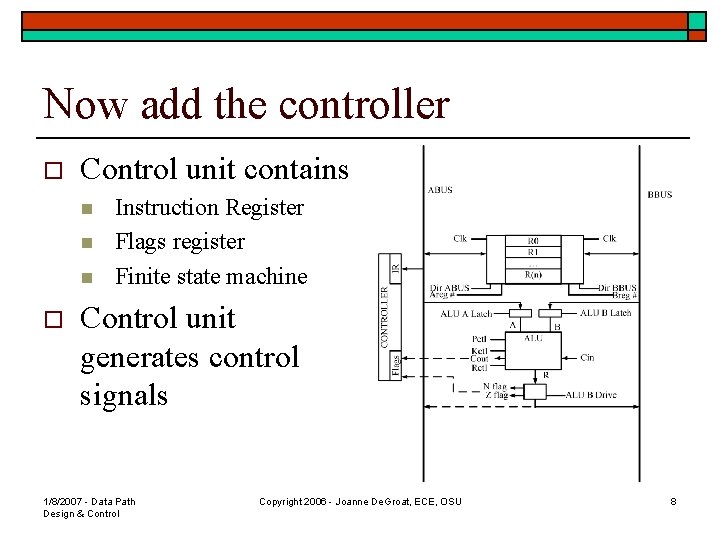

Now add the controller o Control unit contains n n n o Instruction Register Flags register Finite state machine Control unit generates control signals 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 8

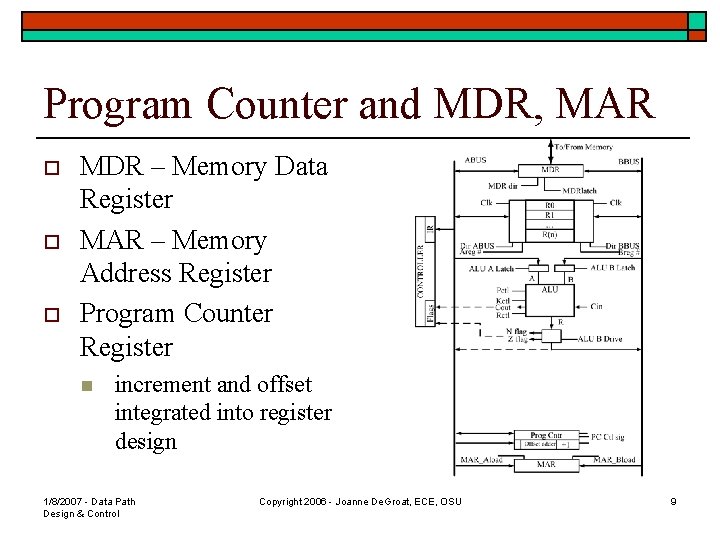

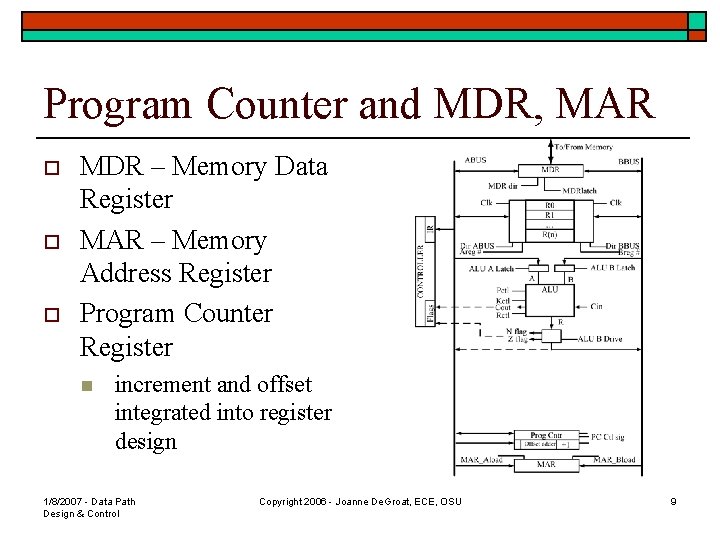

Program Counter and MDR, MAR o o o MDR – Memory Data Register MAR – Memory Address Register Program Counter Register n increment and offset integrated into register design 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 9

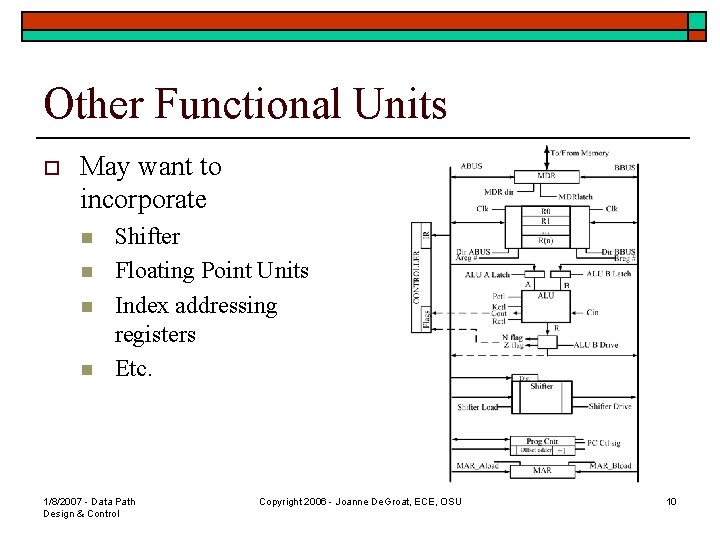

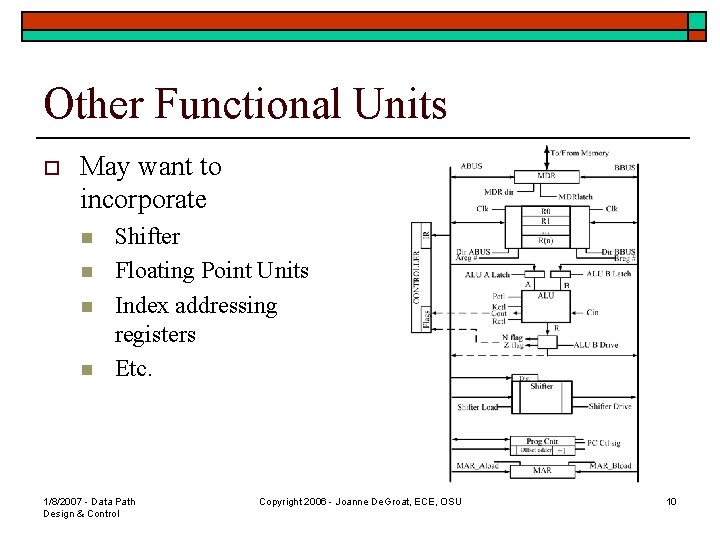

Other Functional Units o May want to incorporate n n Shifter Floating Point Units Index addressing registers Etc. 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 10

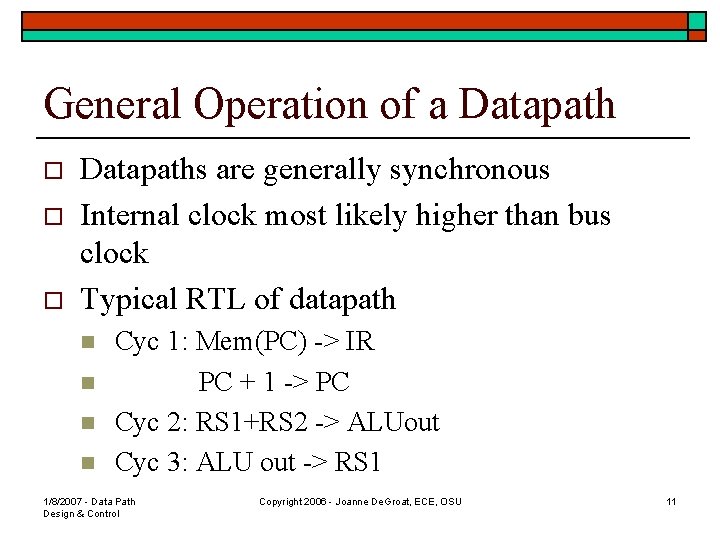

General Operation of a Datapath o o o Datapaths are generally synchronous Internal clock most likely higher than bus clock Typical RTL of datapath n n Cyc 1: Mem(PC) -> IR PC + 1 -> PC Cyc 2: RS 1+RS 2 -> ALUout Cyc 3: ALU out -> RS 1 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 11

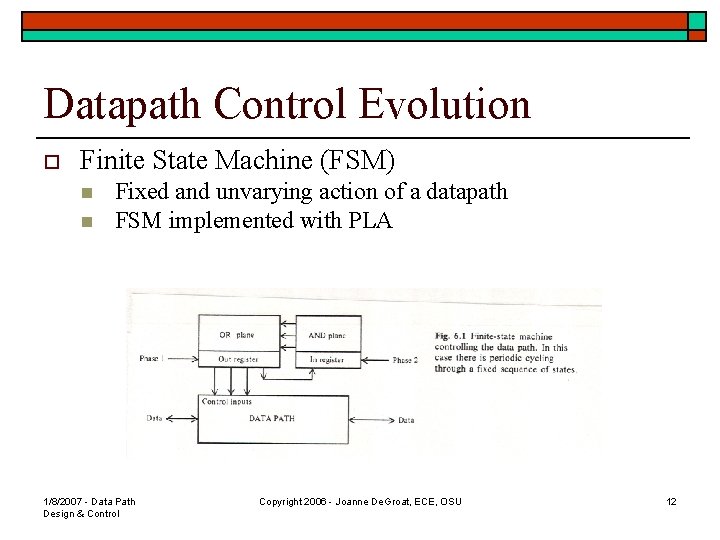

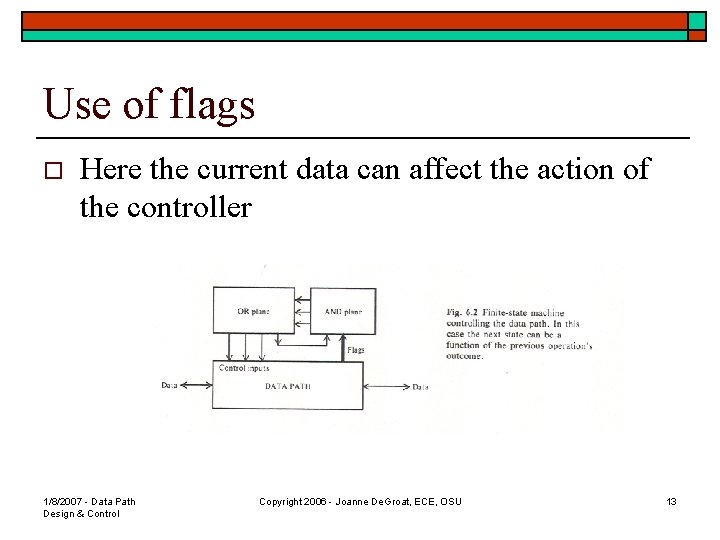

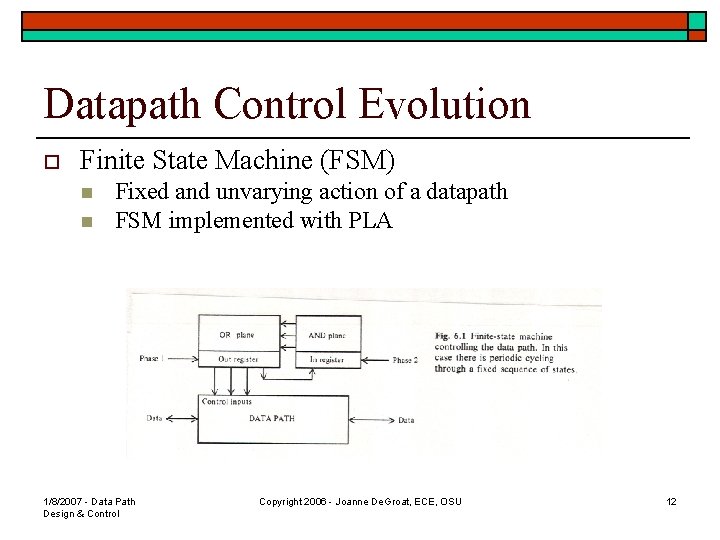

Datapath Control Evolution o Finite State Machine (FSM) n n Fixed and unvarying action of a datapath FSM implemented with PLA 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 12

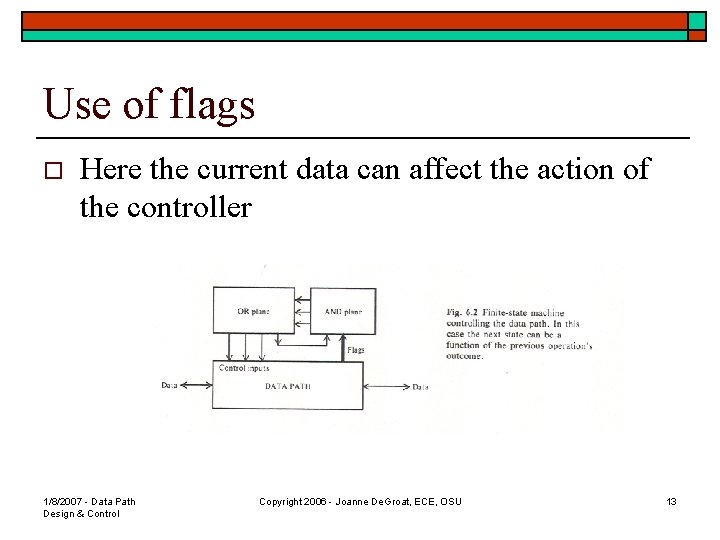

Use of flags o Here the current data can affect the action of the controller 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 13

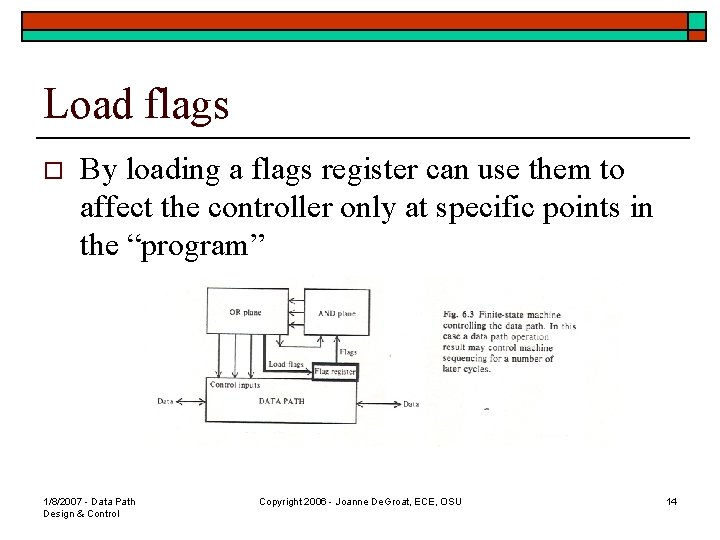

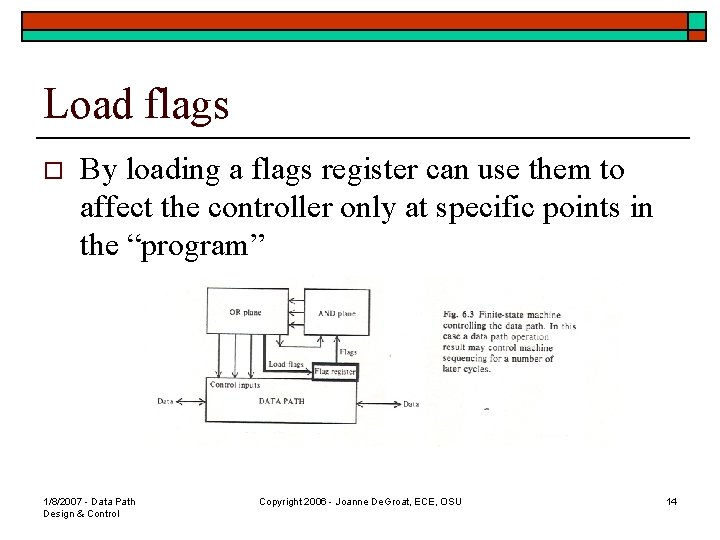

Load flags o By loading a flags register can use them to affect the controller only at specific points in the “program” 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 14

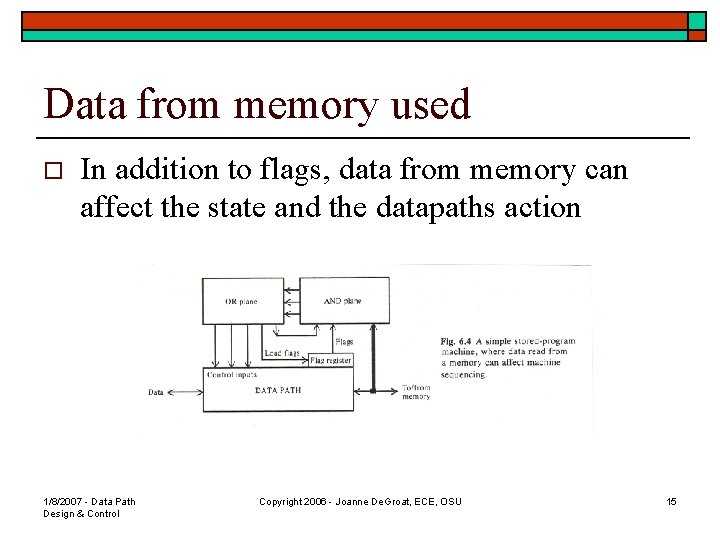

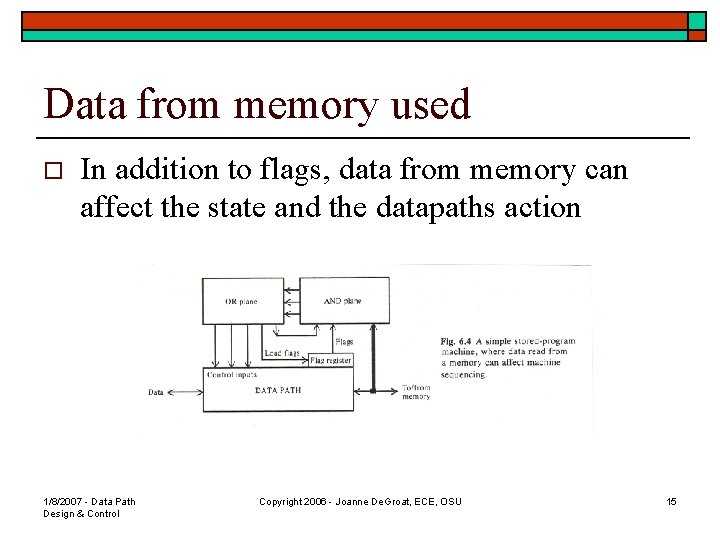

Data from memory used o In addition to flags, data from memory can affect the state and the datapaths action 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 15

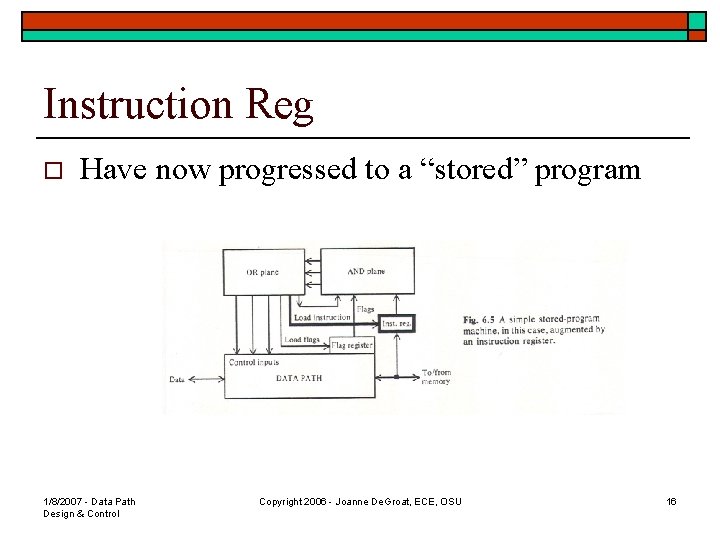

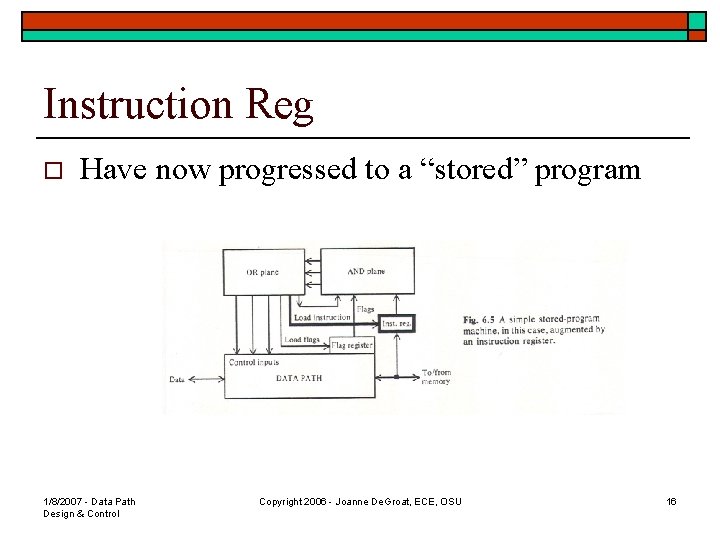

Instruction Reg o Have now progressed to a “stored” program 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 16

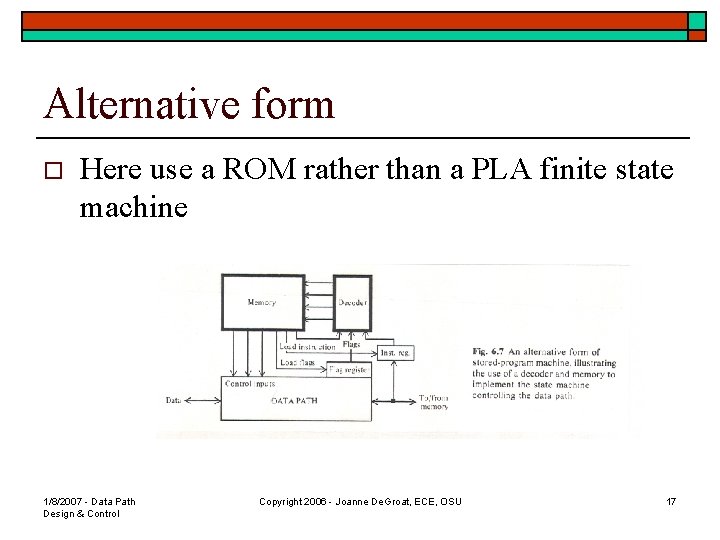

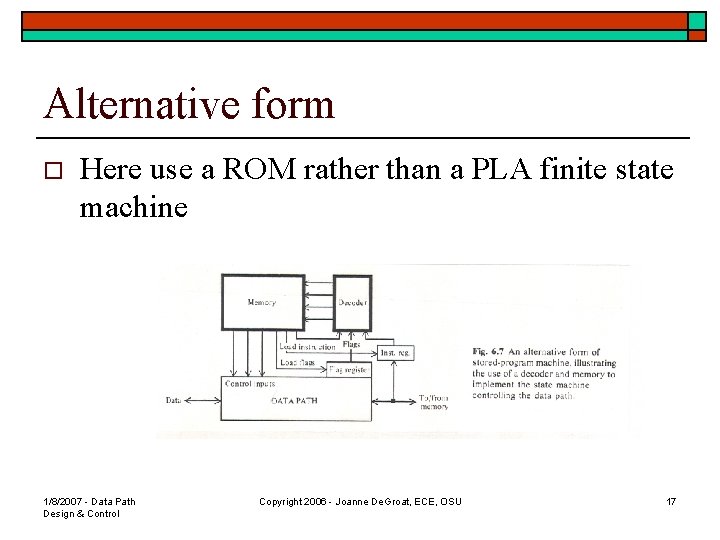

Alternative form o Here use a ROM rather than a PLA finite state machine 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 17

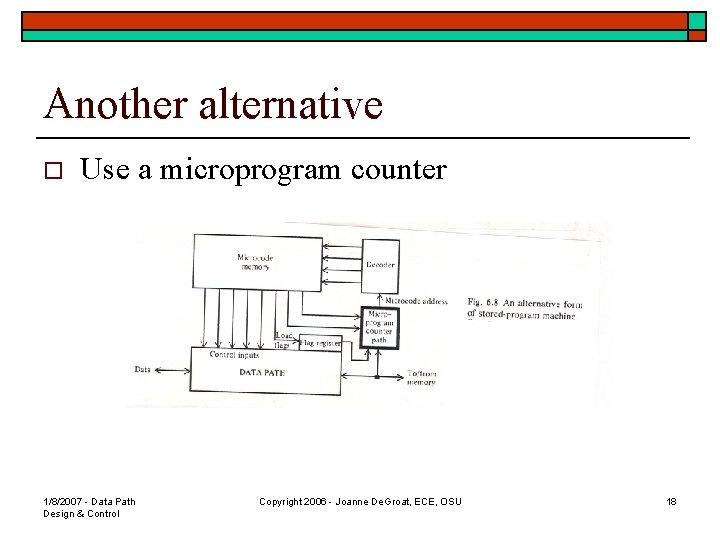

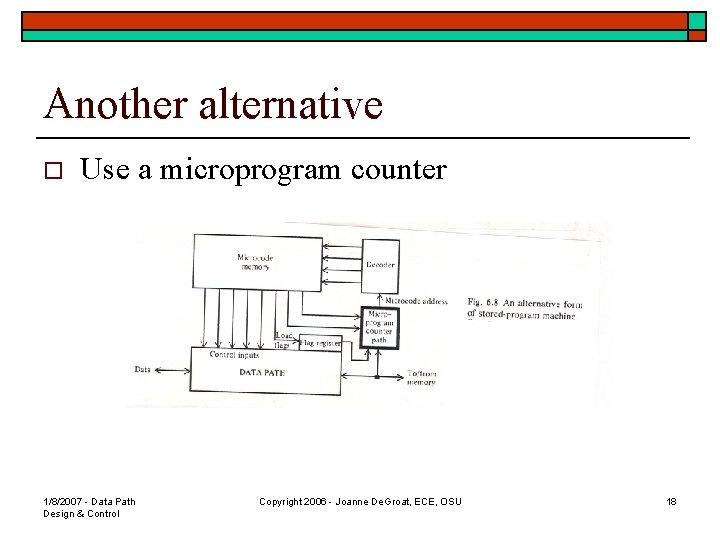

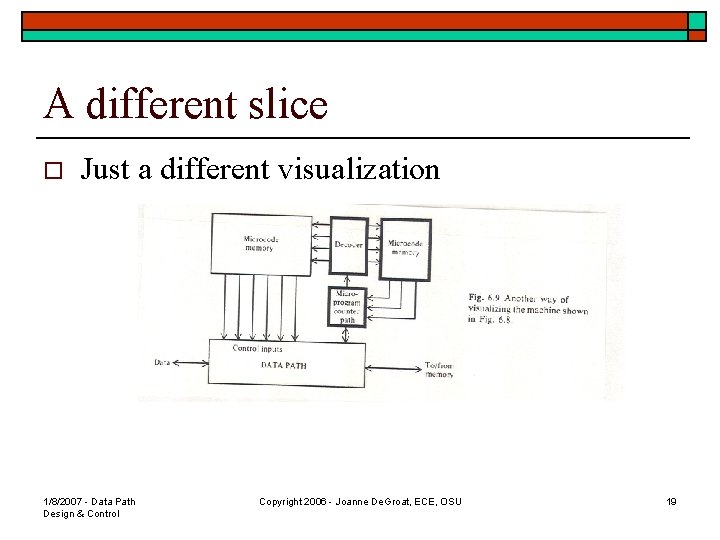

Another alternative o Use a microprogram counter 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 18

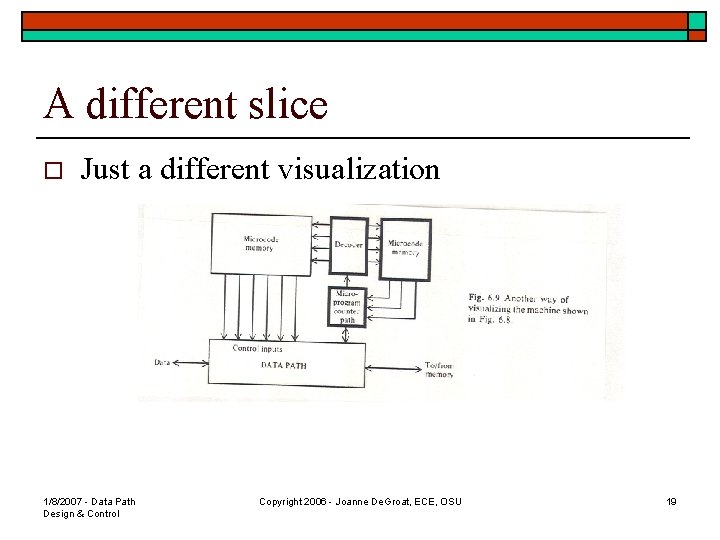

A different slice o Just a different visualization 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 19

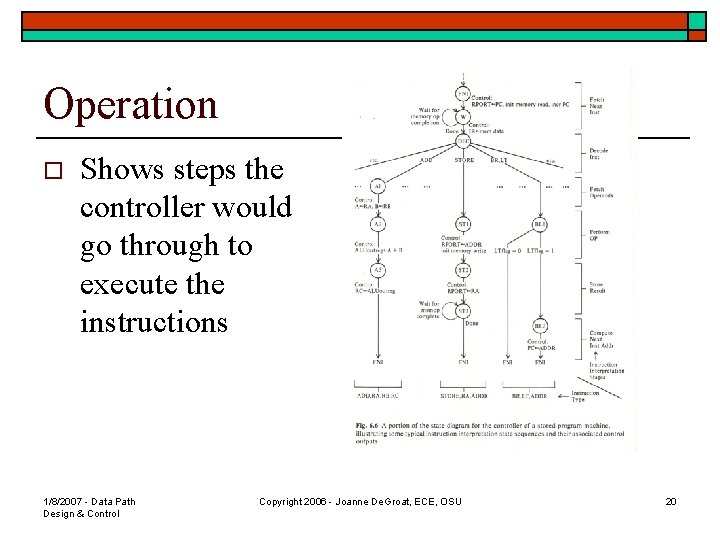

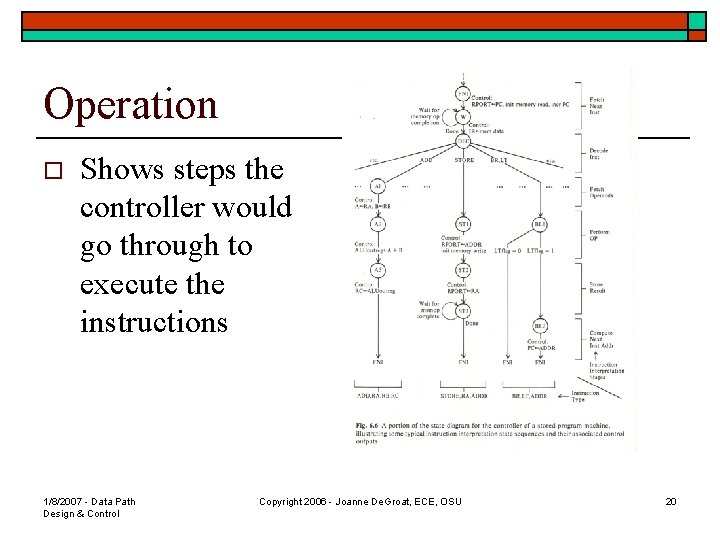

Operation o Shows steps the controller would go through to execute the instructions 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 20

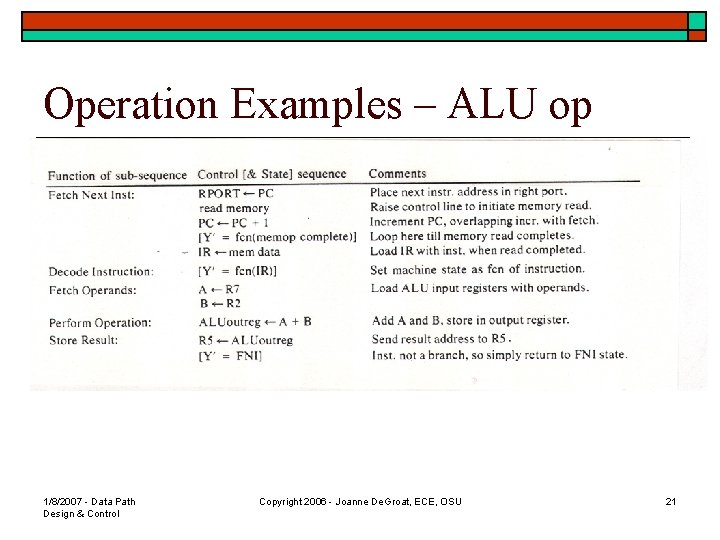

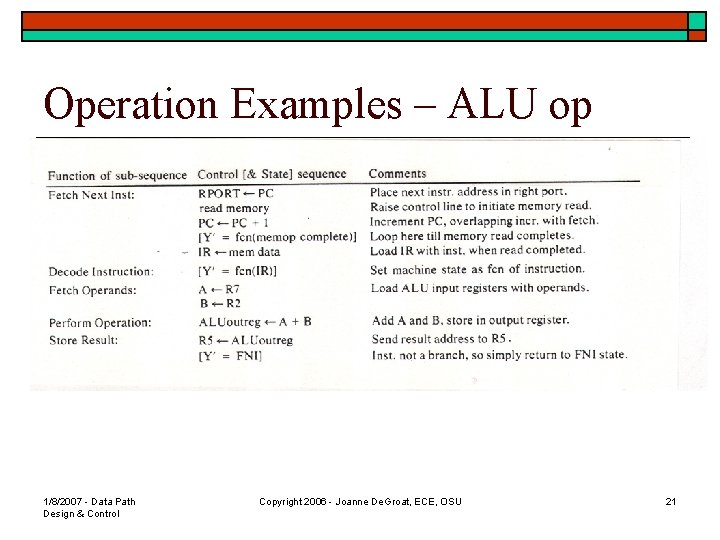

Operation Examples – ALU op 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 21

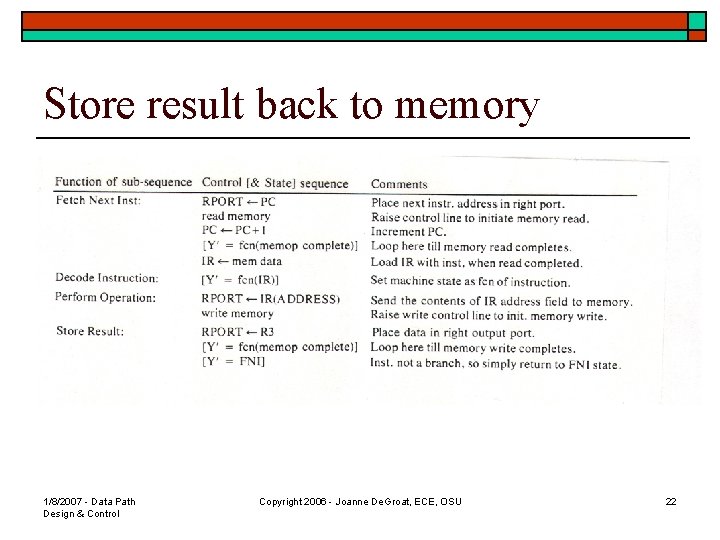

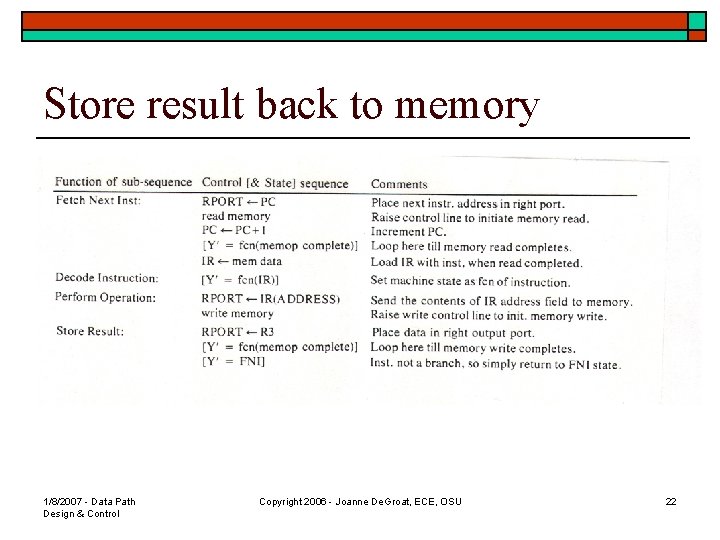

Store result back to memory 1/8/2007 - Data Path Design & Control Copyright 2006 - Joanne De. Groat, ECE, OSU 22