Processor Array Organization IO Ports FPP 0 PC

- Slides: 13

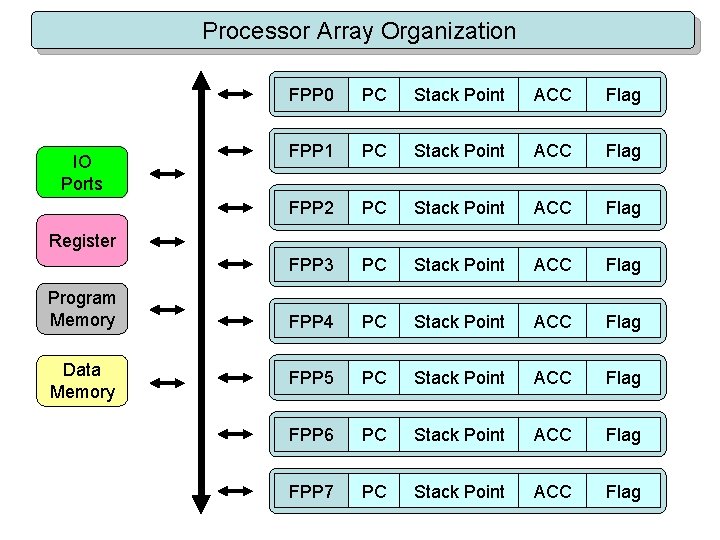

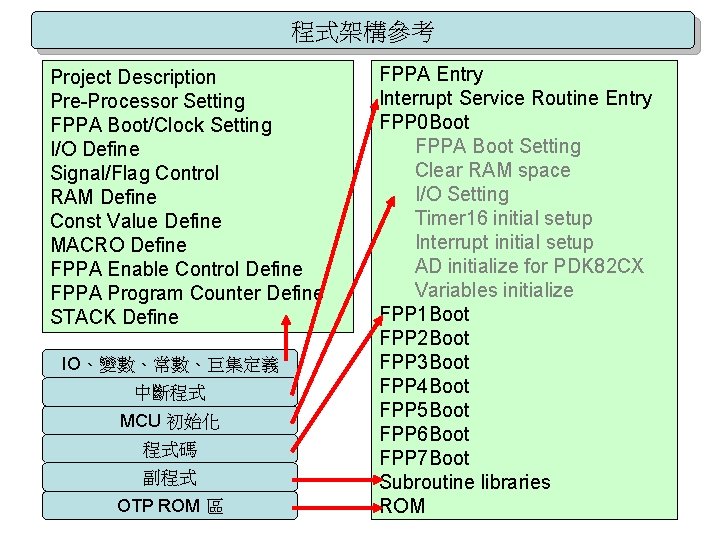

Processor Array Organization IO Ports FPP 0 PC Stack Point ACC Flag FPP 1 PC Stack Point ACC Flag FPP 2 PC Stack Point ACC Flag FPP 3 PC Stack Point ACC Flag FPP 4 PC Stack Point ACC Flag FPP 5 PC Stack Point ACC Flag FPP 6 PC Stack Point ACC Flag FPP 7 PC Stack Point ACC Flag Register Program Memory Data Memory

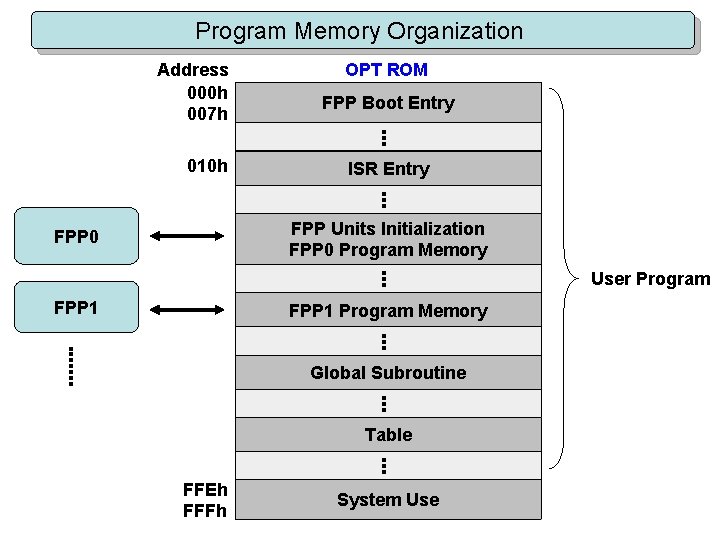

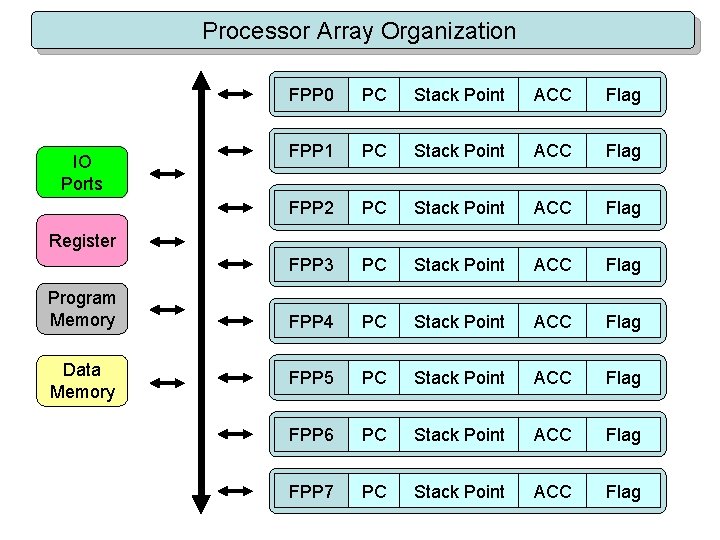

Program Memory Organization Address 000 h 007 h 010 h OPT ROM FPP Boot Entry ISR Entry FPP Units Initialization FPP 0 Program Memory FPP 0 User Program FPP 1 Program Memory Global Subroutine Table FFEh FFFh System Use

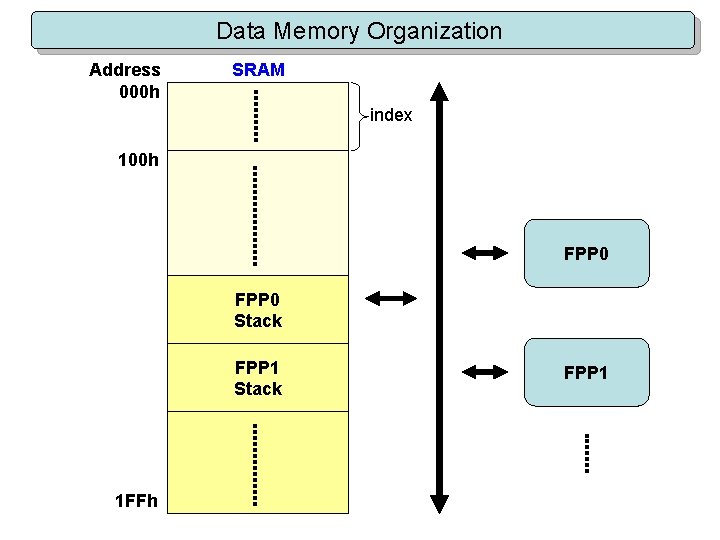

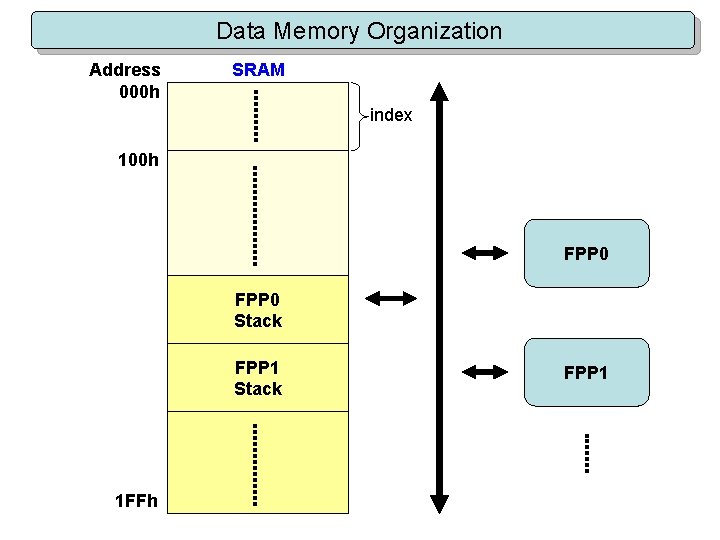

Data Memory Organization Address 000 h SRAM index 100 h FPP 0 Stack FPP 1 Stack 1 FFh FPP 1

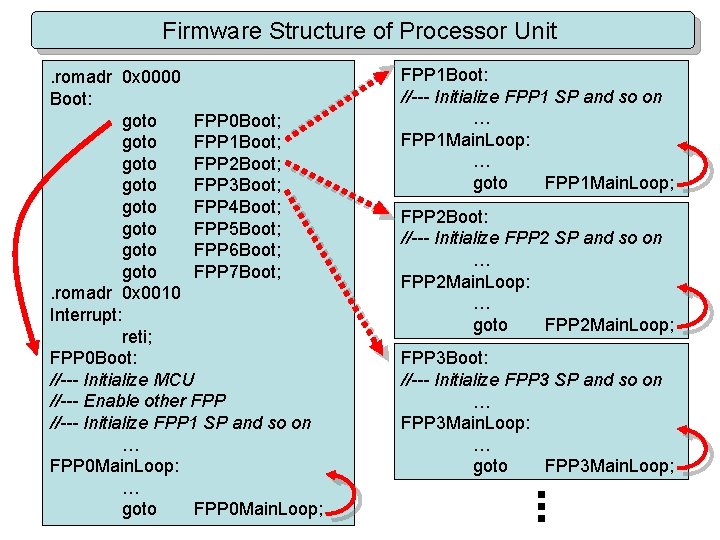

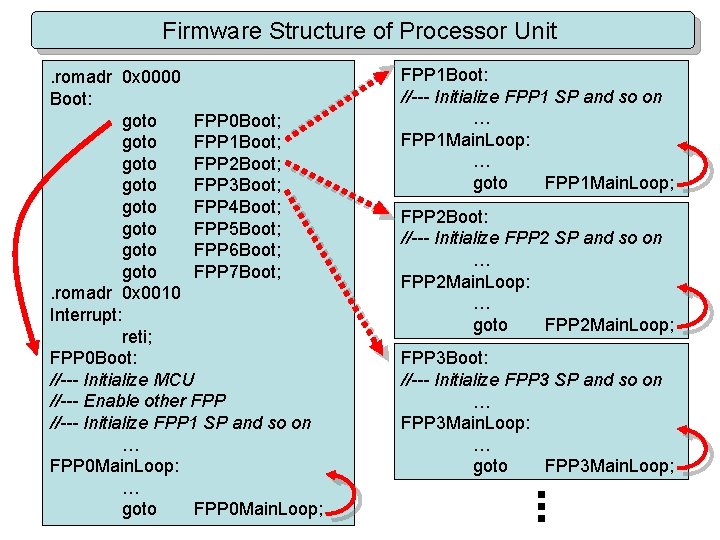

Firmware Structure of Processor Unit. romadr 0 x 0000 Boot: goto FPP 0 Boot; goto FPP 1 Boot; goto FPP 2 Boot; goto FPP 3 Boot; goto FPP 4 Boot; goto FPP 5 Boot; goto FPP 6 Boot; goto FPP 7 Boot; . romadr 0 x 0010 Interrupt: reti; FPP 0 Boot: //--- Initialize MCU //--- Enable other FPP //--- Initialize FPP 1 SP and so on … FPP 0 Main. Loop: … goto FPP 0 Main. Loop; FPP 1 Boot: //--- Initialize FPP 1 SP and so on … FPP 1 Main. Loop: … goto FPP 1 Main. Loop; FPP 2 Boot: //--- Initialize FPP 2 SP and so on … FPP 2 Main. Loop: … goto FPP 2 Main. Loop; FPP 3 Boot: //--- Initialize FPP 3 SP and so on … FPP 3 Main. Loop: … goto FPP 3 Main. Loop;

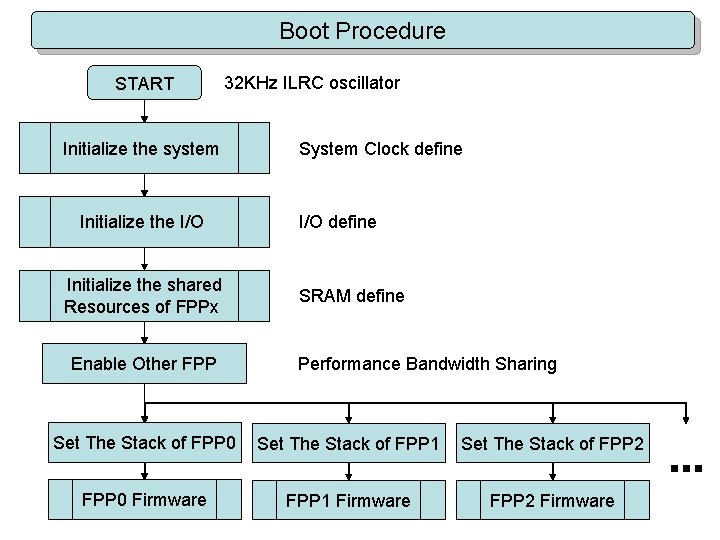

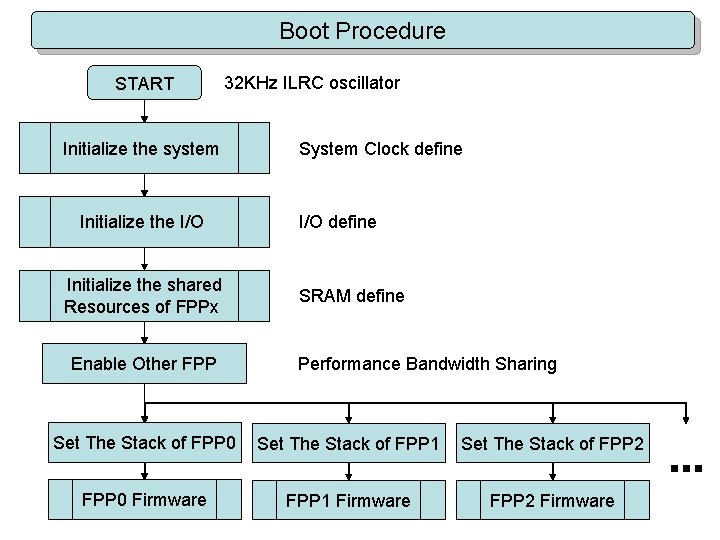

Boot Procedure START 32 KHz ILRC oscillator Initialize the system Initialize the I/O Initialize the shared Resources of FPPx Enable Other FPP System Clock define I/O define SRAM define Performance Bandwidth Sharing Set The Stack of FPP 0 Set The Stack of FPP 1 Set The Stack of FPP 2 FPP 0 Firmware FPP 1 Firmware FPP 2 Firmware

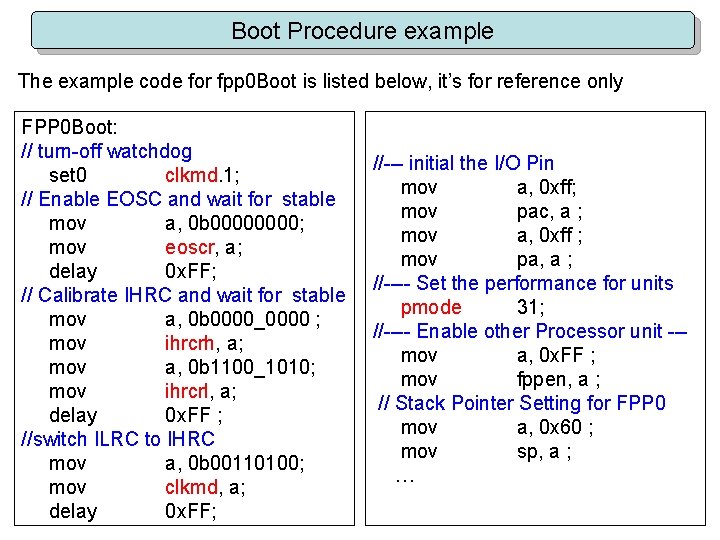

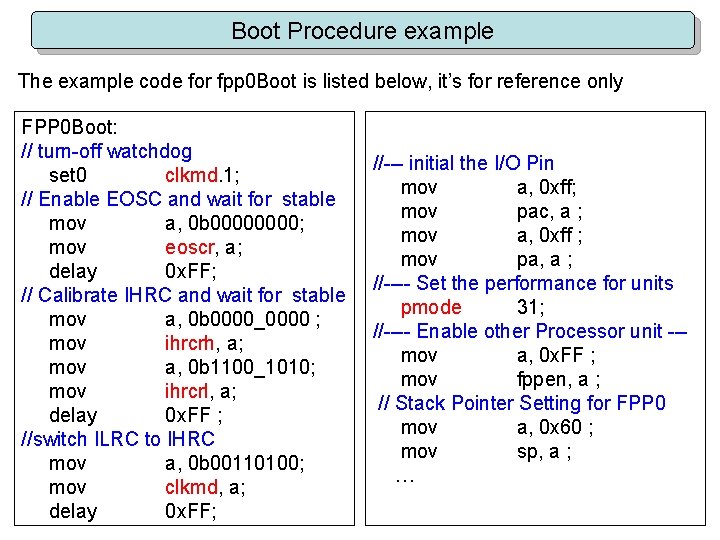

Boot Procedure example The example code for fpp 0 Boot is listed below, it’s for reference only FPP 0 Boot: // turn-off watchdog set 0 clkmd. 1; // Enable EOSC and wait for stable mov a, 0 b 0000; mov eoscr, a; delay 0 x. FF; // Calibrate IHRC and wait for stable mov a, 0 b 0000_0000 ; mov ihrcrh, a; mov a, 0 b 1100_1010; mov ihrcrl, a; delay 0 x. FF ; //switch ILRC to IHRC mov a, 0 b 00110100; mov clkmd, a; delay 0 x. FF; //--- initial the I/O Pin mov a, 0 xff; mov pac, a ; mov a, 0 xff ; mov pa, a ; //---- Set the performance for units pmode 31; //---- Enable other Processor unit --mov a, 0 x. FF ; mov fppen, a ; // Stack Pointer Setting for FPP 0 mov a, 0 x 60 ; mov sp, a ; …

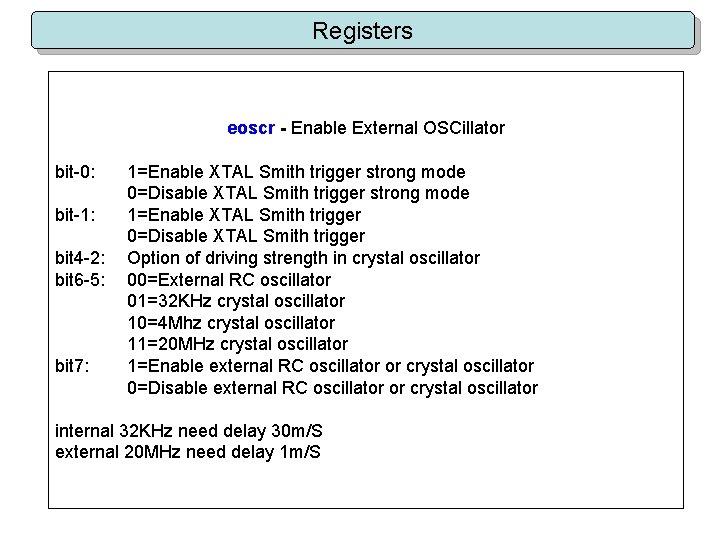

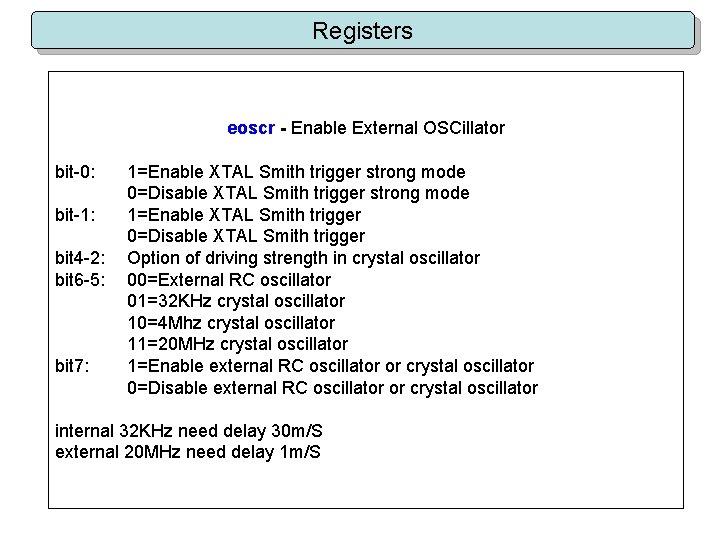

Registers eoscr - Enable External OSCillator bit-0: bit-1: bit 4 -2: bit 6 -5: bit 7: 1=Enable XTAL Smith trigger strong mode 0=Disable XTAL Smith trigger strong mode 1=Enable XTAL Smith trigger 0=Disable XTAL Smith trigger Option of driving strength in crystal oscillator 00=External RC oscillator 01=32 KHz crystal oscillator 10=4 Mhz crystal oscillator 11=20 MHz crystal oscillator 1=Enable external RC oscillator or crystal oscillator 0=Disable external RC oscillator or crystal oscillator internal 32 KHz need delay 30 m/S external 20 MHz need delay 1 m/S

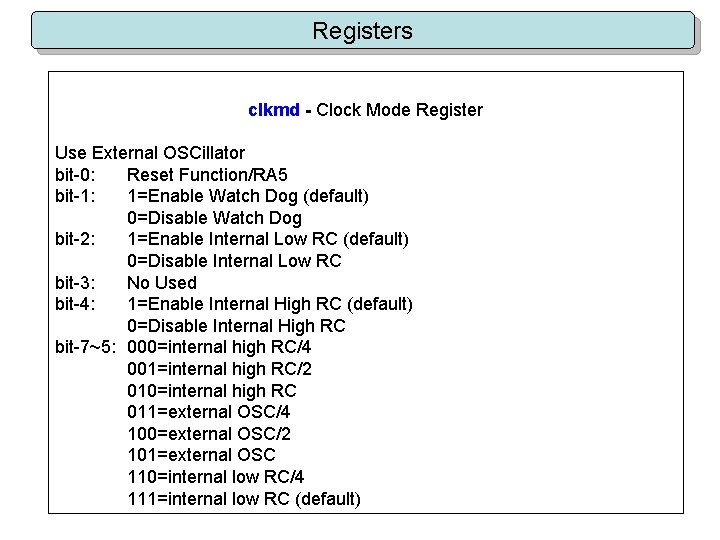

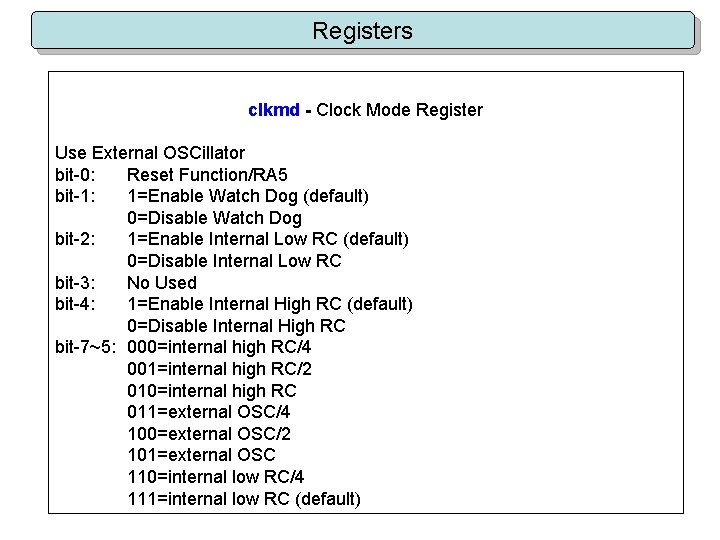

Registers clkmd - Clock Mode Register Use External OSCillator bit-0: Reset Function/RA 5 bit-1: 1=Enable Watch Dog (default) 0=Disable Watch Dog bit-2: 1=Enable Internal Low RC (default) 0=Disable Internal Low RC bit-3: No Used bit-4: 1=Enable Internal High RC (default) 0=Disable Internal High RC bit-7~5: 000=internal high RC/4 001=internal high RC/2 010=internal high RC 011=external OSC/4 100=external OSC/2 101=external OSC 110=internal low RC/4 111=internal low RC (default)

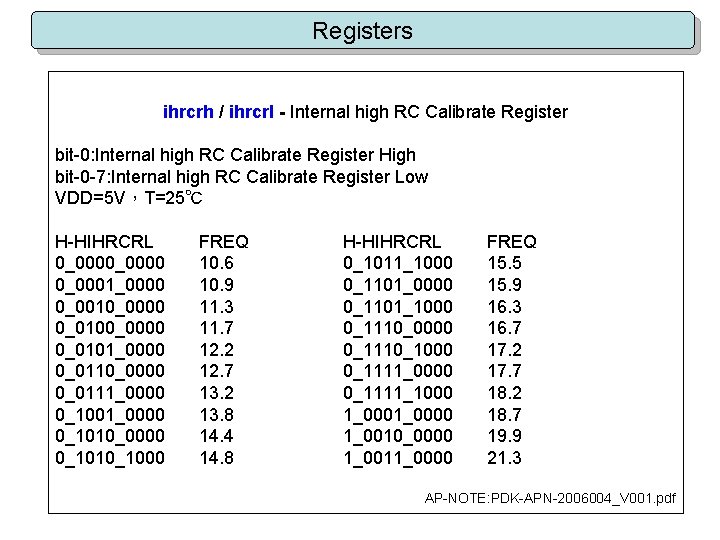

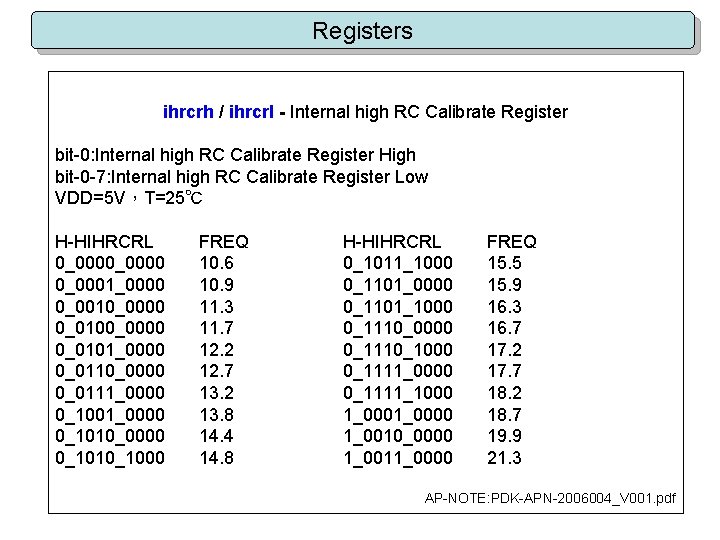

Registers ihrcrh / ihrcrl - Internal high RC Calibrate Register bit-0: Internal high RC Calibrate Register High bit-0 -7: Internal high RC Calibrate Register Low VDD=5 V,T=25℃ H-HIHRCRL 0_0000 0_0001_0000 0_0010_0000 0_0101_0000 0_0110_0000 0_0111_0000 0_1001_0000 0_1010_1000 FREQ 10. 6 10. 9 11. 3 11. 7 12. 2 12. 7 13. 2 13. 8 14. 4 14. 8 H-HIHRCRL 0_1011_1000 0_1101_0000 0_1101_1000 0_1110_0000 0_1110_1000 0_1111_0000 0_1111_1000 1_0000 1_0010_0000 1_0011_0000 FREQ 15. 5 15. 9 16. 3 16. 7 17. 2 17. 7 18. 2 18. 7 19. 9 21. 3 AP-NOTE: PDK-APN-2006004_V 001. pdf

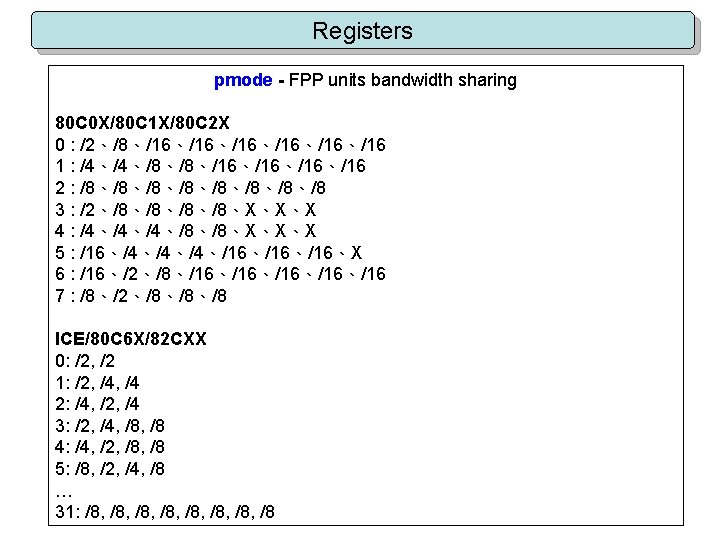

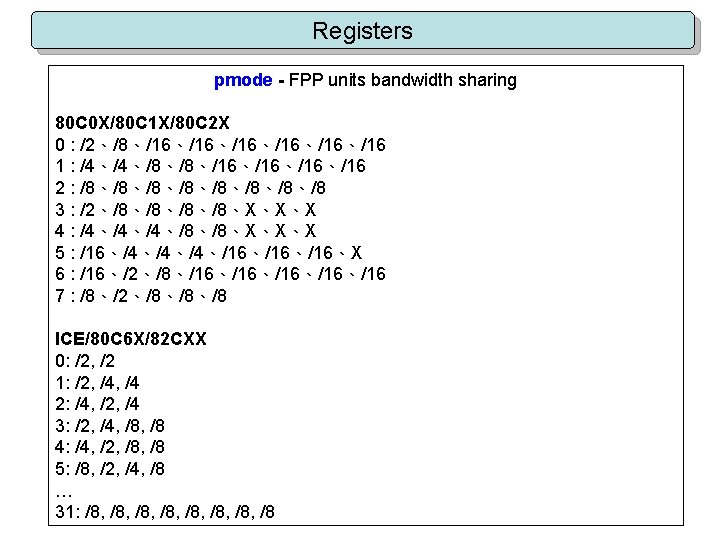

Registers pmode - FPP units bandwidth sharing 80 C 0 X/80 C 1 X/80 C 2 X 0 : /2、/8、/16、/16、/16 1 : /4、/4、/8、/8、/16、/16 2 : /8、/8、/8、/8、/8 3 : /2、/8、/8、X、X、X 4 : /4、/4、/4、/8、/8、X、X、X 5 : /16、/4、/4、/4、/16、/16、X 6 : /16、/2、/8、/16、/16、/16 7 : /8、/2、/8、/8、/8 ICE/80 C 6 X/82 CXX 0: /2, /2 1: /2, /4 2: /4, /2, /4 3: /2, /4, /8 4: /4, /2, /8 5: /8, /2, /4, /8 … 31: /8, /8, /8

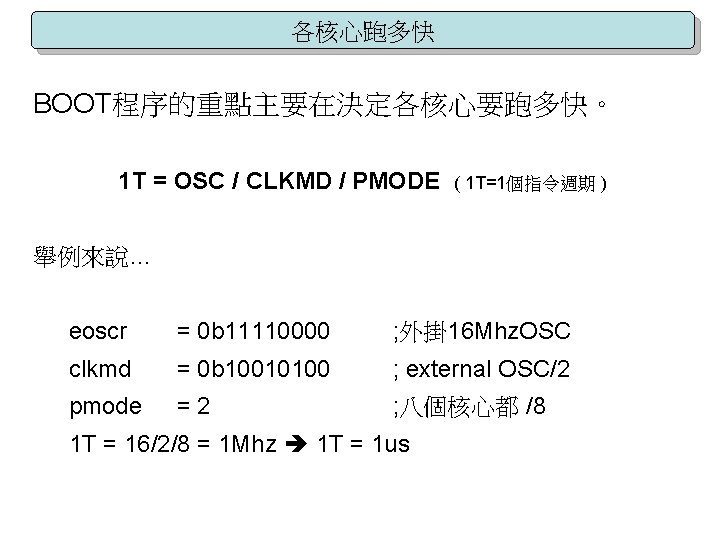

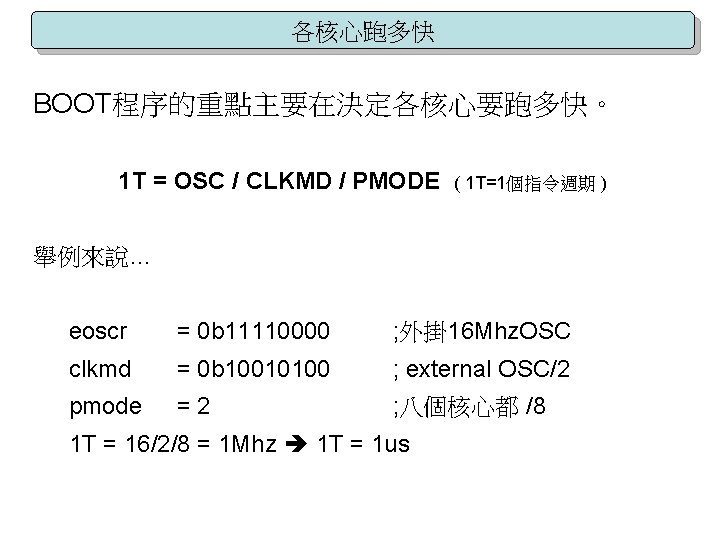

各核心跑多快 BOOT程序的重點主要在決定各核心要跑多快。 1 T = OSC / CLKMD / PMODE ( 1 T=1個指令週期 ) 舉例來說… eoscr = 0 b 11110000 ; 外掛 16 Mhz. OSC clkmd = 0 b 10010100 ; external OSC/2 pmode =2 ; 八個核心都 /8 1 T = 16/2/8 = 1 Mhz 1 T = 1 us

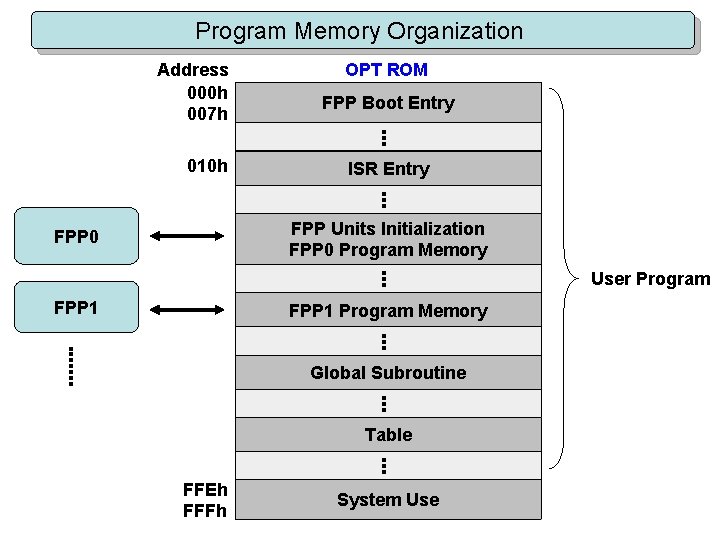

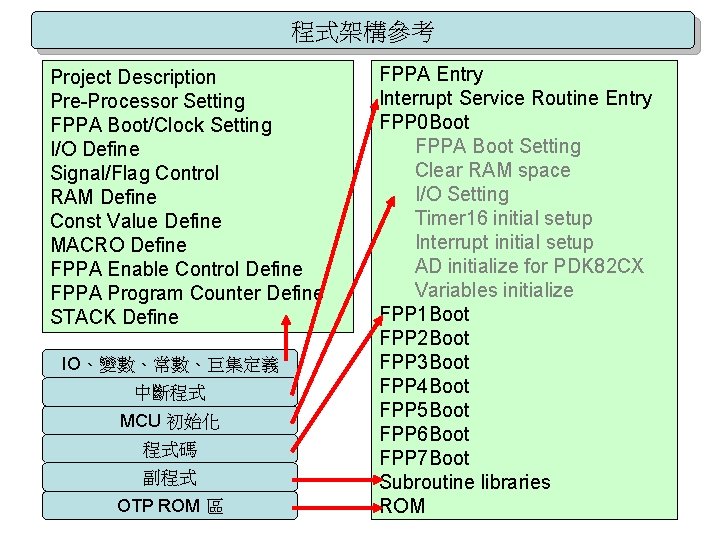

程式架構參考 Project Description Pre-Processor Setting FPPA Boot/Clock Setting I/O Define Signal/Flag Control RAM Define Const Value Define MACRO Define FPPA Enable Control Define FPPA Program Counter Define STACK Define IO、變數、常數、巨集定義 中斷程式 MCU 初始化 程式碼 副程式 OTP ROM 區 FPPA Entry Interrupt Service Routine Entry FPP 0 Boot FPPA Boot Setting Clear RAM space I/O Setting Timer 16 initial setup Interrupt initial setup AD initialize for PDK 82 CX Variables initialize FPP 1 Boot FPP 2 Boot FPP 3 Boot FPP 4 Boot FPP 5 Boot FPP 6 Boot FPP 7 Boot Subroutine libraries ROM