Processadores Aula 02 Professor Andr Luis Meneses Silva

- Slides: 35

Processadores – Aula 02 Professor: André Luis Meneses Silva E-mail/msn: andre. Luis. ms@gmail. com Página: www. dcomp. ufs. br/index. php/docentes: Andre

Agenda Unidade de Controle O Controle da ALU Convertendo tabelas verdade em portas lógicas As demais unidades da unidade de controle.

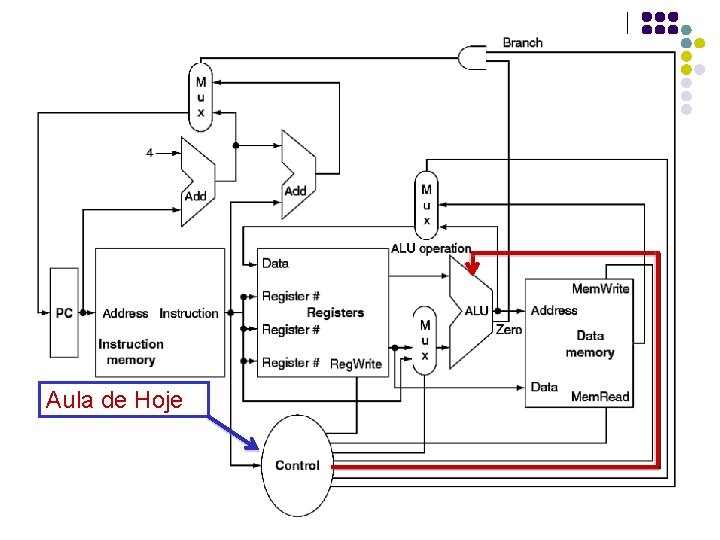

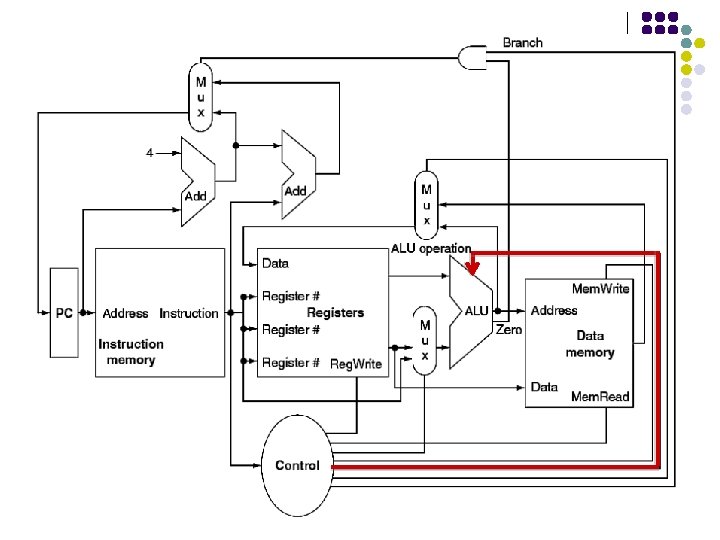

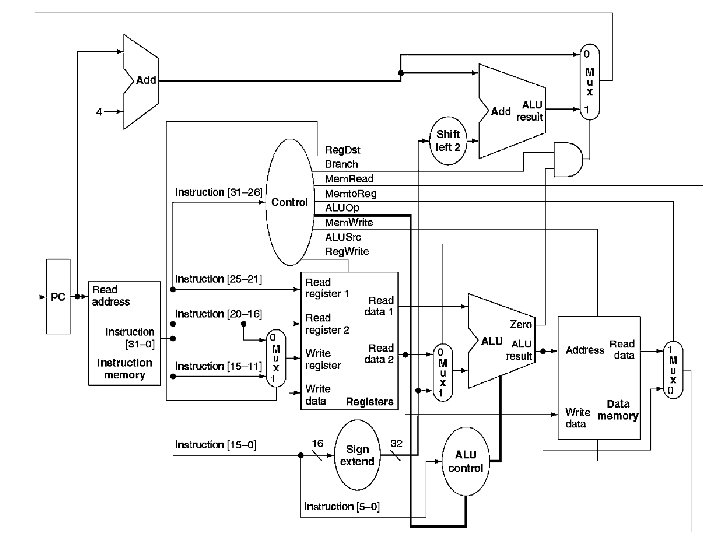

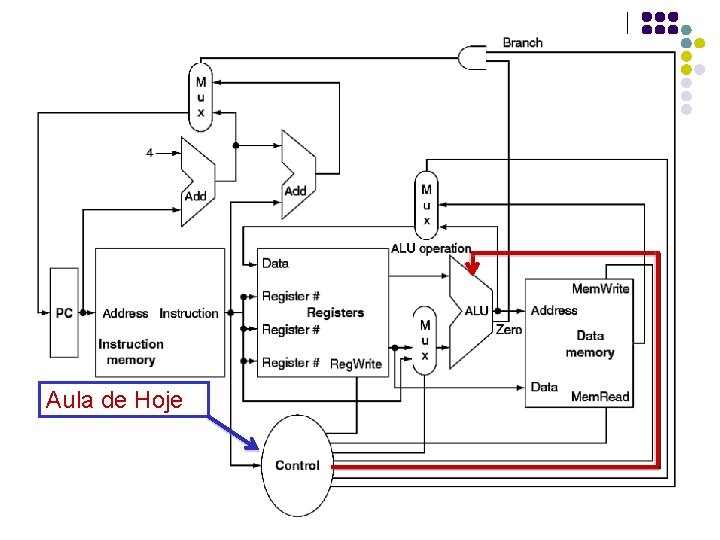

Na aula passada vimos os componentes que formam um projeto simples de um caminho de dados. A aula de hoje será focada na unidade de controle.

Aula de Hoje

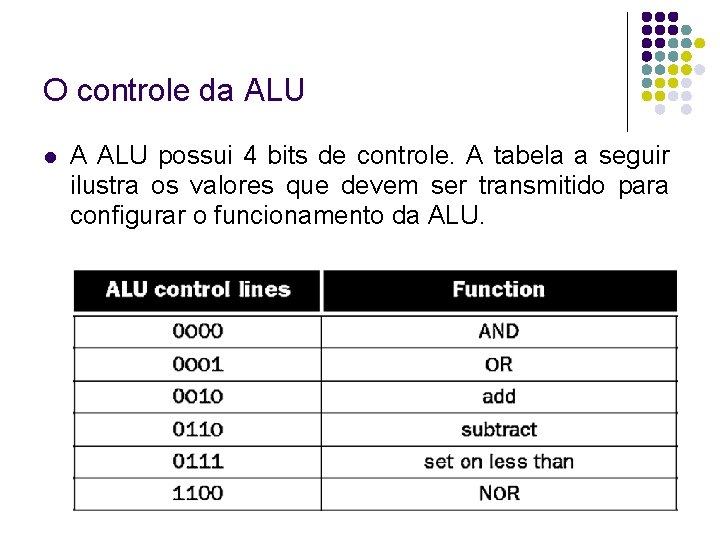

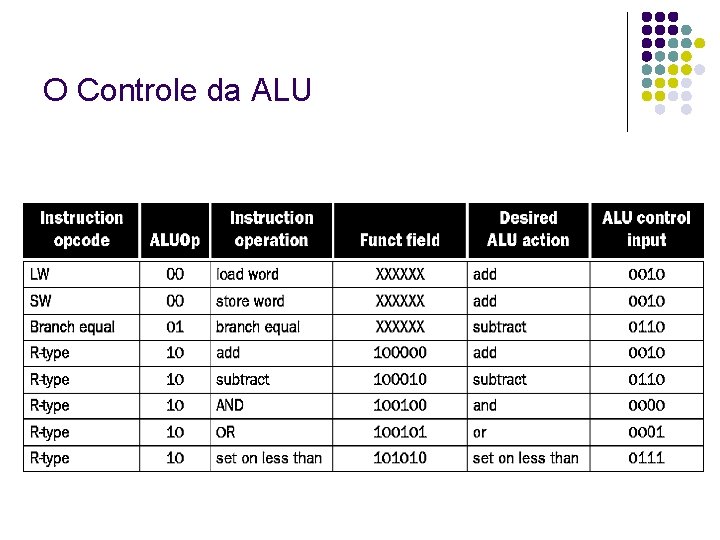

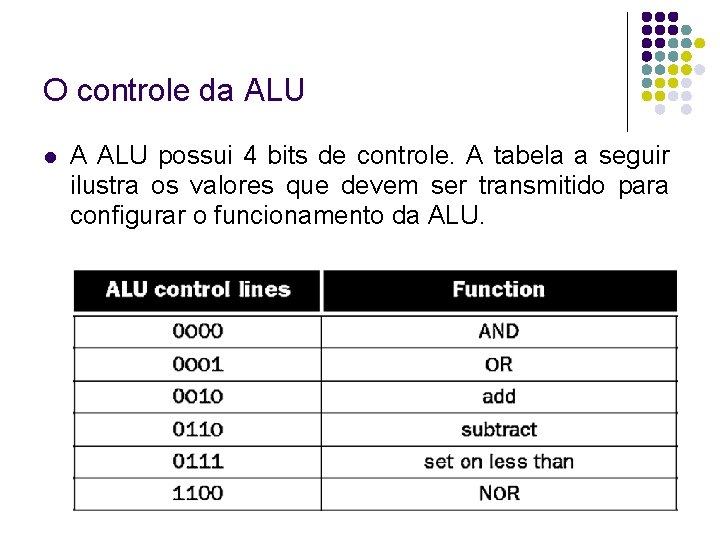

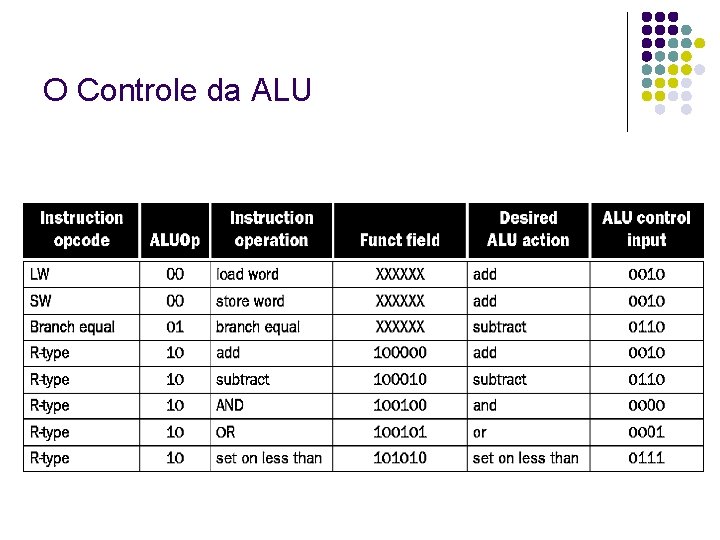

O controle da ALU A ALU possui 4 bits de controle. A tabela a seguir ilustra os valores que devem ser transmitido para configurar o funcionamento da ALU.

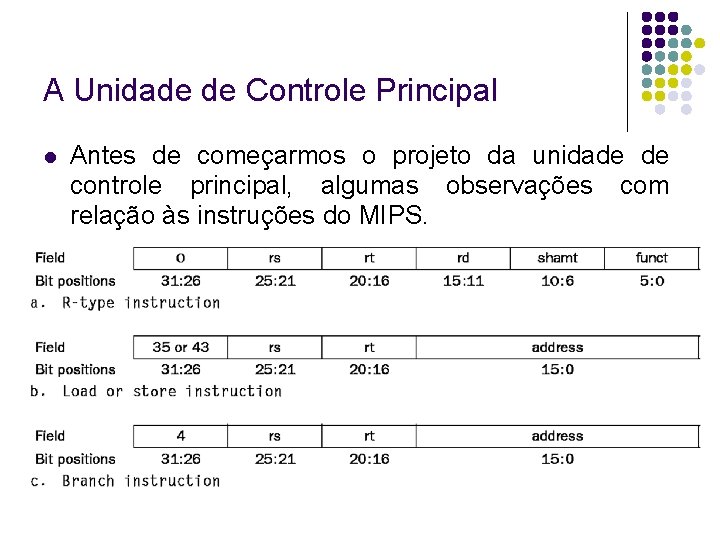

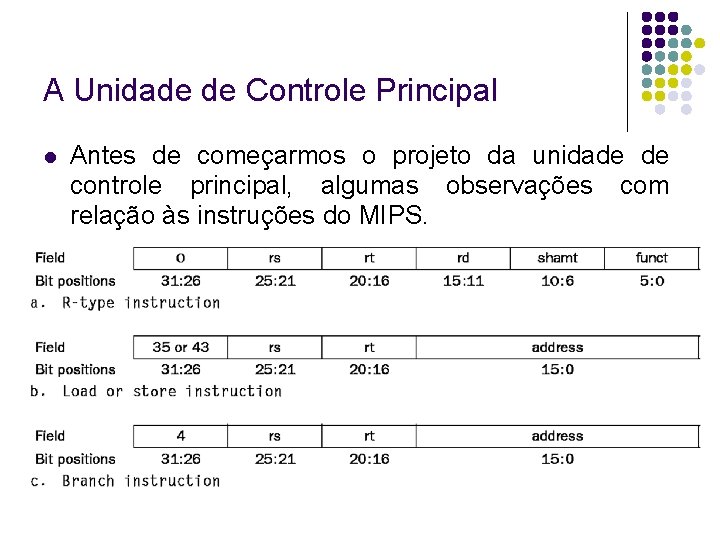

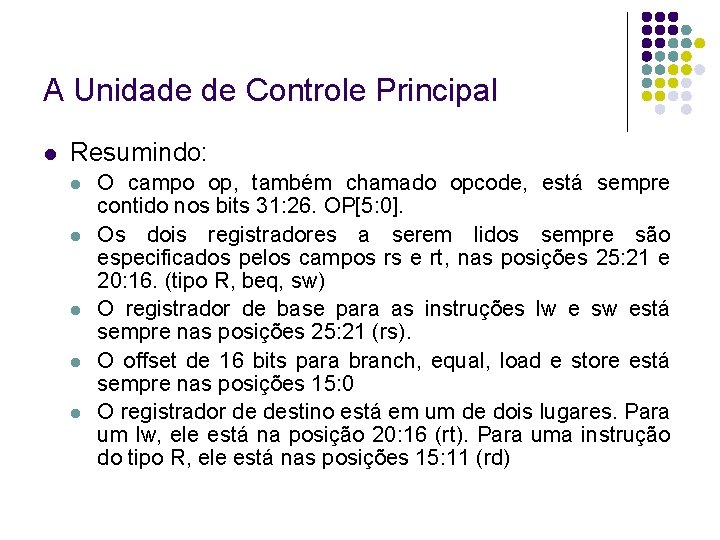

A Unidade de Controle Principal Antes de começarmos o projeto da unidade de controle principal, algumas observações com relação às instruções do MIPS.

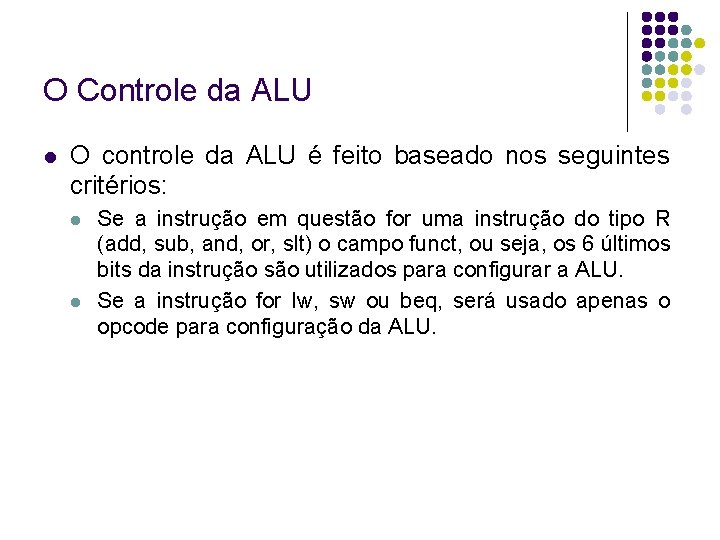

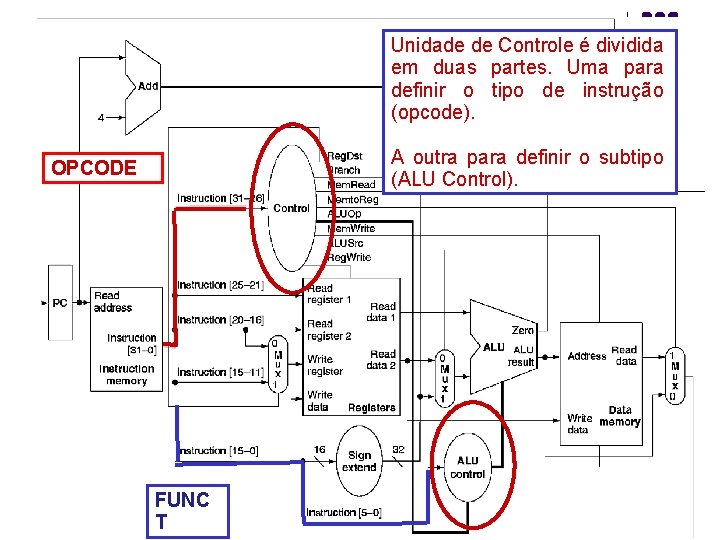

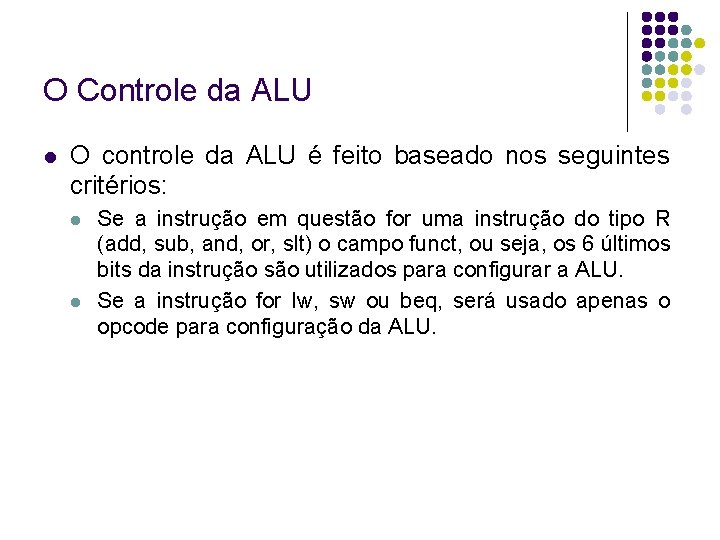

O Controle da ALU O controle da ALU é feito baseado nos seguintes critérios: Se a instrução em questão for uma instrução do tipo R (add, sub, and, or, slt) o campo funct, ou seja, os 6 últimos bits da instrução são utilizados para configurar a ALU. Se a instrução for lw, sw ou beq, será usado apenas o opcode para configuração da ALU.

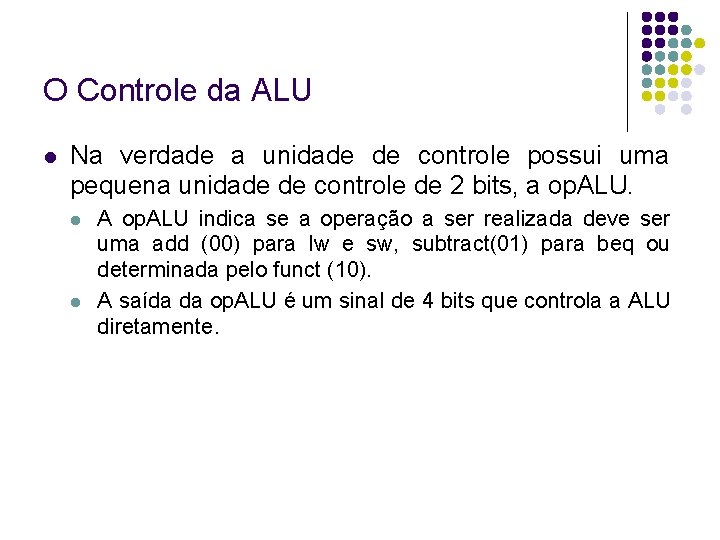

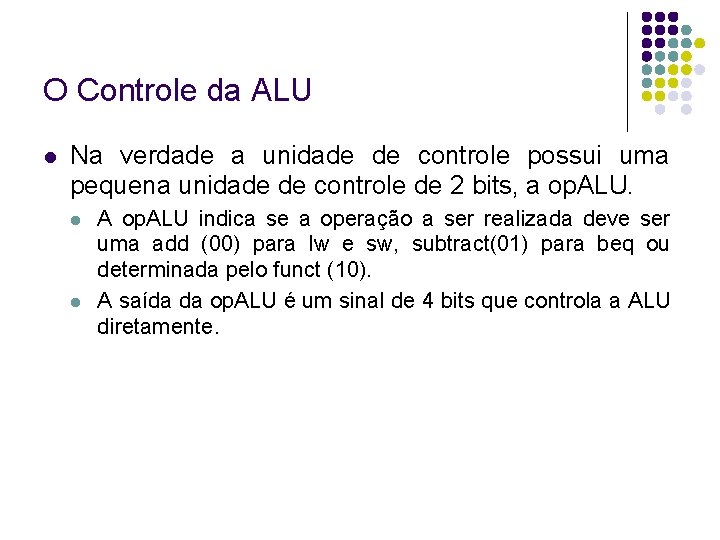

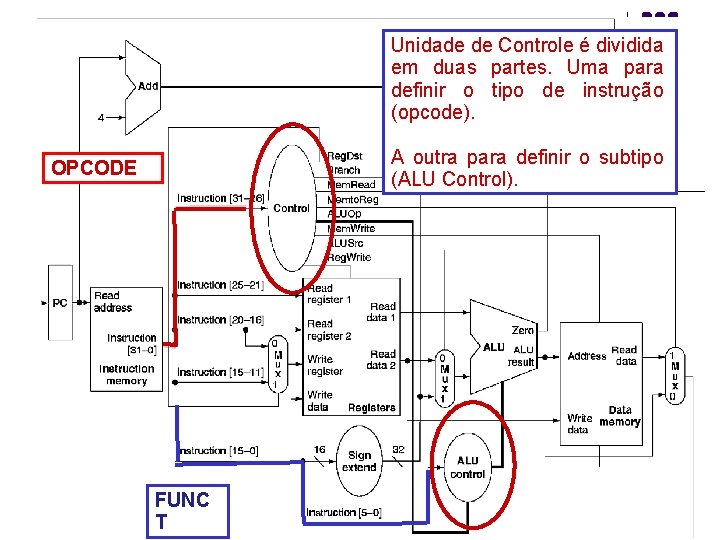

O Controle da ALU Na verdade a unidade de controle possui uma pequena unidade de controle de 2 bits, a op. ALU. A op. ALU indica se a operação a ser realizada deve ser uma add (00) para lw e sw, subtract(01) para beq ou determinada pelo funct (10). A saída da op. ALU é um sinal de 4 bits que controla a ALU diretamente.

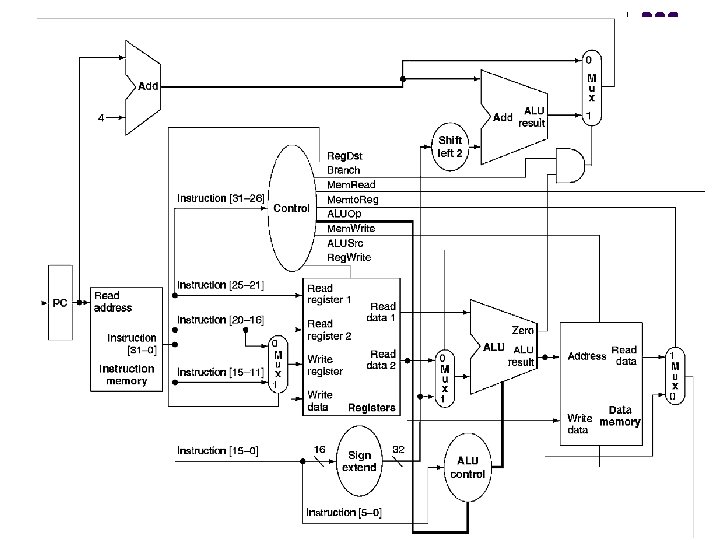

Unidade de Controle é dividida em duas partes. Uma para definir o tipo de instrução (opcode). A outra para definir o subtipo (ALU Control). OPCODE FUNC T

O Controle da ALU

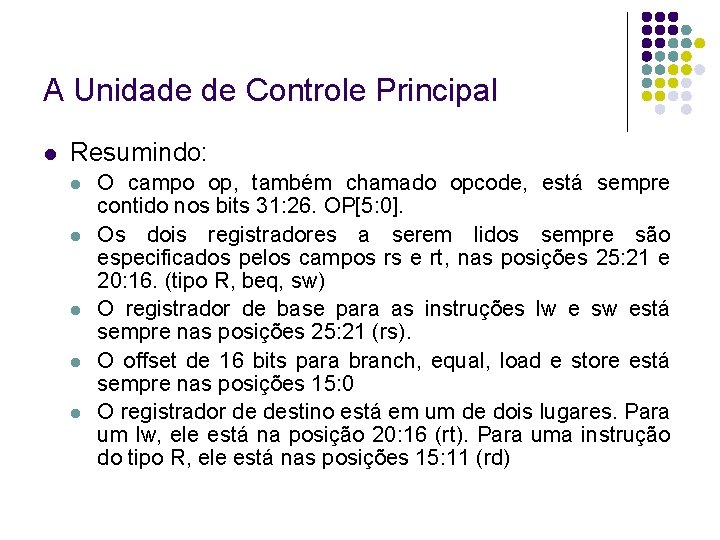

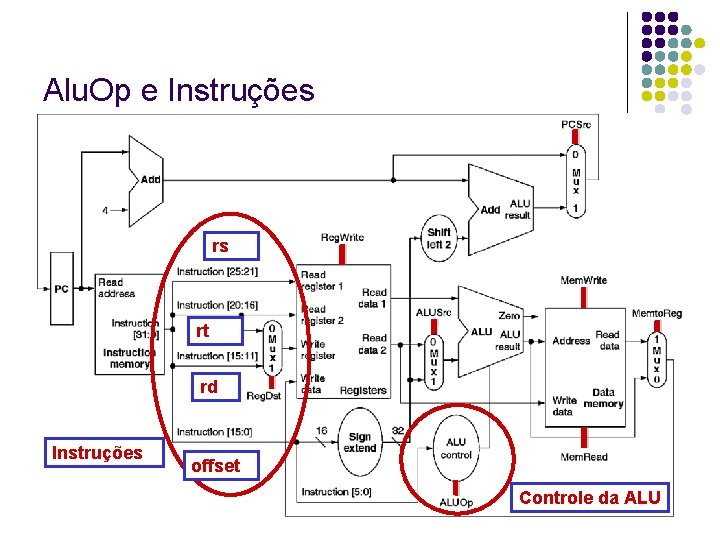

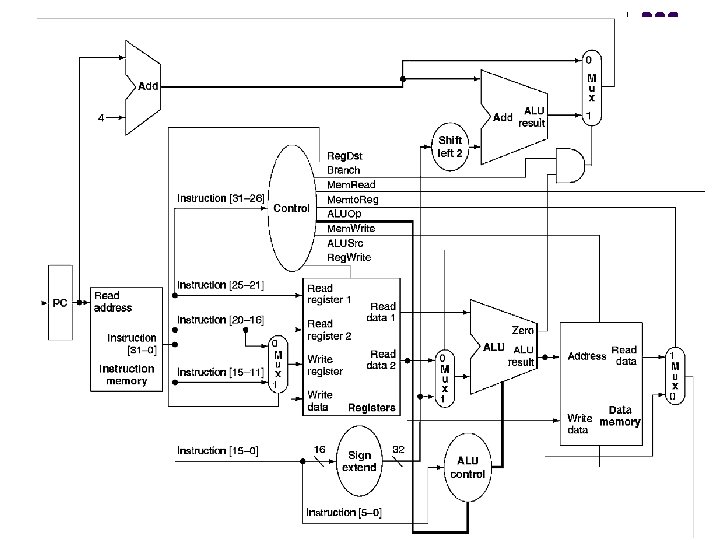

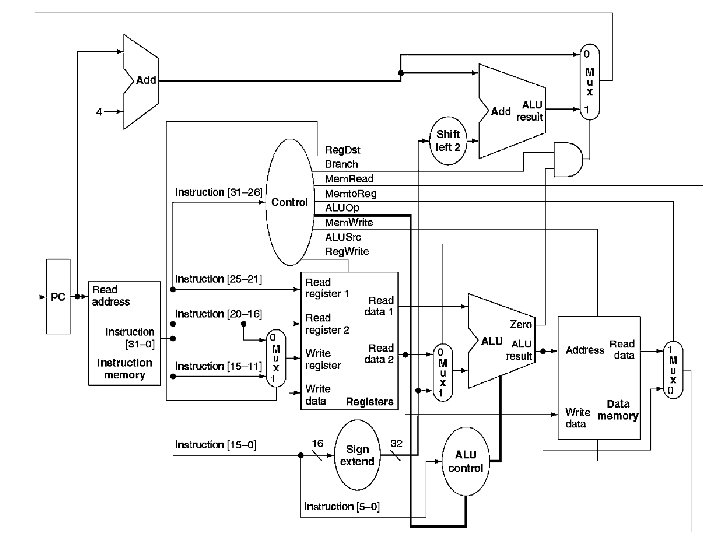

A Unidade de Controle Principal Resumindo: O campo op, também chamado opcode, está sempre contido nos bits 31: 26. OP[5: 0]. Os dois registradores a serem lidos sempre são especificados pelos campos rs e rt, nas posições 25: 21 e 20: 16. (tipo R, beq, sw) O registrador de base para as instruções lw e sw está sempre nas posições 25: 21 (rs). O offset de 16 bits para branch, equal, load e store está sempre nas posições 15: 0 O registrador de destino está em um de dois lugares. Para um lw, ele está na posição 20: 16 (rt). Para uma instrução do tipo R, ele está nas posições 15: 11 (rd)

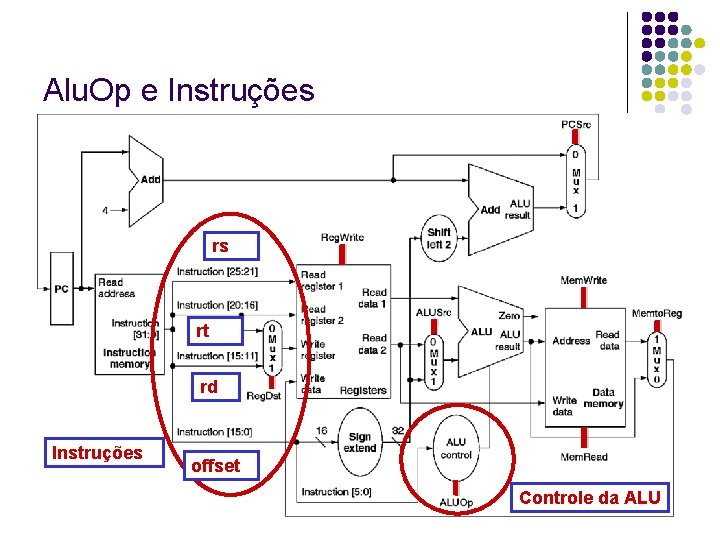

Alu. Op e Instruções rs rt rd Instruções offset Controle da ALU

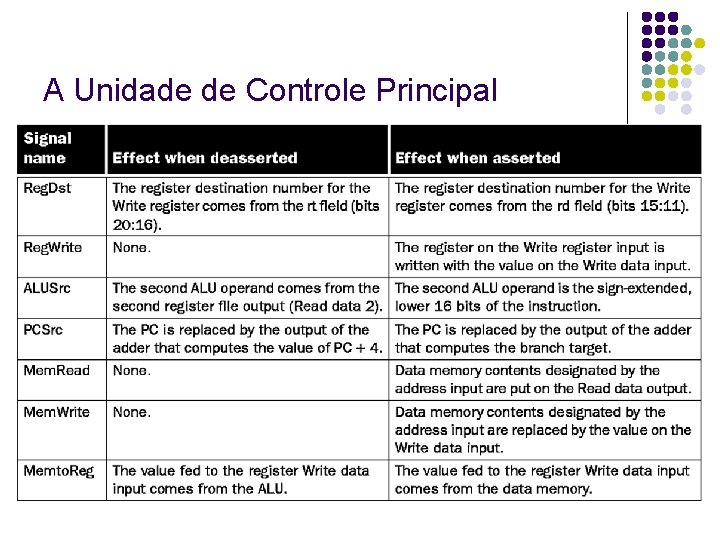

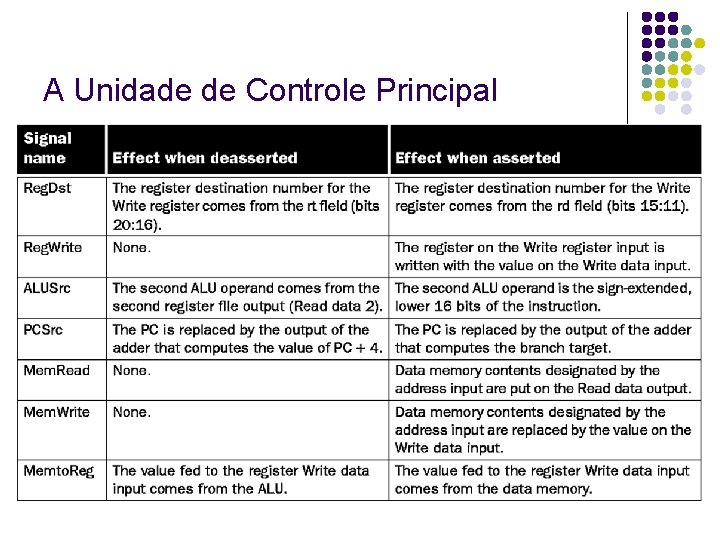

A Unidade de Controle Principal

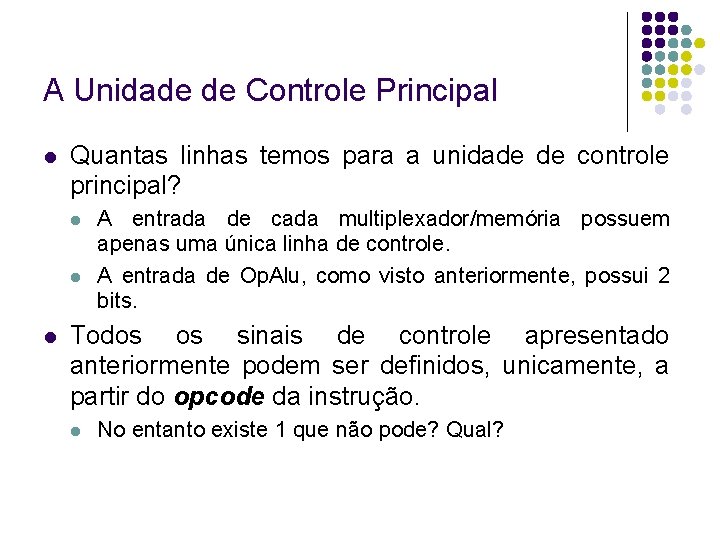

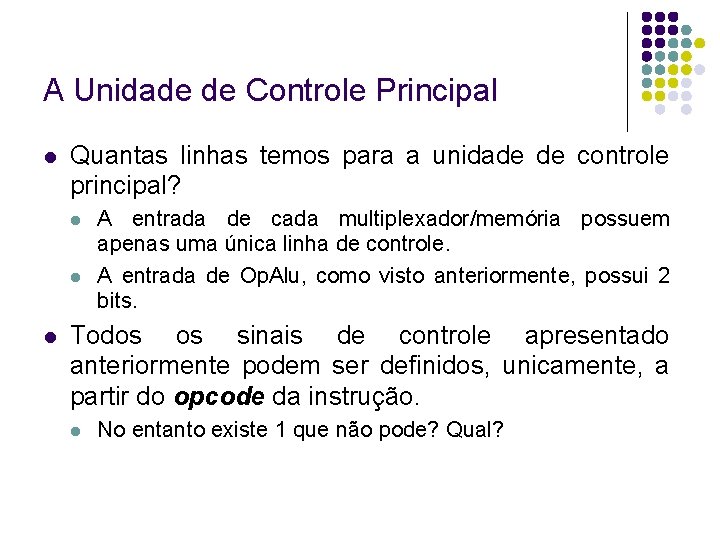

A Unidade de Controle Principal Quantas linhas temos para a unidade de controle principal? A entrada de cada multiplexador/memória possuem apenas uma única linha de controle. A entrada de Op. Alu, como visto anteriormente, possui 2 bits. Todos os sinais de controle apresentado anteriormente podem ser definidos, unicamente, a partir do opcode da instrução. No entanto existe 1 que não pode? Qual?

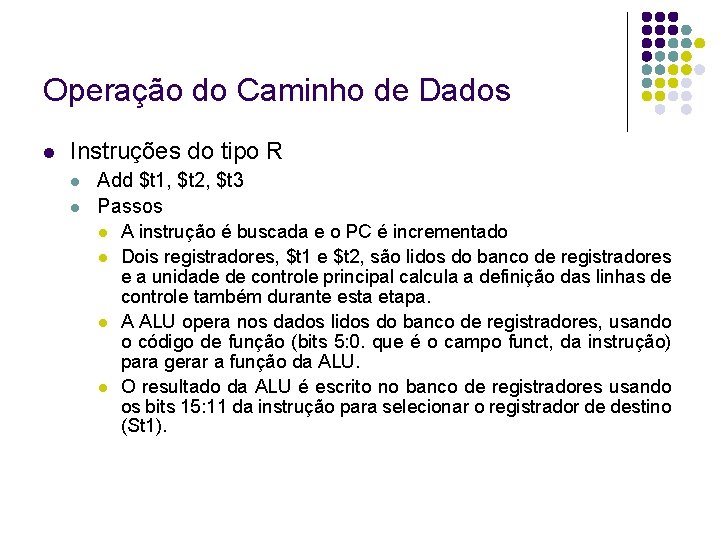

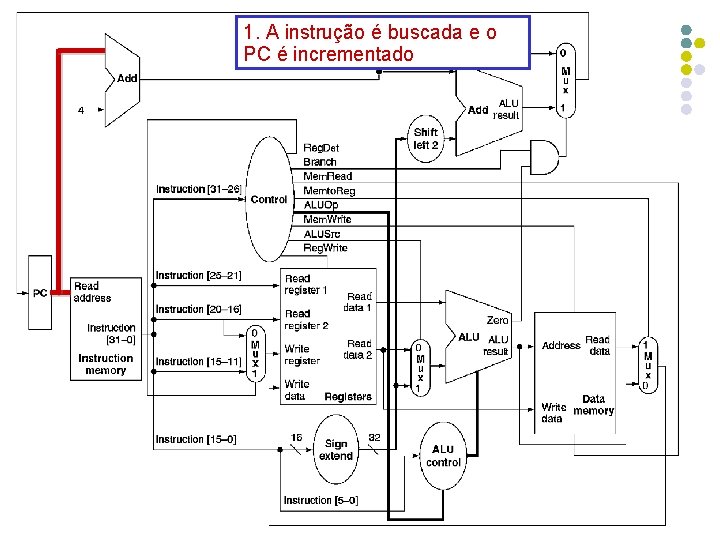

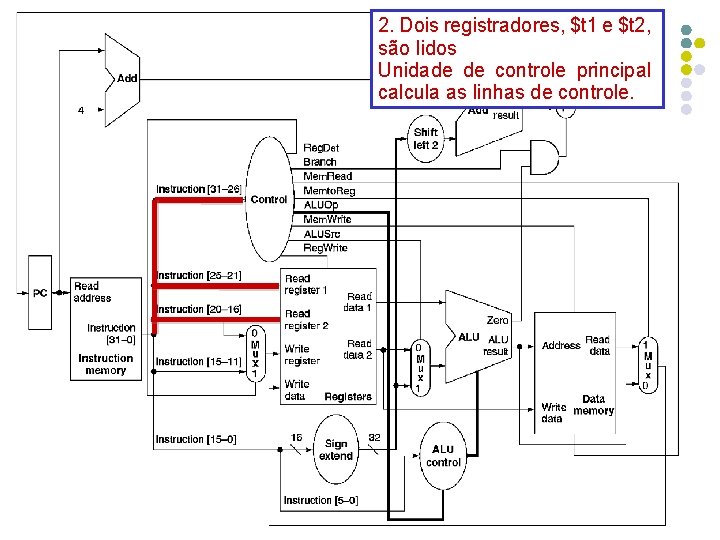

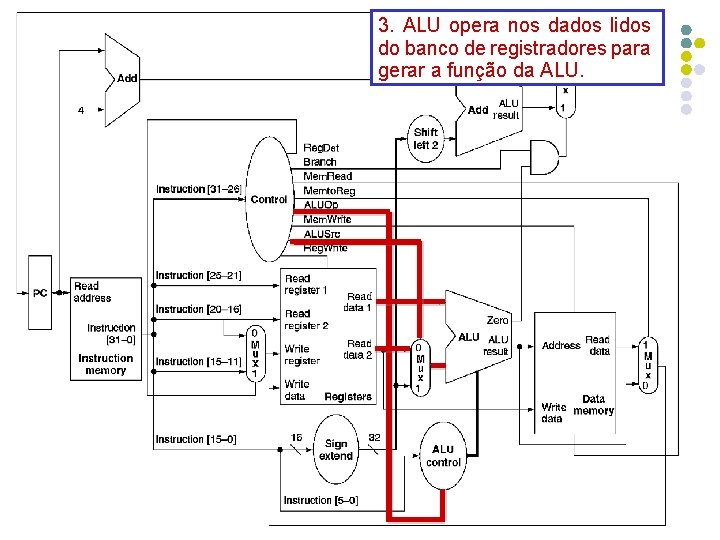

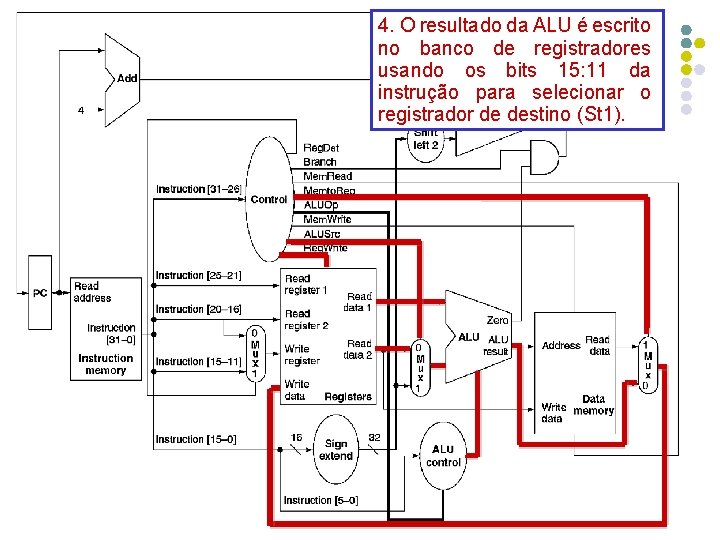

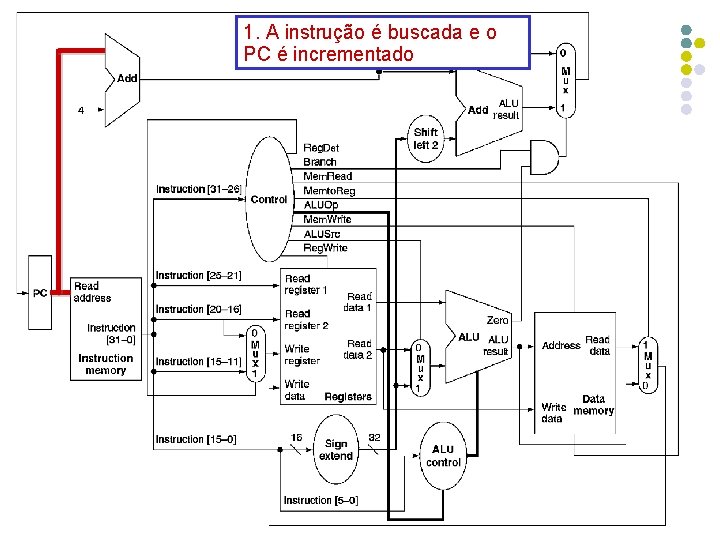

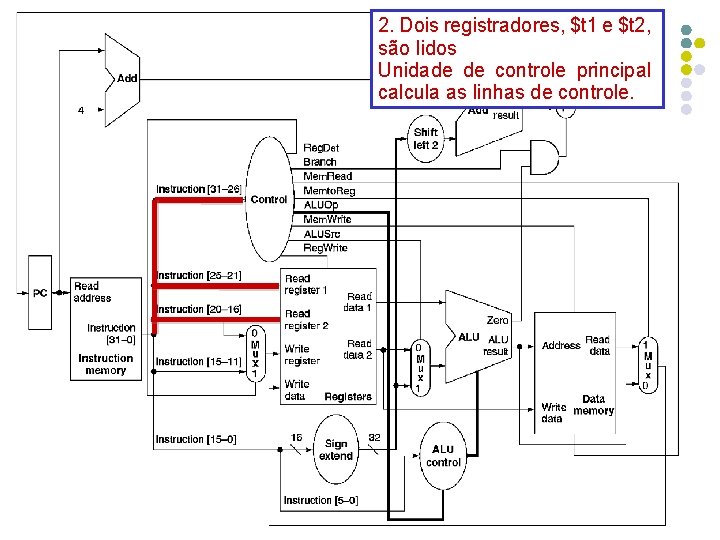

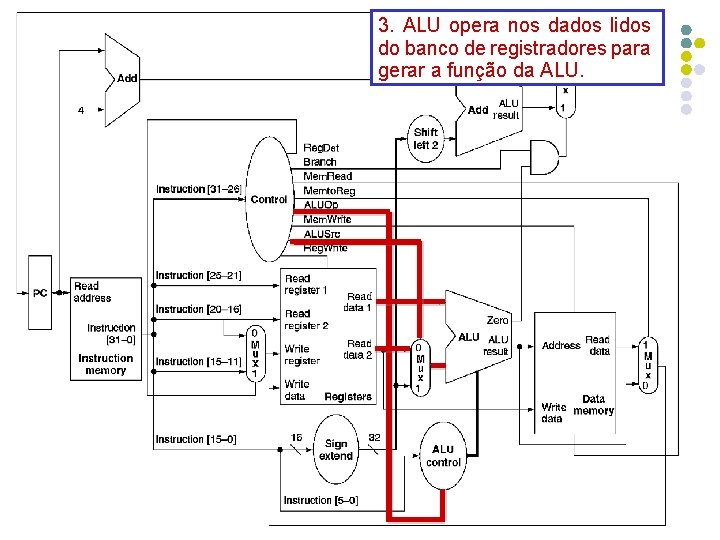

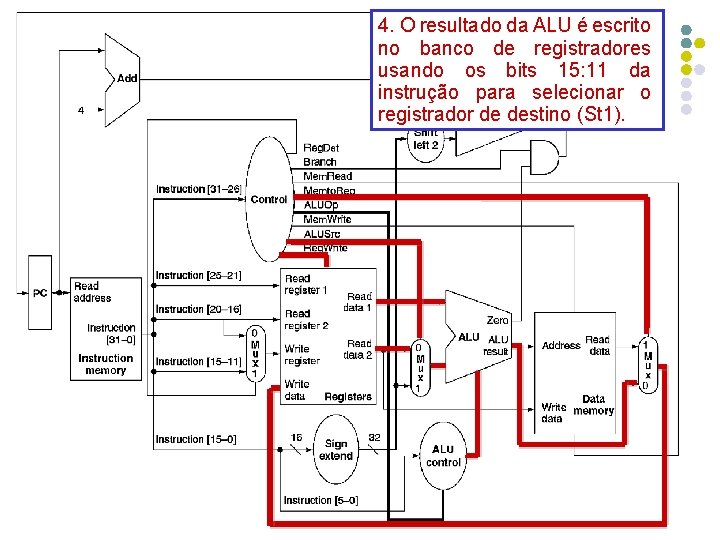

Operação do Caminho de Dados Instruções do tipo R Add $t 1, $t 2, $t 3 Passos A instrução é buscada e o PC é incrementado Dois registradores, $t 1 e $t 2, são lidos do banco de registradores e a unidade de controle principal calcula a definição das linhas de controle também durante esta etapa. A ALU opera nos dados lidos do banco de registradores, usando o código de função (bits 5: 0. que é o campo funct, da instrução) para gerar a função da ALU. O resultado da ALU é escrito no banco de registradores usando os bits 15: 11 da instrução para selecionar o registrador de destino (St 1).

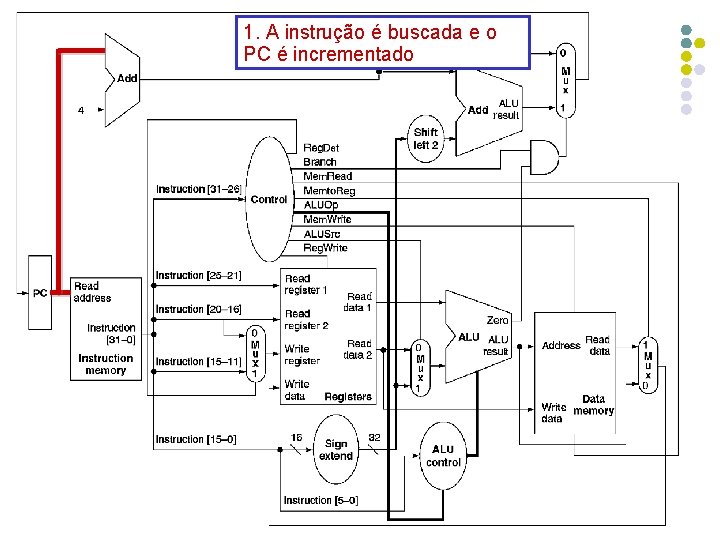

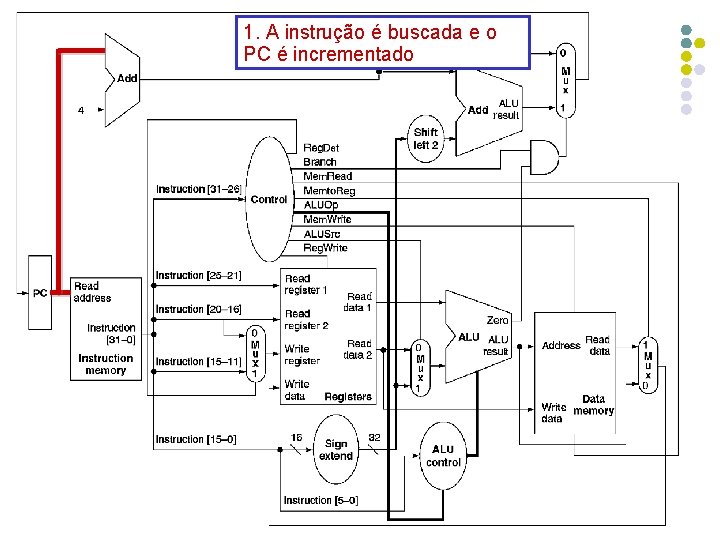

1. A instrução é buscada e o PC é incrementado

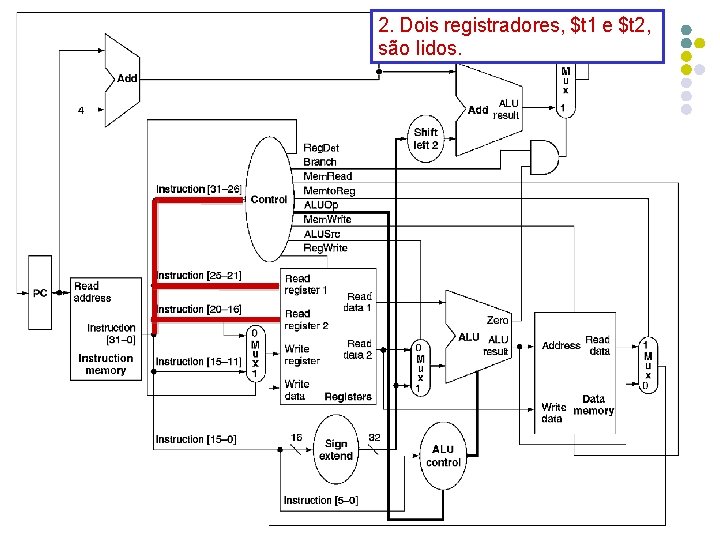

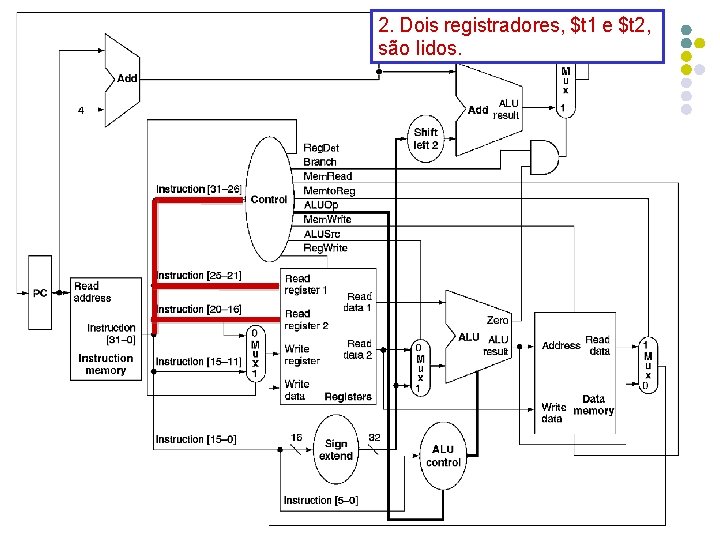

2. Dois registradores, $t 1 e $t 2, são lidos Unidade de controle principal calcula as linhas de controle.

3. ALU opera nos dados lidos do banco de registradores para gerar a função da ALU.

4. O resultado da ALU é escrito no banco de registradores usando os bits 15: 11 da instrução para selecionar o registrador de destino (St 1).

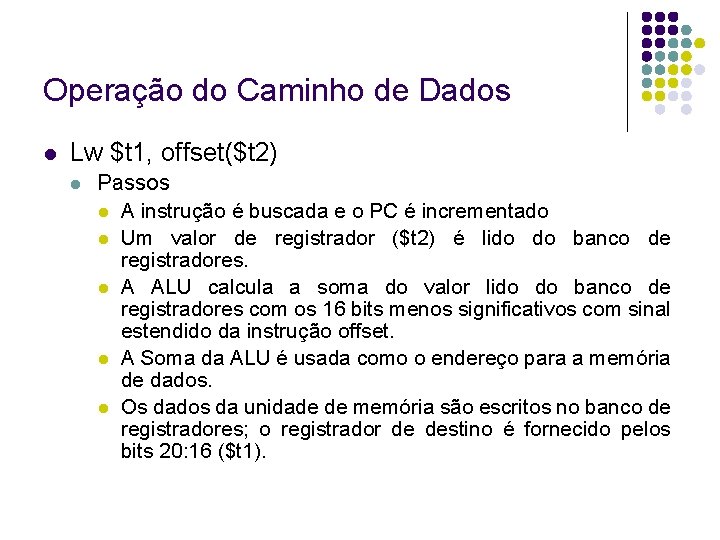

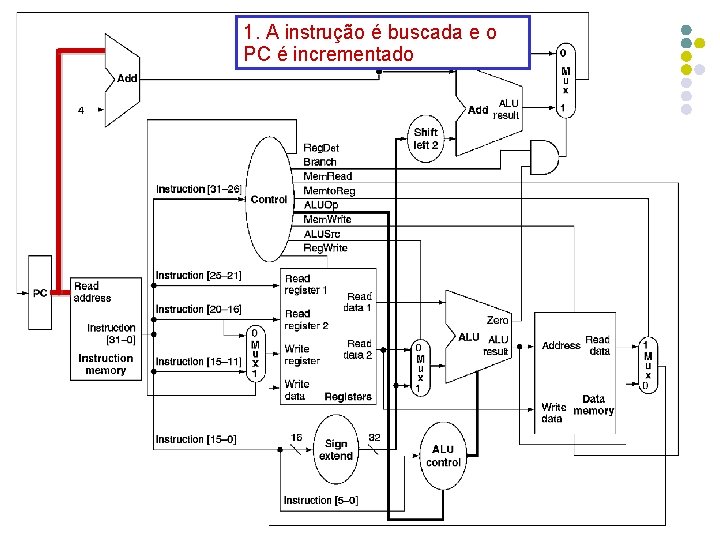

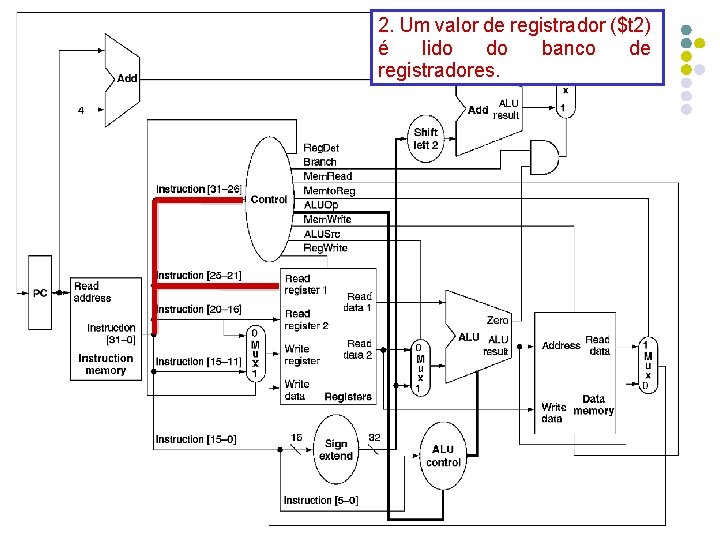

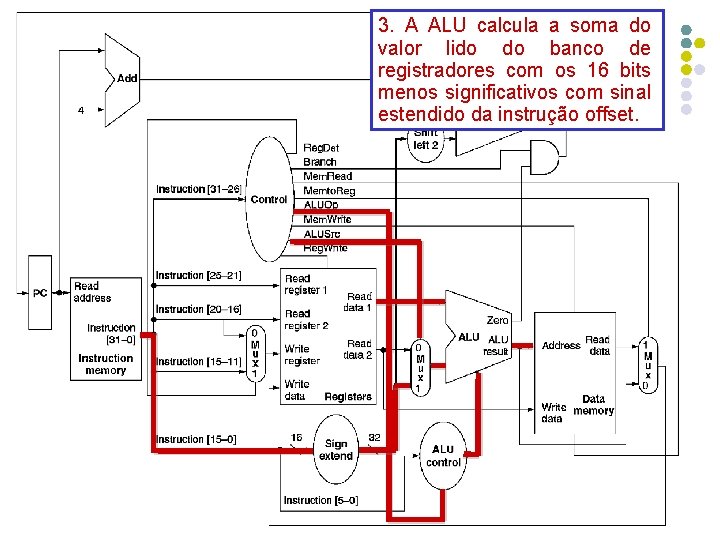

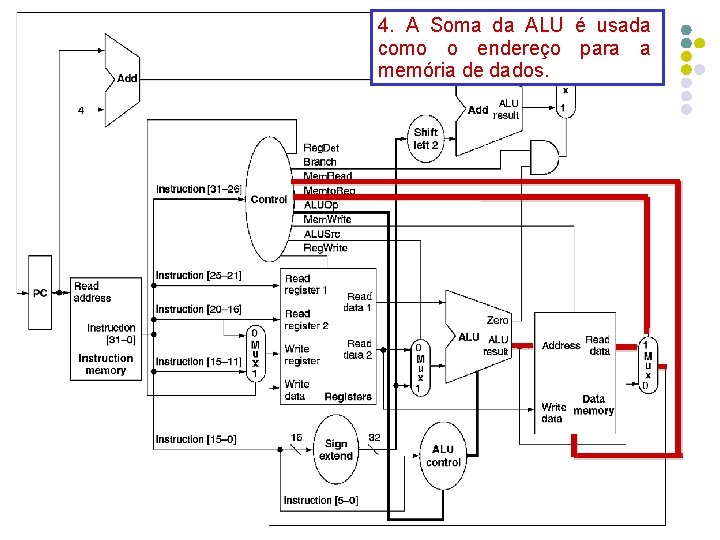

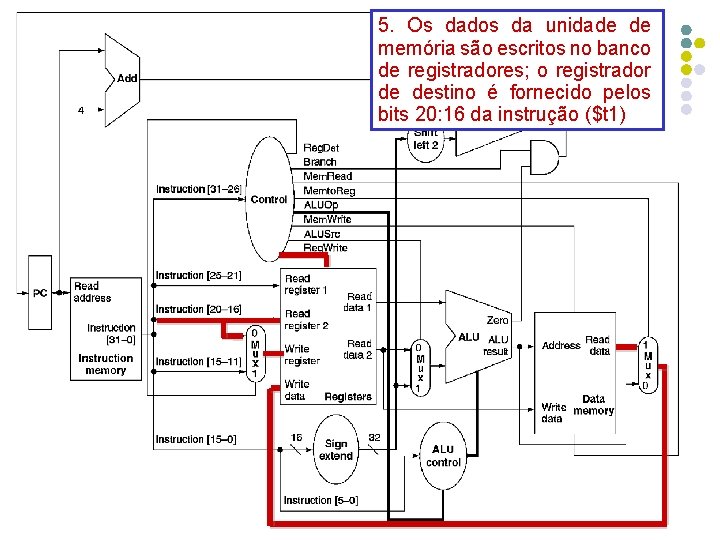

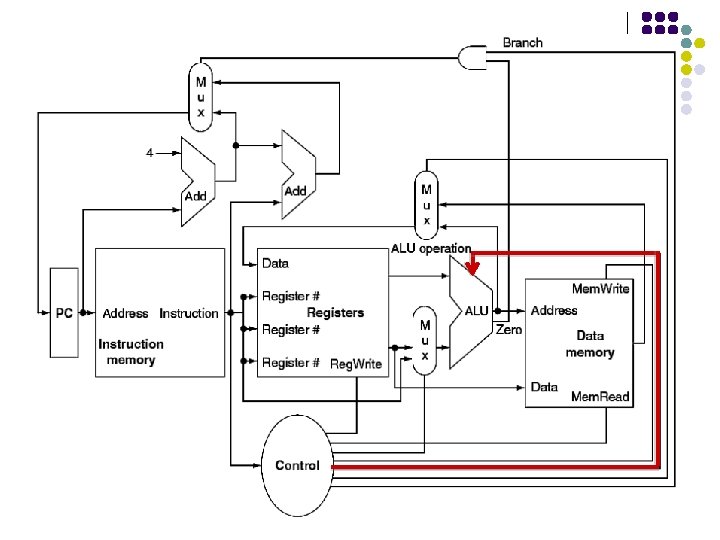

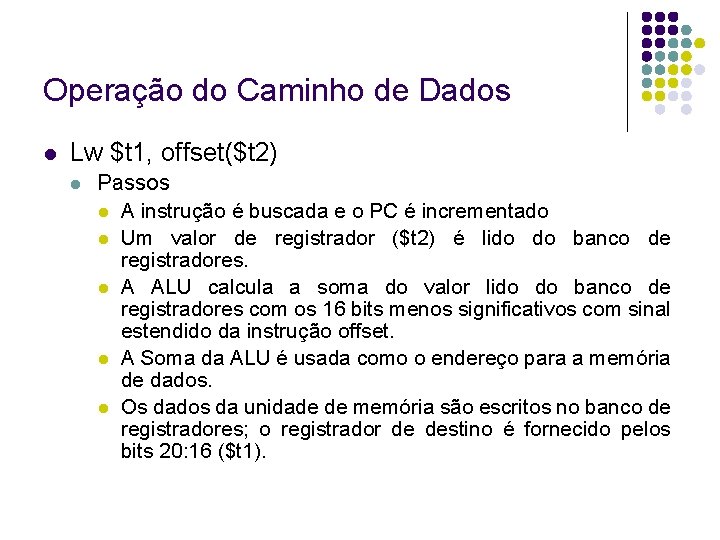

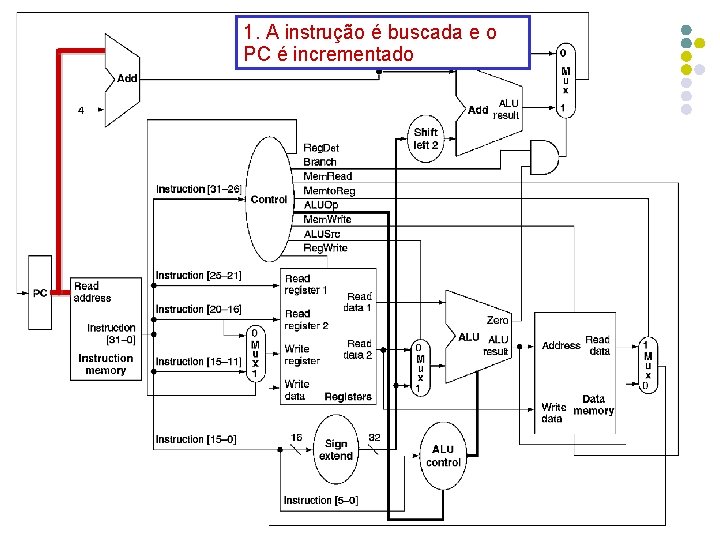

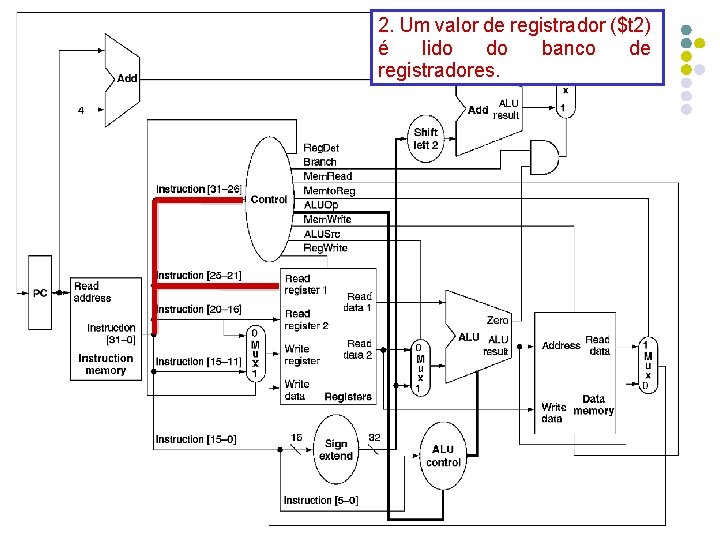

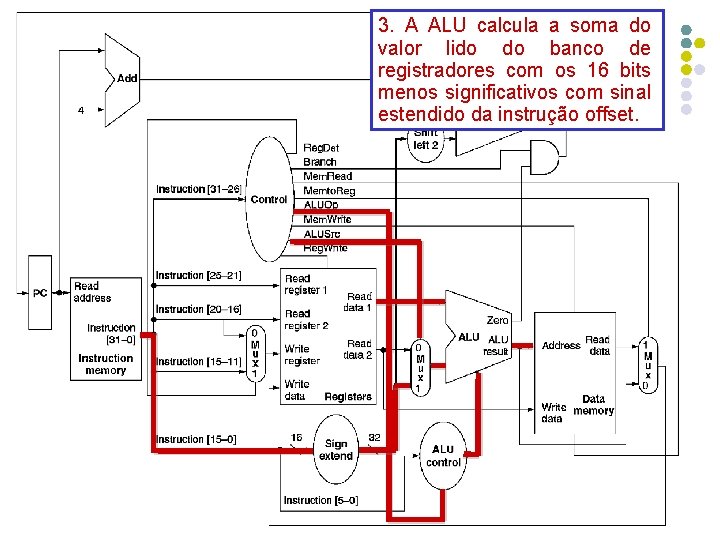

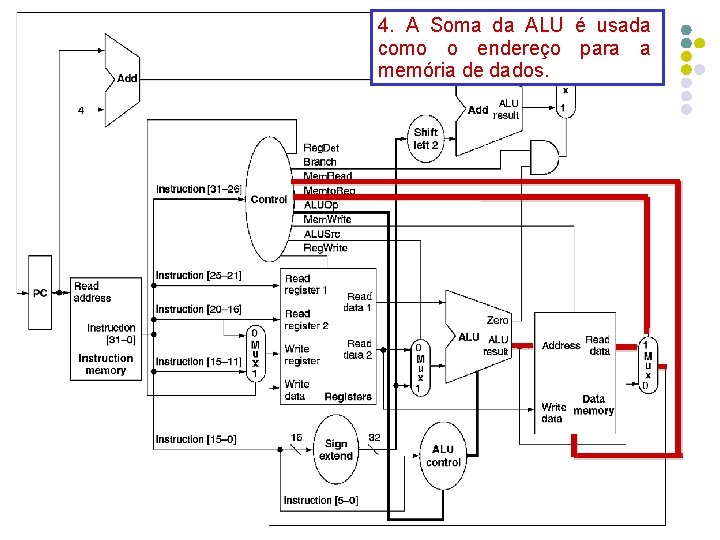

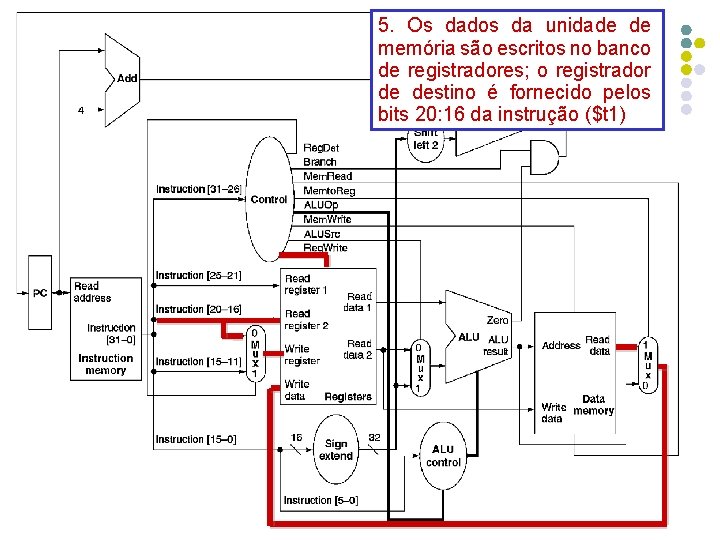

Operação do Caminho de Dados Lw $t 1, offset($t 2) Passos A instrução é buscada e o PC é incrementado Um valor de registrador ($t 2) é lido do banco de registradores. A ALU calcula a soma do valor lido do banco de registradores com os 16 bits menos significativos com sinal estendido da instrução offset. A Soma da ALU é usada como o endereço para a memória de dados. Os dados da unidade de memória são escritos no banco de registradores; o registrador de destino é fornecido pelos bits 20: 16 ($t 1).

1. A instrução é buscada e o PC é incrementado

2. Um valor de registrador ($t 2) é lido do banco de registradores.

3. A ALU calcula a soma do valor lido do banco de registradores com os 16 bits menos significativos com sinal estendido da instrução offset.

4. A Soma da ALU é usada como o endereço para a memória de dados.

5. Os dados da unidade de memória são escritos no banco de registradores; o registrador de destino é fornecido pelos bits 20: 16 da instrução ($t 1)

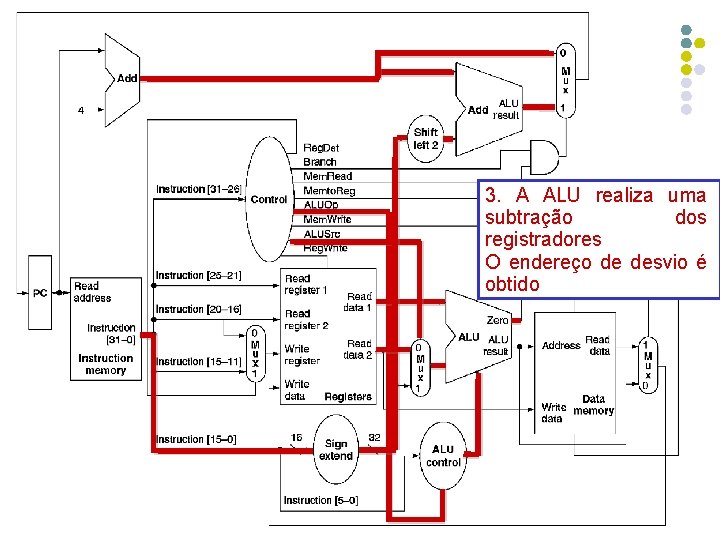

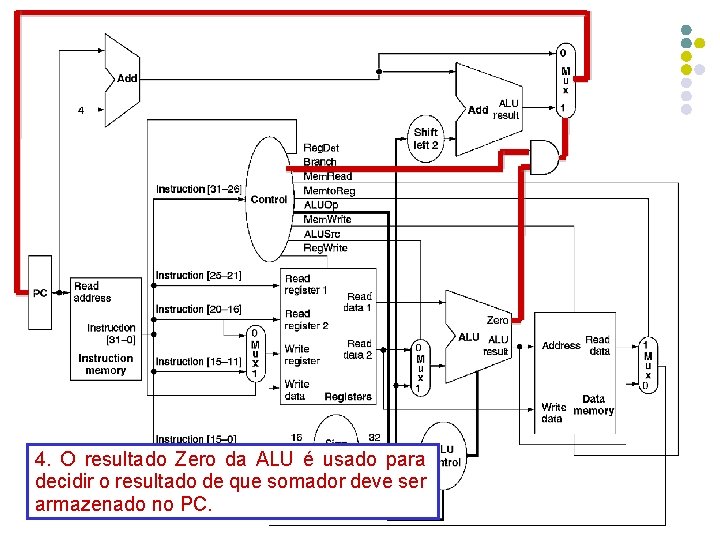

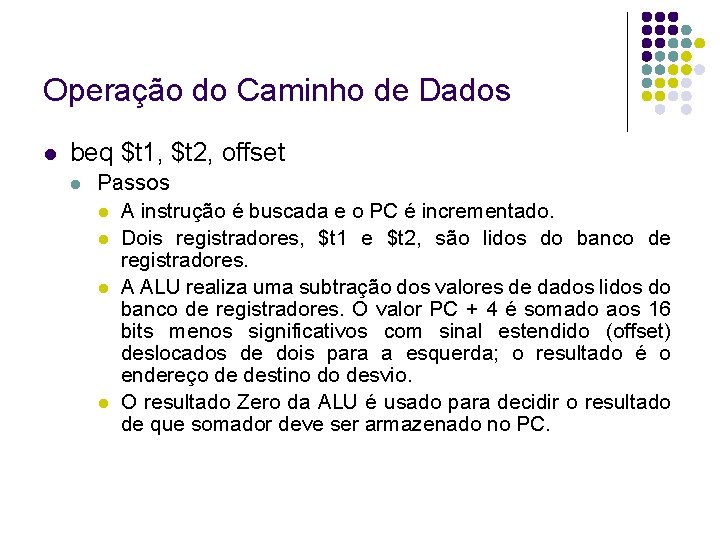

Operação do Caminho de Dados beq $t 1, $t 2, offset Passos A instrução é buscada e o PC é incrementado. Dois registradores, $t 1 e $t 2, são lidos do banco de registradores. A ALU realiza uma subtração dos valores de dados lidos do banco de registradores. O valor PC + 4 é somado aos 16 bits menos significativos com sinal estendido (offset) deslocados de dois para a esquerda; o resultado é o endereço de destino do desvio. O resultado Zero da ALU é usado para decidir o resultado de que somador deve ser armazenado no PC.

1. A instrução é buscada e o PC é incrementado

2. Dois registradores, $t 1 e $t 2, são lidos.

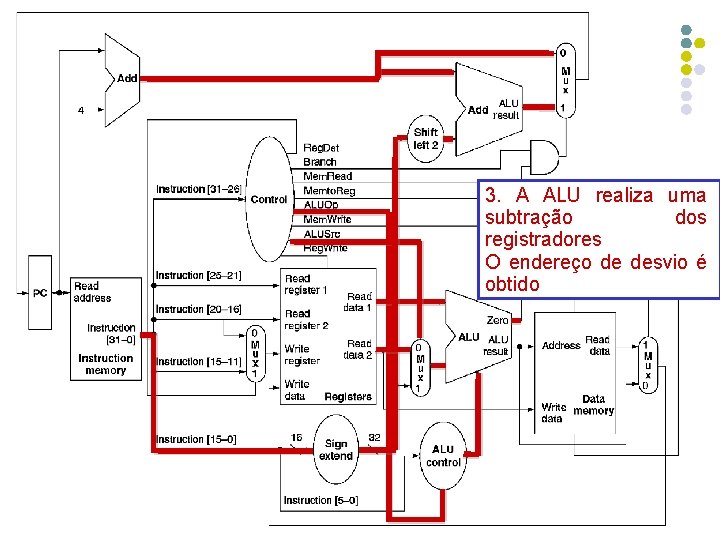

3. A ALU realiza uma subtração dos registradores O endereço de desvio é obtido

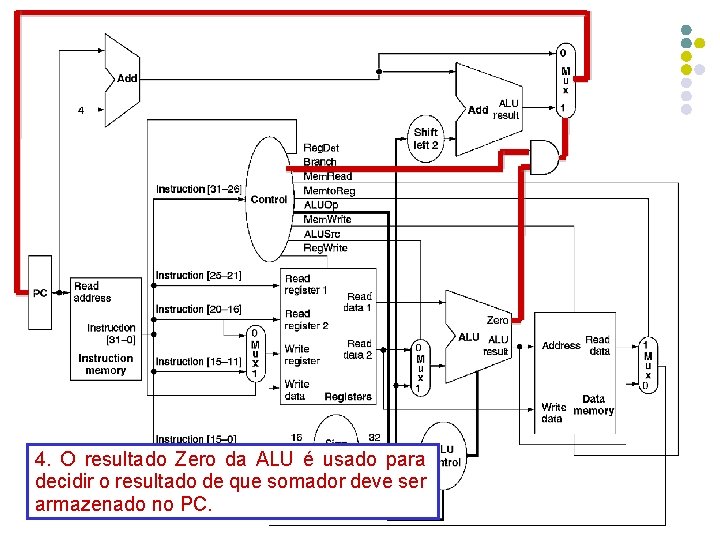

4. O resultado Zero da ALU é usado para decidir o resultado de que somador deve ser armazenado no PC.

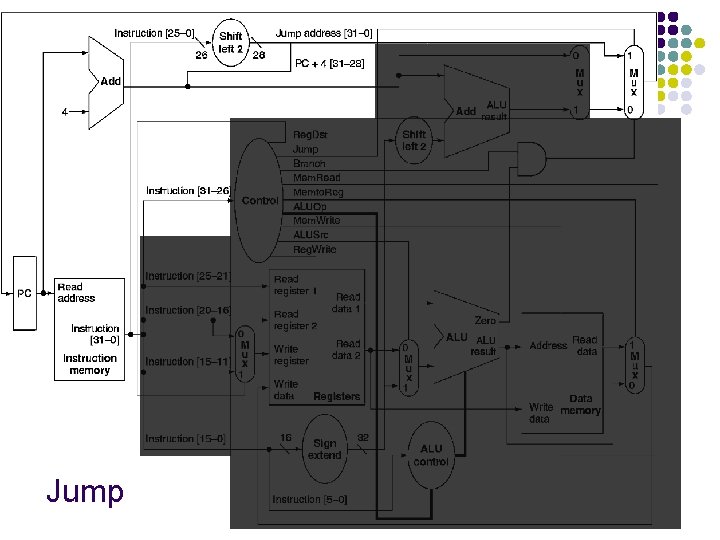

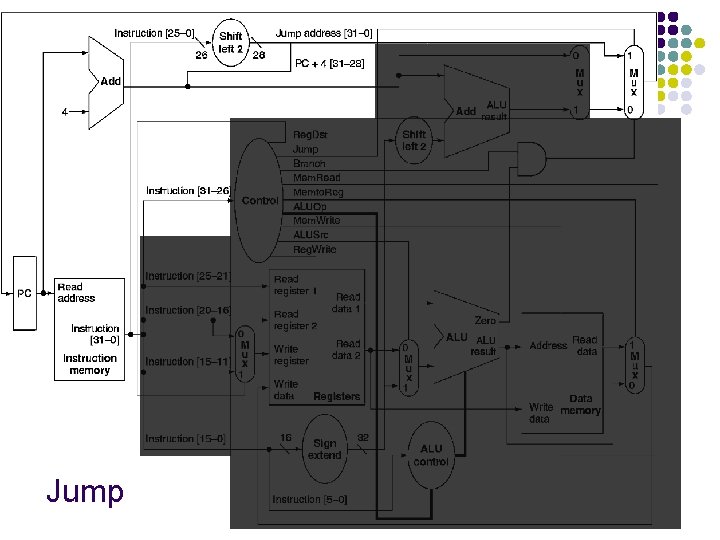

Jump

Referências Hennessy e Patterson Seções 5. 4 e 5. 5