Principle of Microcomputer Based on ARM Technology 37

Principle of Microcomputer Based on ARM Technology (37) 主讲人:陈桂友

CONTENTS • Bridge-in • Objectives • Overview of STM 32 SPI • Structure of SPI • Data frame format • SPI interrupts • Using SPI 2 /12

Bridge-in Review the concept and function of UART. 3 /12

Objectives After learning this section, you will be able to: - know the structure of SPI in STM 32; 4 /12

Overview of STM 32 SPI(1/4) The serial peripheral interface (SPI) allows half/ fullduplex, synchronous, serial communication with external devices. The interface can be configured as the master and in this case it provides the communication clock (SCK) to the external slave device. The interface is also capable of operating in multimaster configuration. 5 /12

Overview of STM 32 SPI(2/4) SPI may be used for a variety of purposes, including simplex synchronous transfers on two lines with a possible bidirectional data line or reliable communication using CRC checking. 6 /12

2. Overview of STM 32 SPI(3/4) SPI features : ● Full-duplex synchronous transfers on three lines ● Simplex synchronous transfers on two lines with or without a bidirectional data line ● 8 - or 16 -bit transfer frame format selection ● Master or slave operation ● Multimaster mode capability ● 8 master mode baud rate prescalers (f PCLK /2 max. ) ● Slave mode frequency (f PCLK /2 max) ● Faster communication for both master and slave 7 /12

2. Overview of STM 32 SPI(4/4) ● NSS management by hardware or software for both master and slave: dynamic change of master/slave operations ● Programmable clock polarity and phase ● Programmable data order with MSB-first or LSB-first shifting ● Dedicated transmission and reception flags with interrupt capability ● SPI busy status flag ● Hardware CRC feature for reliable communication: – CRC value can be transmitted as last byte in Tx mode – Automatic CRC error checking for last received byte ● Master mode fault, overrun and CRC error flags with interrupt capability ● 1 -byte transmission and reception buffer with DMA capability: Tx and Rx requests 8 /12

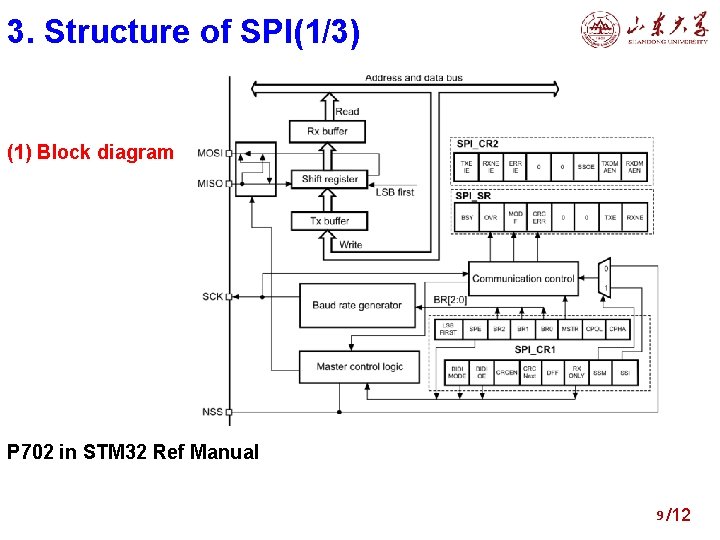

3. Structure of SPI(1/3) (1) Block diagram P 702 in STM 32 Ref Manual 9 /12

3. Structure of SPI(2/3) (2)Pins description: Usually, the SPI is connected to external devices through four pins: • MISO: Master In / Slave Out data. • MOSI: Master Out / Slave In data. • SCK: Serial Clock output for SPI masters and input for SPI slaves. • NSS: Slave select. This is an optional pin to select a slave device. This pin acts as a ‘chip select’ to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave NSS inputs can be driven by standard IO ports on the master device. The NSS pin may also be used as an output if enabled (SSOE bit) and driven low if the SPI is in master configuration. 10 /12

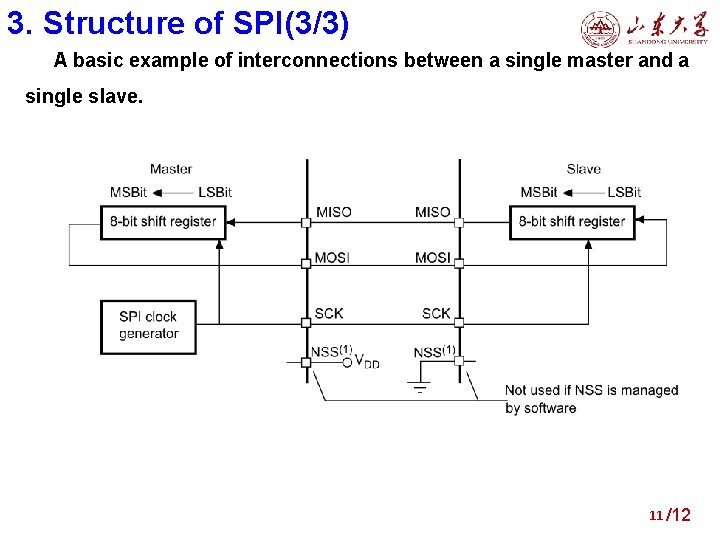

3. Structure of SPI(3/3) A basic example of interconnections between a single master and a single slave. 11 /12

Next lecture chapter 11 STM 32 SPI-2 12 /12

- Slides: 12