Principle of Microcomputer Based on ARM Technology 3

Principle of Microcomputer Based on ARM Technology (3) 主讲人:陈桂友

CONTENTS • Objectives • Introduction • Cortex-M 3 Memory Management • Cortex-M 3 Pipeline, Registers and Operation Modes • Cortex-M 3 Interrupt • Power Management and Reset Sequence • System Timer (Sys. Tick) • Debug Capabilities 2 /19

★Objectives: Ø Familiarize with the meaning of Unaligned Data Support Ø Grasp the method of Atomic Bit Banding Ø Know about Big Endian and Little Endian Ø Know about the memory map 3 /19

Data Memory management (1/12) • Cortex-M 3 includes two technologies to reduce Data memory requirements: 1. Unaligned Data Support 2. Atomic Bit Banding • These technologies can dramatically improve data (SRAM) memory utilization, potentially enabling silicon designers and users to reduce the amount of SRAM required and dramatically impacting silicon usage. 4 /19

Data Memory management(2/12) • Unaligned Data Support: Other Core does not support unaligned data Data aligned on word boundaries Long (32) short (16) Char Unused (wasted) space ARM Cortex-M 3 supports unaligned data that can improve SRAM utilization Long (32) short (16) Char Free space Can be used Reduces SRAM Memory Requirements By Over 50% Less Memory - Low. ER Cost devices 5 /19

Data Memory management(3/12) long (32) char (8) 32 bit machine which does not support unaligned data long (32) char (8) Data aligned int (16) long (32) int (16)c char (8) Structure management example long (32) char (8) long (32) … … long char (8) int (16) long (32) … … long int (16)c char (8) int (16) long … … long (32) int (16) long (32) Unused (wasted) space Free space for the rest of the application Reduces SRAM Memory Requirements By Over 25% 6 /19

Data Memory management(4/12) • Bit Banding: Traditional method Speed and code size optimized Cortex-M 3 implementation Disable external events 32 bit Read byte (RAM, register) 0 1 0 1 1 Mask and modify bit element X X X 1 X X @Rbase+N b 31 b 0 example: 20000000 h to 200 FFFFFh b 31 Write byte (RAM, register) 0 1 0 0 1 1 REAL memory image VIRTUAL aliased bit banding image b 0 Enable external events ♦ Bit Banding done by bus matrix. ♦ Single instruction Read/Modify/Write (no more masking). ♦ No new instruction set Use standard data (AND, OR, XOR…). Optimized RAM, peripherals and IOs registers accesses Easy multi-task semaphore management 7 /19

Data Memory management(5/12) 32 MB alias region 1 MB Peripheral bit-band region 8 /19

Data Memory management(6/12) • Bit Banding formula is: bit_word_addr = bit_band_base + (byte_offset x 32) + (bit_number × 4) where: bit_word_addr: is the address of the word in the alias memory region that maps to the targeted bit_band_base is the starting address of the alias region (0 x 22000000 ) byte_offset is the number of the byte in the bit-band region that contains the targeted bit_number is the bit position of the targeted bit(0 -7). Example -1: How to map bit 2 of the byte located at Peripheral X address 0 x 20000300 in the alias region (Peripheral X based address is 0 x 20000000 ): 9 /19

Data Memory management(7/12) • Solution: 0 x 22006008 = 0 x 22000000 + (0 x 300*32) + (2*4). Writing to address 0 x 22006008 has the same effect as a read-modifywrite operation on bit 2 of the byte at SRAM address 0 x 20000300. Reading address 0 x 22006008 returns the value (0 x 01 or 0 x 00) of bit 2 of the byte at SRAM address 0 x 20000300 (0 x 01: bit set; 0 x 00: bit reset). For more information on Bit-Banding, please refer to the Cortex™-M 3 Technical Reference Manual. For example, to set bit 2 in word data in address 0 x 20000000, we can write 1 to 0 x 22000008. Within the bit-band region, each word is represented by an LSB of 32 words in the bit-band alias address range. In other words, when you access bit-band alias addresses, only the LSB (bit[0]) in the data is used. 10 /19

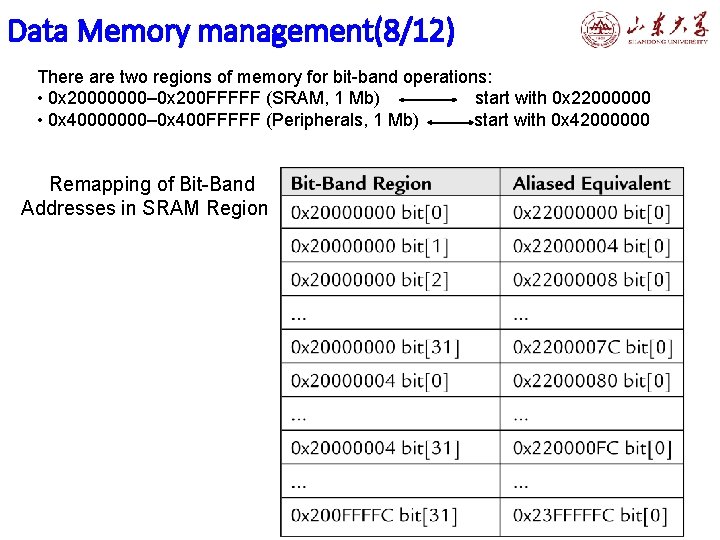

Data Memory management(8/12) There are two regions of memory for bit-band operations: • 0 x 20000000– 0 x 200 FFFFF (SRAM, 1 Mb) start with 0 x 22000000 • 0 x 40000000– 0 x 400 FFFFF (Peripherals, 1 Mb) start with 0 x 42000000 Remapping of Bit-Band Addresses in SRAM Region 11 /19

Data Memory management(9/12) Remapping of Bit-Band Addresses in Peripheral Memory Region 12 /19

Data Memory management(10/12) Bit-Band Operations For example, to set bit 1 in word data in address 0 x 40000000 Assembler Sequence: LDR R 0, =0 x 42000004 MOV R 1, #1 STR R 1, [R 0] ; Setup address ; Setup data ; Write in C Programs: #define DEVICE_REG 0 ((volatile unsigned long *) (0 x 40000000)) #define DEVICE_REG 0_BIT 0 ((volatile unsigned long *) (0 x 42000000)) #define DEVICE_REG 0_BIT 1 ((volatile unsigned long *) (0 x 42000004)) *DEVICE_REG 0_BIT 1 = 0 x 1; // Setting bit 1 using bitband feature // via the bit band alias address 13 /19

Data Memory management(11/12) Bit-Band Operations in C Programs: (Use macros) #define DEVICE_REG 0 0 x 40000000 #define BITBAND(addr, bitnum) ((addr & 0 x. F 0000000)+0 x 02000000+((addr & 0 x. FFFFF)<<5)+(bitnum<<2)) #define MEM_ADDR(addr) *((volatile unsigned long *) (addr)) // Setting bit 1 without using bitband feature MEM_ADDR(DEVICE_REG 0) = MEM_ADDR(DEVICE_REG 0) | 0 x 2; // Setting bit 1 with using bitband feature MEM_ADDR(BITBAND(DEVICE_REG 0, 1)) = 0 x 1; • Ref Bit Banding formula: bit_word_addr = bit_band_base + (byte_offset x 32) + (bit_number × 4) 14 /19

Data Memory management(12/12) Big Endian and Little Endian Big-endian and little-endian are terms that describe the order in which a sequence of bytes are stored in data memory. Big-endian is an order in which the "big end" (most significant value in the sequence) is stored first (at the lowest storage address). Little-endian is an order in which the "little end" (least significant value in the sequence) is stored first. Assume 0 x 12345678 is stored in data memory from the address 0 x 4000. In the little-endian mode: Address 0 x 4000 0 x 4001 0 x 4002 0 x 4003 Contents 0 x 78 0 x 56 0 x 34 0 x 12 In the big-endian mode: Address 0 x 4000 0 x 4001 0 x 4002 0 x 4003 Contents 0 x 12 0 x 34 0 x 56 0 x 78 15 /19

Cortex-M 3 Memory Map 16 /19

Cortex-M 3 Memory Map A Simple Memory Usage Example 17 /19

Cortex-M 3 Memory Map The Cortex-M 3 has a predefined memory map. This allows the built-in peripherals, such as the interrupt controller and debug components, to be accessed by simple memory access instructions. Thus most system features are accessible in C program code. The Bus Interface There are several bus interfaces on the Cortex-M 3 processor. They allow the Cortex-M 3 to carry instruction fetches and data accesses at the same time. The main bus interfaces are: I-Code: instruction fetches • Code memory buses D-Code: table look-up • System bus: is used to access memory and peripherals. This provides access to the SRAM, peripherals, external RAM, external devices, and part of the systemlevel memory regions. • Private peripheral bus: debugging components 18 /19

Next lecture Cortex-M 3 Pipeline, Registers and Operation Modes 19 /19

- Slides: 19