Principle of Microcomputer Based on ARM Technology 25

Principle of Microcomputer Based on ARM Technology (25) 主讲人:陈桂友

CONTENTS • Objectives • Overview of STM 32 interrupts • Priority of STM 32 interrupts • External interrupt/event controller (EXTI) • Using external interrupts 2 /14

Bridge-in Review the conception of exception and interrupt in Cortex M 3. Review the characters of exceptions in Cortex M 3. How many exceptions and interrupts are there in Cortex M 3? 256 exceptions: 16 core exceptions + 240 external interrupts. 256 priority levels. 3 /14

★Objectives: know the structure of interrupts module in STM 32 Know the registers related to interrupts module in STM 32 4 /14

Overview of STM 32 interrupts(1/2) As the Cortex M 3 core is adopted, the mechanism of exception is kept in STM 32. The NVIC of STM 32 is a subset of Cortex M 3 NVIC. When an exception takes place, the registers PC, PSR, R 0–R 3, R 12, and LR are pushed to the stack. While the data bus (Dbus) is busy stacking the registers, the instruction bus (Ibus) carries out another important task of the interrupt sequence: It fetches the exception vector (the starting address of the exception handler) from the vector table. Since the stacking and vector fetch are performed on separate bus interfaces, they can be carried out at the same time. After the stacking and vector fetch are completed, the exception will start to execute. At the end of the exception handler, an exception exit (known as an interrupt return in some processors) is required to restore the system status so that the interrupted program can resume normal execution. 5 /14

Overview of STM 32 interrupts(2/2) Features of Nested vectored interrupt controller (NVIC) All interrupts including the core exceptions are managed by the NVIC. ● up to 81 interrupts (depends on the STM 32 device type) ● A programmable priority level of 0 -15 for each interrupt. A higher number corresponds to a lower priority, so level 0 is the highest interrupt priority ● Low-latency exception and interrupt handling ● Preempt priority and subpriority ● An external Non-maskable interrupt (NMI) 6 /14

Priority of STM 32 interrupts(1/6) Preempt priority and subpriority Using a configuration register in the NVIC called Priority Group, the priority-level configuration registers for each exception with programmable priority levels is divided into two halves. The upper half (left bits) is the preempt priority, and the lower half (right bits) is the subpriority. u Preempt priority An interrupt with higher preempt priority level can interrupt main program or another interrupt with lower preempt priority. ----- Interrupt Nested 7 /14

Priority of STM 32 interrupts(2/6) u Subpriority The subpriority level value is used only when two exceptions with same preempt priority level occur at the same time. In this case, the exception with higher subpriority (lower value) will be handled first. When an exception is handling, another exception with same preempt priority level can not interrupt it. Exceptions with same preempt priority level can NOT be nested. u Sequence of exceptions response Consider the preemption firstly, and then the subpriority. Nested character is dominated by preempt priority. 8 /14

Priority of STM 32 interrupts(3/6) u How to deal with the confliction of priority? As we know, an interrupt with higher preempt priority level can interrupt main program or another interrupt with lower preempt priority. It is called Interrupt Nested. Two exceptions with same preempt priority level can not be nested with each other. When two exceptions with same preempt priority level occur at the same time, the exception with higher subpriority (lower value) will be handled first. When two exceptions with same preempt priority level and same subpriority occur at the same time, they will be handled by the order of the position listed in the vector table. 9 /14

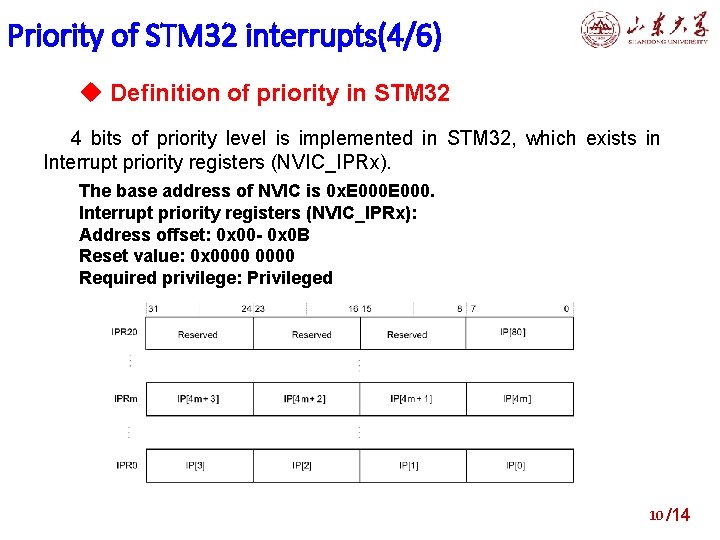

Priority of STM 32 interrupts(4/6) u Definition of priority in STM 32 4 bits of priority level is implemented in STM 32, which exists in Interrupt priority registers (NVIC_IPRx). The base address of NVIC is 0 x. E 000. Interrupt priority registers (NVIC_IPRx): Address offset: 0 x 00 - 0 x 0 B Reset value: 0 x 0000 Required privilege: Privileged 10 /14

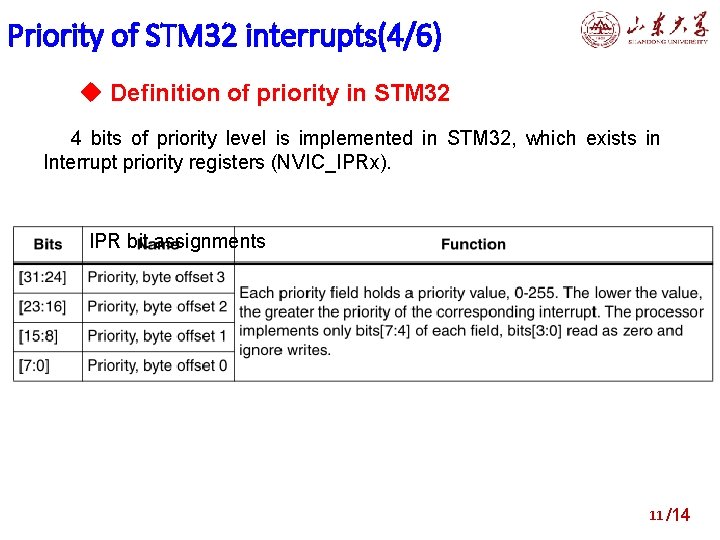

Priority of STM 32 interrupts(4/6) u Definition of priority in STM 32 4 bits of priority level is implemented in STM 32, which exists in Interrupt priority registers (NVIC_IPRx). IPR bit assignments 11 /14

![Priority of STM 32 interrupts(5/6) u Definition of priority in STM 32 Bits[7: 4] Priority of STM 32 interrupts(5/6) u Definition of priority in STM 32 Bits[7: 4]](http://slidetodoc.com/presentation_image_h2/7b82664ad709d1907f3626d9d6f6970d/image-12.jpg)

Priority of STM 32 interrupts(5/6) u Definition of priority in STM 32 Bits[7: 4] in each field of IPR are used to specify the two priority types. Preemption Priority and Subpriority in STM 32. There are 5 groups described by 4 bits of priority register. Preemption Priority Group Preemption Priority Level Subpriority Level 4 4 bits/16 levels 0 bit/ 0 level 3 3 bits/8 levels 1 bit/2 levels 2 2 bits/4 levels 1 1 bit/2 levels 3 bits/8 levels 0 0 bit/ 0 level 4 bits/16 levels Subpriority 12 /14

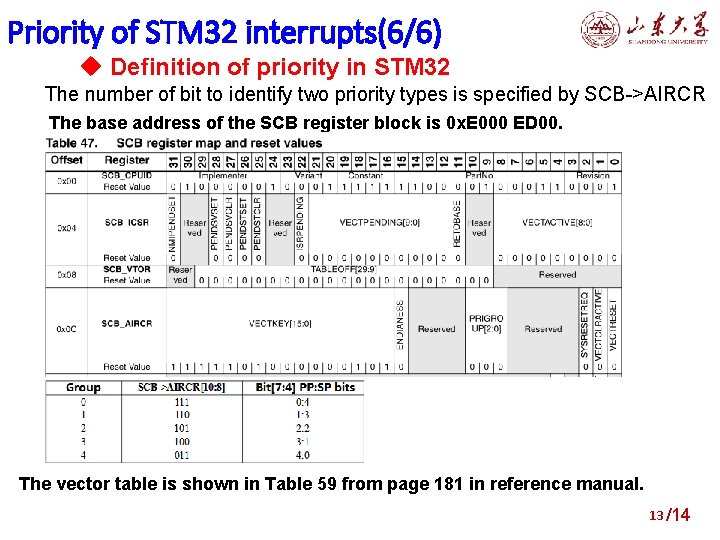

Priority of STM 32 interrupts(6/6) u Definition of priority in STM 32 The number of bit to identify two priority types is specified by SCB->AIRCR The base address of the SCB register block is 0 x. E 000 ED 00. The vector table is shown in Table 59 from page 181 in reference manual. 13 /14

Next lecture chapter 7 STM 32 interrupts-2 14 /14

- Slides: 14