Presented by Manfred Muecke CERN Unified Model Generation

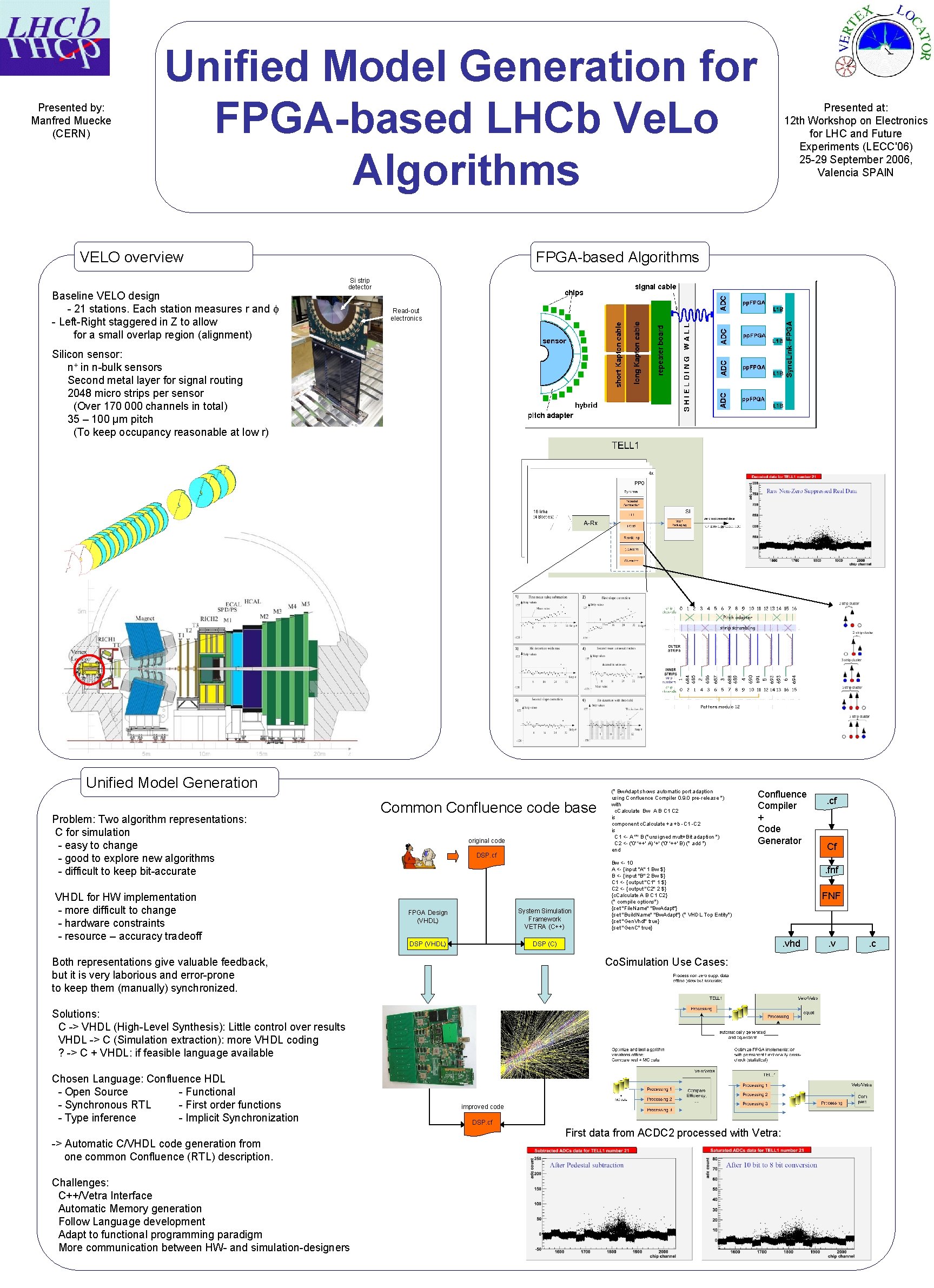

Presented by: Manfred Muecke (CERN) Unified Model Generation for FPGA-based LHCb Ve. Lo Algorithms VELO overview Baseline VELO design - 21 stations. Each station measures r and - Left-Right staggered in Z to allow for a small overlap region (alignment) Presented at: 12 th Workshop on Electronics for LHC and Future Experiments (LECC'06) 25 -29 September 2006, Valencia SPAIN FPGA-based Algorithms Si strip detector Read-out electronics Silicon sensor: n+ in n-bulk sensors Second metal layer for signal routing 2048 micro strips per sensor (Over 170 000 channels in total) 35 – 100 μm pitch (To keep occupancy reasonable at low r) Unified Model Generation Problem: Two algorithm representations: C for simulation - easy to change - good to explore new algorithms - difficult to keep bit-accurate VHDL for HW implementation - more difficult to change - hardware constraints - resource – accuracy tradeoff Common Confluence code base original code DSP. cf FPGA Design (VHDL) System Simulation Framework VETRA (C++) DSP (VHDL) DSP (C) (* Bw. Adapt shows automatic port adaption using Confluence Compiler 0. 9. 0 pre-release *) with c. Calculate Bw A B C 1 C 2 is component c. Calculate +a +b -C 1 -C 2 is C 1 <- A '*' B (*unsigned mult+Bit adaption *) C 2 <- ('0' '++' A) '+' ('0' '++' B) (* add *) end Confluence Compiler + Code Generator Bw <- 10 A <- {input "A" 1 Bw $} B <- {input "B" 2 Bw $} C 1 <- {output "C 1" 1 $} C 2 <- {output "C 2" 2 $} {c. Calculate A B C 1 C 2} (* compile options*) {set "File. Name" "Bw. Adapt"} {set "Build. Name" "Bw. Adapt"} (* VHDL Top Entity*) {set "Gen. Vhdl" true} {set "Gen. C" true} Solutions: C -> VHDL (High-Level Synthesis): Little control over results VHDL -> C (Simulation extraction): more VHDL coding ? -> C + VHDL: if feasible language available Chosen Language: Confluence HDL - Open Source - Functional - Synchronous RTL - First order functions - Type inference - Implicit Synchronization -> Automatic C/VHDL code generation from one common Confluence (RTL) description. Challenges: C++/Vetra Interface Automatic Memory generation Follow Language development Adapt to functional programming paradigm More communication between HW- and simulation-designers improved code DSP. cf First data from ACDC 2 processed with Vetra: Cf. fnf FNF . vhd Co. Simulation Use Cases: Both representations give valuable feedback, but it is very laborious and error-prone to keep them (manually) synchronized. . cf . v . c

- Slides: 1