Preparation run TezzaronChartered Introduction Preparation FEI 4 Preparation

- Slides: 9

Preparation run Tezzaron-Chartered • Introduction Preparation FE-I 4 • Preparation FE-TC 4 -Proto • Tests CPPM FE-I 4 -Proto • Tests au PS CERN en 2009 CPPM 20 Fevrierr 2009 A. Rozanov 1

Preparation run Tezzaron-Chartered • Preparation FE-I 4 Review au CERN 2 mars 2009 - participation • 15. 03. 09 Soumision de FE-I 4 -Proto 2 – discriminateur basse consomation • 15. 03. 05 Soumision de SEU-test 3 – ameliorations des registres • juin 2009 test de FE-I 4 -Proto 2 et SEU-test 3 au CPPM • juillet 2009 test de SEU-test 3 au PS CERN • juillet-aout 2009 soumision de FE-I 4 CPPM 20 Fevrierr 2009 A. Rozanov 2

Preparation run Tezzaron-Chartered • Preparation FE-TC 4 -Proto Tier-analogique: FE-C 4 -Proto + switch to Tier digital + vias to bump bonds + vias to wire-bond (new) + reduction vers 5 couches metal • Tier-digital: two versions • Simple – memoire “big pipe-line” shift registers • Complex – a la future FE-I 4 - local buffer+trigger logic+clustering • Une double coulonne avec discri basse tension de Mohsine ? • Portage chip SEU-TC ? ? • Test chip SLHC-ILC (daisy chains, transistors, logique sous wire bonds etc)? ? ? CPPM 20 Fevrierr 2009 A. Rozanov 3

Preparation run Tezzaron-Chartered • Test CPPM FE-I 4 -Proto Preparation pour test FE-C 4 -Proto(mai), FE-I 4 -Proto 2(juin), FE-TC 4 -proto (aout) • 3 setups • Test setup registre SEU – Patrick(CPPM) • Test setup LBNL (carte USB National, Soft LBNL NI studio) • Test setup. Bonn (carte USB Bonn, soft Bonn • Deux chips: new at CPPM, irradiated at CERN • Mesure: dispersion thresholds, noise (S-curves) CPPM 20 Fevrierr 2009 A. Rozanov 4

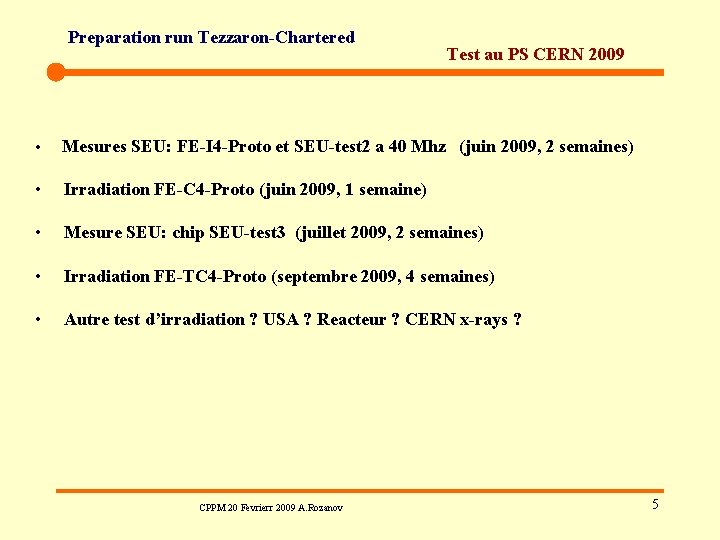

Preparation run Tezzaron-Chartered Test au PS CERN 2009 • Mesures SEU: FE-I 4 -Proto et SEU-test 2 a 40 Mhz (juin 2009, 2 semaines) • Irradiation FE-C 4 -Proto (juin 2009, 1 semaine) • Mesure SEU: chip SEU-test 3 (juillet 2009, 2 semaines) • Irradiation FE-TC 4 -Proto (septembre 2009, 4 semaines) • Autre test d’irradiation ? USA ? Reacteur ? CERN x-rays ? CPPM 20 Fevrierr 2009 A. Rozanov 5

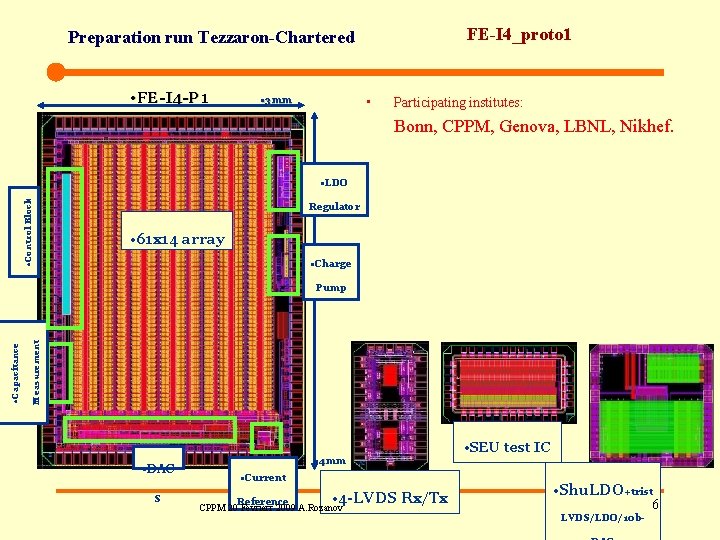

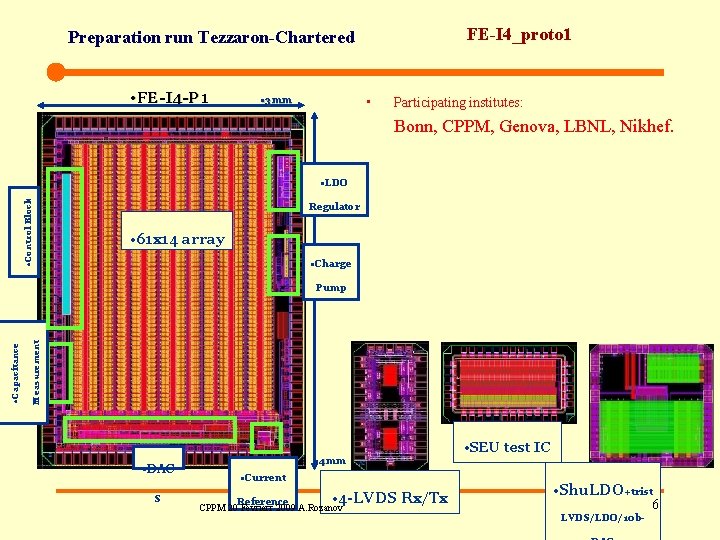

FE-I 4_proto 1 Preparation run Tezzaron-Chartered • FE-I 4 -P 1 • 3 mm • Participating institutes: Bonn, CPPM, Genova, LBNL, Nikhef. • Control Block • LDO Regulator • 61 x 14 array • Charge Measurement • Capacitance Pump • DAC s • SEU test IC • 4 mm • Current • 4 -LVDS Reference CPPM 20 Fevrierr 2009 A. Rozanov Rx/Tx • Shu. LDO+trist LVDS/LDO/10 b- 6

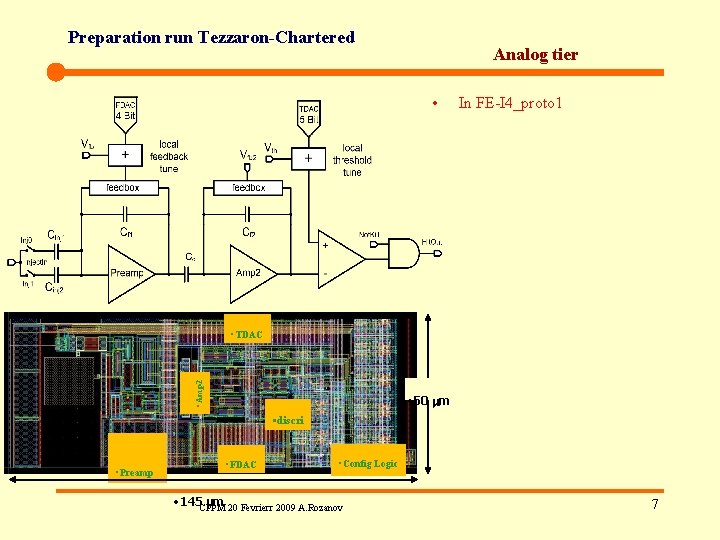

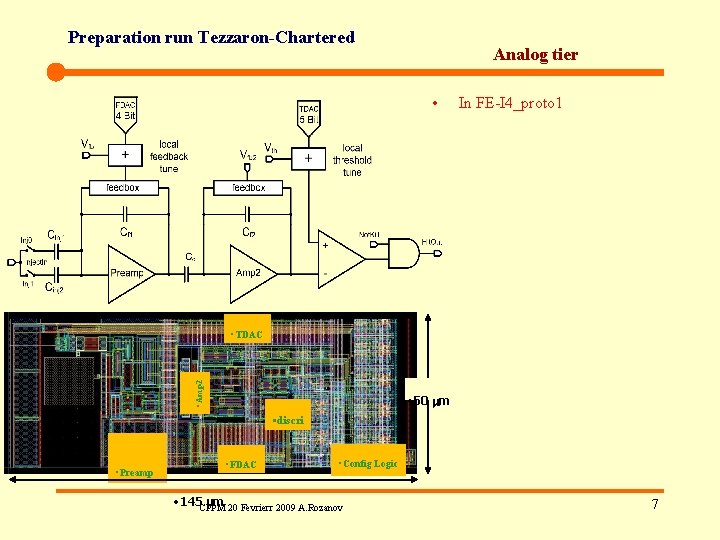

Preparation run Tezzaron-Chartered Analog tier • In FE-I 4_proto 1 • Amp 2 • TDAC • 50 mm • discri • Preamp • FDAC • Config Logic • 145 CPPM mm 20 Fevrierr 2009 A. Rozanov 7

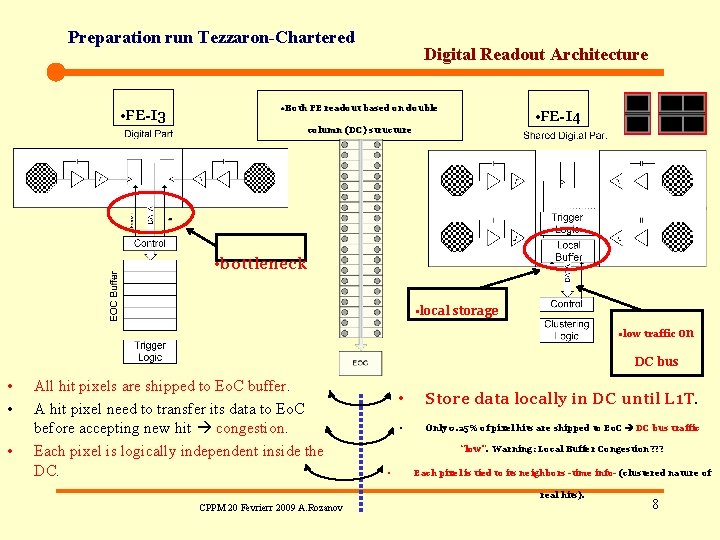

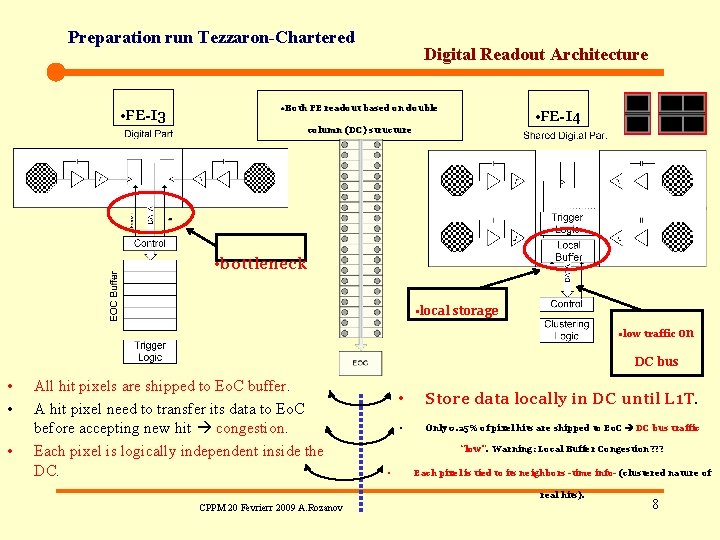

Preparation run Tezzaron-Chartered • FE-I 3 Digital Readout Architecture • Both FE readout based on double • FE-I 4 column (DC) structure • bottleneck • local storage • low traffic on DC bus • • • All hit pixels are shipped to Eo. C buffer. A hit pixel need to transfer its data to Eo. C before accepting new hit congestion. Each pixel is logically independent inside the DC. • Store data locally in DC until L 1 T. • Only 0. 25% of pixel hits are shipped to Eo. C DC bus traffic “low”. Warning: Local Buffer Congestion? ? ? • Each pixel is tied to its neighbors -time info- (clustered nature of real hits). CPPM 20 Fevrierr 2009 A. Rozanov 8

Preparation run Tezzaron-Chartered • Details Utiliser (ou non) les couches bonding pour les bus Vdd /Vdda ? • Multiplicite des points de bonding: Fe-I 4 a naturellement 4 types de pixels, donc motif de (12+1+12)x(62+1+62)=2*50 um x 2*125 um • Passage de tier 1 a tiers 2 via les bus lines s’ils ne sont pas dans chaque pixel ? CPPM 20 Fevrierr 2009 A. Rozanov 9