Practical Implementation of a IEEE 1588 Based Synchronization

Practical Implementation of a IEEE 1588 Based Synchronization Distribution System DANIEL GALLANT – ITSF NOVEMBER 2018

Agenda − Practical Implementation of a T-BC − To. D Synchronization Between Master and Slave − To. D Synchronization within the Network Element − Challenges of Meeting 5 ns Time Error − Possible Solutions for Meeting 5 ns and Beyond 2

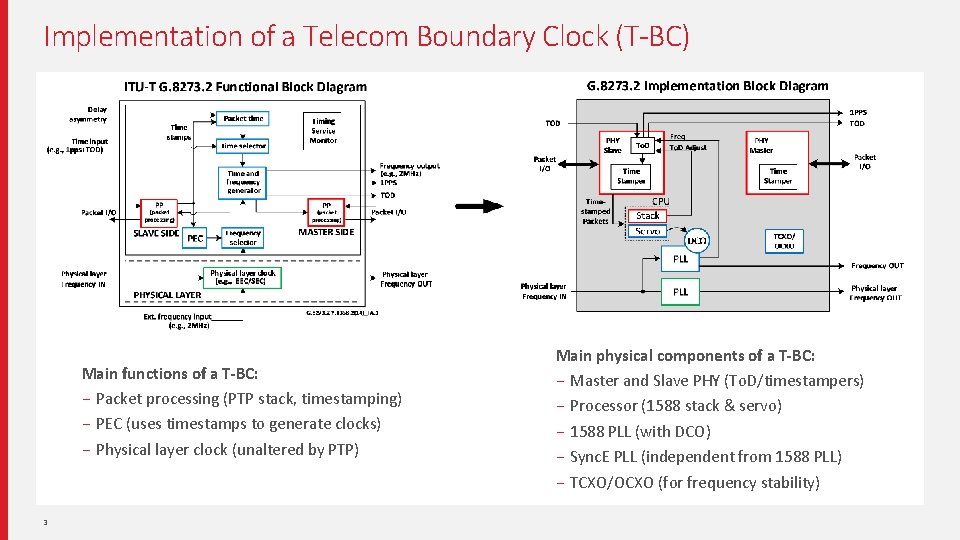

Implementation of a Telecom Boundary Clock (T-BC) Main functions of a T-BC: − Packet processing (PTP stack, timestamping) − PEC (uses timestamps to generate clocks) − Physical layer clock (unaltered by PTP) 3 Main physical components of a T-BC: − Master and Slave PHY (To. D/timestampers) − Processor (1588 stack & servo) − 1588 PLL (with DCO) − Sync. E PLL (independent from 1588 PLL) − TCXO/OCXO (for frequency stability)

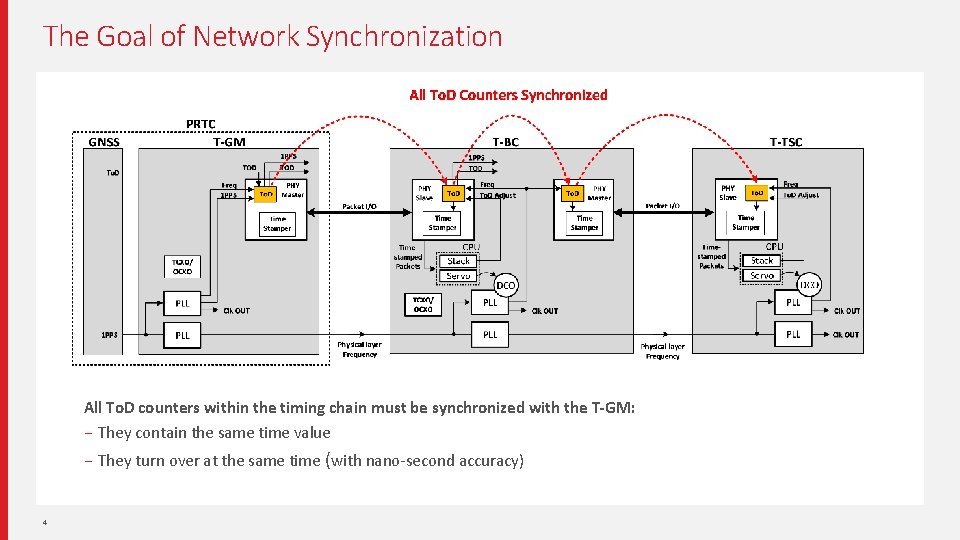

The Goal of Network Synchronization All To. D counters within the timing chain must be synchronized with the T-GM: − They contain the same time value − They turn over at the same time (with nano-second accuracy) 4

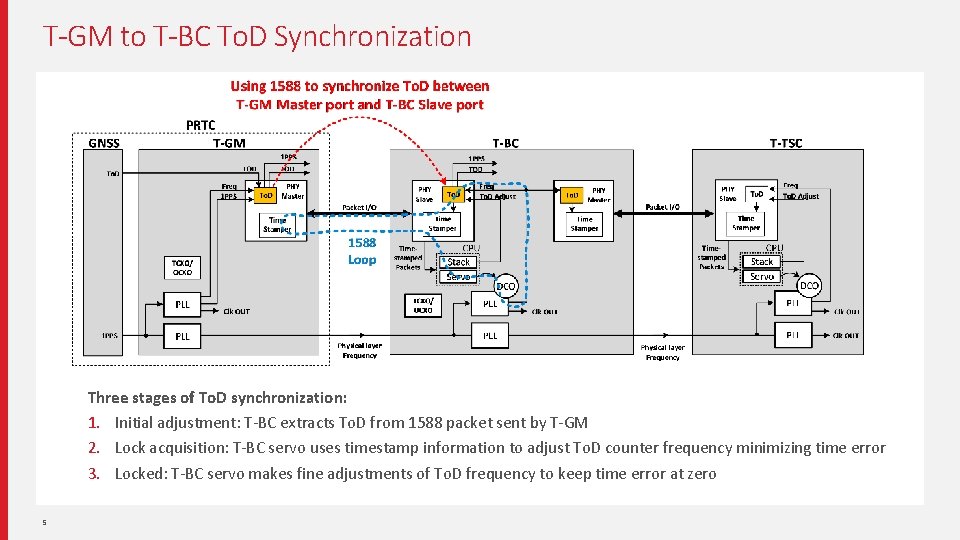

T-GM to T-BC To. D Synchronization Three stages of To. D synchronization: 1. Initial adjustment: T-BC extracts To. D from 1588 packet sent by T-GM 2. Lock acquisition: T-BC servo uses timestamp information to adjust To. D counter frequency minimizing time error 3. Locked: T-BC servo makes fine adjustments of To. D frequency to keep time error at zero 5

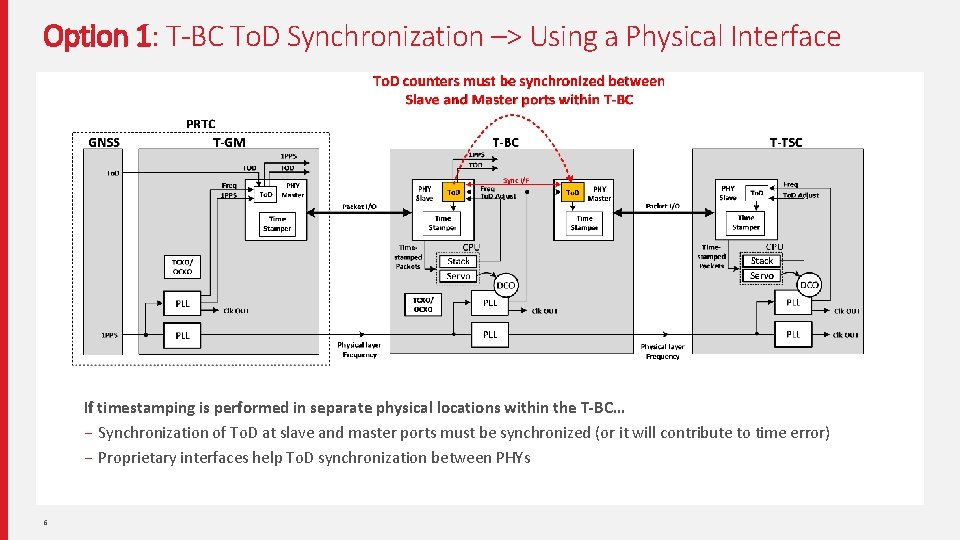

Option 1: T-BC To. D Synchronization –> Using a Physical Interface If timestamping is performed in separate physical locations within the T-BC… − Synchronization of To. D at slave and master ports must be synchronized (or it will contribute to time error) − Proprietary interfaces help To. D synchronization between PHYs 6

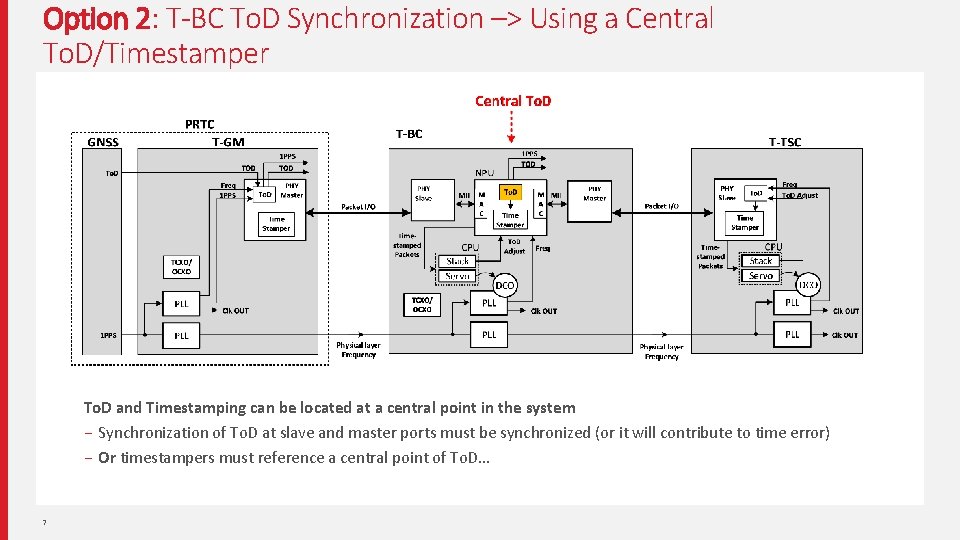

Option 2: T-BC To. D Synchronization –> Using a Central To. D/Timestamper To. D and Timestamping can be located at a central point in the system − Synchronization of To. D at slave and master ports must be synchronized (or it will contribute to time error) − Or timestampers must reference a central point of To. D… 7

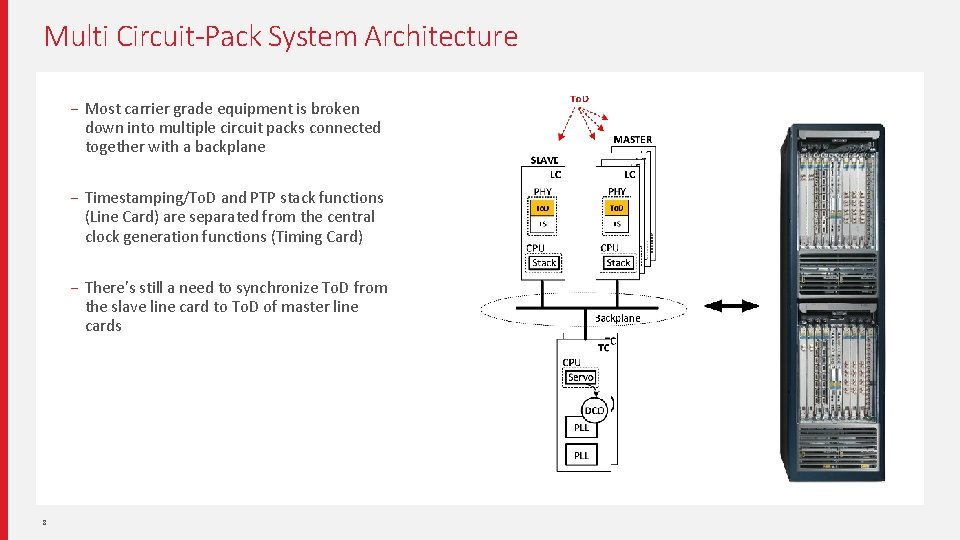

Multi Circuit-Pack System Architecture − Most carrier grade equipment is broken down into multiple circuit packs connected together with a backplane − Timestamping/To. D and PTP stack functions (Line Card) are separated from the central clock generation functions (Timing Card) − There’s still a need to synchronize To. D from the slave line card to To. D of master line cards 8

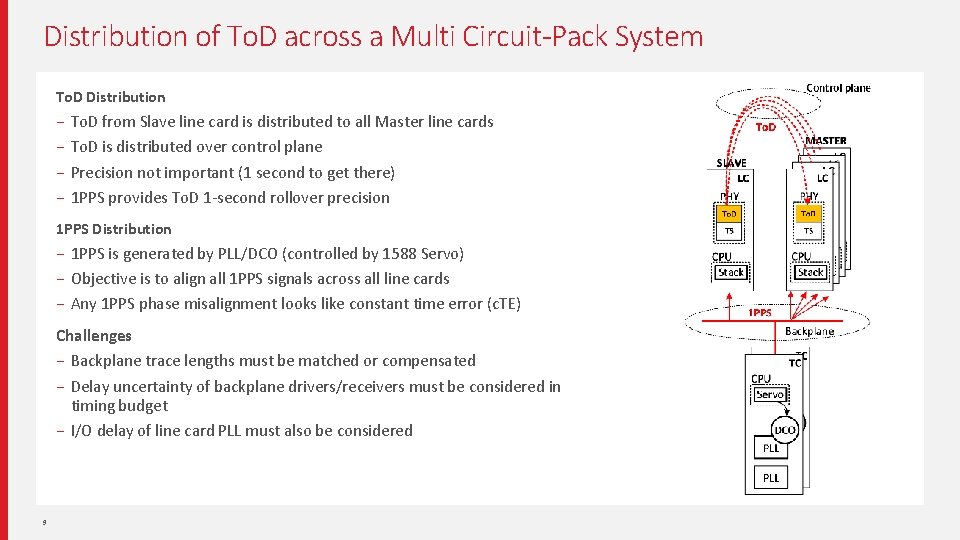

Distribution of To. D across a Multi Circuit-Pack System To. D Distribution − − To. D from Slave line card is distributed to all Master line cards To. D is distributed over control plane Precision not important (1 second to get there) 1 PPS provides To. D 1 -second rollover precision 1 PPS Distribution − 1 PPS is generated by PLL/DCO (controlled by 1588 Servo) − Objective is to align all 1 PPS signals across all line cards − Any 1 PPS phase misalignment looks like constant time error (c. TE) Challenges − Backplane trace lengths must be matched or compensated − Delay uncertainty of backplane drivers/receivers must be considered in timing budget − I/O delay of line card PLL must also be considered 9

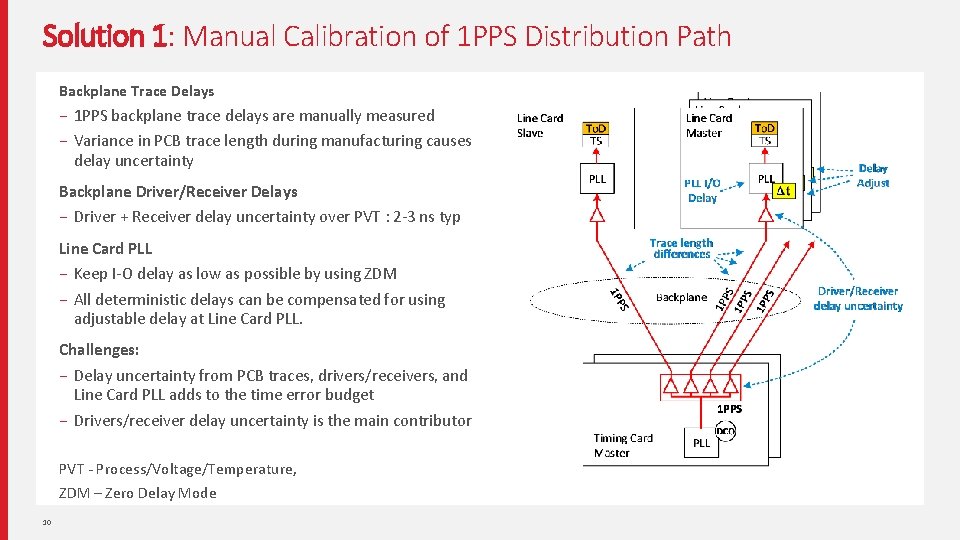

Solution 1: Manual Calibration of 1 PPS Distribution Path Backplane Trace Delays − 1 PPS backplane trace delays are manually measured − Variance in PCB trace length during manufacturing causes delay uncertainty Backplane Driver/Receiver Delays − Driver + Receiver delay uncertainty over PVT : 2 -3 ns typ Line Card PLL − Keep I-O delay as low as possible by using ZDM − All deterministic delays can be compensated for using adjustable delay at Line Card PLL. Challenges: − Delay uncertainty from PCB traces, drivers/receivers, and Line Card PLL adds to the time error budget − Drivers/receiver delay uncertainty is the main contributor PVT - Process/Voltage/Temperature, ZDM – Zero Delay Mode 10

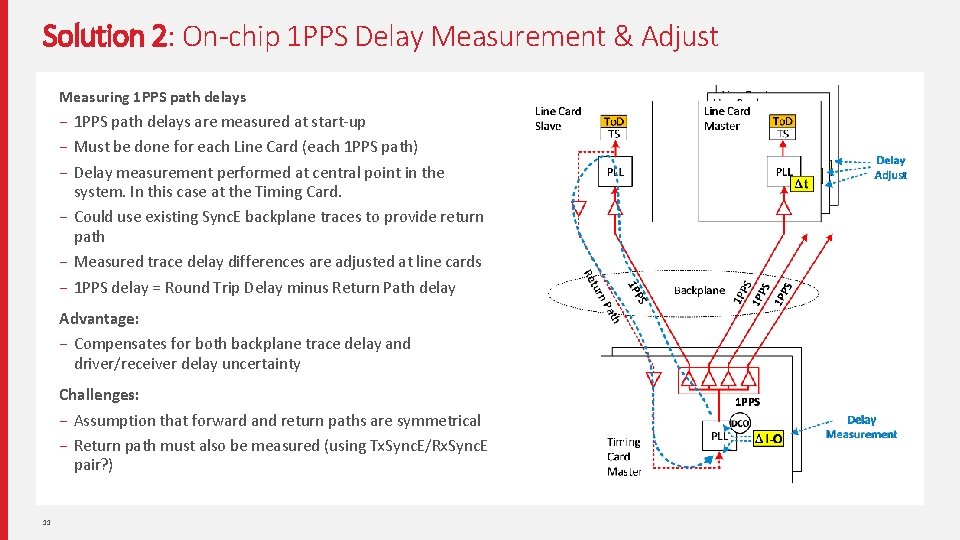

Solution 2: On-chip 1 PPS Delay Measurement & Adjust Measuring 1 PPS path delays − 1 PPS path delays are measured at start-up − Must be done for each Line Card (each 1 PPS path) − Delay measurement performed at central point in the system. In this case at the Timing Card. − Could use existing Sync. E backplane traces to provide return path − Measured trace delay differences are adjusted at line cards − 1 PPS delay = Round Trip Delay minus Return Path delay Advantage: − Compensates for both backplane trace delay and driver/receiver delay uncertainty Challenges: − Assumption that forward and return paths are symmetrical − Return path must also be measured (using Tx. Sync. E/Rx. Sync. E pair? ) 11

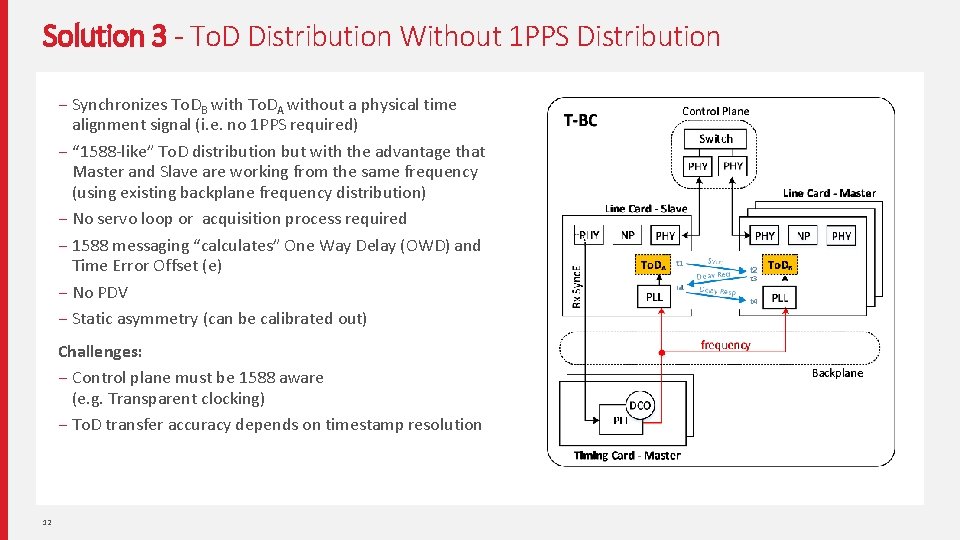

Solution 3 - To. D Distribution Without 1 PPS Distribution − Synchronizes To. DB with To. DA without a physical time alignment signal (i. e. no 1 PPS required) − “ 1588 -like” To. D distribution but with the advantage that Master and Slave are working from the same frequency (using existing backplane frequency distribution) − No servo loop or acquisition process required − 1588 messaging “calculates” One Way Delay (OWD) and Time Error Offset (e) − No PDV − Static asymmetry (can be calibrated out) Challenges: − Control plane must be 1588 aware (e. g. Transparent clocking) − To. D transfer accuracy depends on timestamp resolution 12

Conclusions − Time error of a T-BC consist of PTP servo error + misalignment of To. D − Distribution of To. D in a multi circuit-pack system takes careful design − Meeting 5 ns time error is a difficult challenge. − New design practices and synchronization distribution architectures will be needed 13

Thank You

- Slides: 14