Poznte Xilinx Robotick przdniny 6 0 Bratislava 7

Poznáte Xilinx ? Robotické prázdniny 6. 0 Bratislava 7. 9. 2006

Díky programovatelným polím si každý může vyrobit vlastní zákaznický integrovaný obvod šitý přesně na míru dané aplikaci s minimálními náklady. Základní pojmy Všechny programovatelné součástky se souhrnně označují PLD, což znamená Programmable Logic Device. Číslicové programovatelné součástky je možné podle vnitřní struktury rozdělit do tří skupin. První skupinu budu označovat klasické PLD, druhou komplexní PLD a do třetí skupiny patří obvody typu FPGA.

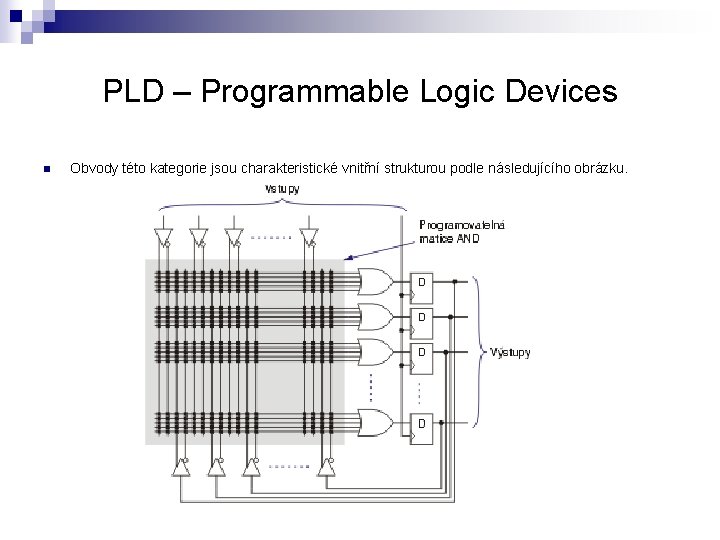

PLD – Programmable Logic Devices n Obvody této kategorie jsou charakteristické vnitřní strukturou podle následujícího obrázku.

Obvody typu PAL (Programmable Array Logic) mají strukturu podle výše uvedených obrázků. Některé starší typy neměly například výstupní registry, takže byly vhodné spíše pro kombinační logiku. Zástupci této kategorie jsou obvody PAL, GAL a PALCE. Obvody typu PLA (Programmable Logic Array) mají obecnější strukturu než PAL na horním obrázku. Mají totiž programovatelnou nejenom matici logických součinů, ale i následující matici logických součtů.

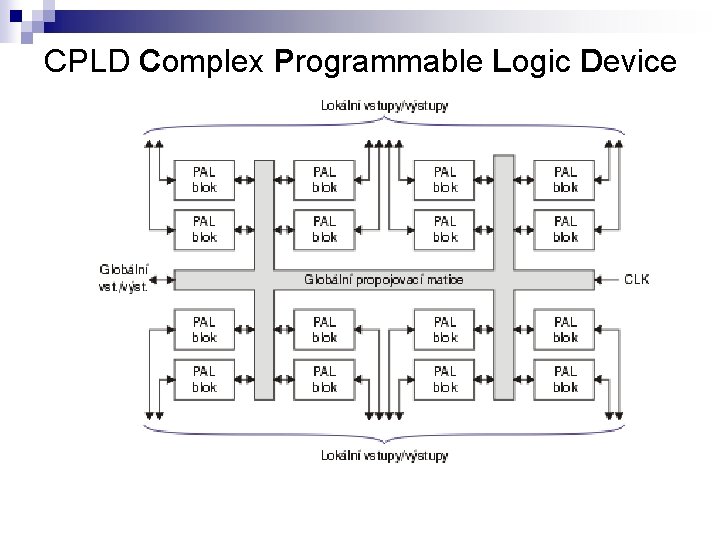

CPLD Complex Programmable Logic Device

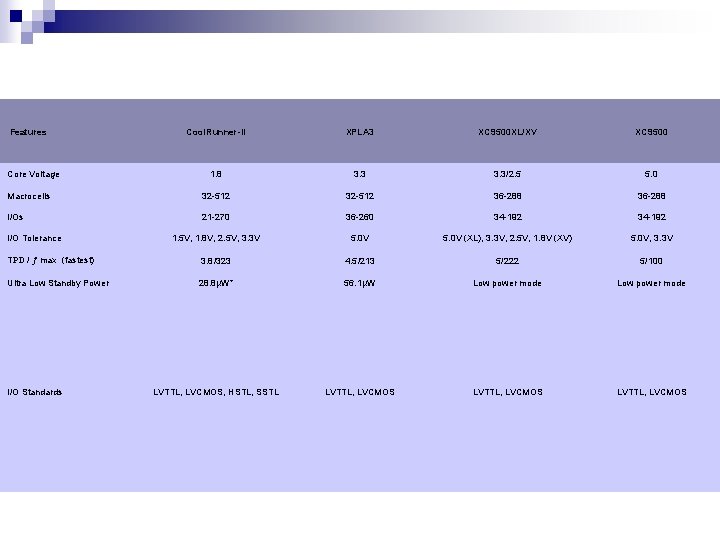

Features Cool. Runner-II XPLA 3 XC 9500 XL/XV XC 9500 1. 8 3. 3/2. 5 5. 0 Macrocells 32 -512 36 -288 I/Os 21 -270 36 -260 34 -192 1. 5 V, 1. 8 V, 2. 5 V, 3. 3 V 5. 0 V (XL), 3. 3 V, 2. 5 V, 1. 8 V (XV) 5. 0 V, 3. 3 V TPD / ƒ max (fastest) 3. 8/323 4. 5/213 5/222 5/100 Ultra Low Standby Power 28. 8µW* 56. 1µW Low power mode LVTTL, LVCMOS, HSTL, SSTL LVTTL, LVCMOS Core Voltage I/O Tolerance I/O Standards

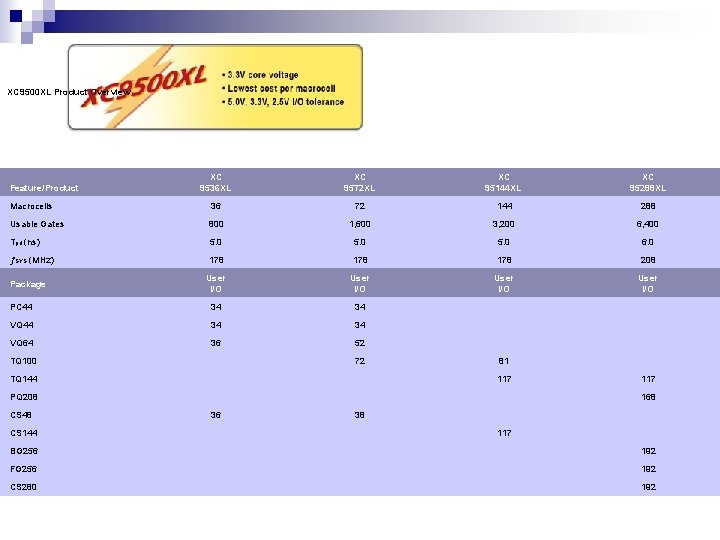

XC 9500 XL Product Overview XC 9536 XL XC 9572 XL XC 95144 XL XC 95288 XL Macrocells 36 72 144 288 Usable Gates 800 1, 600 3, 200 6, 400 Tpd (ns) 5. 0 6. 0 ƒSYS (MHz) 178 178 208 Package User I/O PC 44 34 VQ 44 34 VQ 64 36 52 Feature/Product TQ 100 72 81 TQ 144 117 PQ 208 168 CS 48 36 38 CS 144 117 BG 256 192 FG 256 192 CS 280 192

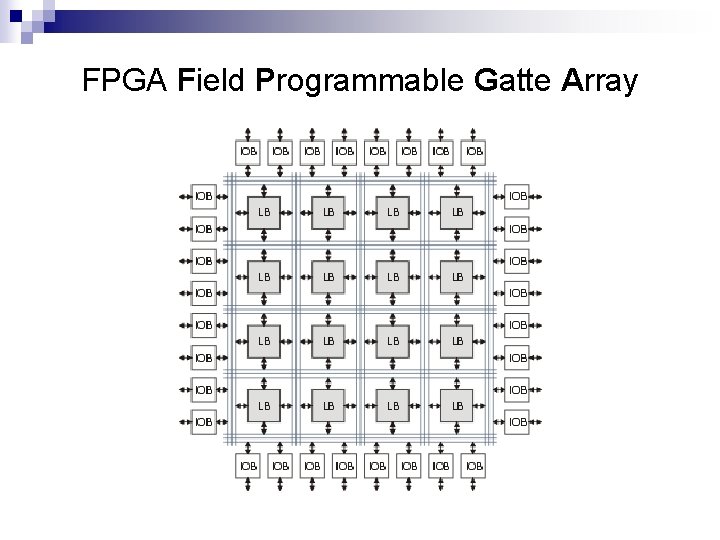

FPGA Field Programmable Gatte Array

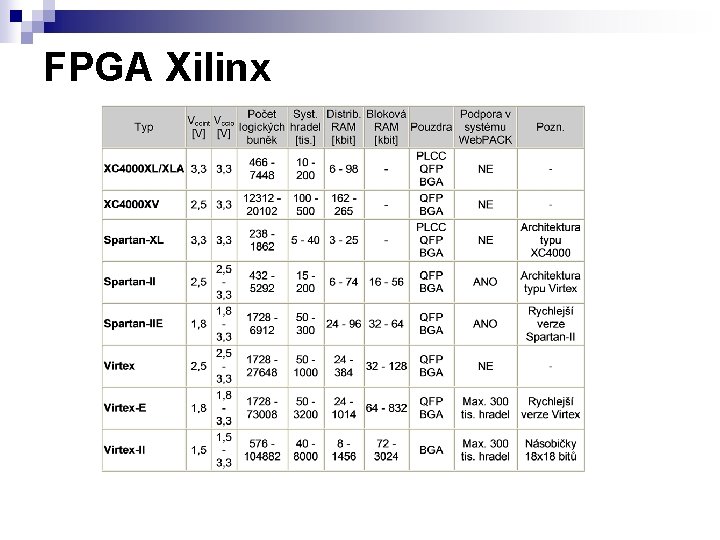

FPGA Xilinx

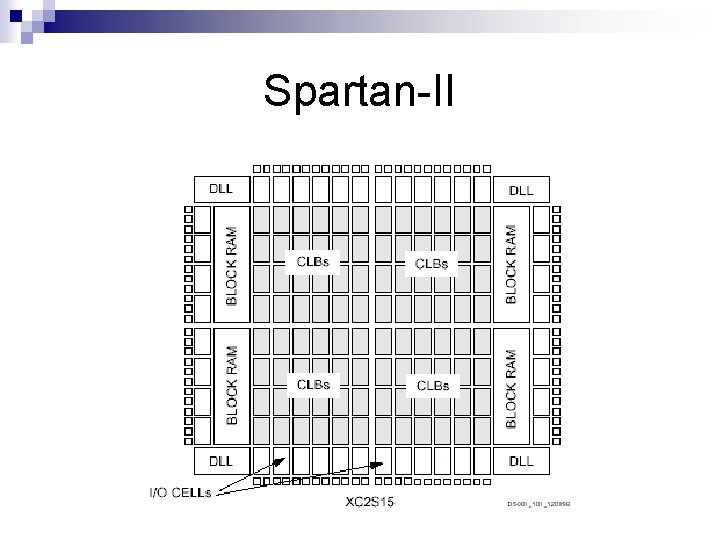

Spartan-II

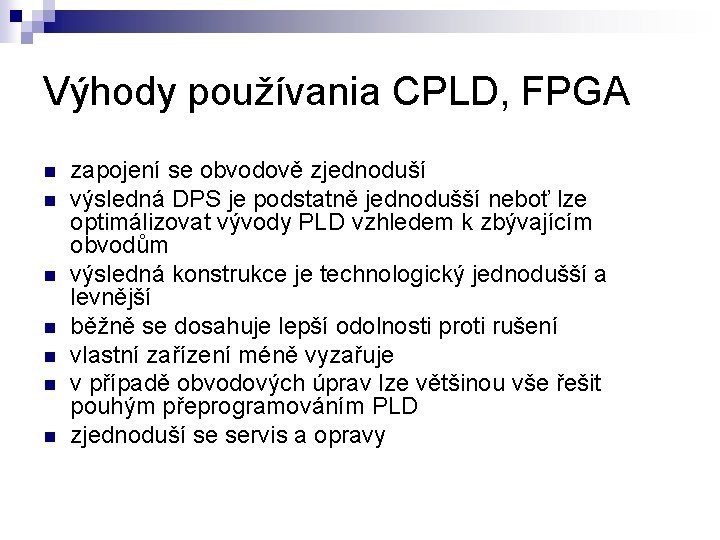

Výhody používania CPLD, FPGA n n n n zapojení se obvodově zjednoduší výsledná DPS je podstatně jednodušší neboť lze optimálizovat vývody PLD vzhledem k zbývajícím obvodům výsledná konstrukce je technologický jednodušší a levnější běžně se dosahuje lepší odolnosti proti rušení vlastní zařízení méně vyzařuje v případě obvodových úprav lze většinou vše řešit pouhým přeprogramováním PLD zjednoduší se servis a opravy

Využitie CPLD, FPGA n DSP, software-defined radio, aerospace and defense systems, ASIC prototyping, medical imaging, computer vision, speech recognition, cryptography, bioinformatics, computer hardware emulation

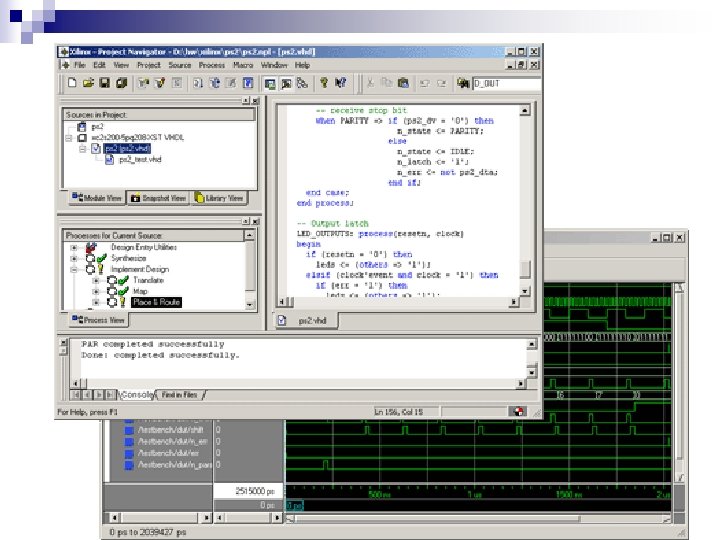

Vývojové prostředky Pokud chce člověk začít pracovat s obvody FPGA musí si tedy obstarat základní programové vybavení od výrobce obvodů a případně další software od třetí strany. Kromě nástrojů pro syntézu je velmi výhodné používat ještě simulátor, čímž se může předejít chybám již v průběhu návrhu. Ceny vývojových prostředků jsou však velmi vysoké (ceny licencí na jeden rok se obvykle pohybují od 1000 do 2000 USD). Firma Xilinx nabízí pro FPGA s menší hustotou logiky mnohem levnější alternativu. Vývojový systém ISE Web. PACK je totiž zadarmo. Tento vývojový systém pro FPGA firmy Xilinx je omezenou verzí jejich kompletního systému. Omezení se však týká pouze velikosti hradlových polí pro které je možno prostředí použít. Navíc neobsahuje některé rozšířené součásti jako například plnohodnotný editor výsledného propojení. Web. PACK je i přesto plně funkční a plnohodnotný návrhový systém. Kromě vlastního prostředí Web. PACK je možné zdarma získat i omezenou verzi HDL simulátoru Model. Sim XE, což je verze s předkompilovanými knihovnami primitiv pro FPGA Xilinx. Omezení simulátoru spočívá ve zpomalení jeho funkce pro velké návrhy. Simulátor je tedy opět plně funkční, pouze doba simulace složitého návrhu je několikanásobná oproti plné verzi.

- Slides: 15