Power supply per Fisica delle Alte Energie problematiche

Power supply per Fisica delle Alte Energie: problematiche e soluzioni innovative B. Allongue 1, G. Blanchot 1, S. Buso 2, F. Faccio 1, C. Fuentes 1, 3, P. Mattavelli 2, S. Michelis 1, 4, S. Orlandi 1, G. Spiazzi 2 1 CERN – PH-ESE 2 Dept. Information Engineering, Padova University, Italy 3 UTFSM, Valparaiso, Chile 4 EPFL, Lausanne 1

Outline • Present power distribution architectures at LHC experiments • Expected power supply requirements for the future LHC upgrade • Serial powering • Parallel powering: DC-DC converters based solution – DC-DC converter topologies for Point of Load (POL) converters • Conclusions 2

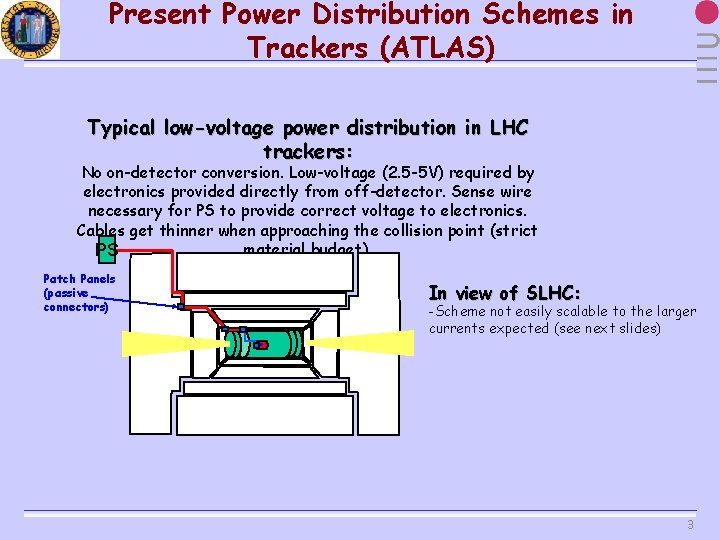

Present Power Distribution Schemes in Trackers (ATLAS) Typical low-voltage power distribution in LHC trackers: No on-detector conversion. Low-voltage (2. 5 -5 V) required by electronics provided directly from off-detector. Sense wire necessary for PS to provide correct voltage to electronics. Cables get thinner when approaching the collision point (strict material budget). PS Patch Panels (passive connectors) In view of SLHC: -Scheme not easily scalable to the larger currents expected (see next slides) 3

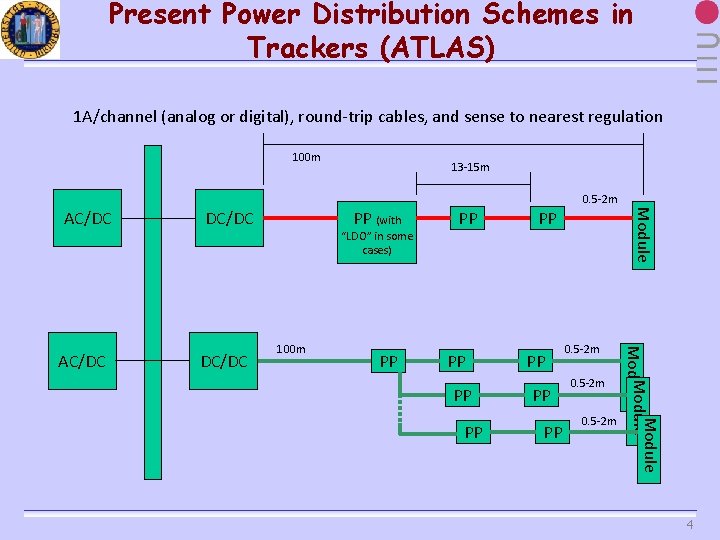

Present Power Distribution Schemes in Trackers (ATLAS) 1 A/channel (analog or digital), round-trip cables, and sense to nearest regulation 100 m 13 -15 m AC/DC DC/DC “LDO” in some cases) 100 m PP PP PP 0. 5 -2 m Module AC/DC PP (with DC/DC Module 0. 5 -2 m 4

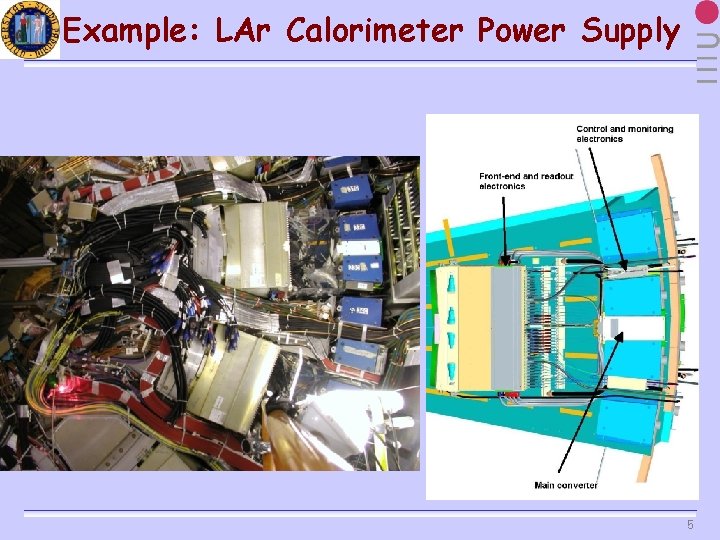

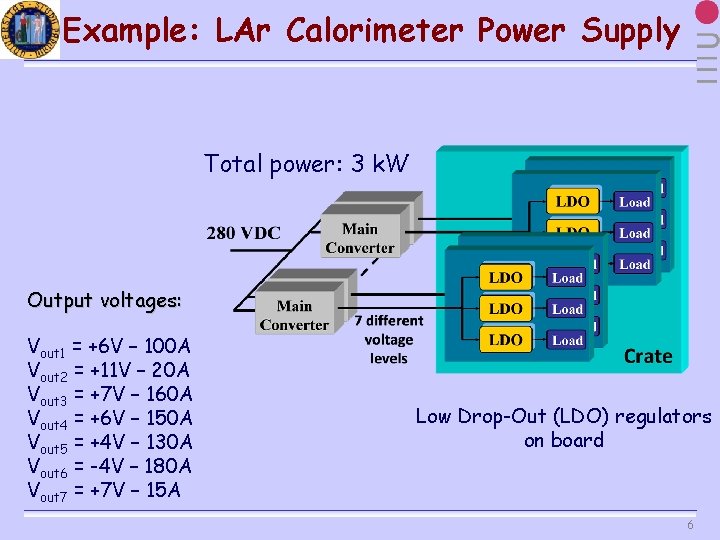

Example: LAr Calorimeter Power Supply 5

Example: LAr Calorimeter Power Supply Total power: 3 k. W Output voltages: Vout 1 = +6 V – 100 A Vout 2 = +11 V – 20 A Vout 3 = +7 V – 160 A Vout 4 = +6 V – 150 A Vout 5 = +4 V – 130 A Vout 6 = -4 V – 180 A Vout 7 = +7 V – 15 A Low Drop-Out (LDO) regulators on board 6

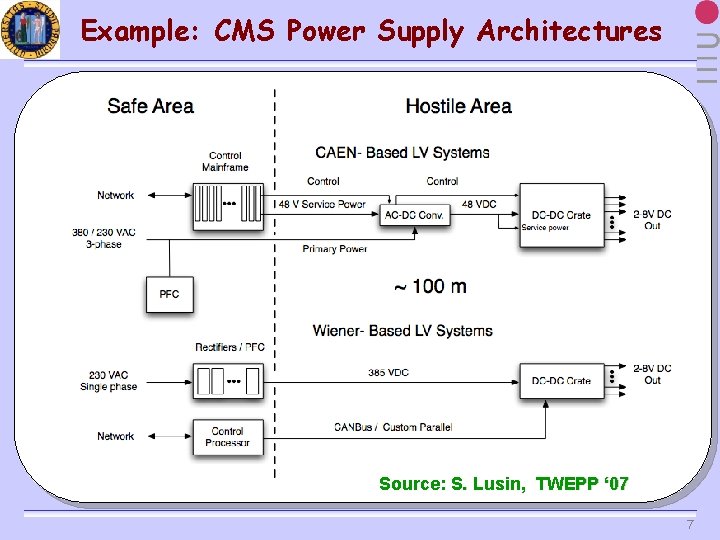

Example: CMS Power Supply Architectures Source: S. Lusin, TWEPP ‘ 07 7

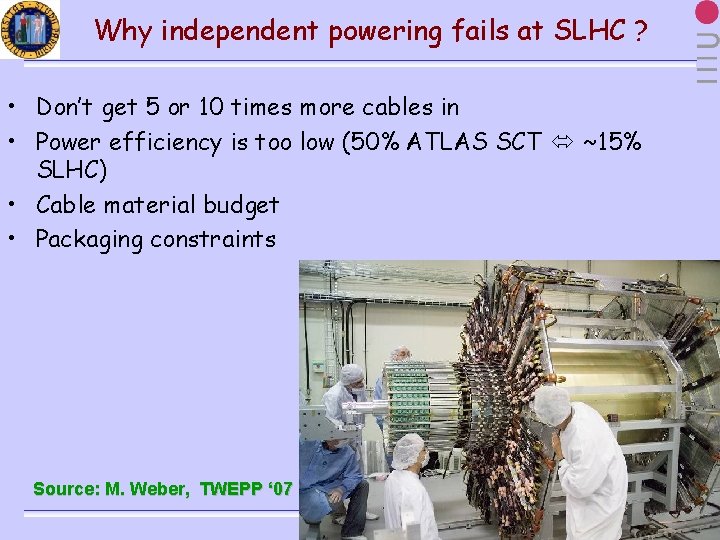

Why independent powering fails at SLHC ? • Don’t get 5 or 10 times more cables in • Power efficiency is too low (50% ATLAS SCT ~15% SLHC) • Cable material budget • Packaging constraints Source: M. Weber, TWEPP ‘ 07 8

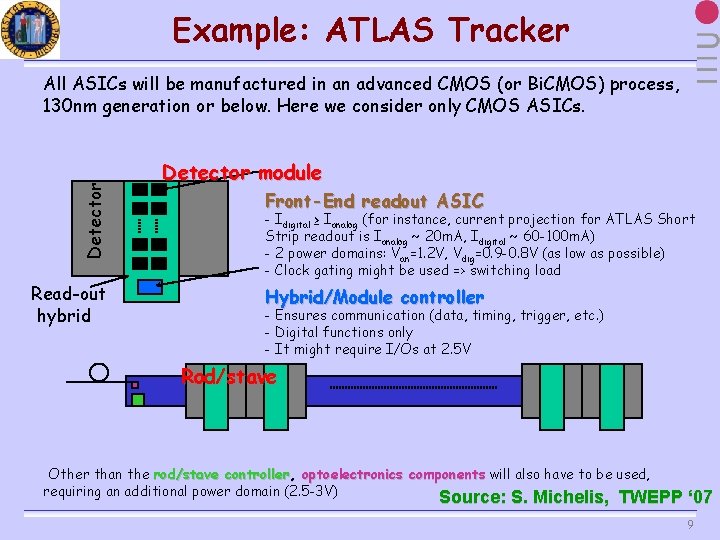

Example: ATLAS Tracker Detector All ASICs will be manufactured in an advanced CMOS (or Bi. CMOS) process, 130 nm generation or below. Here we consider only CMOS ASICs. Read-out hybrid Detector module Front-End readout ASIC - Idigital ≥ Ianalog (for instance, current projection for ATLAS Short Strip readout is Ianalog ~ 20 m. A, Idigital ~ 60 -100 m. A) - 2 power domains: Van=1. 2 V, Vdig=0. 9 -0. 8 V (as low as possible) - Clock gating might be used => switching load Hybrid/Module controller - Ensures communication (data, timing, trigger, etc. ) - Digital functions only - It might require I/Os at 2. 5 V Rod/stave Other than the rod/stave controller, optoelectronics components will also have to be used, requiring an additional power domain (2. 5 -3 V) Source: S. Michelis, TWEPP ‘ 07 9

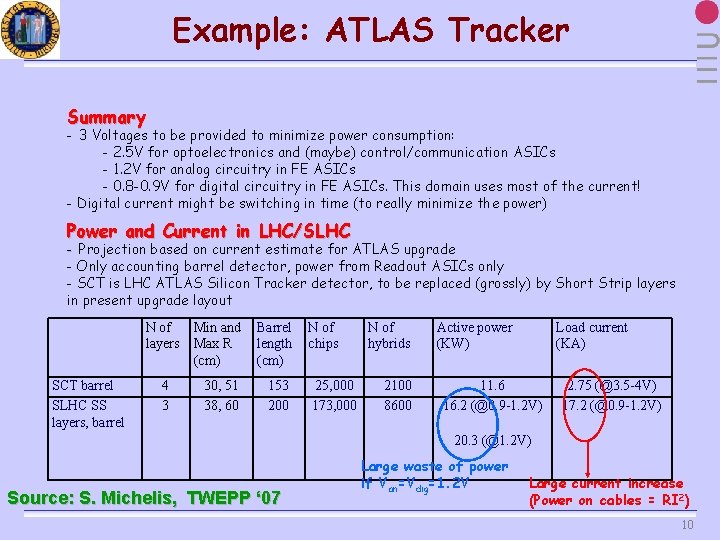

Example: ATLAS Tracker Summary - 3 Voltages to be provided to minimize power consumption: - 2. 5 V for optoelectronics and (maybe) control/communication ASICs - 1. 2 V for analog circuitry in FE ASICs - 0. 8 -0. 9 V for digital circuitry in FE ASICs. This domain uses most of the current! - Digital current might be switching in time (to really minimize the power) Power and Current in LHC/SLHC - Projection based on current estimate for ATLAS upgrade - Only accounting barrel detector, power from Readout ASICs only - SCT is LHC ATLAS Silicon Tracker detector, to be replaced (grossly) by Short Strip layers in present upgrade layout N of layers SCT barrel SLHC SS layers, barrel 4 3 Min and Barrel N of Max R length chips (cm) 30, 51 38, 60 153 200 25, 000 173, 000 N of hybrids 2100 8600 Active power (KW) Load current (KA) 11. 6 16. 2 (@0. 9 -1. 2 V) 2. 75 (@3. 5 -4 V) 17. 2 (@0. 9 -1. 2 V) 20. 3 (@1. 2 V) Source: S. Michelis, TWEPP ‘ 07 Large waste of power if Van=Vdig=1. 2 V Large current increase (Power on cables = RI 2) 10

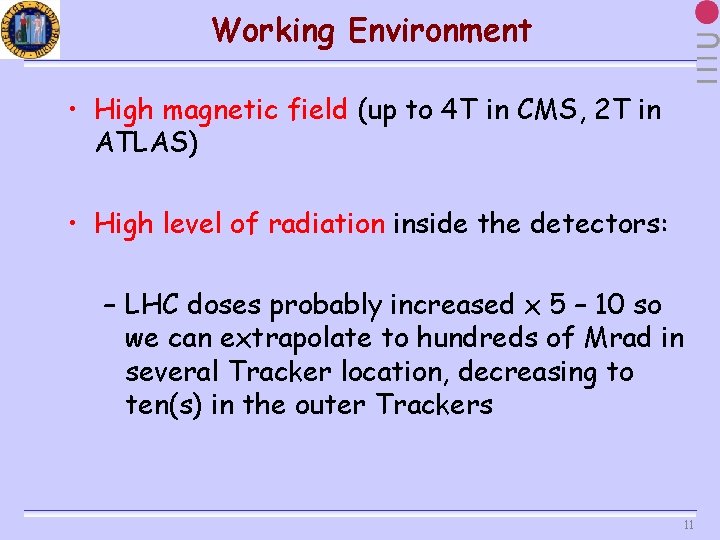

Working Environment • High magnetic field (up to 4 T in CMS, 2 T in ATLAS) • High level of radiation inside the detectors: – LHC doses probably increased x 5 – 10 so we can extrapolate to hundreds of Mrad in several Tracker location, decreasing to ten(s) in the outer Trackers 11

Power Distribution Schemes • Serial Powering (SP) – Shunt regulators • Parallel Powering (PP) – Inductor-based switching converters – Switched capacitor converters 12

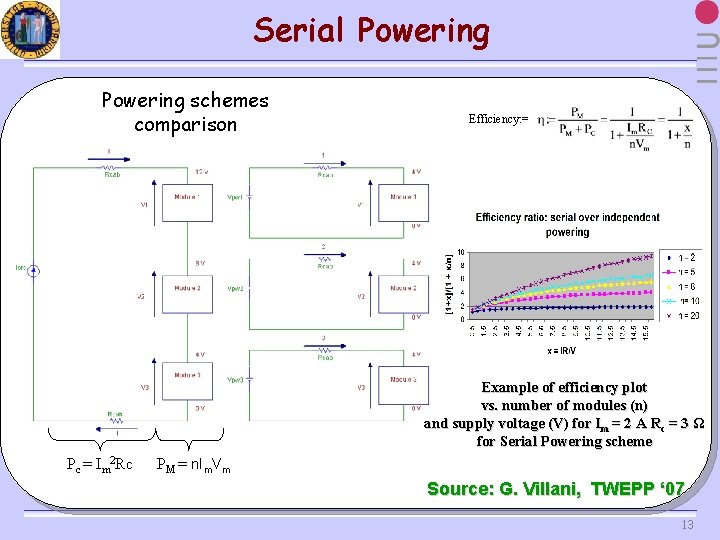

Serial Powering schemes comparison Efficiency: = Example of efficiency plot vs. number of modules (n) and supply voltage (V) for Im = 2 A Rc = 3 Ω for Serial Powering scheme Pc = Im 2 Rc PM = n. Im. Vm Source: G. Villani, TWEPP ‘ 07 13

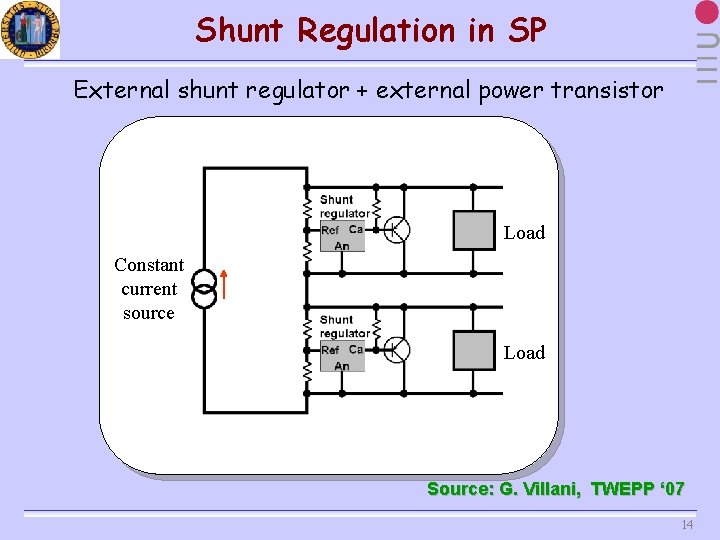

Shunt Regulation in SP External shunt regulator + external power transistor Load Constant current source Load Source: G. Villani, TWEPP ‘ 07 14

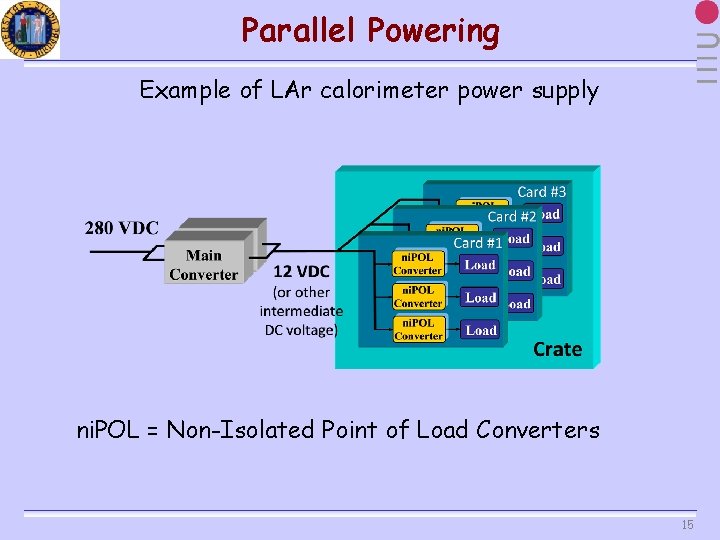

Parallel Powering Example of LAr calorimeter power supply ni. POL = Non-Isolated Point of Load Converters 15

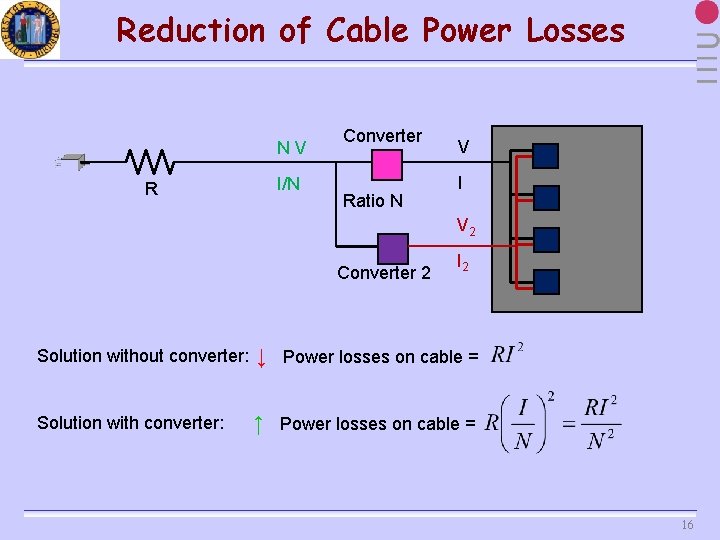

Reduction of Cable Power Losses N V R I/N Converter Ratio N V I V 2 Converter 2 I 2 Solution without converter: ↓ Power losses on cable = Solution with converter: ↑ Power losses on cable = 16

Power supply for ATLAS Trackers • The high magnetic field calls for coreless conversion stages • Low-value air core inductors can be used with switching frequencies in the megahertz region • Inductor-less conversion stages can also be used (switched capacitor converters) • Switching noise is a big concern Soft-switching is a must! 19

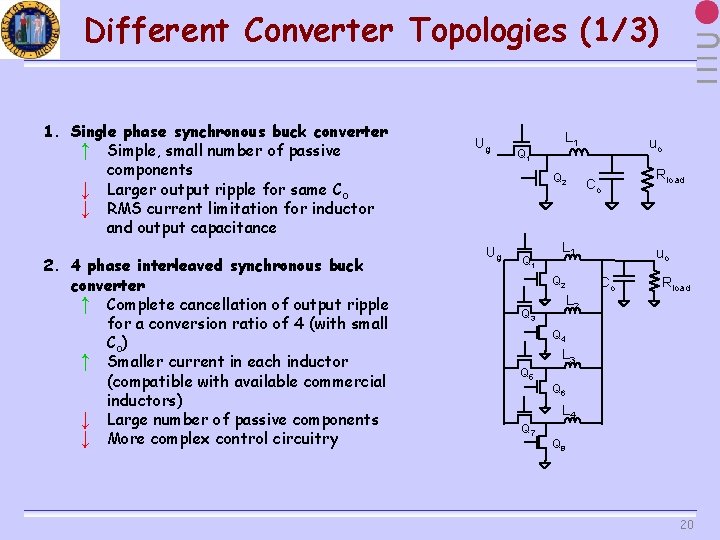

Different Converter Topologies (1/3) 1. Single phase synchronous buck converter ↑ Simple, small number of passive components ↓ Larger output ripple for same Co ↓ RMS current limitation for inductor and output capacitance 2. 4 phase interleaved synchronous buck converter ↑ Complete cancellation of output ripple for a conversion ratio of 4 (with small Co) ↑ Smaller current in each inductor (compatible with available commercial inductors) ↓ Large number of passive components ↓ More complex control circuitry Ug Q 1 L 1 Q 2 Ug Q 1 uo Co L 1 Q 2 L 2 Q 3 Rload uo Co Rload Q 4 L 3 Q 5 Q 6 L 4 Q 7 Q 8 20

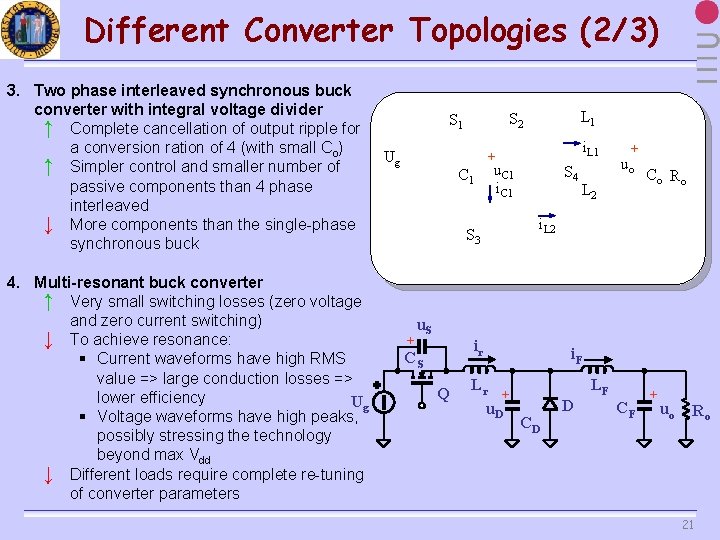

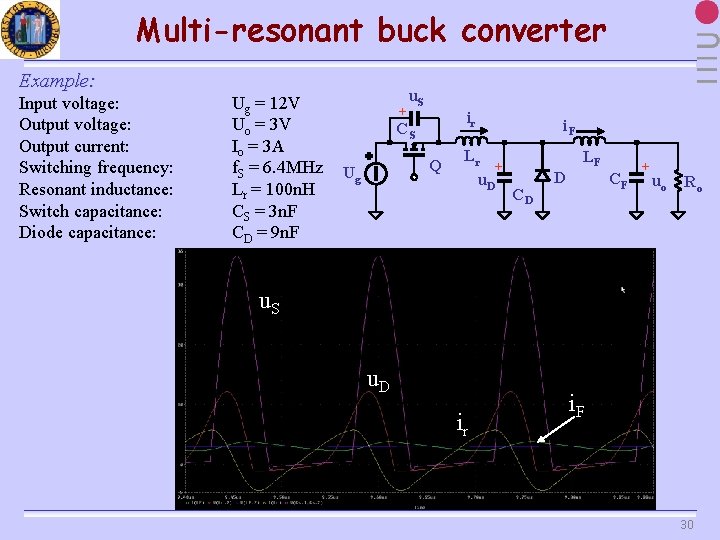

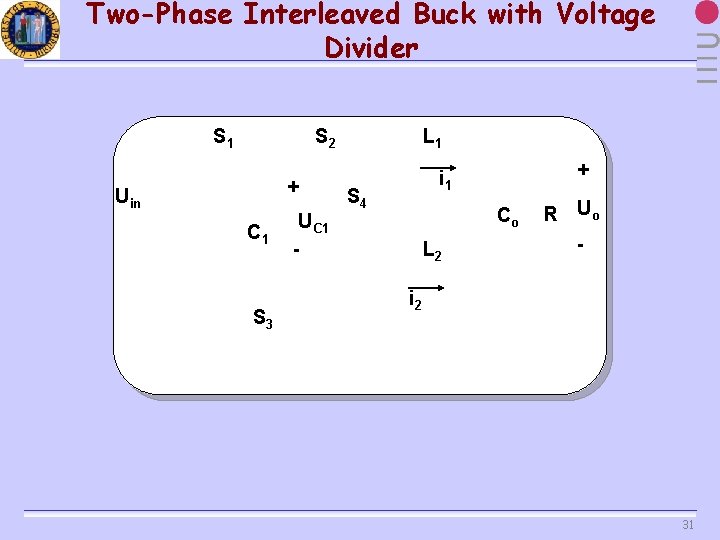

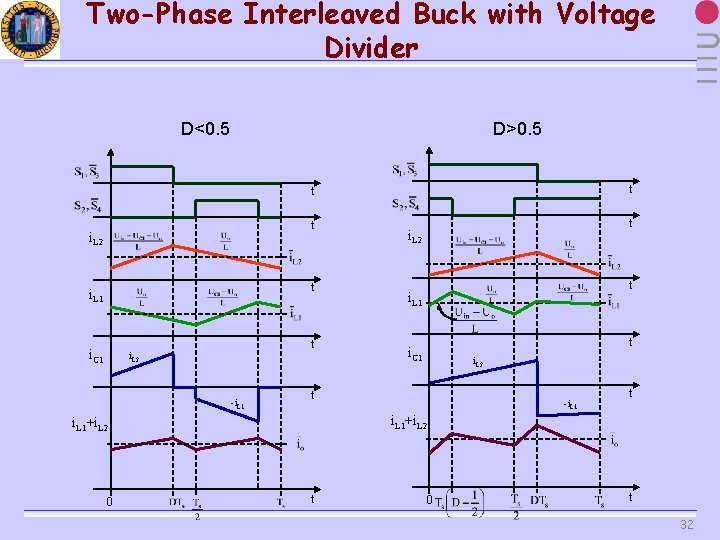

Different Converter Topologies (2/3) 3. Two phase interleaved synchronous buck converter with integral voltage divider ↑ Complete cancellation of output ripple for a conversion ration of 4 (with small Co) ↑ Simpler control and smaller number of passive components than 4 phase interleaved ↓ More components than the single-phase synchronous buck 4. Multi-resonant buck converter ↑ Very small switching losses (zero voltage and zero current switching) ↓ To achieve resonance: § Current waveforms have high RMS value => large conduction losses => lower efficiency Ug § Voltage waveforms have high peaks, possibly stressing the technology beyond max Vdd ↓ Different loads require complete re-tuning of converter parameters Ug C 1 + CS i. L 1 + u. C 1 i. C 1 S 3 u. S L 1 S 2 S 1 S 4 Lr + u. D uo L 2 Co Ro i. L 2 ir Q + i. F CD D LF CF + uo Ro 21

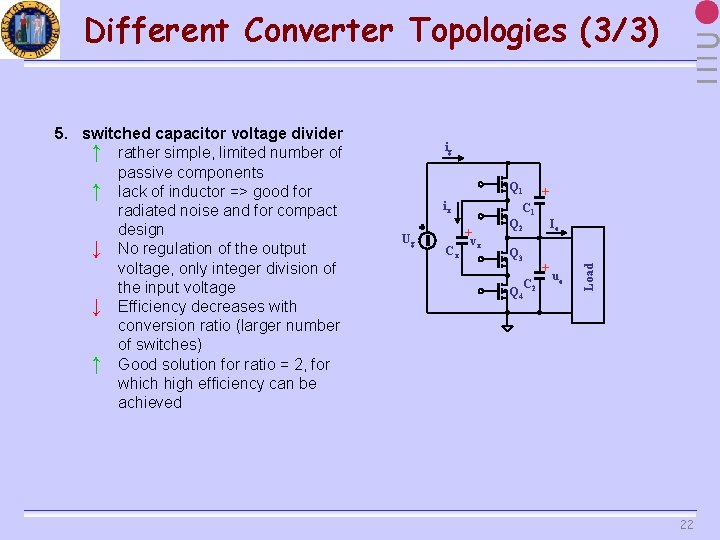

Different Converter Topologies (3/3) ig Q 1 ix Ug Cx + vx + C 1 Q 2 Q 3 C 2 Q 4 Io + uo Load 5. switched capacitor voltage divider ↑ rather simple, limited number of passive components ↑ lack of inductor => good for radiated noise and for compact design ↓ No regulation of the output voltage, only integer division of the input voltage ↓ Efficiency decreases with conversion ratio (larger number of switches) ↑ Good solution for ratio = 2, for which high efficiency can be achieved 22

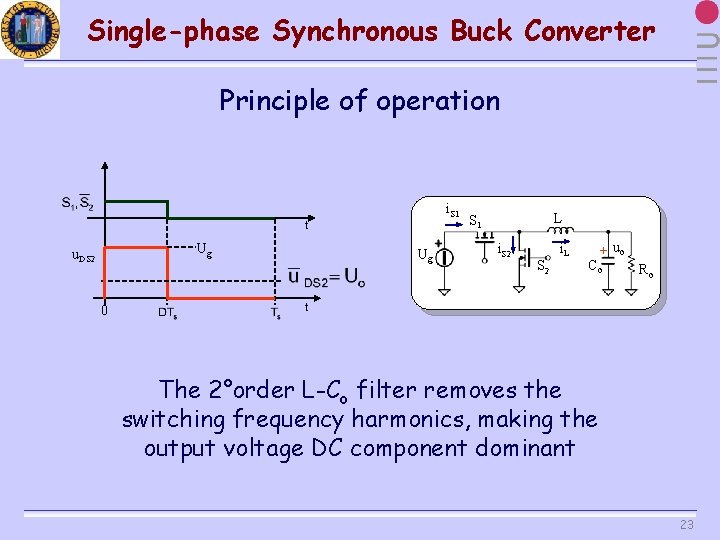

Single-phase Synchronous Buck Converter Principle of operation i. S 1 t Ug u. DS 2 0 Ug L S 1 i. S 2 i. L + uo Co Ro t The 2°order L-Co filter removes the switching frequency harmonics, making the output voltage DC component dominant 23

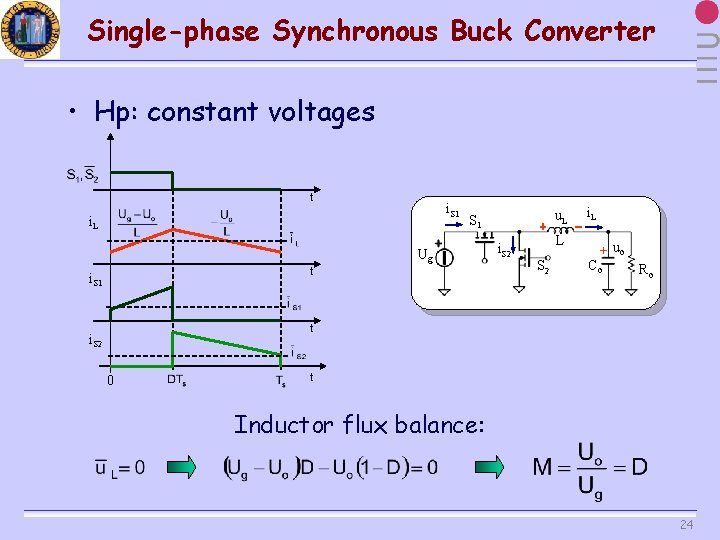

Single-phase Synchronous Buck Converter • Hp: constant voltages t i. S 1 i. L Ug t i. S 1 u. L S 1 i. S 2 L S 2 i. L + uo Co Ro t i. S 2 0 t Inductor flux balance: 24

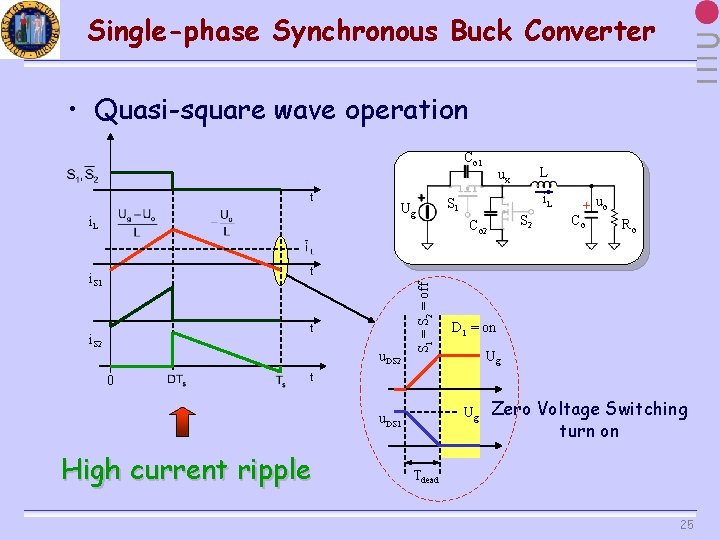

Single-phase Synchronous Buck Converter • Quasi-square wave operation Co 1 t i. L Ug L ux i. L S 1 S 2 Co 2 + uo Co Ro t i. S 2 u. DS 2 0 S 1 = S 2 = off t i. S 1 D 1 = on Ug t Ug u. DS 1 High current ripple Zero Voltage Switching turn on Tdead 25

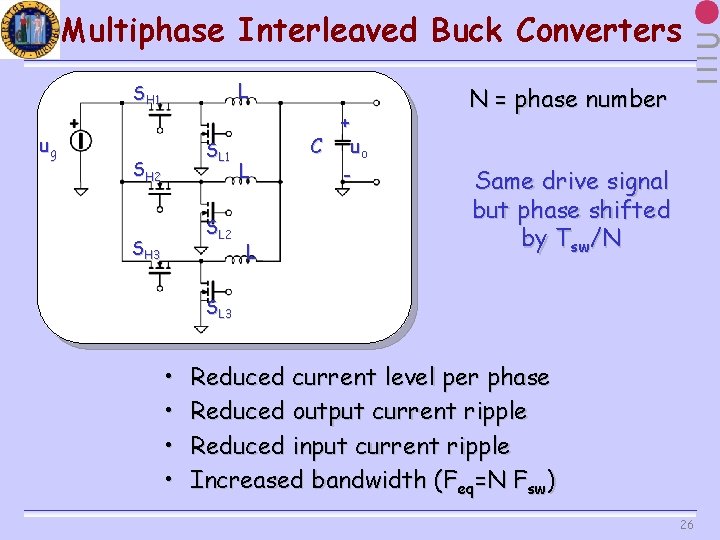

Multiphase Interleaved Buck Converters L SH 1 ug SL 1 SH 2 SL 2 SH 3 L L + C uo - N = phase number Same drive signal but phase shifted by Tsw/N SL 3 • • Reduced current level per phase Reduced output current ripple Reduced input current ripple Increased bandwidth (Feq=N Fsw) 26

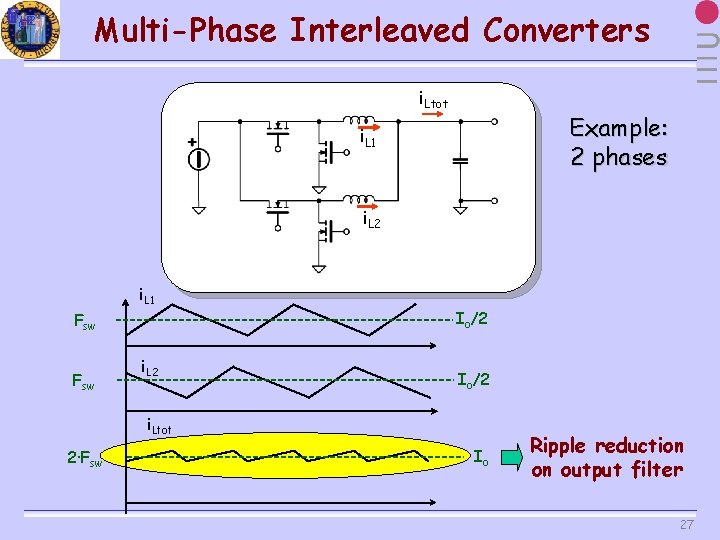

S L +- go. H 2 u C H 1 L 2 Multi-Phase Interleaved Converters i. Ltot Example: 2 phases i. L 1 i. L 2 i. L 1 Fsw i. L 2 Io/2 i. Ltot 2·Fsw Io Ripple reduction on output filter 27

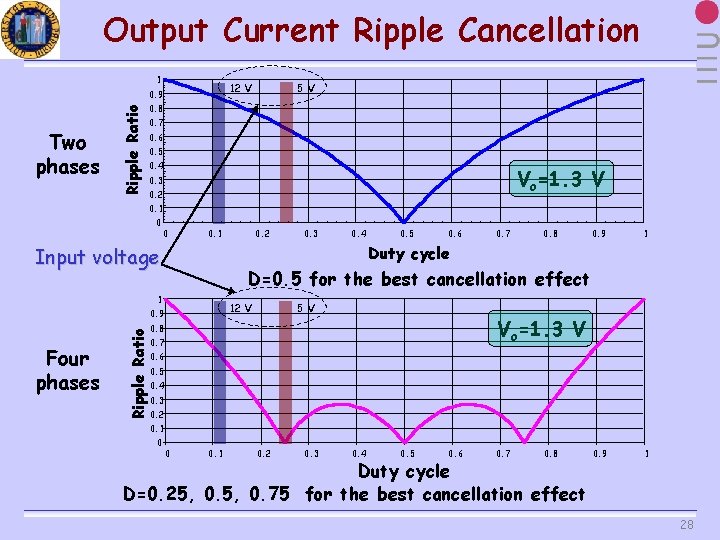

Output Current Ripple Cancellation 1 12 V Two phases Ripple Ratio 0. 9 5 V 0. 8 0. 7 0. 6 0. 5 0. 4 Vo=1. 3 V 0. 3 0. 2 0. 1 0 0 0. 1 0. 4 0. 5 0. 6 0. 7 0. 8 0. 9 1 D=0. 5 for the best cancellation effect 1 12 V 0. 9 Ripple Ratio 0. 3 Duty cycle Input voltage Four phases 0. 2 5 V Vo=1. 3 V 0. 8 0. 7 0. 6 0. 5 0. 4 0. 3 0. 2 0. 1 0 0 0. 1 0. 2 0. 3 0. 4 0. 5 0. 6 0. 7 0. 8 Duty cycle D=0. 25, 0. 75 for the best cancellation effect 28

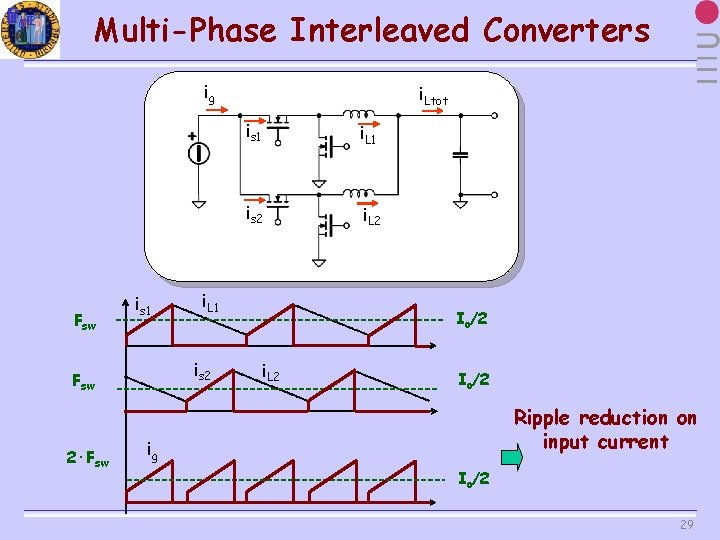

S L +- go. H 2 u C H 1 L 2 Multi-Phase Interleaved Converters ig Fsw is 1 2·Fsw is 1 i. L 1 is 2 Fsw i. Ltot Io/2 i. L 2 Io/2 Ripple reduction on input current ig Io/2 29

Multi-resonant buck converter Example: Input voltage: Output current: Switching frequency: Resonant inductance: Switch capacitance: Diode capacitance: Ug = 12 V Uo = 3 V Io = 3 A f. S = 6. 4 MHz Lr = 100 n. H CS = 3 n. F CD = 9 n. F u. S + CS ir Q Ug Lr + u. D i. F CD D LF CF + uo Ro u. S u. D ir i. F 30

Two-Phase Interleaved Buck with Voltage Divider S 1 S 2 + Uin C 1 S 3 UC 1 - L 1 + i 1 S 4 Co L 2 R Uo - i 2 31

Two-Phase Interleaved Buck with Voltage Divider D<0. 5 D>0. 5 t t t i. L 2 t i. L 1 i. C 1 t i. L 2 -i. L 1 t i. C 1 i. L 2 t -i. L 1 t i. L 1+i. L 2 0 t i. L 2 t 0 t 32

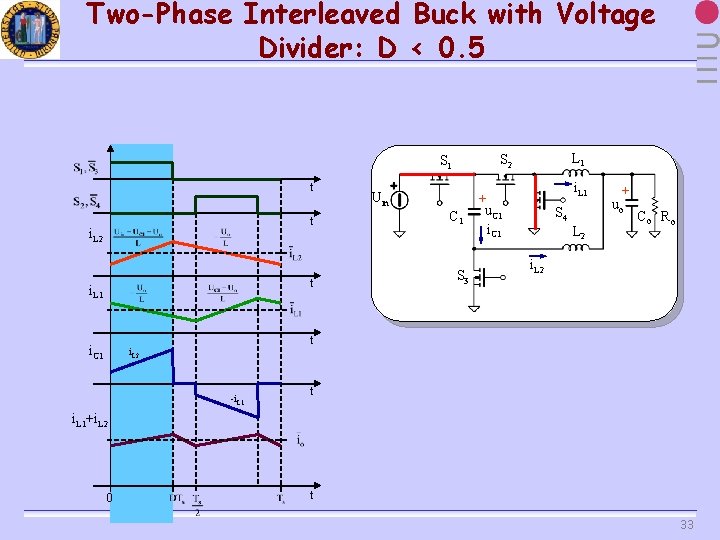

Two-Phase Interleaved Buck with Voltage Divider: D < 0. 5 t t i. L 2 t i. L 1 i. C 1 L 1 S 2 S 1 Uin C 1 S 3 i. L 1 + u. C 1 i. C 1 S 4 L 2 + uo Co Ro i. L 2 t i. L 2 -i. L 1 t i. L 1+i. L 2 0 t 33

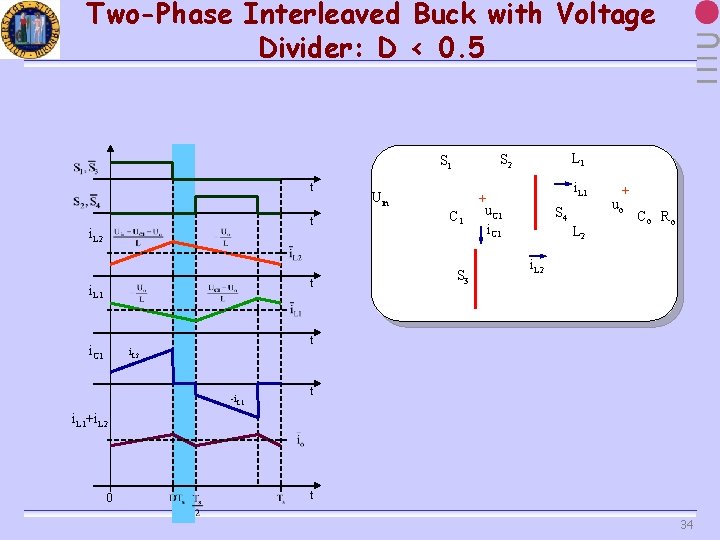

Two-Phase Interleaved Buck with Voltage Divider: D < 0. 5 t t i. L 2 t i. L 1 i. C 1 L 1 S 2 S 1 Uin C 1 S 3 i. L 1 + u. C 1 i. C 1 S 4 L 2 + uo Co Ro i. L 2 t i. L 2 -i. L 1 t i. L 1+i. L 2 0 t 34

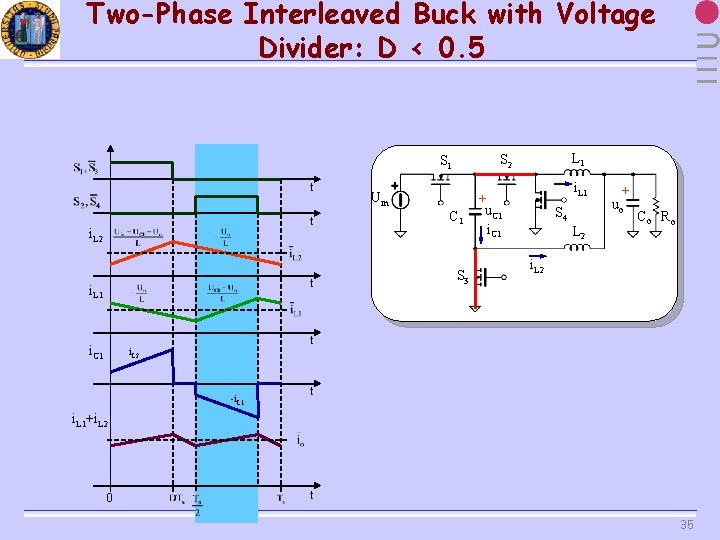

Two-Phase Interleaved Buck with Voltage Divider: D < 0. 5 t t i. L 2 t i. L 1 i. C 1 L 1 S 2 S 1 Uin C 1 S 3 i. L 1 + u. C 1 i. C 1 S 4 L 2 + uo Co Ro i. L 2 t i. L 2 -i. L 1 t i. L 1+i. L 2 0 t 35

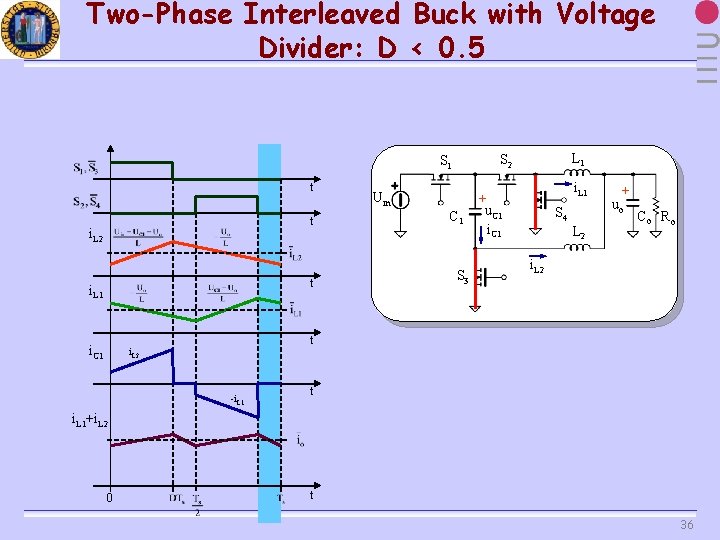

Two-Phase Interleaved Buck with Voltage Divider: D < 0. 5 t t i. L 2 t i. L 1 i. C 1 L 1 S 2 S 1 Uin C 1 S 3 i. L 1 + u. C 1 i. C 1 S 4 L 2 + uo Co Ro i. L 2 t i. L 2 -i. L 1 t i. L 1+i. L 2 0 t 36

Steady-state analysis (D < 0. 5) • Inductor flux balance: • Capacitor charge balance: 37

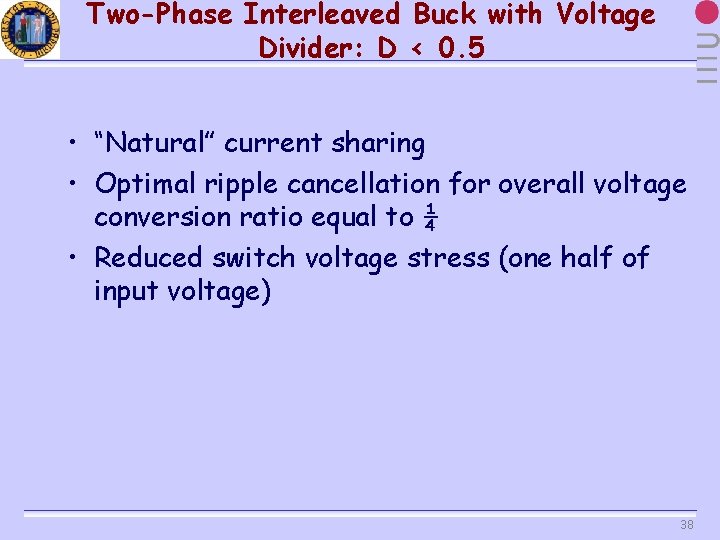

Two-Phase Interleaved Buck with Voltage Divider: D < 0. 5 • “Natural” current sharing • Optimal ripple cancellation for overall voltage conversion ratio equal to ¼ • Reduced switch voltage stress (one half of input voltage) 38

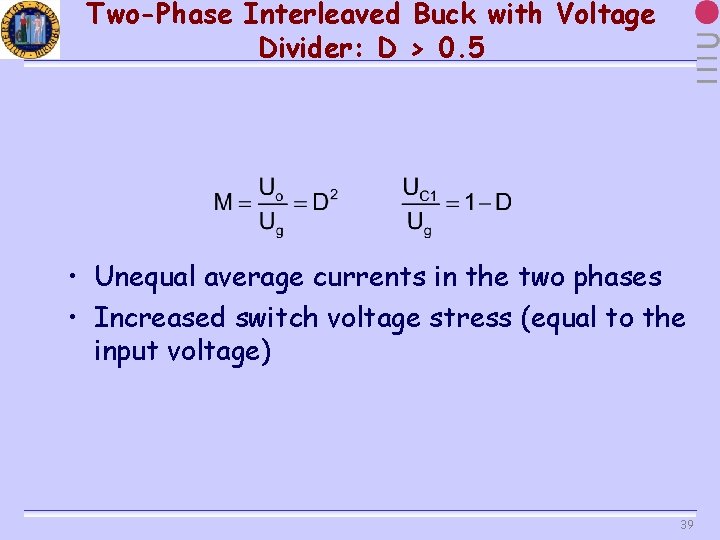

Two-Phase Interleaved Buck with Voltage Divider: D > 0. 5 • Unequal average currents in the two phases • Increased switch voltage stress (equal to the input voltage) 39

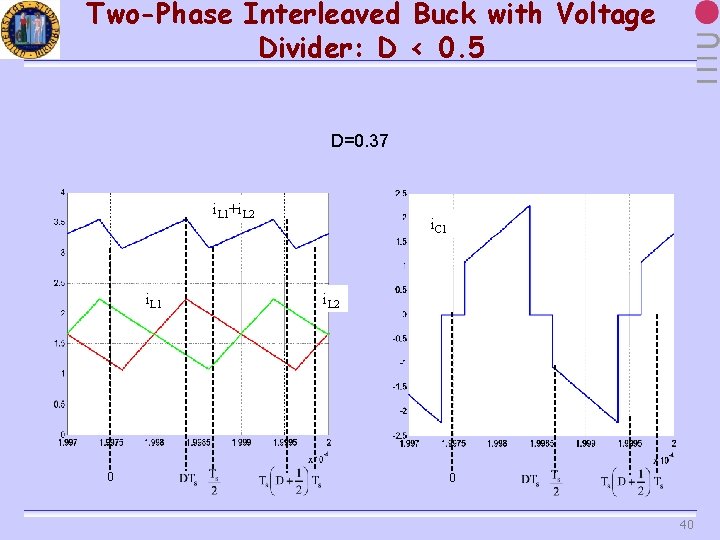

Two-Phase Interleaved Buck with Voltage Divider: D < 0. 5 D=0. 37 i. L 1+i. L 2 i. L 1 0 i. C 1 i. L 2 0 40

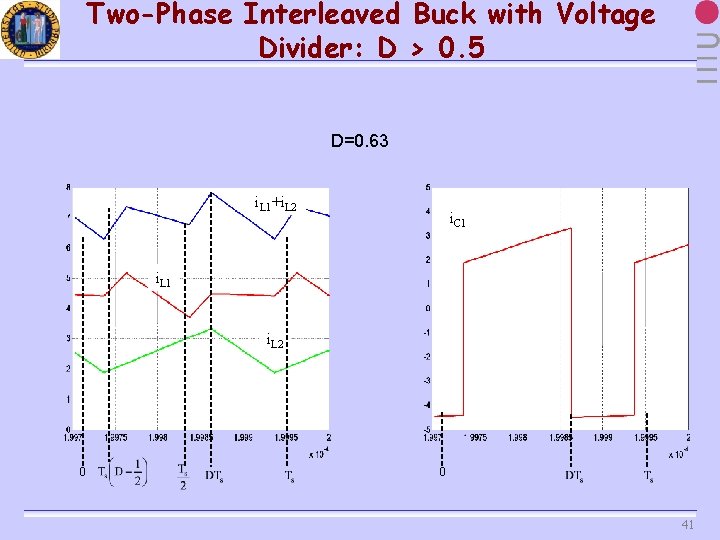

Two-Phase Interleaved Buck with Voltage Divider: D > 0. 5 D=0. 63 i. L 1+i. L 2 i. C 1 i. L 2 0 0 41

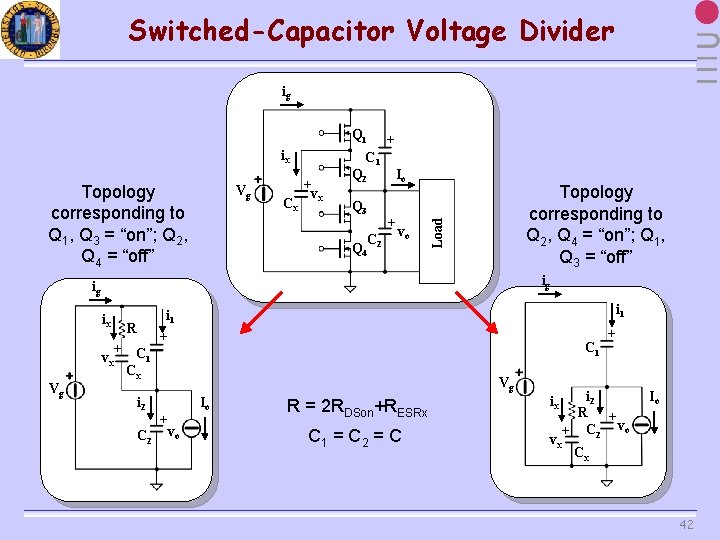

Switched-Capacitor Voltage Divider ig ix Topology corresponding to Q 1, Q 3 = “on”; Q 2, Q 4 = “off” Vg Cx + C 1 + vx Q 2 Q 3 C 2 Q 4 Io + vo Topology corresponding to Q 2, Q 4 = “on”; Q 1, Q 3 = “off” Load Q 1 ig ig ix + vx Vg R i 1 + C 1 Cx i 2 C 2 Vg + Io vo + i 2 R + + C 2 vo R = 2 RDSon+RESRx ix C 1 = C 2 = C vx Io Cx 42

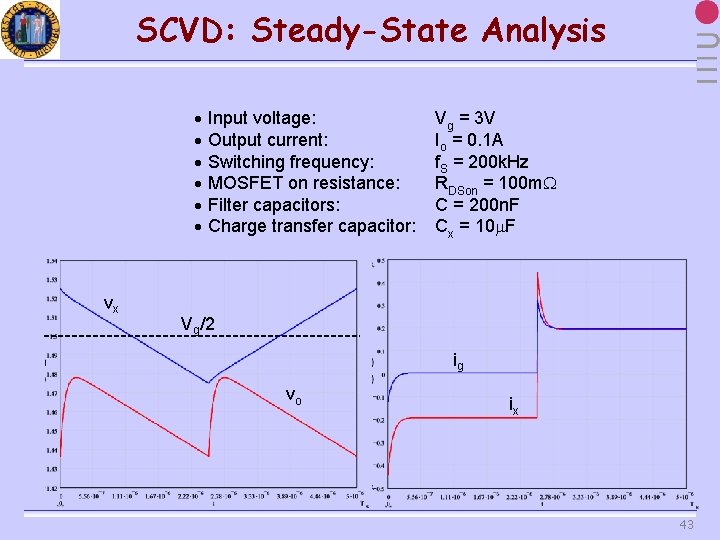

SCVD: Steady-State Analysis vx Input voltage: Output current: Switching frequency: MOSFET on resistance: Filter capacitors: Charge transfer capacitor: Vg = 3 V Io = 0. 1 A f. S = 200 k. Hz RDSon = 100 m. W C = 200 n. F Cx = 10 m. F Vg/2 ig vo ix 43

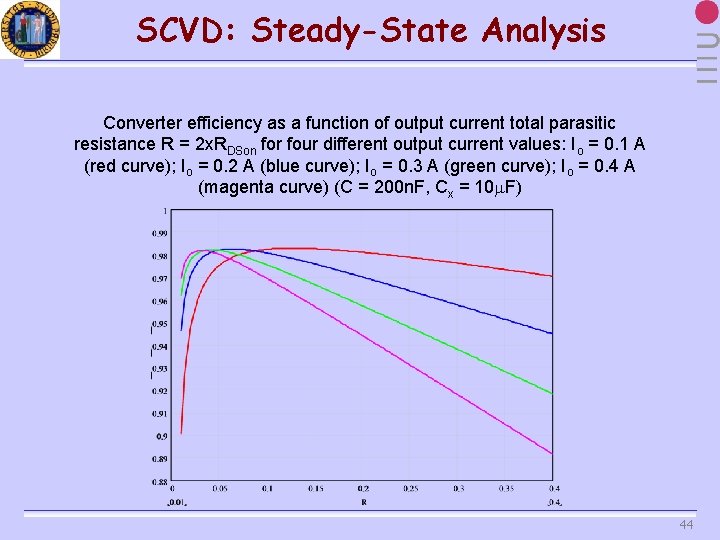

SCVD: Steady-State Analysis Converter efficiency as a function of output current total parasitic resistance R = 2 x. RDSon for four different output current values: Io = 0. 1 A (red curve); Io = 0. 2 A (blue curve); Io = 0. 3 A (green curve); Io = 0. 4 A (magenta curve) (C = 200 n. F, Cx = 10 m. F) 44

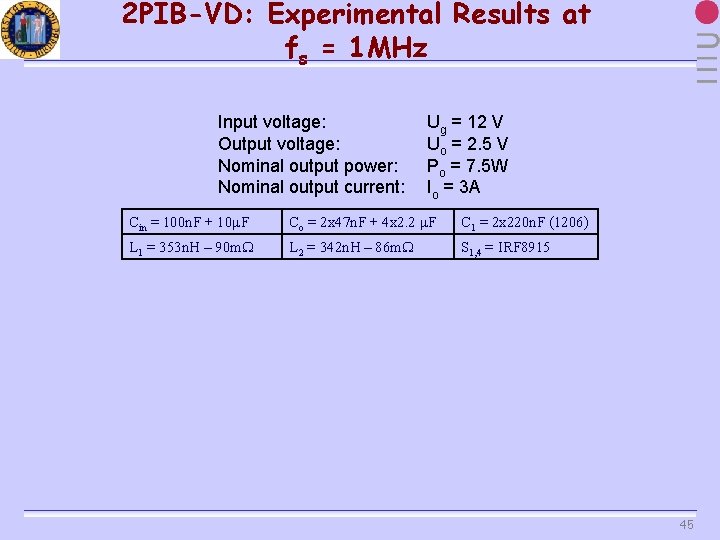

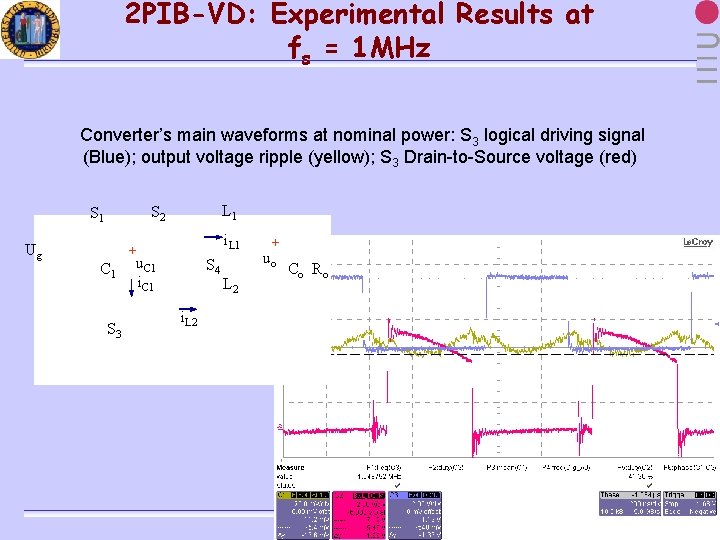

2 PIB-VD: Experimental Results at fs = 1 MHz Input voltage: Output voltage: Nominal output power: Nominal output current: Ug = 12 V Uo = 2. 5 V Po = 7. 5 W Io = 3 A Cin = 100 n. F + 10 m. F Co = 2 x 47 n. F + 4 x 2. 2 m. F C 1 = 2 x 220 n. F (1206) L 1 = 353 n. H – 90 m. W L 2 = 342 n. H – 86 m. W S 1, 4 = IRF 8915 45

2 PIB-VD: Experimental Results at fs = 1 MHz Converter’s main waveforms at nominal power: S 3 logical driving signal (Blue); output voltage ripple (yellow); S 3 Drain-to-Source voltage (red) Ug L 1 S 2 S 1 C 1 S 3 i. L 1 + u. C 1 i. C 1 S 4 L 2 + uo Co Ro i. L 2 46

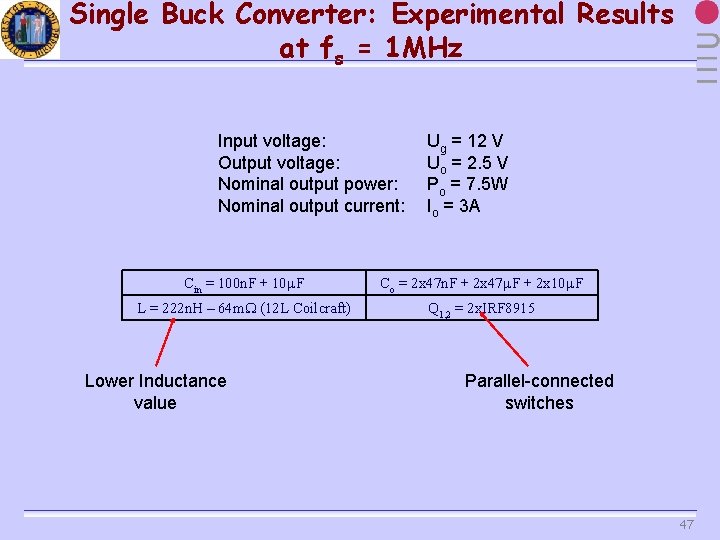

Single Buck Converter: Experimental Results at fs = 1 MHz Input voltage: Output voltage: Nominal output power: Nominal output current: Ug = 12 V Uo = 2. 5 V Po = 7. 5 W Io = 3 A Cin = 100 n. F + 10 m. F Co = 2 x 47 n. F + 2 x 47 m. F + 2 x 10 m. F L = 222 n. H – 64 m. W (12 L Coilcraft) Q 1, 2 = 2 x. IRF 8915 Lower Inductance value Parallel-connected switches 47

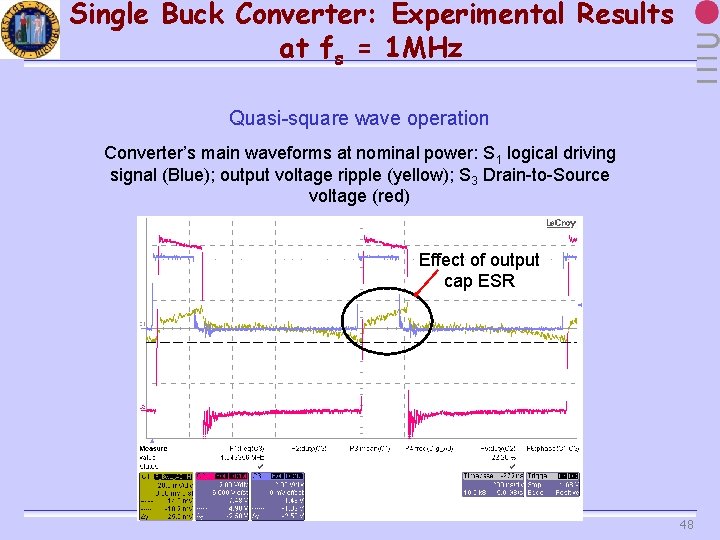

Single Buck Converter: Experimental Results at fs = 1 MHz Quasi-square wave operation Converter’s main waveforms at nominal power: S 1 logical driving signal (Blue); output voltage ripple (yellow); S 3 Drain-to-Source voltage (red) Effect of output cap ESR 48

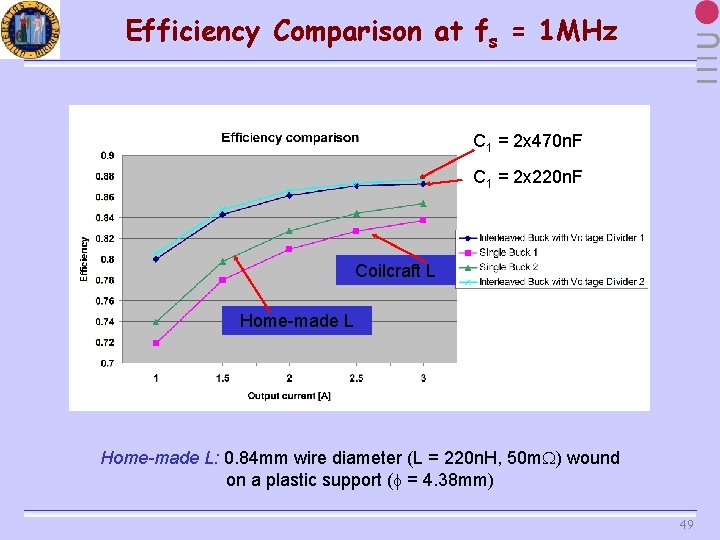

Efficiency Comparison at fs = 1 MHz C 1 = 2 x 470 n. F C 1 = 2 x 220 n. F Coilcraft L Home-made L: 0. 84 mm wire diameter (L = 220 n. H, 50 m. W) wound on a plastic support (f = 4. 38 mm) 49

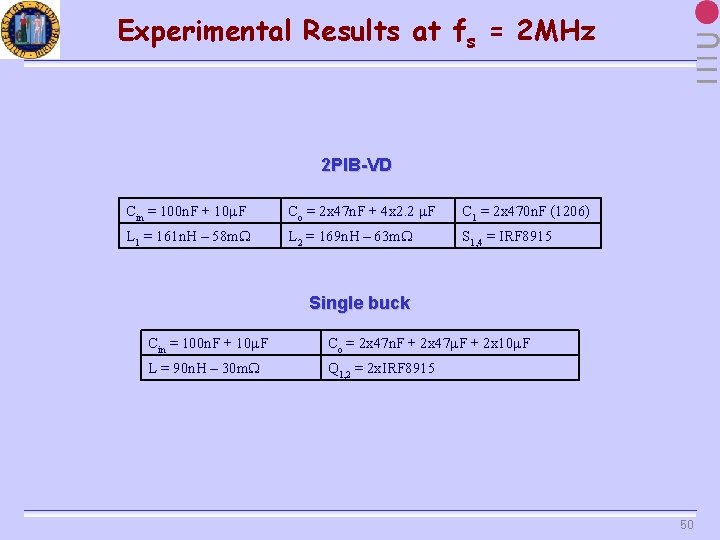

Experimental Results at fs = 2 MHz 2 PIB-VD Cin = 100 n. F + 10 m. F Co = 2 x 47 n. F + 4 x 2. 2 m. F C 1 = 2 x 470 n. F (1206) L 1 = 161 n. H – 58 m. W L 2 = 169 n. H – 63 m. W S 1, 4 = IRF 8915 Single buck Cin = 100 n. F + 10 m. F Co = 2 x 47 n. F + 2 x 47 m. F + 2 x 10 m. F L = 90 n. H – 30 m. W Q 1, 2 = 2 x. IRF 8915 50

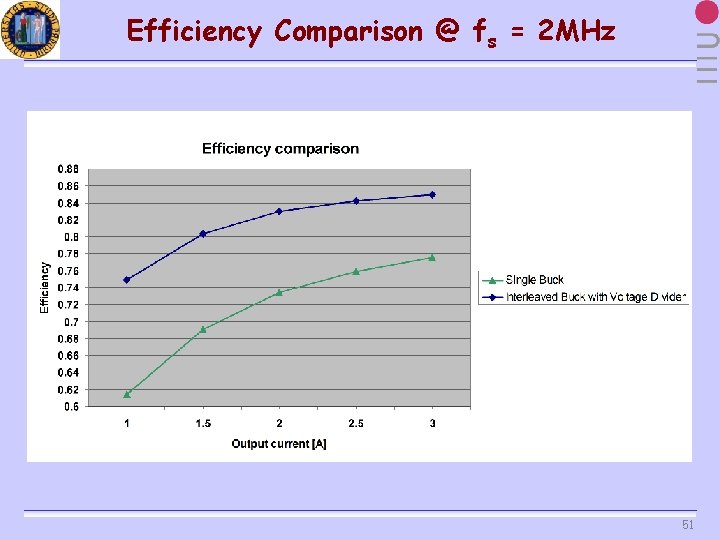

Efficiency Comparison @ fs = 2 MHz 51

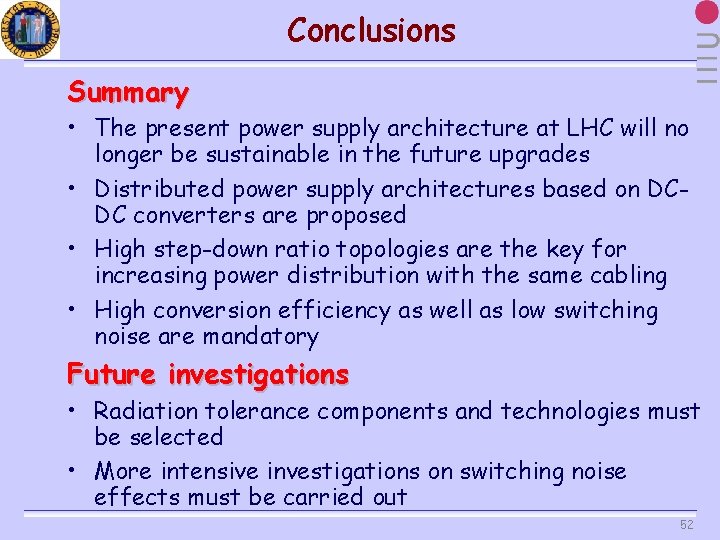

Conclusions Summary • The present power supply architecture at LHC will no longer be sustainable in the future upgrades • Distributed power supply architectures based on DCDC converters are proposed • High step-down ratio topologies are the key for increasing power distribution with the same cabling • High conversion efficiency as well as low switching noise are mandatory Future investigations • Radiation tolerance components and technologies must be selected • More intensive investigations on switching noise effects must be carried out 52

- Slides: 50