Power Supply Control Interface and Orbit Feedback Environment

Power Supply Control Interface and Orbit Feedback Environment for TPS Pei-Chen Chiu On-behalf of the TPS Feedback Team NSRRC, Hsinchu, Taiwan EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011

Outline • • • TPS Power Supply & Control Interface Integrated Orbit Feedback System Infrastructure Corrector Control Interface BPM & Feedback Engine Interface Summary EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 2

Power Supply and Control Interface EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011

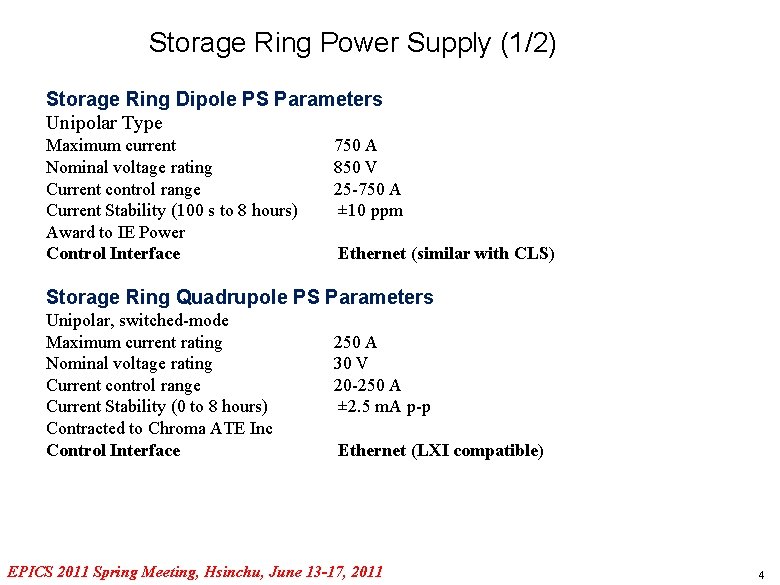

Storage Ring Power Supply (1/2) Storage Ring Dipole PS Parameters Unipolar Type Maximum current Nominal voltage rating Current control range Current Stability (100 s to 8 hours) Award to IE Power Control Interface 750 A 850 V 25 -750 A ± 10 ppm Ethernet (similar with CLS) Storage Ring Quadrupole PS Parameters Unipolar, switched-mode Maximum current rating Nominal voltage rating Current control range Current Stability (0 to 8 hours) Contracted to Chroma ATE Inc Control Interface 250 A 30 V 20 -250 A ± 2. 5 m. A p-p Ethernet (LXI compatible) EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 4

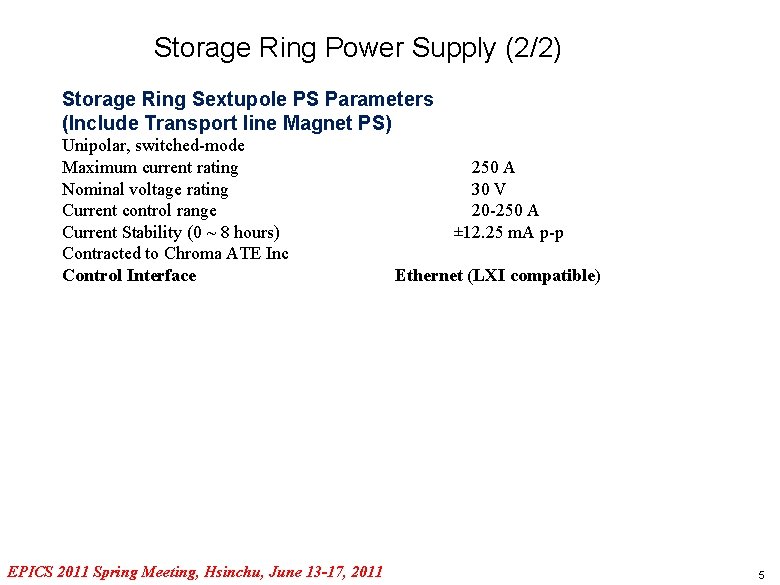

Storage Ring Power Supply (2/2) Storage Ring Sextupole PS Parameters (Include Transport line Magnet PS) Unipolar, switched-mode Maximum current rating Nominal voltage rating Current control range Current Stability (0 ~ 8 hours) Contracted to Chroma ATE Inc Control Interface EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 250 A 30 V 20 -250 A ± 12. 25 m. A p-p Ethernet (LXI compatible) 5

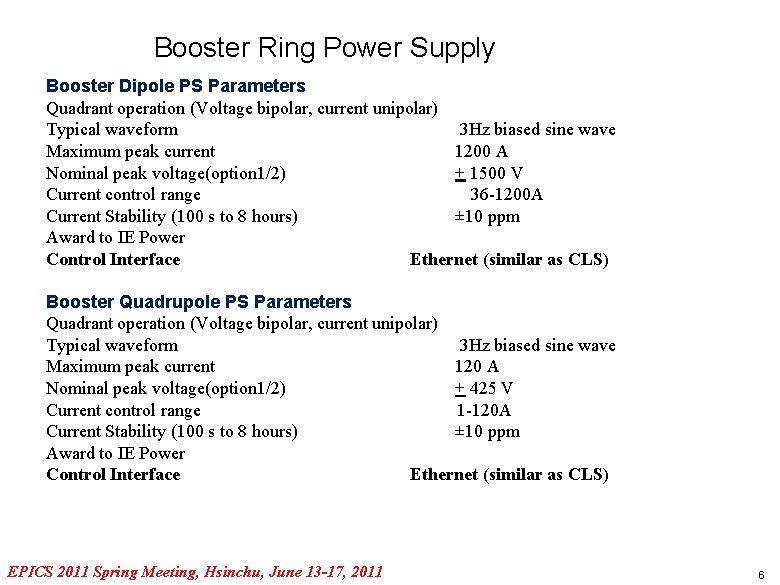

Booster Ring Power Supply Booster Dipole PS Parameters Quadrant operation (Voltage bipolar, current unipolar) Typical waveform 3 Hz biased sine wave Maximum peak current 1200 A Nominal peak voltage(option 1/2) + 1500 V Current control range 36 -1200 A Current Stability (100 s to 8 hours) ± 10 ppm Award to IE Power Control Interface Ethernet (similar as CLS) Booster Quadrupole PS Parameters Quadrant operation (Voltage bipolar, current unipolar) Typical waveform 3 Hz biased sine wave Maximum peak current 120 A Nominal peak voltage(option 1/2) + 425 V Current control range 1 -120 A Current Stability (100 s to 8 hours) ± 10 ppm Award to IE Power Control Interface Ethernet (similar as CLS) EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 6

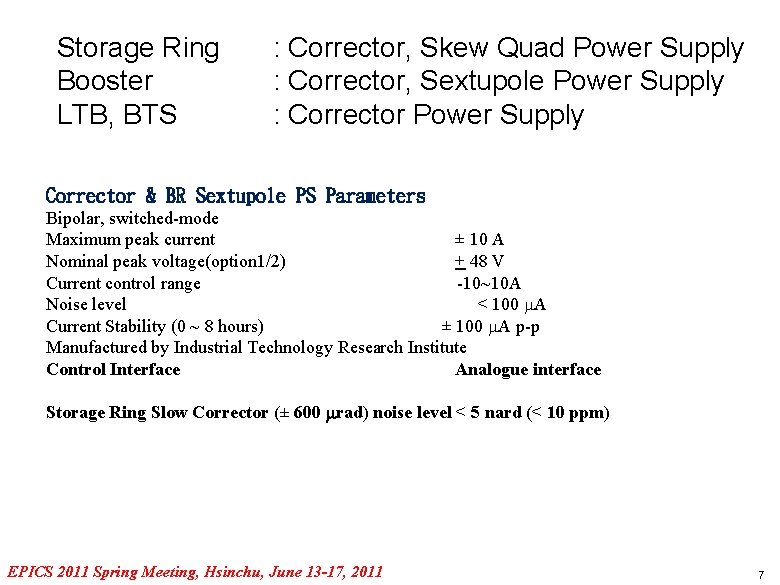

Storage Ring Booster LTB, BTS : Corrector, Skew Quad Power Supply : Corrector, Sextupole Power Supply : Corrector Power Supply Corrector & BR Sextupole PS Parameters Bipolar, switched-mode Maximum peak current ± 10 A Nominal peak voltage(option 1/2) + 48 V Current control range -10~10 A Noise level < 100 m. A Current Stability (0 ~ 8 hours) ± 100 m. A p-p Manufactured by Industrial Technology Research Institute Control Interface Analogue interface Storage Ring Slow Corrector (± 600 mrad) noise level < 5 nard (< 10 ppm) EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 7

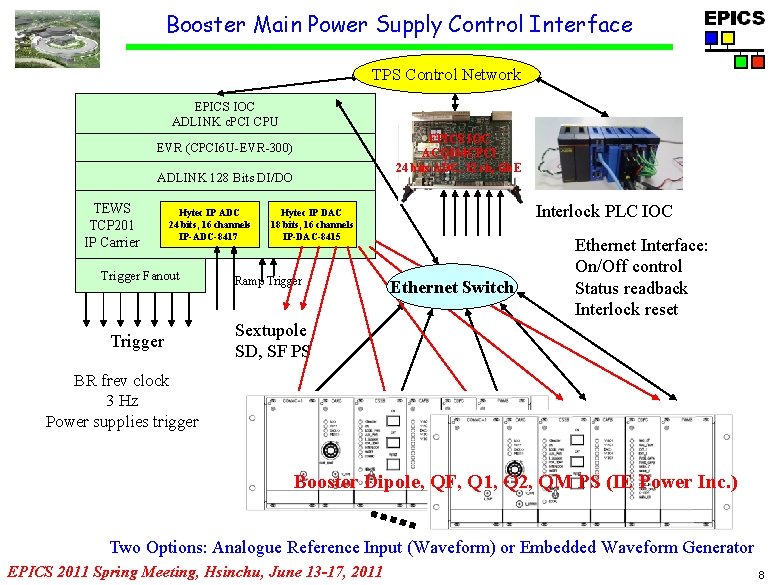

Booster Main Power Supply Control Interface TPS Control Network EPICS IOC ADLINK c. PCI CPU EVR (CPCI 6 U-EVR-300) ADLINK 128 Bits DI/DO TEWS TCP 201 IP Carrier Hytec IP ADC 24 bits, 16 channels IP-ADC-8417 Trigger Fanout Trigger EPICS IOC ACQ 164 CPCI 24 bits ADC, 32 ch, Gb. E Interlock PLC IOC Hytec IP DAC 18 bits, 16 channels IP-DAC-8415 Ramp Trigger Ethernet Switch Ethernet Interface: On/Off control Status readback Interlock reset Sextupole SD, SF PS BR frev clock 3 Hz Power supplies trigger Booster Dipole, QF, Q 1, Q 2, QM PS (IE Power Inc. ) Two Options: Analogue Reference Input (Waveform) or Embedded Waveform Generator EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 8

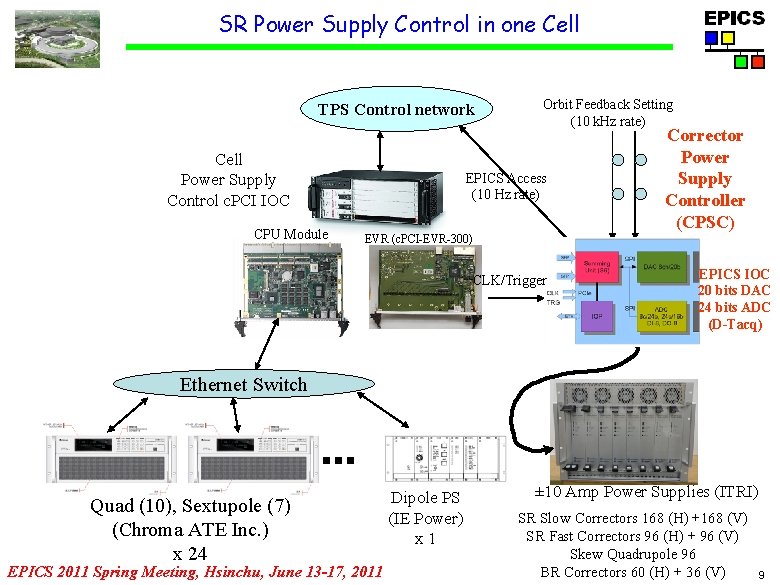

SR Power Supply Control in one Cell TPS Control network Cell Power Supply Control c. PCI IOC CPU Module Orbit Feedback Setting (10 k. Hz rate) EPICS Access (10 Hz rate) Corrector Power Supply Controller (CPSC) EVR (c. PCI-EVR-300) CLK/Trigger EPICS IOC 20 bits DAC 24 bits ADC (D-Tacq) Ethernet Switch Quad (10), Sextupole (7) (Chroma ATE Inc. ) x 24 EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 Dipole PS (IE Power) x 1 ± 10 Amp Power Supplies (ITRI) SR Slow Correctors 168 (H) +168 (V) SR Fast Correctors 96 (H) + 96 (V) Skew Quadrupole 96 BR Correctors 60 (H) + 36 (V) 9

Integrated Orbit Feedback System Infrastructure EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011

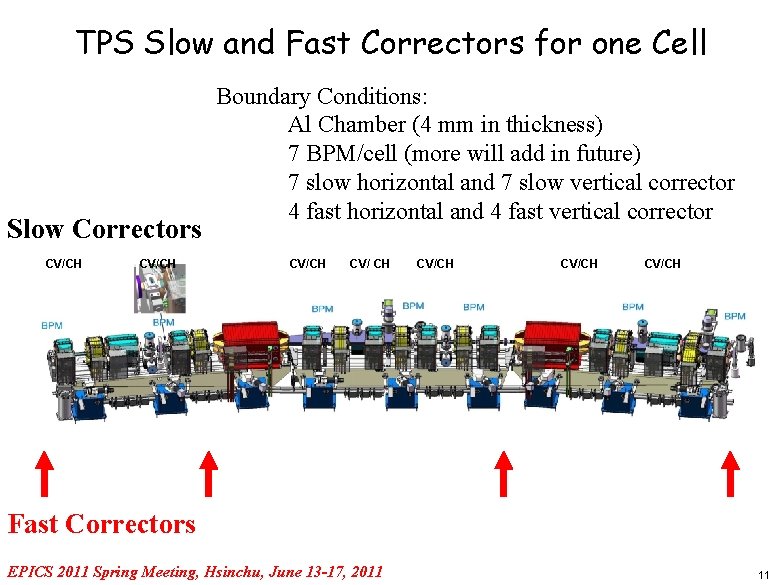

TPS Slow and Fast Correctors for one Cell Slow Correctors CV/CH Boundary Conditions: Al Chamber (4 mm in thickness) 7 BPM/cell (more will add in future) 7 slow horizontal and 7 slow vertical corrector 4 fast horizontal and 4 fast vertical corrector CV/CH CV/CH CV/CH Fast Correctors EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 11

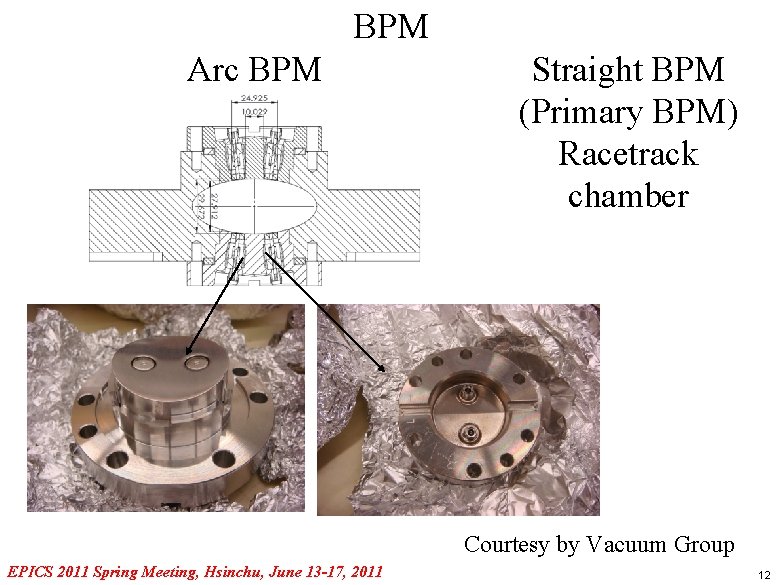

BPM Arc BPM Straight BPM (Primary BPM) Racetrack chamber Courtesy by Vacuum Group EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 12

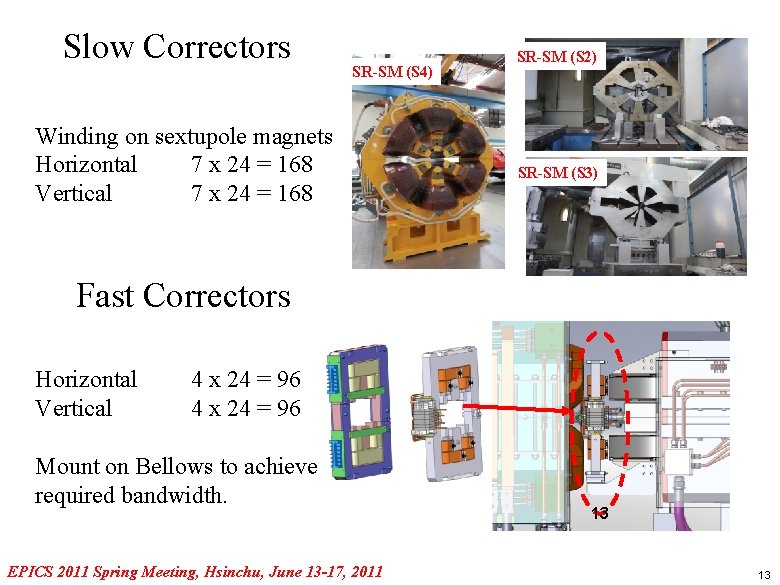

Slow Correctors SR-SM (S 4) Winding on sextupole magnets Horizontal 7 x 24 = 168 Vertical 7 x 24 = 168 SR-SM (S 2) SR-SM (S 3) Fast Correctors Horizontal Vertical 4 x 24 = 96 Mount on Bellows to achieve required bandwidth. EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 13 13

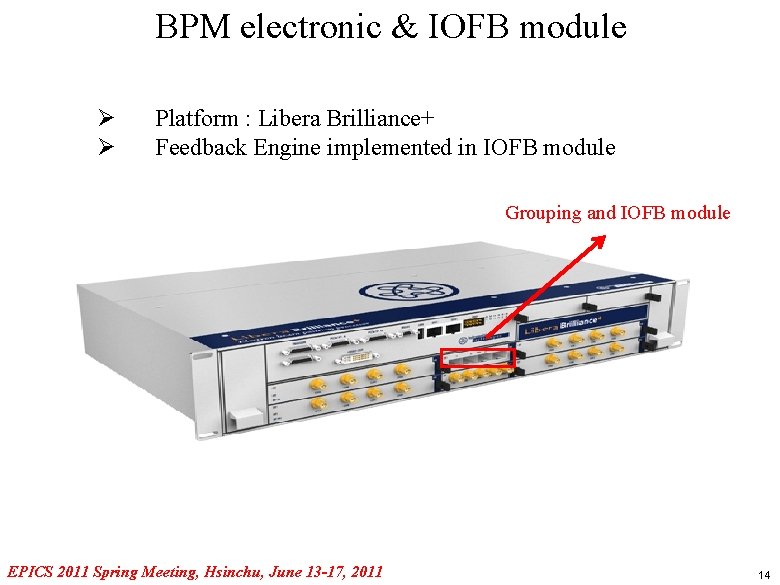

BPM electronic & IOFB module Ø Ø Platform : Libera Brilliance+ Feedback Engine implemented in IOFB module Grouping and IOFB module EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 14

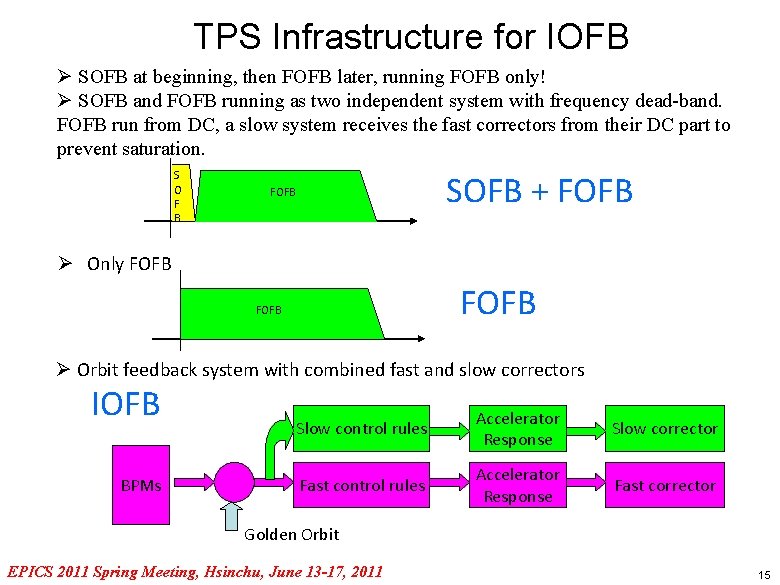

TPS Infrastructure for IOFB Ø SOFB at beginning, then FOFB later, running FOFB only! Ø SOFB and FOFB running as two independent system with frequency dead-band. FOFB run from DC, a slow system receives the fast correctors from their DC part to prevent saturation. S O F B SOFB + FOFB Ø Only FOFB Ø Orbit feedback system with combined fast and slow correctors IOFB BPMs Slow control rules Accelerator Response Slow corrector Fast control rules Accelerator Response Fast corrector Golden Orbit EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 15

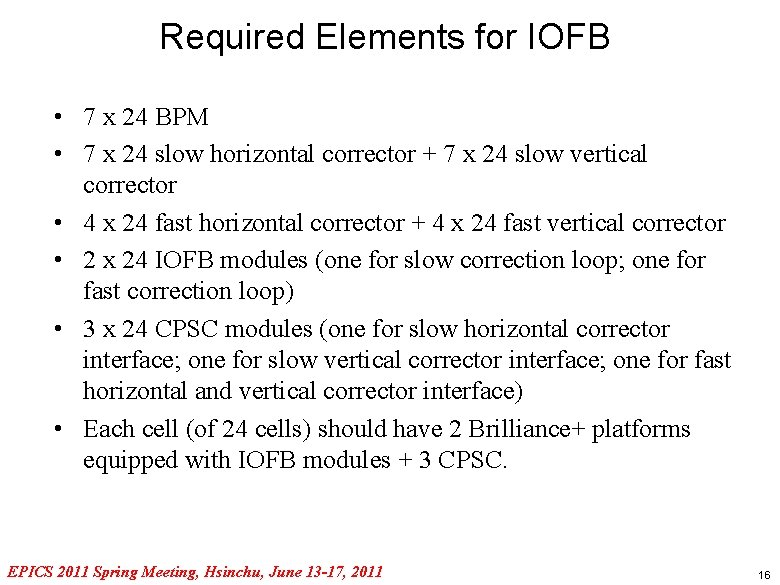

Required Elements for IOFB • 7 x 24 BPM • 7 x 24 slow horizontal corrector + 7 x 24 slow vertical corrector • 4 x 24 fast horizontal corrector + 4 x 24 fast vertical corrector • 2 x 24 IOFB modules (one for slow correction loop; one for fast correction loop) • 3 x 24 CPSC modules (one for slow horizontal corrector interface; one for slow vertical corrector interface; one for fast horizontal and vertical corrector interface) • Each cell (of 24 cells) should have 2 Brilliance+ platforms equipped with IOFB modules + 3 CPSC. EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 16

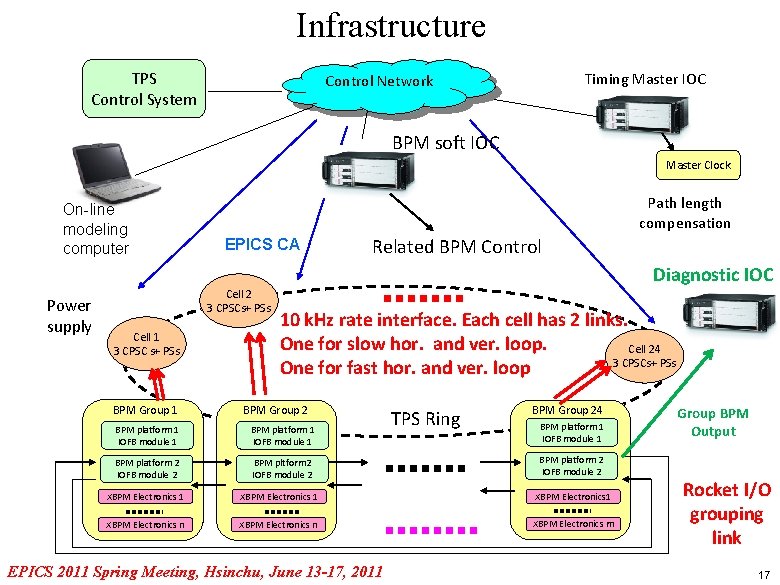

Infrastructure TPS Control System Timing Master IOC Control Network BPM soft IOC Master Clock On-line modeling computer Power supply Path length compensation EPICS CA Cell 2 3 CPSCs+ PSs Cell 1 3 CPSC s+ PSs BPM Group 1 Related BPM Control Diagnostic IOC 10 k. Hz rate interface. Each cell has 2 links. One for slow hor. and ver. loop. Cell 24 3 CPSCs+ PSs One for fast hor. and ver. loop BPM Group 2 TPS Ring BPM Group 24 BPM platform 1 IOFB module 1 BPM platform 2 IOFB module 2 XBPM Electronics 1 XBPM Electronics n XBPM Electronics m EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 Group BPM Output Rocket I/O grouping link 17

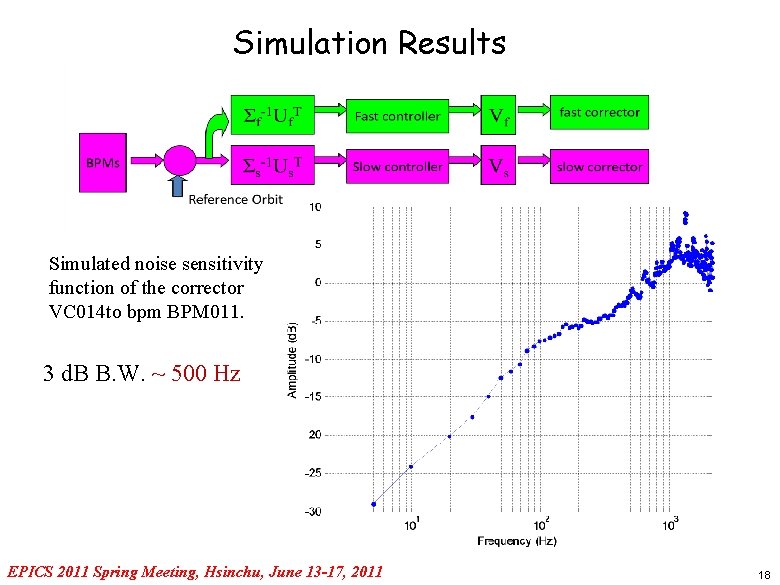

Simulation Results Simulated noise sensitivity function of the corrector VC 014 to bpm BPM 011. 3 d. B B. W. ~ 500 Hz EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 18

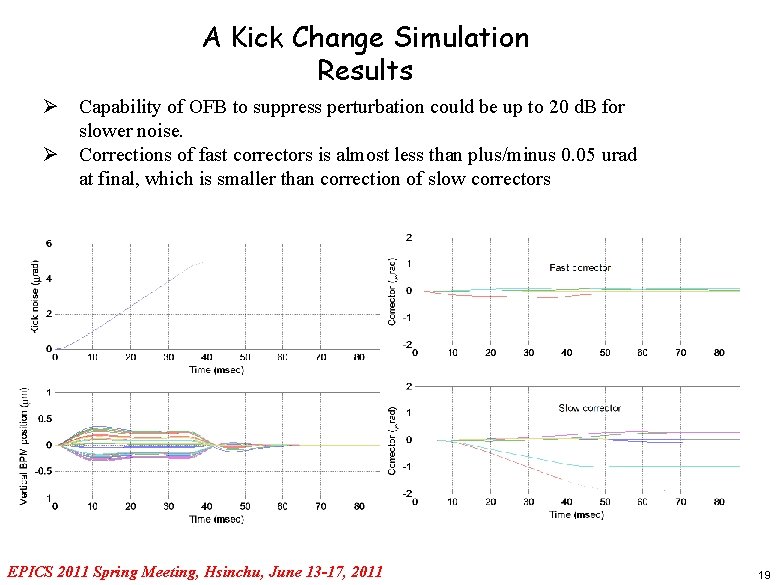

A Kick Change Simulation Results Ø Capability of OFB to suppress perturbation could be up to 20 d. B for slower noise. Ø Corrections of fast correctors is almost less than plus/minus 0. 05 urad at final, which is smaller than correction of slow correctors EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 19

Corrector Control Interface EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011

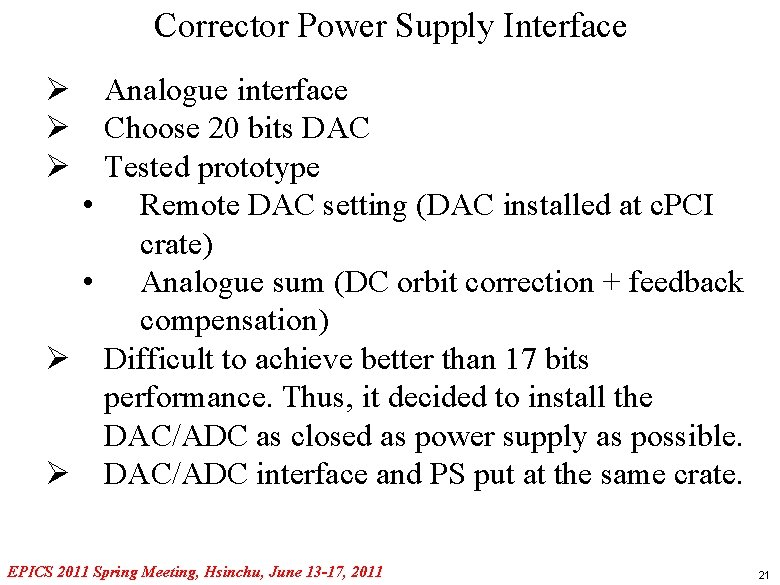

Corrector Power Supply Interface Ø Ø Ø Analogue interface Choose 20 bits DAC Tested prototype • Remote DAC setting (DAC installed at c. PCI crate) • Analogue sum (DC orbit correction + feedback compensation) Ø Difficult to achieve better than 17 bits performance. Thus, it decided to install the DAC/ADC as closed as power supply as possible. Ø DAC/ADC interface and PS put at the same crate. EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 21

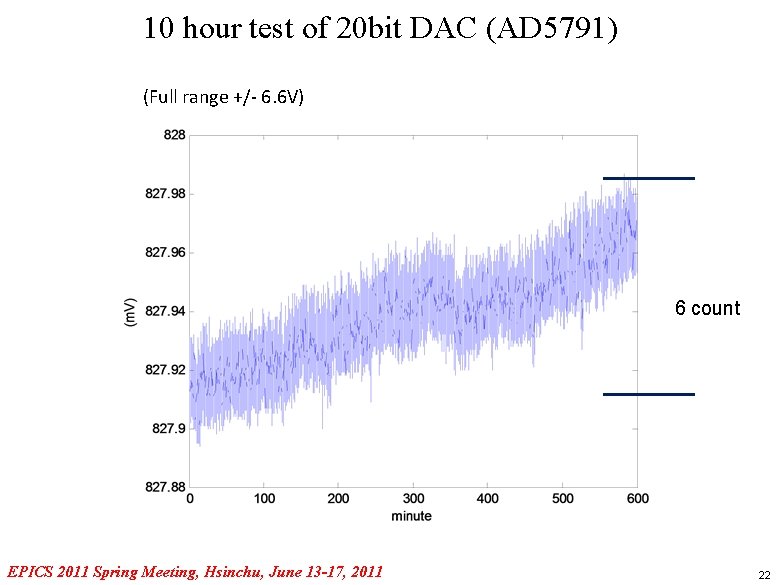

10 hour test of 20 bit DAC (AD 5791) (Full range +/- 6. 6 V) 6 count EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 22

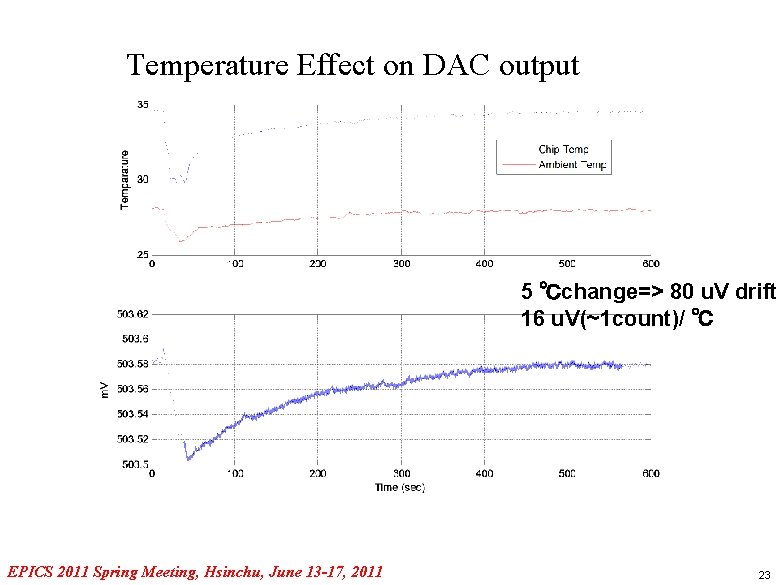

Temperature Effect on DAC output 5 ℃change=> 80 u. V drift 16 u. V(~1 count)/ ℃ EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 23

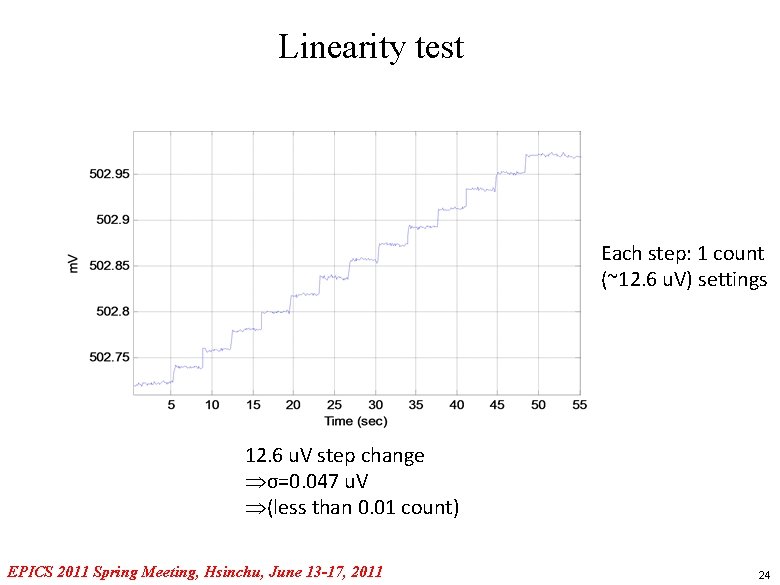

Linearity test Each step: 1 count (~12. 6 u. V) settings 12. 6 u. V step change Þσ=0. 047 u. V Þ(less than 0. 01 count) EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 24

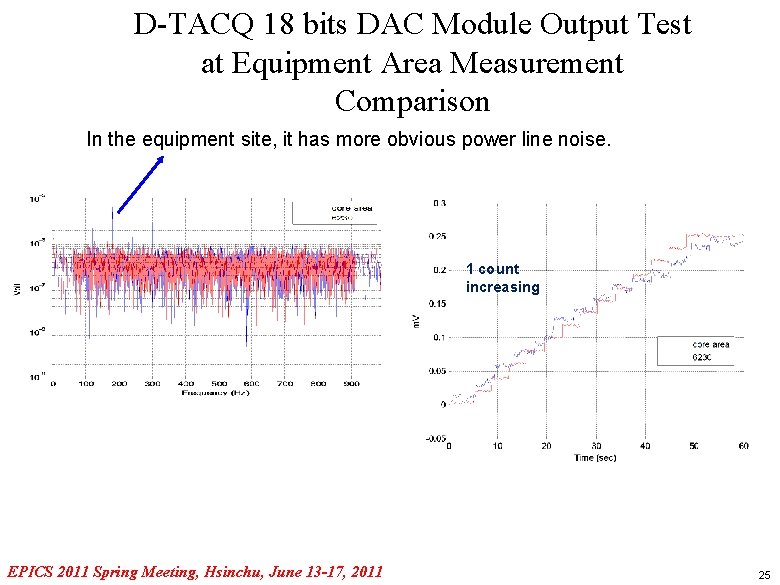

D-TACQ 18 bits DAC Module Output Test at Equipment Area Measurement Comparison In the equipment site, it has more obvious power line noise. 1 count increasing EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 25

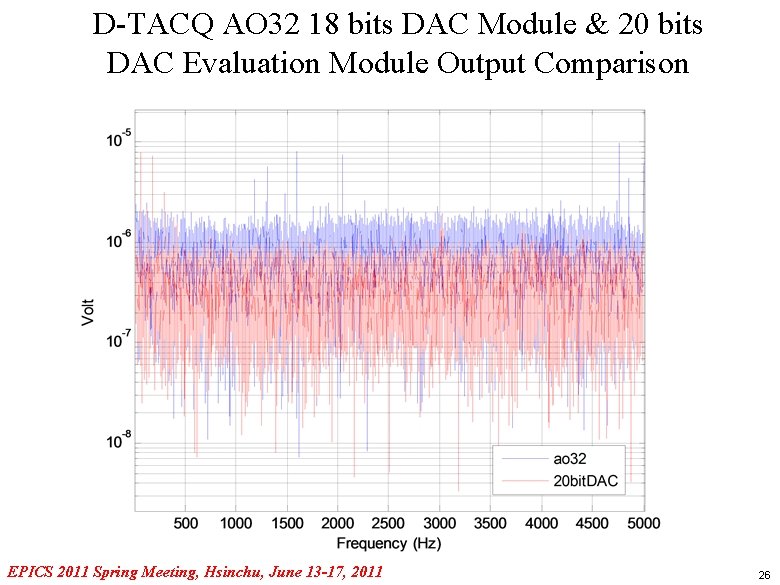

D-TACQ AO 32 18 bits DAC Module & 20 bits DAC Evaluation Module Output Comparison EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 26

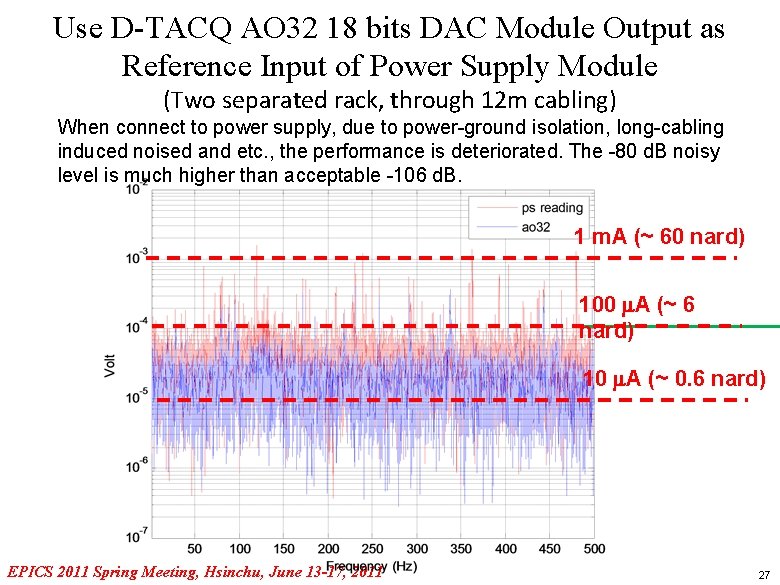

Use D-TACQ AO 32 18 bits DAC Module Output as Reference Input of Power Supply Module (Two separated rack, through 12 m cabling) When connect to power supply, due to power-ground isolation, long-cabling induced noised and etc. , the performance is deteriorated. The -80 d. B noisy level is much higher than acceptable -106 d. B. 1 m. A (~ 60 nard) 100 m. A (~ 6 nard) 10 m. A (~ 0. 6 nard) EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 27

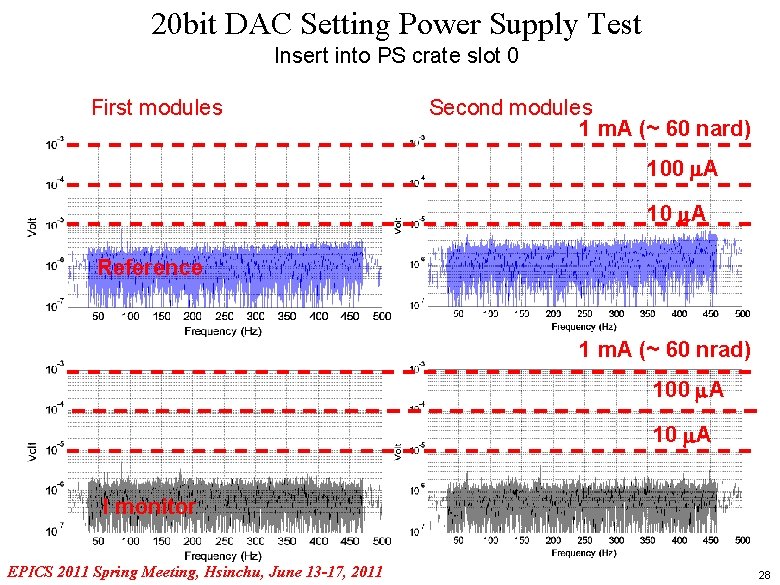

20 bit DAC Setting Power Supply Test Insert into PS crate slot 0 First modules Second modules 1 m. A (~ 60 nard) 100 m. A 10 m. A Reference 1 m. A (~ 60 nrad) 100 m. A 10 m. A I monitor EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 28

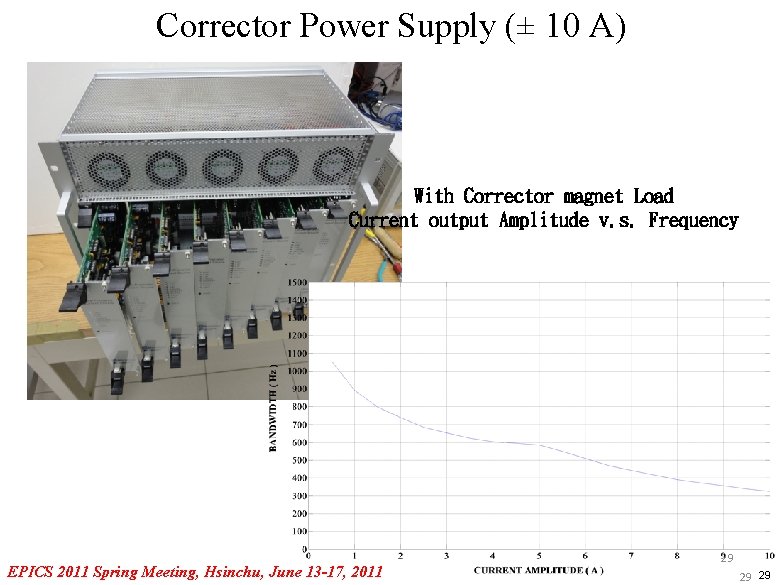

Corrector Power Supply (± 10 A) With Corrector magnet Load Current output Amplitude v. s. Frequency EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 29 29 29

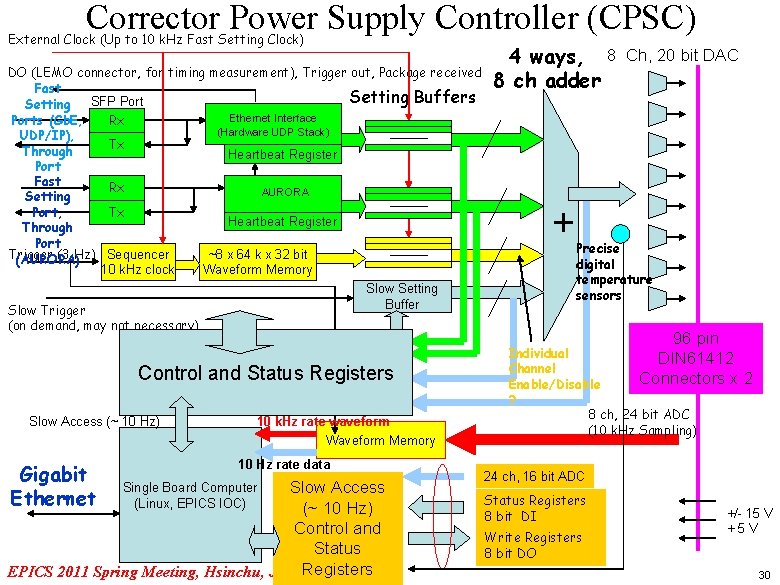

Corrector Power Supply Controller (CPSC) External Clock (Up to 10 k. Hz Fast Setting Clock) DO (LEMO connector, for timing measurement), Trigger out, Package received Fast Setting Buffers SFP Port Setting Ethernet Interface Ports (Gb. E, Rx (Hardware UDP Stack) UDP/IP), Tx Through Heartbeat Register Port Fast Rx AURORA Setting Port, Tx Heartbeat Register Through Port ~8 x 64 k x 32 bit Trigger (3 Hz) Sequencer (AURORA) 10 k. Hz clock Waveform Memory Slow Setting Buffer Slow Trigger 4 ways, 8 Ch, 20 bit DAC 8 ch adder + Precise digital temperature sensors (on demand, may not necessary) Control and Status Registers Slow Access (~ 10 Hz) Gigabit Ethernet 10 k. Hz rate waveform Waveform Memory 10 Hz rate data Slow Access (~ 10 Hz) Control and Status EPICS 2011 Spring Meeting, Hsinchu, June. Registers 13 -17, 2011 Single Board Computer (Linux, EPICS IOC) 96 pin DIN 61412 Connectors x 2 Individual Channel Enable/Disable ? 8 ch, 24 bit ADC (10 k. Hz Sampling) 24 ch, 16 bit ADC Status Registers 8 bit DI Write Registers 8 bit DO +/- 15 V +5 V 30

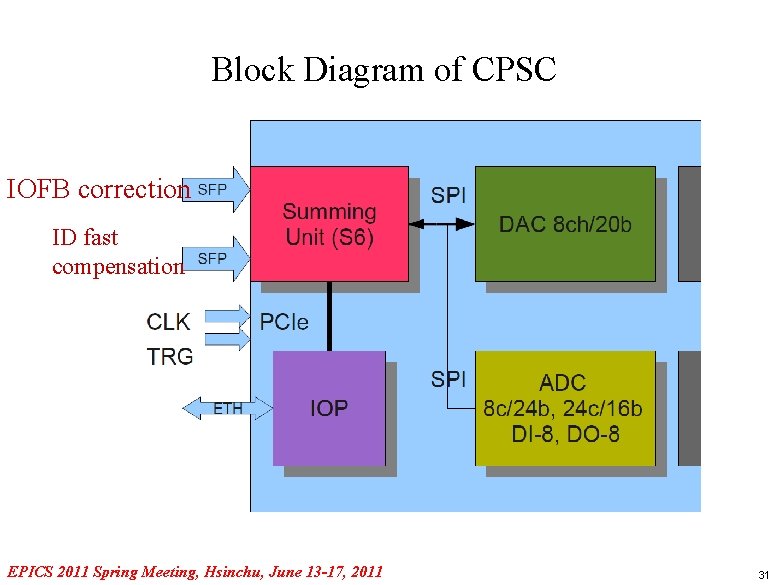

Block Diagram of CPSC IOFB correction ID fast compensation EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 31

Feedback Engine Interface EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011

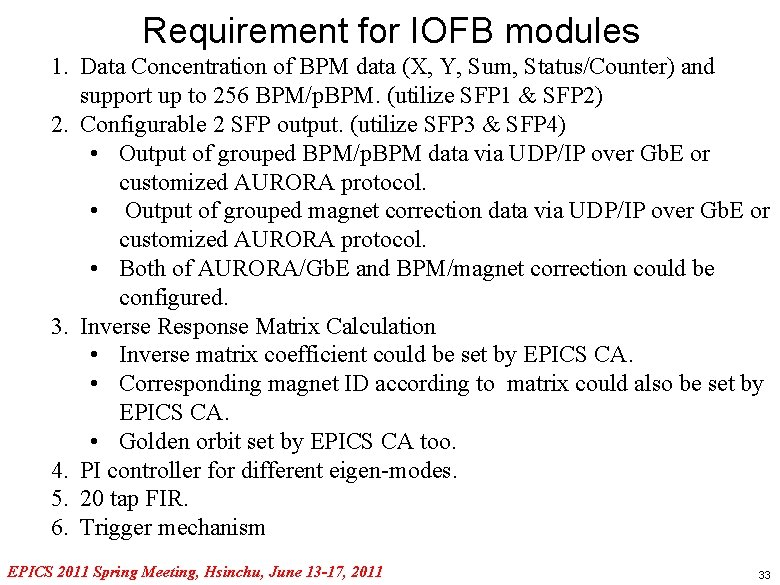

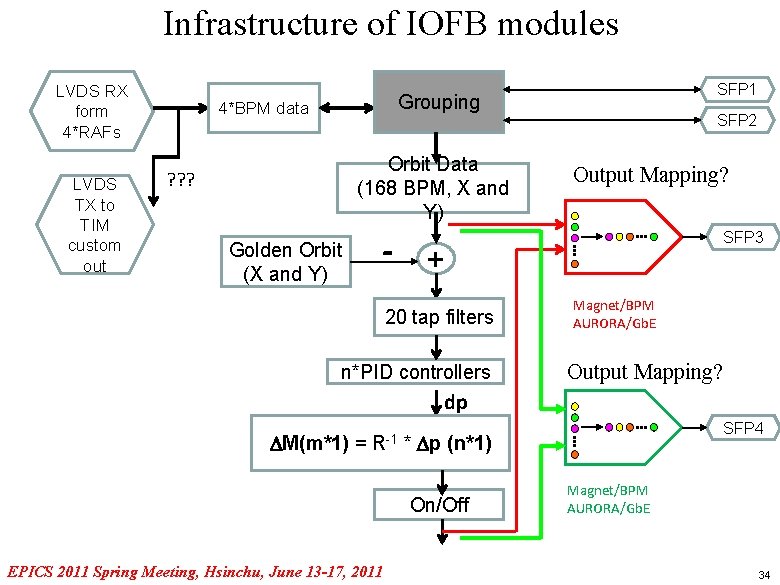

Requirement for IOFB modules 1. Data Concentration of BPM data (X, Y, Sum, Status/Counter) and support up to 256 BPM/p. BPM. (utilize SFP 1 & SFP 2) 2. Configurable 2 SFP output. (utilize SFP 3 & SFP 4) • Output of grouped BPM/p. BPM data via UDP/IP over Gb. E or customized AURORA protocol. • Output of grouped magnet correction data via UDP/IP over Gb. E or customized AURORA protocol. • Both of AURORA/Gb. E and BPM/magnet correction could be configured. 3. Inverse Response Matrix Calculation • Inverse matrix coefficient could be set by EPICS CA. • Corresponding magnet ID according to matrix could also be set by EPICS CA. • Golden orbit set by EPICS CA too. 4. PI controller for different eigen-modes. 5. 20 tap FIR. 6. Trigger mechanism EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 33

Infrastructure of IOFB modules LVDS RX form 4*RAFs LVDS TX to TIM custom out SFP 1 Grouping 4*BPM data Orbit Data (168 BPM, X and Y) ? ? ? Golden Orbit (X and Y) SFP 2 Output Mapping? - + 20 tap filters n*PID controllers SFP 3 Magnet/BPM AURORA/Gb. E Output Mapping? dp DM(m*1) = R-1 * Dp (n*1) On/Off EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 SFP 4 Magnet/BPM AURORA/Gb. E 34

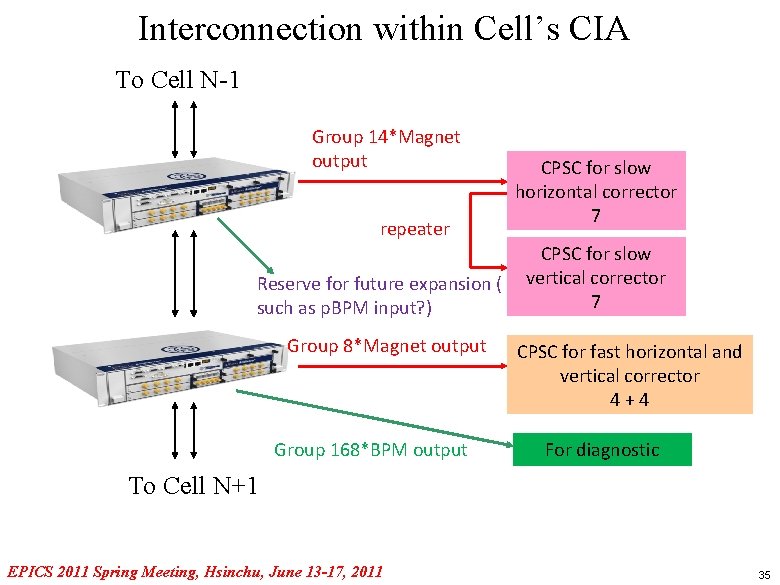

Interconnection within Cell’s CIA To Cell N-1 Group 14*Magnet output repeater Reserve for future expansion ( such as p. BPM input? ) Group 8*Magnet output Group 168*BPM output CPSC for slow horizontal corrector 7 CPSC for slow vertical corrector 7 CPSC for fast horizontal and vertical corrector 4+4 For diagnostic To Cell N+1 EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 35

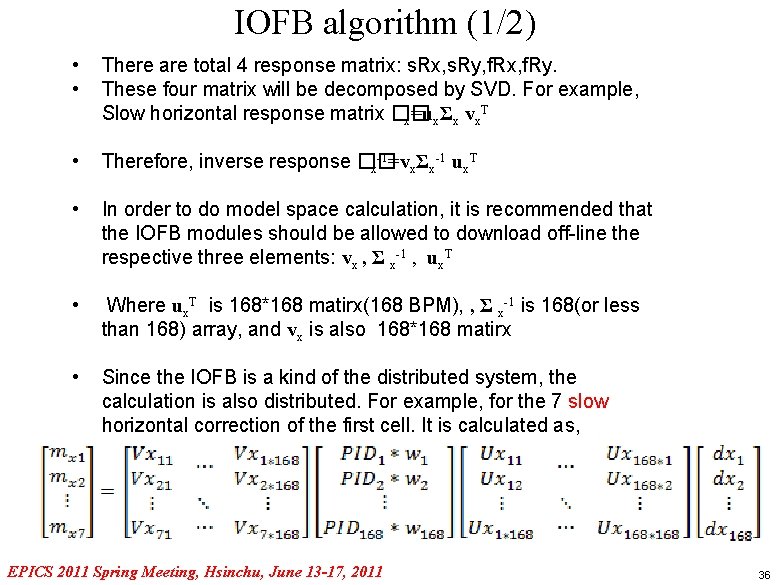

IOFB algorithm (1/2) • • There are total 4 response matrix: s. Rx, s. Ry, f. Rx, f. Ry. These four matrix will be decomposed by SVD. For example, T Slow horizontal response matrix �� x=uxΣx vx • -1 -1 T Therefore, inverse response �� x =vxΣx ux • In order to do model space calculation, it is recommended that the IOFB modules should be allowed to download off-line the respective three elements: vx , Σ x-1 , ux. T • Where ux. T is 168*168 matirx(168 BPM), , Σ x-1 is 168(or less than 168) array, and vx is also 168*168 matirx • Since the IOFB is a kind of the distributed system, the calculation is also distributed. For example, for the 7 slow horizontal correction of the first cell. It is calculated as, EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 36

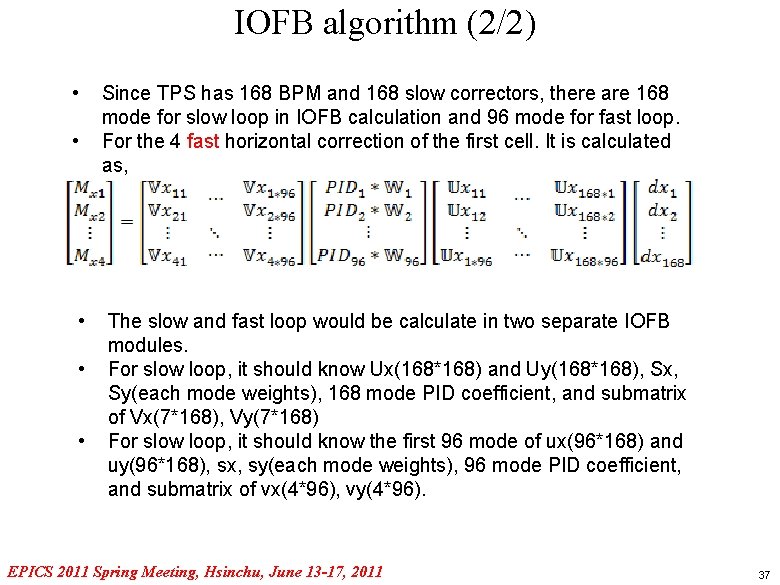

IOFB algorithm (2/2) • • • Since TPS has 168 BPM and 168 slow correctors, there are 168 mode for slow loop in IOFB calculation and 96 mode for fast loop. For the 4 fast horizontal correction of the first cell. It is calculated as, The slow and fast loop would be calculate in two separate IOFB modules. For slow loop, it should know Ux(168*168) and Uy(168*168), Sx, Sy(each mode weights), 168 mode PID coefficient, and submatrix of Vx(7*168), Vy(7*168) For slow loop, it should know the first 96 mode of ux(96*168) and uy(96*168), sx, sy(each mode weights), 96 mode PID coefficient, and submatrix of vx(4*96), vy(4*96). EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 37

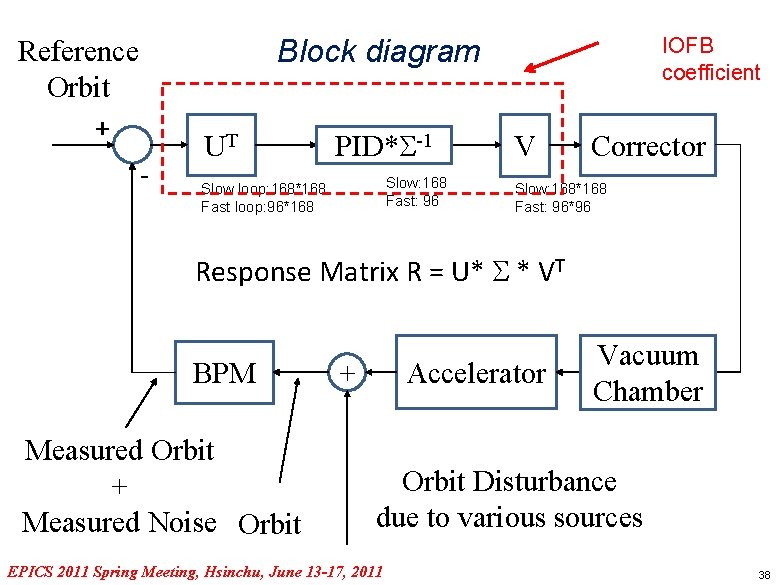

Block diagram Reference Orbit + - UT PID*S-1 Slow: 168 Fast: 96 Slow loop: 168*168 Fast loop: 96*168 IOFB coefficient V Corrector Slow: 168*168 Fast: 96*96 Response Matrix R = U* S * VT BPM Measured Orbit + Measured Noise Orbit Accelerator + Vacuum Chamber Orbit Disturbance due to various sources EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 38

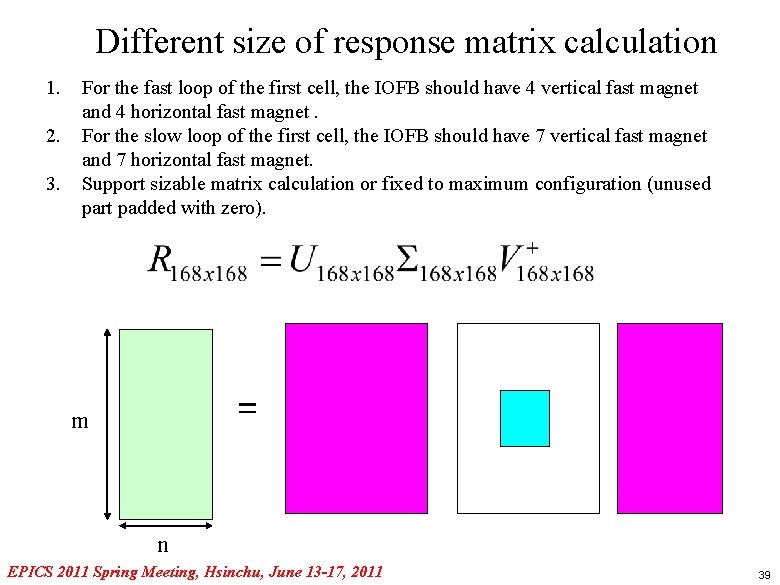

Different size of response matrix calculation 1. 2. 3. For the fast loop of the first cell, the IOFB should have 4 vertical fast magnet and 4 horizontal fast magnet. For the slow loop of the first cell, the IOFB should have 7 vertical fast magnet and 7 horizontal fast magnet. Support sizable matrix calculation or fixed to maximum configuration (unused part padded with zero). = m n EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 39

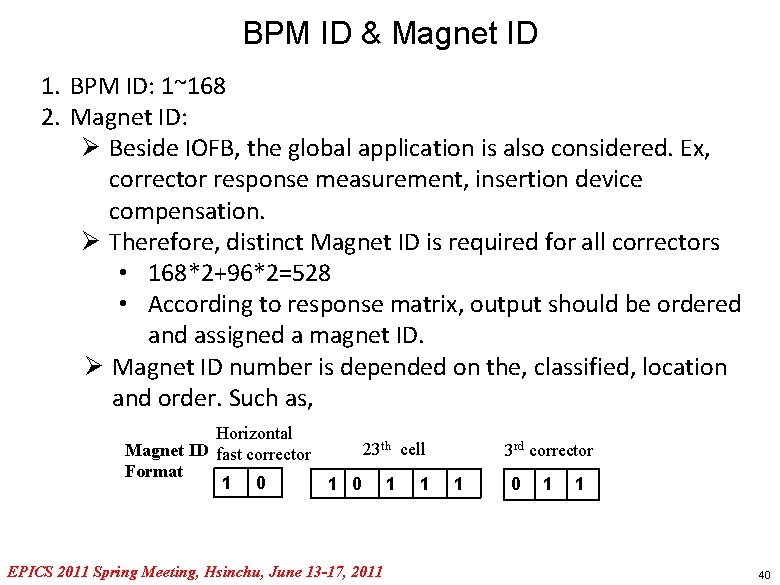

BPM ID & Magnet ID 1. BPM ID: 1~168 2. Magnet ID: Ø Beside IOFB, the global application is also considered. Ex, corrector response measurement, insertion device compensation. Ø Therefore, distinct Magnet ID is required for all correctors • 168*2+96*2=528 • According to response matrix, output should be ordered and assigned a magnet ID. Ø Magnet ID number is depended on the, classified, location and order. Such as, Horizontal 23 th cell Magnet ID fast corrector Format 1 0 1 1 EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 3 rd corrector 1 0 1 1 40

Summary Ø Ø Overview of TPS power supply control Feedback system infrastructure. BPM and corrector interface. Corrector power supply controller (CPSC) were contracted to D-Tacq. Ø I-Tech award the contract of BPM platforms. Ø Specifications for integrated orbit feedback (IOFB) FPGA modules are still on going. Ø Communication between CPSC and IOFB modules are in proceed now. EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011 41

Thanks for Your Attention! EPICS 2011 Spring Meeting, Hsinchu, June 13 -17, 2011

- Slides: 42