Power Distribution Peter W Phillips STFC Rutherford Appleton

Power Distribution Peter W Phillips STFC Rutherford Appleton Laboratory ECFA HL-LHC Workshop, Aix-les-Bains, 1 -3 October 2013

Abstract The power distribution systems of the LHC experiments use a number of stages to convert power from the 50 Hz mains grid to the voltages needed by the front end systems. In many cases a final linear regulation step takes place in the front end system, but in other cases this step takes place off-detector, presenting challenges in terms of stability as remote sensing must be used to maintain the correct voltage at the point of load. In any event, resistive losses in the power cables are often of a similar magnitude to the delivered power. Considering the low voltages and high currents needed by contemporary front end designs, reduced tolerance to over-voltage events and the increased channel counts in some of the proposed detector systems, it is clear that new power distribution strategies are required. Two alternate powering schemes are being studied with a view to HL-LHC: DC-DC Conversion and Serial Powering. Radiation hard DC-DC converters with air-core inductors have been designed and built, as have the circuit blocks needed to operate a chain of serially connected detector modules, and both schemes have been shown to perform well in small-scale system tests. In addition, switched capacitor DC-DC converters have been demonstrated to be a viable, high efficiency alternative to on-chip linear regulators. The status of this work shall be shown and the merits and drawbacks of each scheme outlined. The directions of future development shall be described, as required to deliver reliable, low-mass powering solutions on an appropriate timescale. Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 2

Outline • Power Distribution at LHC – Individual Powering – Parallel Powering – Motivations for change • Serial Powering – Switched Capacitor • Concept • Examples • HV Multiplexing • Conclusions – Concept – Examples • DC-DC Point of Load – Buck Converter • Concept • Examples Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 3

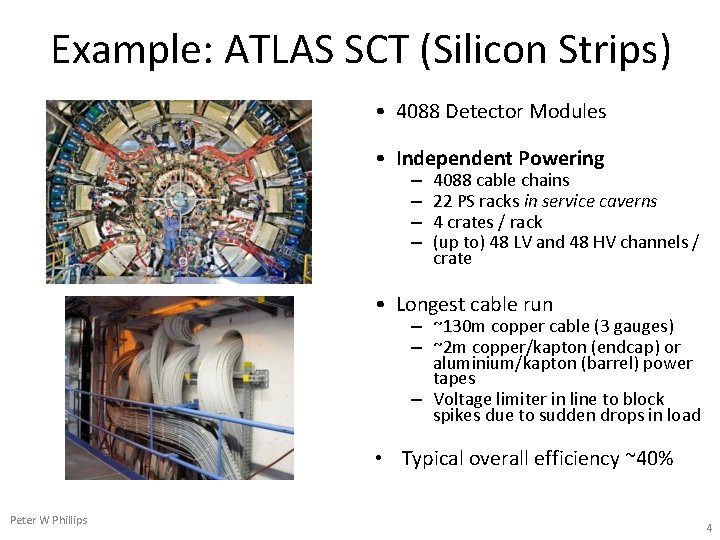

Example: ATLAS SCT (Silicon Strips) • 4088 Detector Modules • Independent Powering – – 4088 cable chains 22 PS racks in service caverns 4 crates / rack (up to) 48 LV and 48 HV channels / crate • Longest cable run – ~130 m copper cable (3 gauges) – ~2 m copper/kapton (endcap) or aluminium/kapton (barrel) power tapes – Voltage limiter in line to block spikes due to sudden drops in load • Typical overall efficiency ~40% Peter W Phillips 4

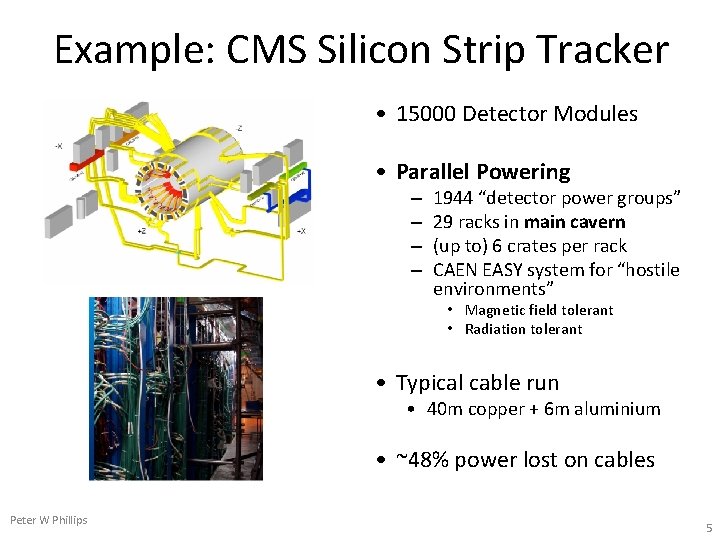

Example: CMS Silicon Strip Tracker • 15000 Detector Modules • Parallel Powering – – 1944 “detector power groups” 29 racks in main cavern (up to) 6 crates per rack CAEN EASY system for “hostile environments” • Magnetic field tolerant • Radiation tolerant • Typical cable run • 40 m copper + 6 m aluminium • ~48% power lost on cables Peter W Phillips 5

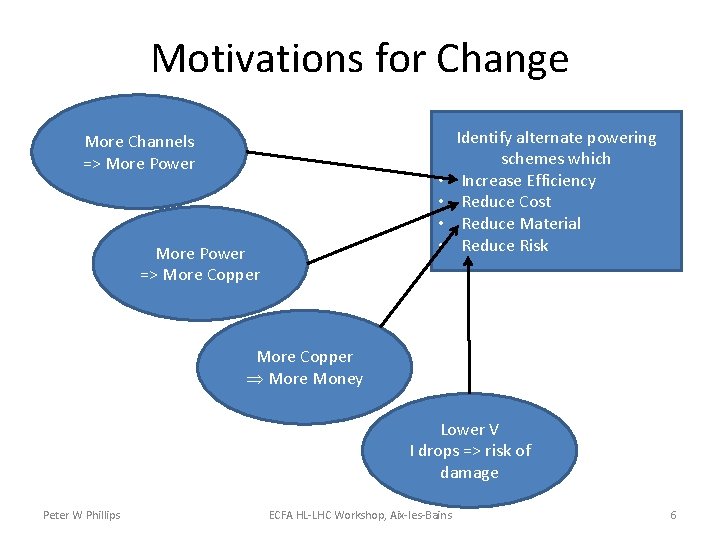

Motivations for Change More Channels => More Power • • More Power => More Copper Identify alternate powering schemes which Increase Efficiency Reduce Cost Reduce Material Reduce Risk More Copper Þ More Money Lower V I drops => risk of damage Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 6

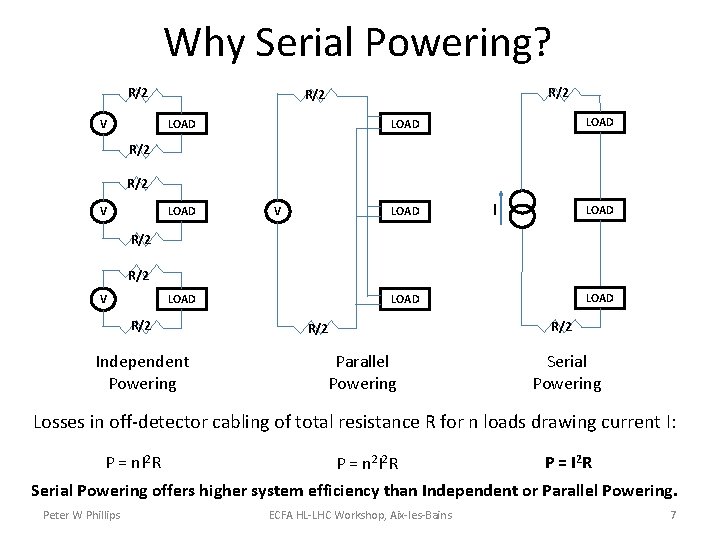

Why Serial Powering? R/2 V R/2 LOAD R/2 V LOAD I LOAD R/2 V LOAD R/2 Independent Powering LOAD R/2 Parallel Powering Serial Powering Losses in off-detector cabling of total resistance R for n loads drawing current I: P = n. I 2 R P = n 2 I 2 R P = I 2 R Serial Powering offers higher system efficiency than Independent or Parallel Powering. Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 7

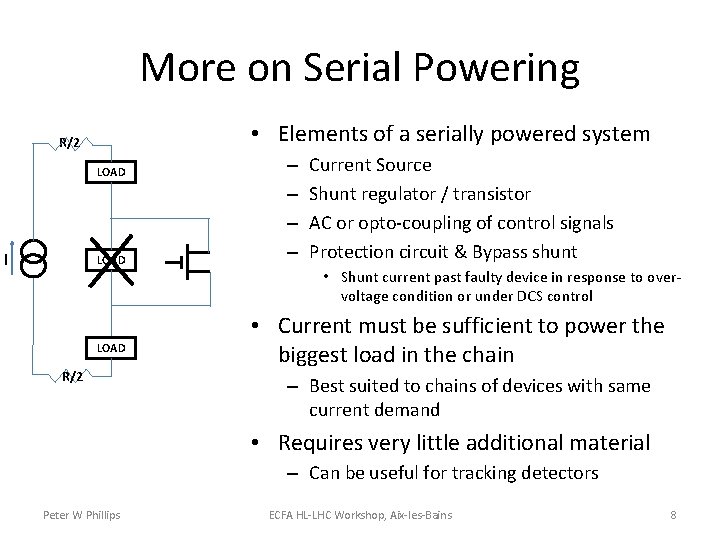

More on Serial Powering • Elements of a serially powered system R/2 LOAD I LOAD R/2 – – Current Source Shunt regulator / transistor AC or opto-coupling of control signals Protection circuit & Bypass shunt • Shunt current past faulty device in response to overvoltage condition or under DCS control • Current must be sufficient to power the biggest load in the chain – Best suited to chains of devices with same current demand • Requires very little additional material – Can be useful for tracking detectors Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 8

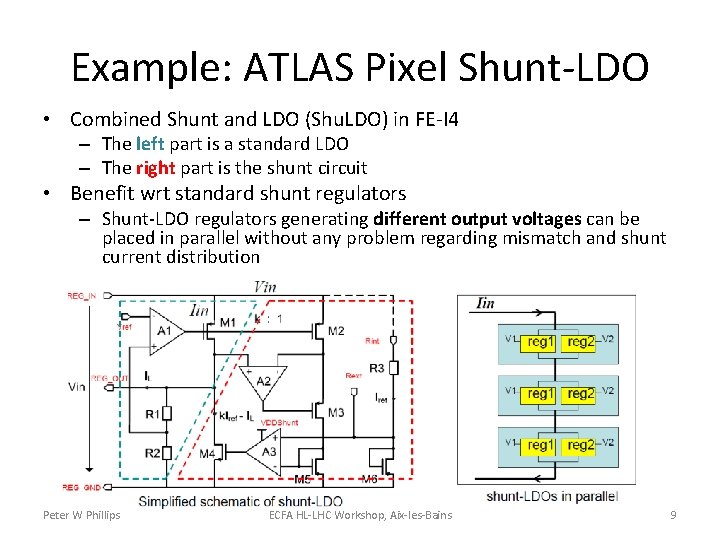

Example: ATLAS Pixel Shunt-LDO • Combined Shunt and LDO (Shu. LDO) in FE-I 4 – The left part is a standard LDO – The right part is the shunt circuit • Benefit wrt standard shunt regulators – Shunt-LDO regulators generating different output voltages can be placed in parallel without any problem regarding mismatch and shunt current distribution Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 9

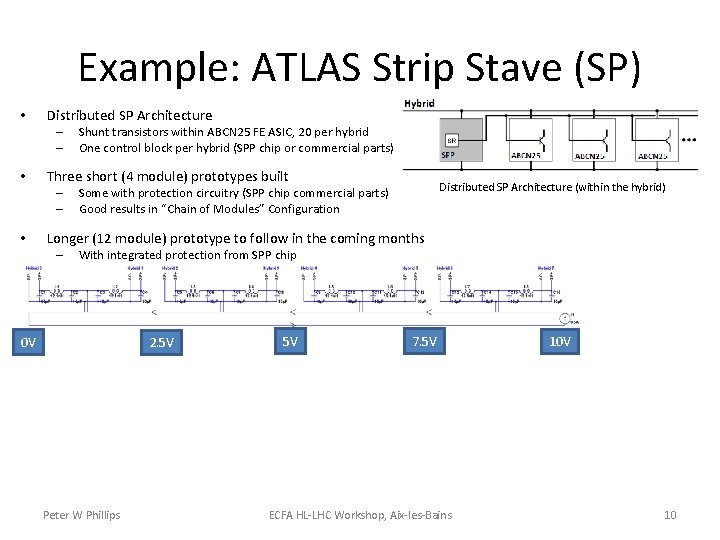

Example: ATLAS Strip Stave (SP) • Distributed SP Architecture – – • Three short (4 module) prototypes built – – • Shunt transistors within ABCN 25 FE ASIC, 20 per hybrid One control block per hybrid (SPP chip or commercial parts) Distributed SP Architecture (within the hybrid) Some with protection circuitry (SPP chip commercial parts) Good results in “Chain of Modules” Configuration Longer (12 module) prototype to follow in the coming months – With integrated protection from SPP chip 0 V 2. 5 V Peter W Phillips 5 V 7. 5 V ECFA HL-LHC Workshop, Aix-les-Bains 10 V 10

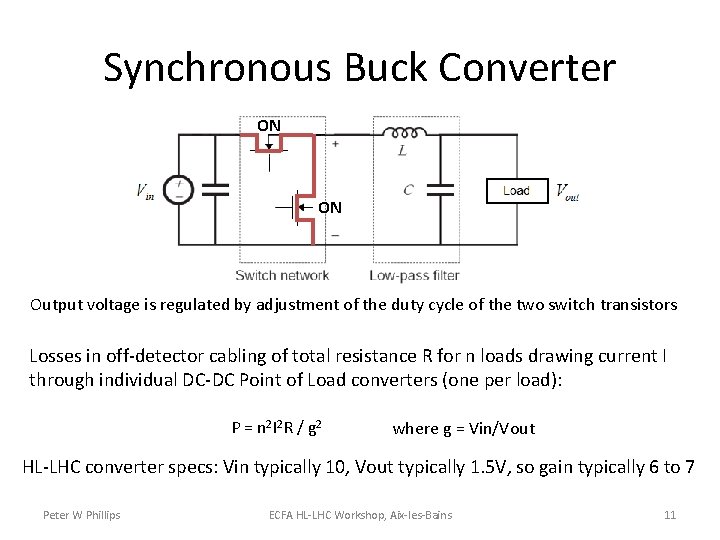

Synchronous Buck Converter ON ON Output voltage is regulated by adjustment of the duty cycle of the two switch transistors Losses in off-detector cabling of total resistance R for n loads drawing current I through individual DC-DC Point of Load converters (one per load): P = n 2 I 2 R / g 2 where g = Vin/Vout HL-LHC converter specs: Vin typically 10, Vout typically 1. 5 V, so gain typically 6 to 7 Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 11

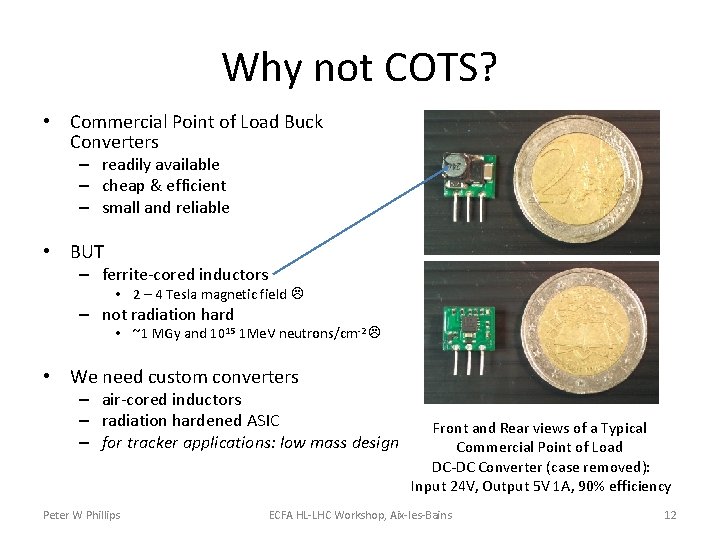

Why not COTS? • Commercial Point of Load Buck Converters – readily available – cheap & efficient – small and reliable • BUT – ferrite-cored inductors • 2 – 4 Tesla magnetic field – not radiation hard • ~1 MGy and 1015 1 Me. V neutrons/cm-2 • We need custom converters – air-cored inductors – radiation hardened ASIC – for tracker applications: low mass design Peter W Phillips Front and Rear views of a Typical Commercial Point of Load DC-DC Converter (case removed): Input 24 V, Output 5 V 1 A, 90% efficiency ECFA HL-LHC Workshop, Aix-les-Bains 12

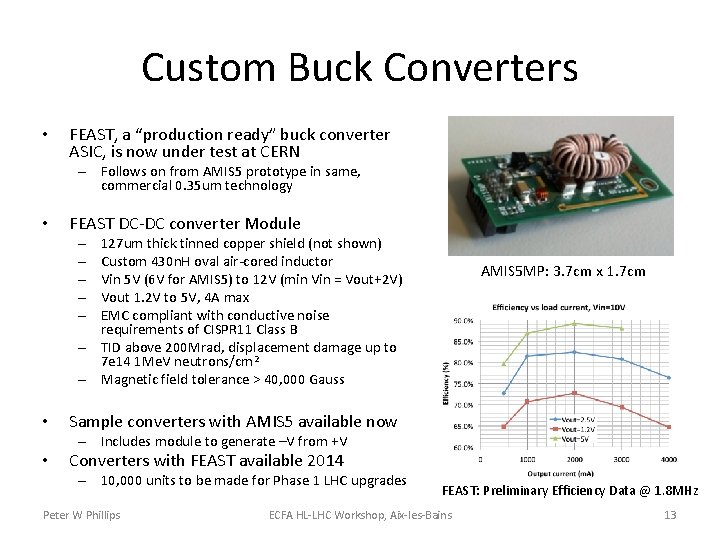

Custom Buck Converters • FEAST, a “production ready” buck converter ASIC, is now under test at CERN – Follows on from AMIS 5 prototype in same, commercial 0. 35 um technology • FEAST DC-DC converter Module 127 um thick tinned copper shield (not shown) Custom 430 n. H oval air-cored inductor Vin 5 V (6 V for AMIS 5) to 12 V (min Vin = Vout+2 V) Vout 1. 2 V to 5 V, 4 A max EMC compliant with conductive noise requirements of CISPR 11 Class B – TID above 200 Mrad, displacement damage up to 7 e 14 1 Me. V neutrons/cm 2 – Magnetic field tolerance > 40, 000 Gauss – – – • AMIS 5 MP: 3. 7 cm x 1. 7 cm Sample converters with AMIS 5 available now – Includes module to generate –V from +V • Converters with FEAST available 2014 – 10, 000 units to be made for Phase 1 LHC upgrades Peter W Phillips FEAST: Preliminary Efficiency Data @ 1. 8 MHz ECFA HL-LHC Workshop, Aix-les-Bains 13

Example: Phase 1 Calorimeter • Information to follow from Federico Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 14

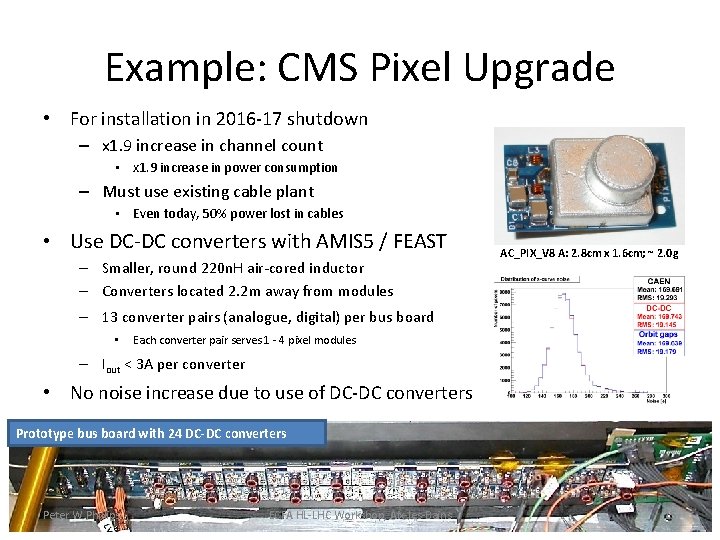

Example: CMS Pixel Upgrade • For installation in 2016 -17 shutdown – x 1. 9 increase in channel count • x 1. 9 increase in power consumption – Must use existing cable plant • Even today, 50% power lost in cables • Use DC-DC converters with AMIS 5 / FEAST – Smaller, round 220 n. H air-cored inductor – Converters located 2. 2 m away from modules AC_PIX_V 8 A: 2. 8 cm x 1. 6 cm; ~ 2. 0 g – 13 converter pairs (analogue, digital) per bus board • Each converter pair serves 1 - 4 pixel modules – Iout < 3 A per converter • No noise increase due to use of DC-DC converters Prototype bus board with 24 DC-DC converters Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 15

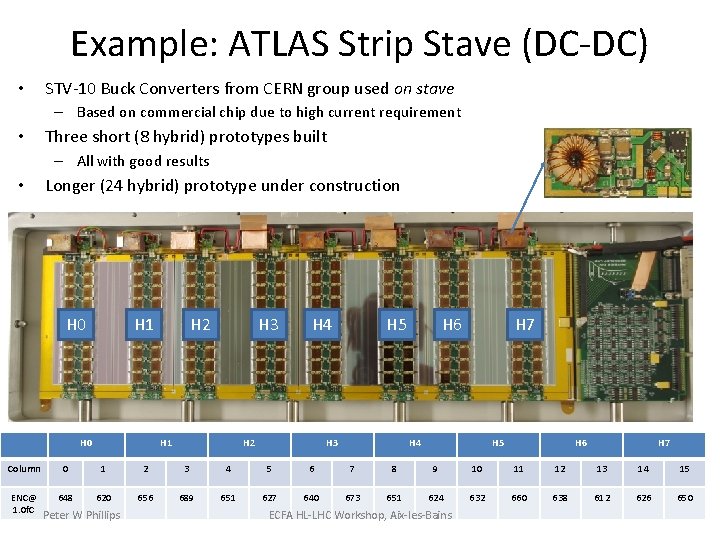

Example: ATLAS Strip Stave (DC-DC) • STV-10 Buck Converters from CERN group used on stave – Based on commercial chip due to high current requirement • Three short (8 hybrid) prototypes built – All with good results • Longer (24 hybrid) prototype under construction H 0 H 1 H 0 H 2 H 3 H 1 H 4 H 2 H 5 H 3 H 6 H 7 H 4 H 5 H 6 H 7 Column 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 ENC@ 1. 0 f. C 648 620 656 689 651 627 640 673 651 624 632 660 638 612 626 650 Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 16

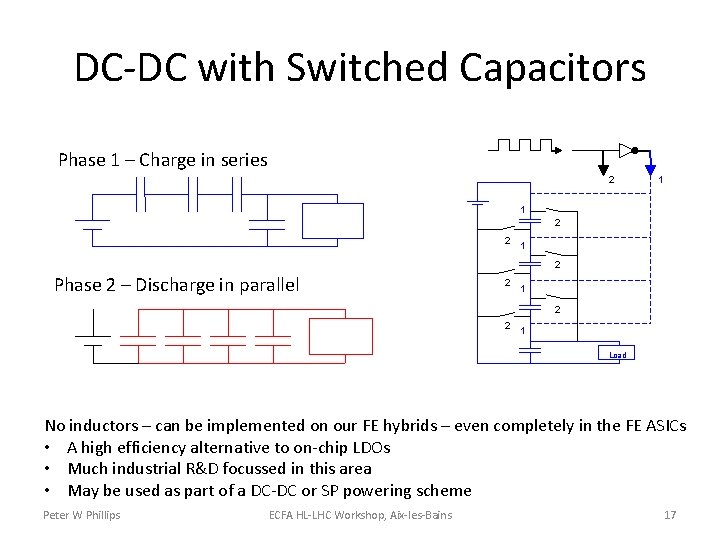

DC-DC with Switched Capacitors Phase 1 – Charge in series 2 1 1 2 2 1 2 Phase 2 – Discharge in parallel 2 1 2 2 1 Load No inductors – can be implemented on our FE hybrids – even completely in the FE ASICs • A high efficiency alternative to on-chip LDOs • Much industrial R&D focussed in this area • May be used as part of a DC-DC or SP powering scheme Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 17

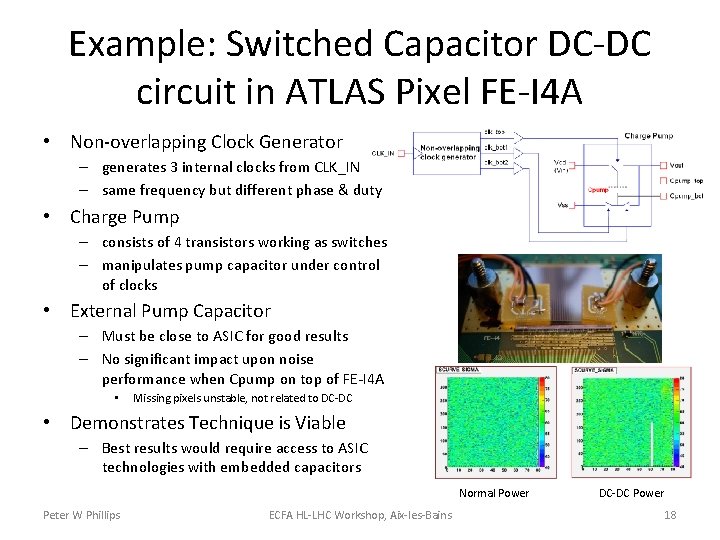

Example: Switched Capacitor DC-DC circuit in ATLAS Pixel FE-I 4 A • Non-overlapping Clock Generator – generates 3 internal clocks from CLK_IN – same frequency but different phase & duty • Charge Pump – consists of 4 transistors working as switches – manipulates pump capacitor under control of clocks • External Pump Capacitor – Must be close to ASIC for good results – No significant impact upon noise performance when Cpump on top of FE-I 4 A • Missing pixels unstable, not related to DC-DC • Demonstrates Technique is Viable – Best results would require access to ASIC technologies with embedded capacitors Normal Power Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains DC-DC Power 18

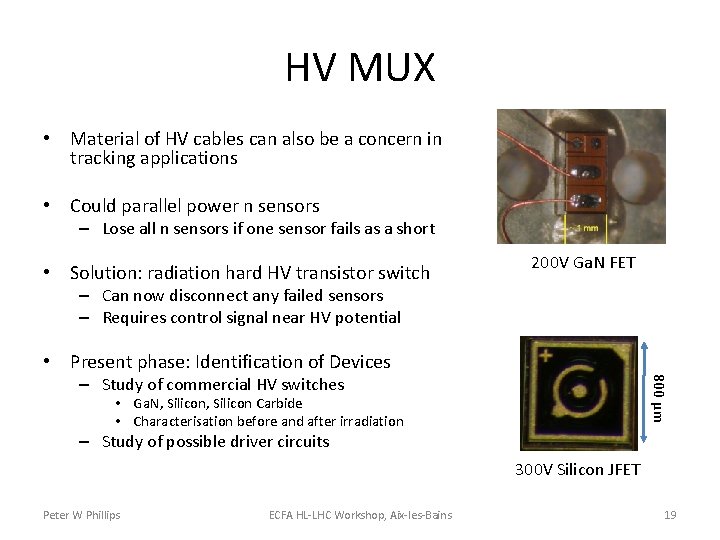

HV MUX • Material of HV cables can also be a concern in tracking applications • Could parallel power n sensors – Lose all n sensors if one sensor fails as a short • Solution: radiation hard HV transistor switch 200 V Ga. N FET – Can now disconnect any failed sensors – Requires control signal near HV potential • Present phase: Identification of Devices 800 μm – Study of commercial HV switches • Ga. N, Silicon Carbide • Characterisation before and after irradiation – Study of possible driver circuits 300 V Silicon JFET Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 19

Conclusions • Two main power strategies being explored for HL-LHC – SP circuit blocks built, small scale system tests give encouraging results – Radiation hard, air cored DC-DC converters have been demonstrated • In addition – Switched capacitor DC-DC conversion is a viable, high efficiency alternative to on-chip LDO regulators – Risks associated with parallel sensor biasing can be eliminated if suitable HV switch transistors can be identified • Continued support needed to deliver suitable parts in time for HL-LHC Peter W Phillips ECFA HL-LHC Workshop, Aix-les-Bains 20

- Slides: 20