Power Delivery Network Optimization for Low Power So

- Slides: 11

Power Delivery Network Optimization for Low Power So. C Anil Gundurao Melinda Yang Eileen You Harpreet Gill System LSI So. C Bay Area R&D Samsung Semiconductor Inc.

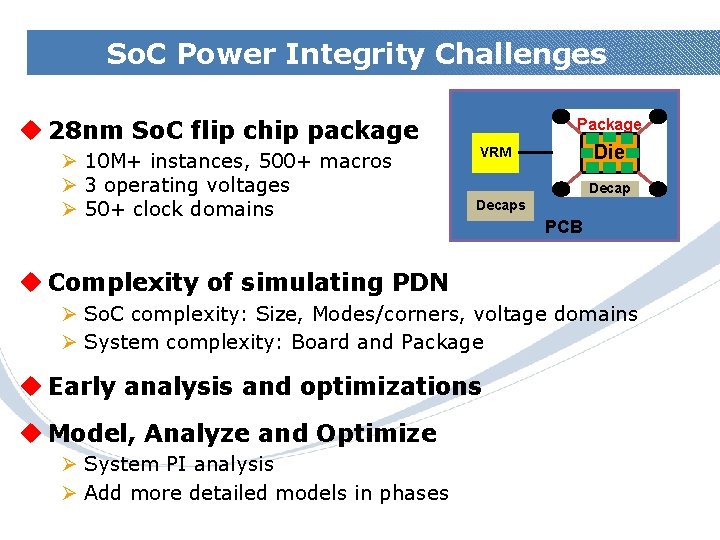

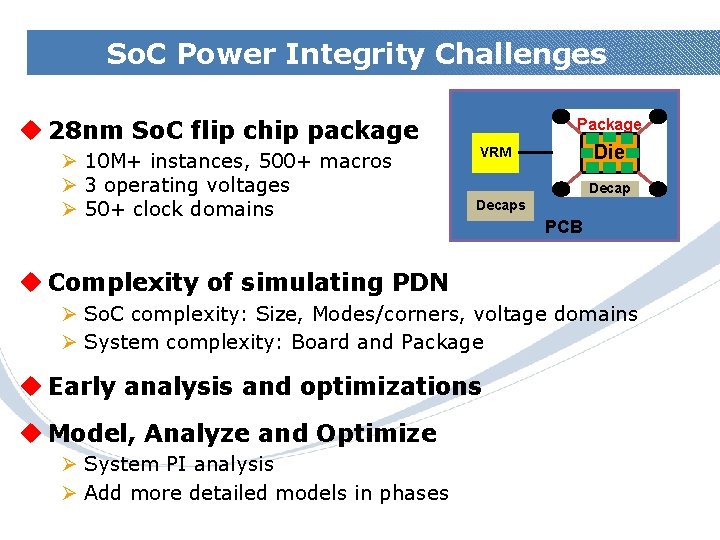

So. C Power Integrity Challenges u 28 nm So. C flip chip package Ø 10 M+ instances, 500+ macros Ø 3 operating voltages Ø 50+ clock domains Package Die VRM Decaps PCB u Complexity of simulating PDN Ø So. C complexity: Size, Modes/corners, voltage domains Ø System complexity: Board and Package u Early analysis and optimizations u Model, Analyze and Optimize Ø System PI analysis Ø Add more detailed models in phases Samsung Confidential

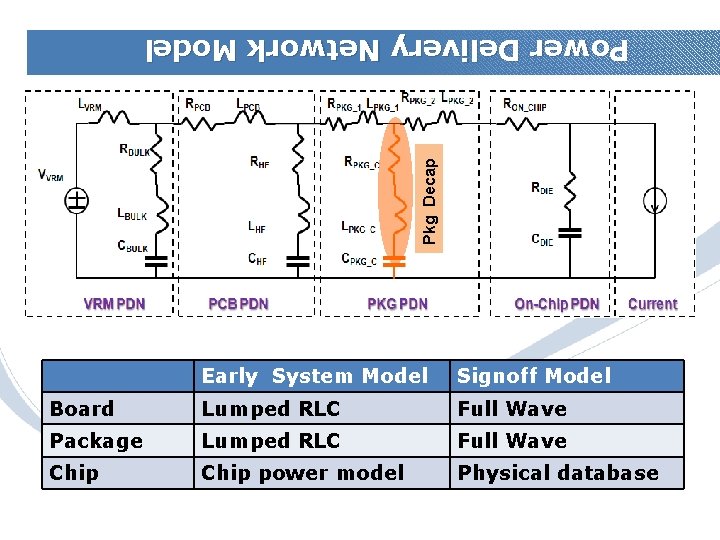

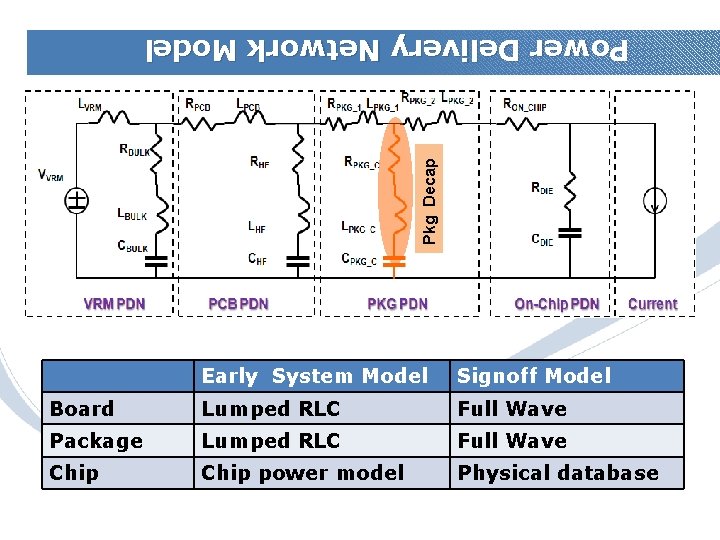

Pkg Decap Power Delivery Network Model Early System Model Signoff Model Board Lumped RLC Full Wave Package Lumped RLC Full Wave Chip power model Physical database Samsung Confidential

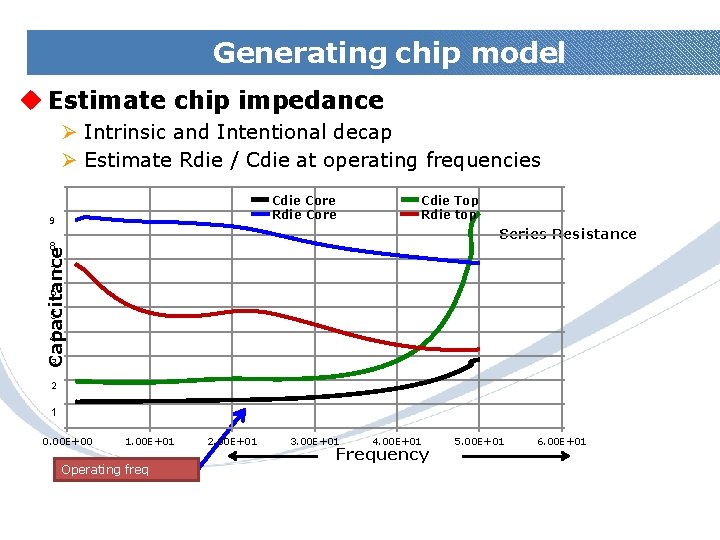

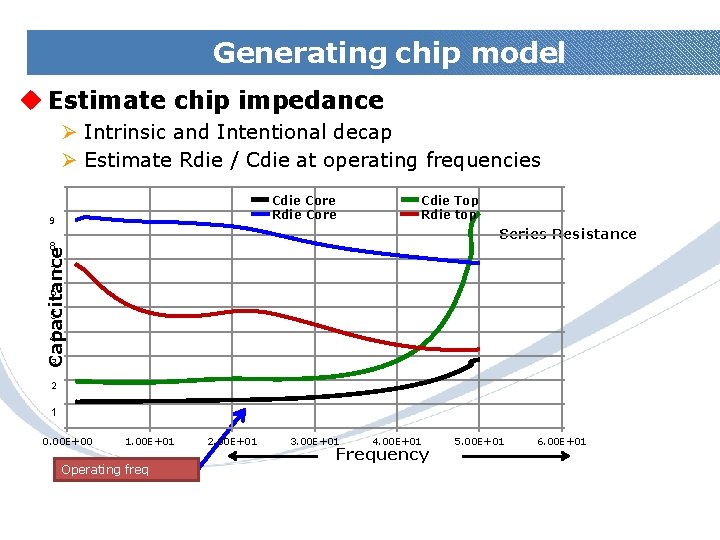

Generating chip model u Estimate chip impedance Ø Intrinsic and Intentional decap Ø Estimate Rdie / Cdie at operating frequencies Cdie Core Rdie Core 9 Cdie Top Rdie top Series Resistance Capacitance 8 7 6 5 4 3 2 1 0. 00 E+00 1. 00 E+01 Operating freq 2. 00 E+01 3. 00 E+01 4. 00 E+01 Frequency Samsung Confidential 5. 00 E+01 6. 00 E+01

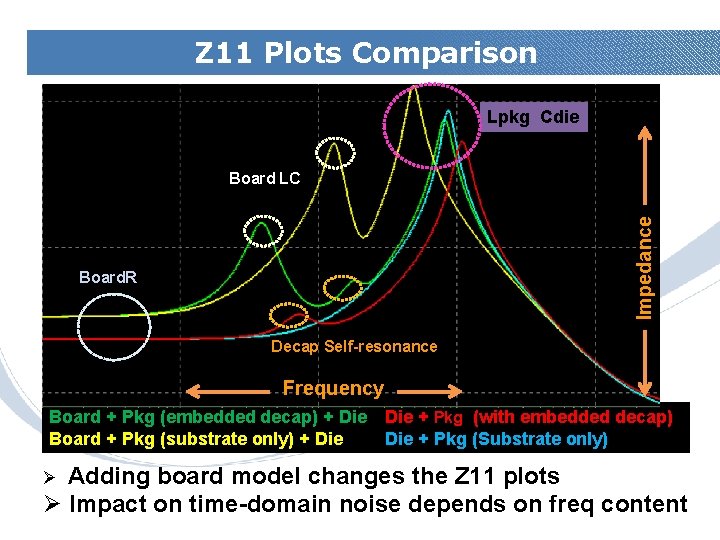

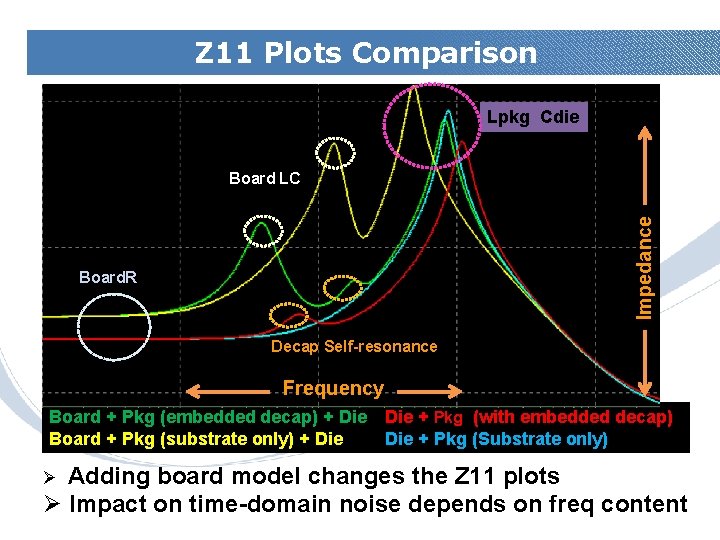

Z 11 Plots Comparison Lpkg Cdie Impedance Board LC Board. R Decap Self-resonance Frequency Board + Pkg (embedded decap) + Die Board + Pkg (substrate only) + Die + Pkg (with embedded decap) Die + Pkg (Substrate only) Adding board model changes the Z 11 plots Ø Impact on time-domain noise depends on freq content Ø Samsung Confidential

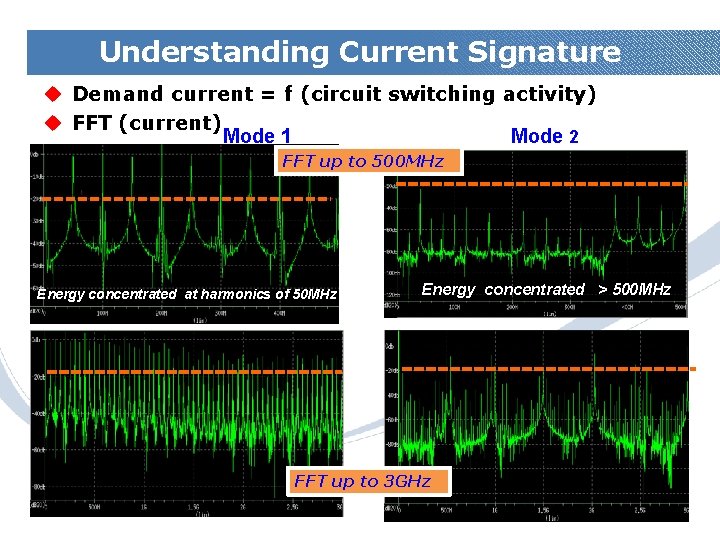

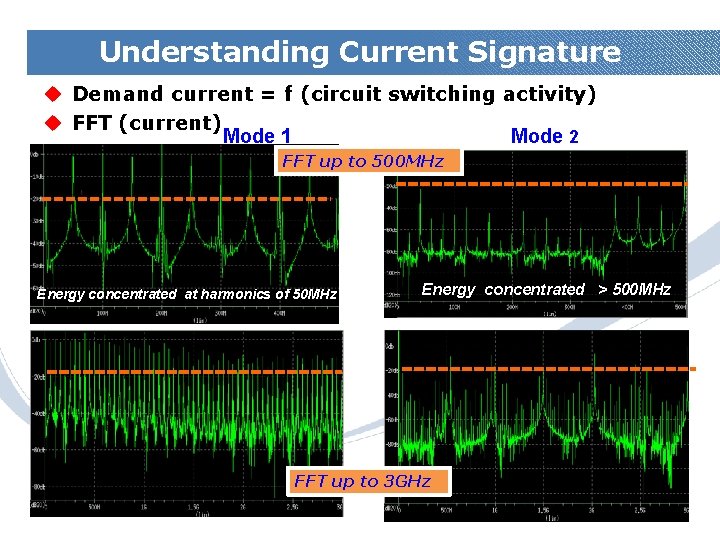

Understanding Current Signature u Demand current = f (circuit switching activity) u FFT (current) Mode 1 Mode 2 FFT up to 500 MHz Energy concentrated at harmonics of 50 MHz Energy concentrated > 500 MHz FFT up to 3 GHz Samsung Confidential

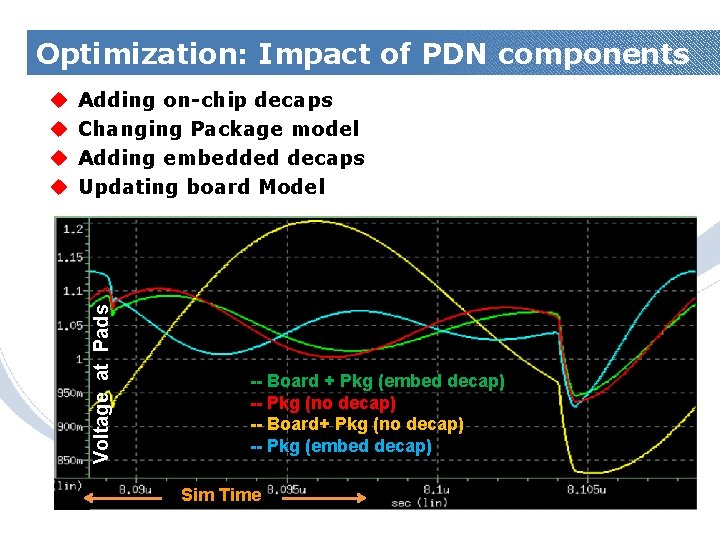

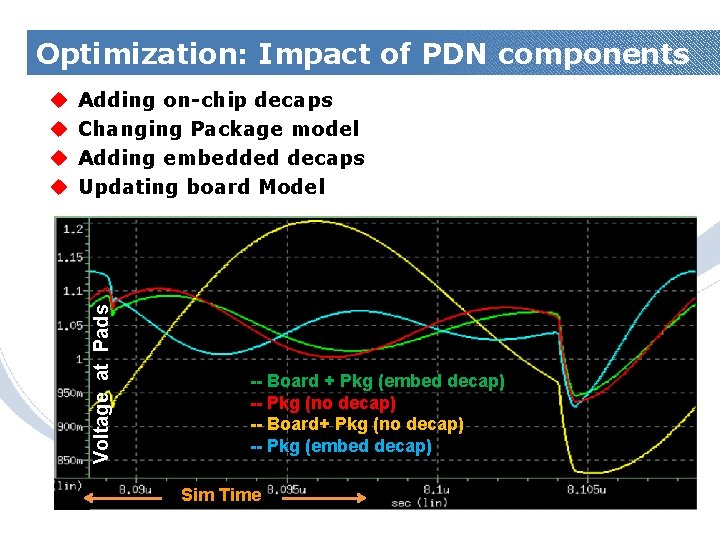

Optimization: Impact of PDN components Adding on-chip decaps Changing Package model Adding embedded decaps Updating board Model Voltage at Pads u u -- Board + Pkg (embed decap) -- Pkg (no decap) -- Board+ Pkg (no decap) -- Pkg (embed decap) Sim Time Samsung Confidential

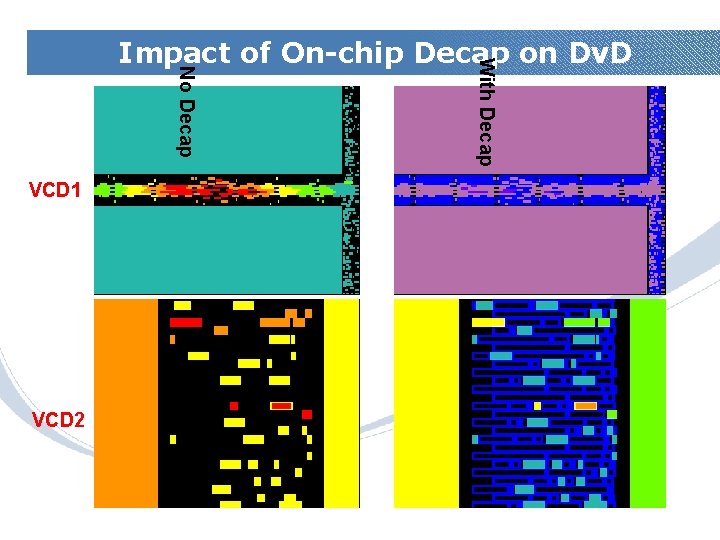

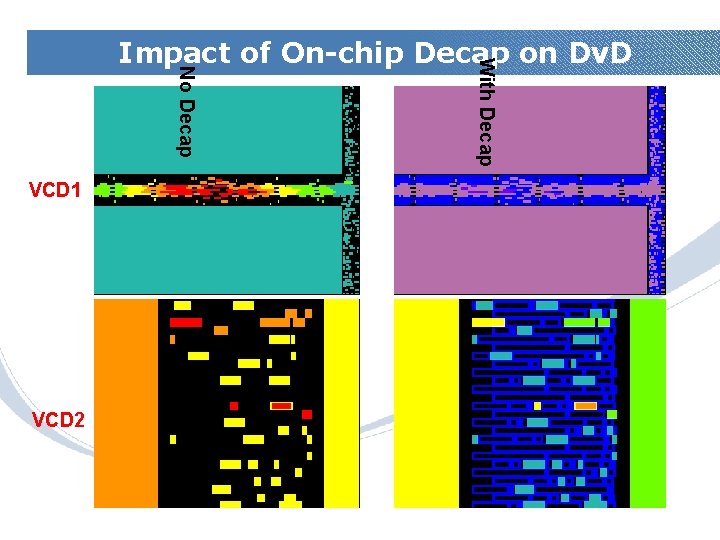

No Decap With Decap Impact of On-chip Decap on Dv. D VCD 1 VCD 2 Samsung Confidential

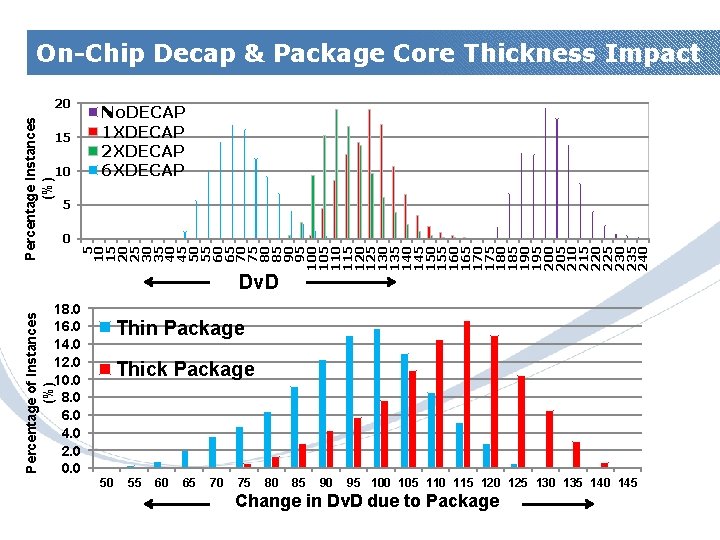

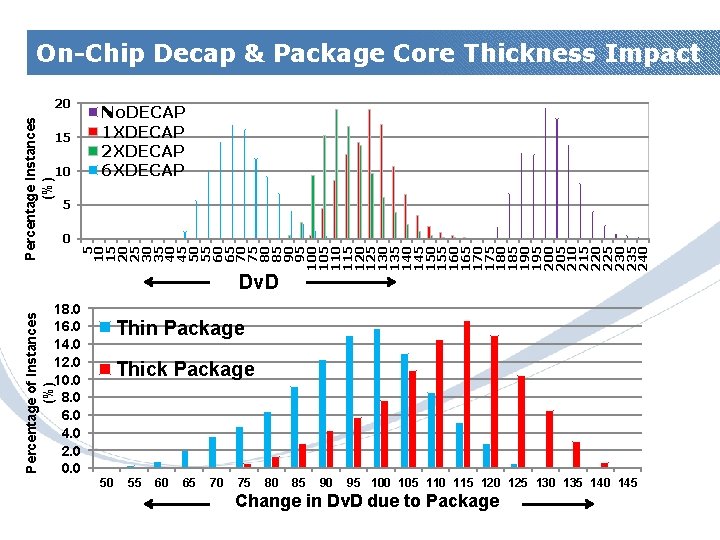

On-Chip Decap & Package Core Thickness Impact Percentage Instances (%) 20 No. DECAP 1 XDECAP 2 XDECAP 6 XDECAP 15 10 5 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 85 90 95 100 105 110 115 120 125 130 135 140 145 150 155 160 165 170 175 180 185 190 195 200 205 210 215 220 225 230 235 240 0 Dv. D Percentage of Instances (%) 18. 0 16. 0 14. 0 12. 0 10. 0 8. 0 6. 0 4. 0 2. 0 0. 0 Thin Package Thick Package 50 55 60 65 70 75 80 85 90 95 100 105 110 115 120 125 130 135 140 145 Change in Dv. D due to Package Samsung Confidential

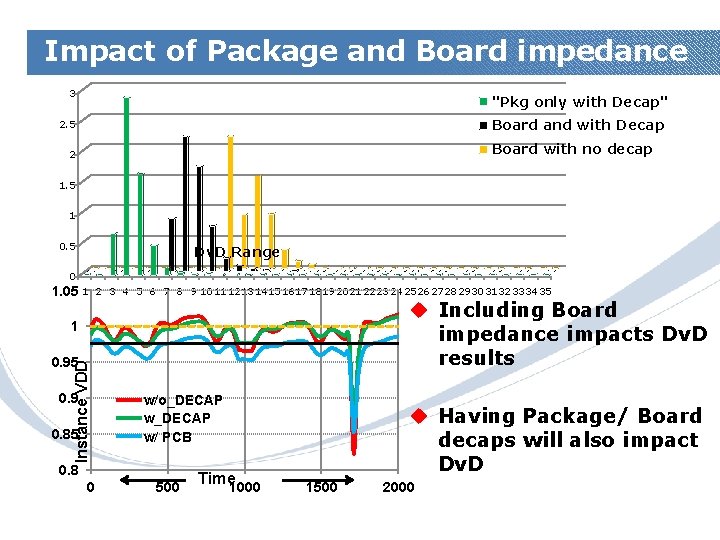

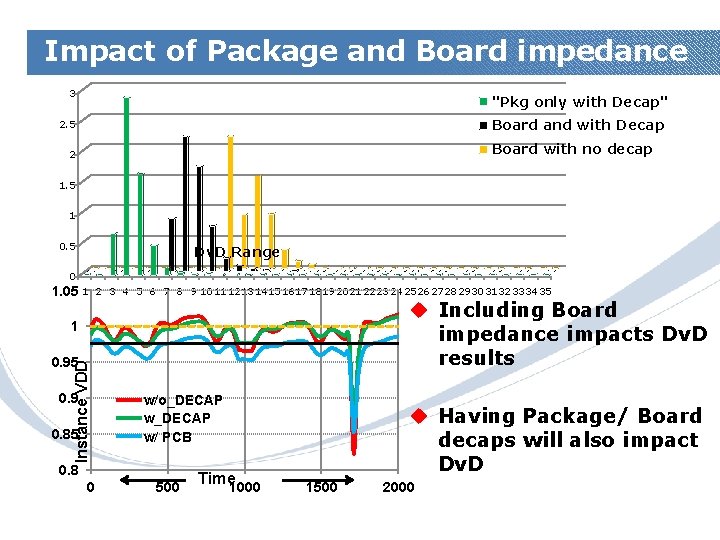

Impact of Package and Board impedance 3 "Pkg only with Decap" Board and with Decap 2. 5 Board with no decap 2 1. 5 1 0. 5 Dv. D Range 0 1. 05 1 2 3 4 5 6 7 8 9 10 11 1213 1415 1617 1819 2021 2223 24 2526 2728 2930 3132 3334 35 u Including Board impedance impacts Dv. D results 1 Instance VDD 0. 95 0. 9 0. 85 w/o_DECAP w/ PCB 0. 8 0 500 Time 1000 u Having Package/ Board decaps will also impact Dv. D 1500 2000 Samsung Confidential

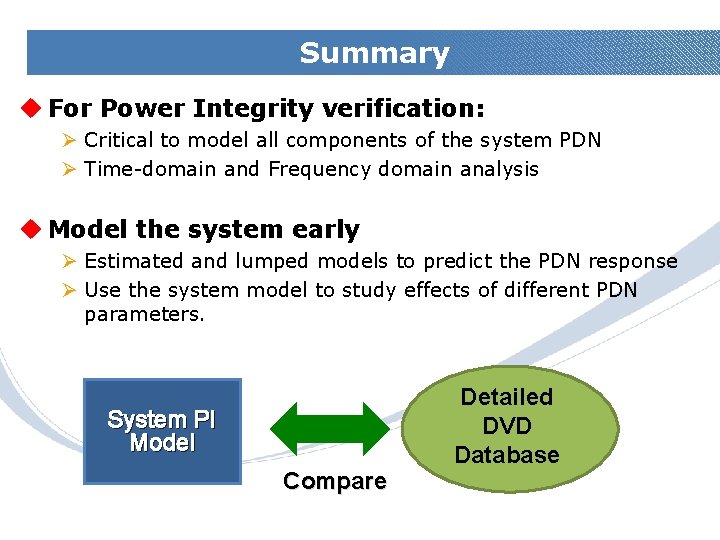

Summary u For Power Integrity verification: Ø Critical to model all components of the system PDN Ø Time-domain and Frequency domain analysis u Model the system early Ø Estimated and lumped models to predict the PDN response Ø Use the system model to study effects of different PDN parameters. System PI Model Compare Samsung Confidential Detailed DVD Database