Power and Complexity Aware Microarchitectures Jaume Abella 1

Power and Complexity Aware Microarchitectures Jaume Abella 1 jabella@ac. upc. es http: //people. ac. upc. es/jabella Ramon Canal 1 rcanal@ac. upc. es http: //people. ac. upc. es/rcanal Antonio González 1, 2 antonio@ac. upc. es http: //people. ac. upc. es/antonio 1 Computer Architecture Dept. UPC-Barcelona UPC 2 Intel Barcelona Research Center Intel Labs – UPC, Barcelona

Issue Logic (I) n Adaptative IQ l Resize dynamically the ROB and issue queue according to their occupancy “Power-Aware Adaptive Issue Queue and Register File”, Hi. PC 2003 n Dependence Based IQ l Keep direct relationships between producer and consumer “ A Low Complexity Issue Logic”, ICS 2000 n Prescheduling IQ l UPC Schedule instruction issue according to the latencies of functional units “Reducing the Complexity of the Issue Logic”, ICS 2001

Issue Logic (II) n FP distributed issue queue without CAM cells l Dispatch – Instructions belonging to a dependence chain are sent to the same queue – Multiple dependence chains may share a queue l Issue – Small table keeps track of how many cycles has to wait the first instruction of a chain to be issued – First, select the oldest instruction that will become ready next cycle. Second, the oldest ready instruction UPC “Low-Complexity Distributed Issue Queue”, HPCA 2004

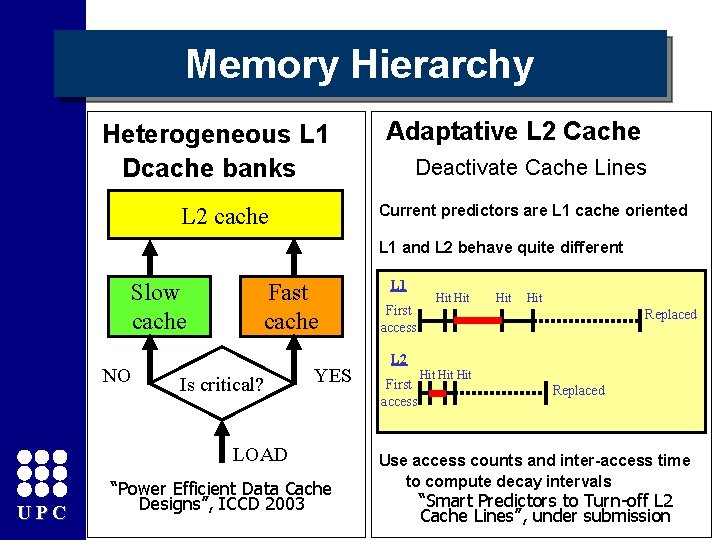

Memory Hierarchy Heterogeneous L 1 Dcache banks Adaptative L 2 Cache Deactivate Cache Lines Current predictors are L 1 cache oriented L 2 cache L 1 and L 2 behave quite different Slow cache NO Fast cache Is critical? YES LOAD UPC “Power Efficient Data Cache Designs”, ICCD 2003 L 1 First access Hit Hit Replaced L 2 First access Hit Hit Replaced Use access counts and inter-access time to compute decay intervals “Smart Predictors to Turn-off L 2 Cache Lines”, under submission

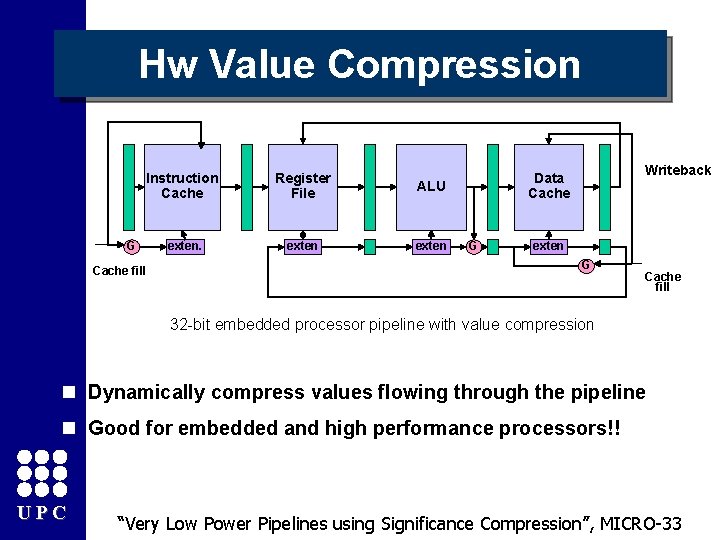

Hw Value Compression Instruction Cache Register File ALU exten G Cache fill Writeback Data Cache G exten G Cache fill 32 -bit embedded processor pipeline with value compression n Dynamically compress values flowing through the pipeline n Good for embedded and high performance processors!! UPC “Very Low Power Pipelines using Significance Compression”, MICRO-33

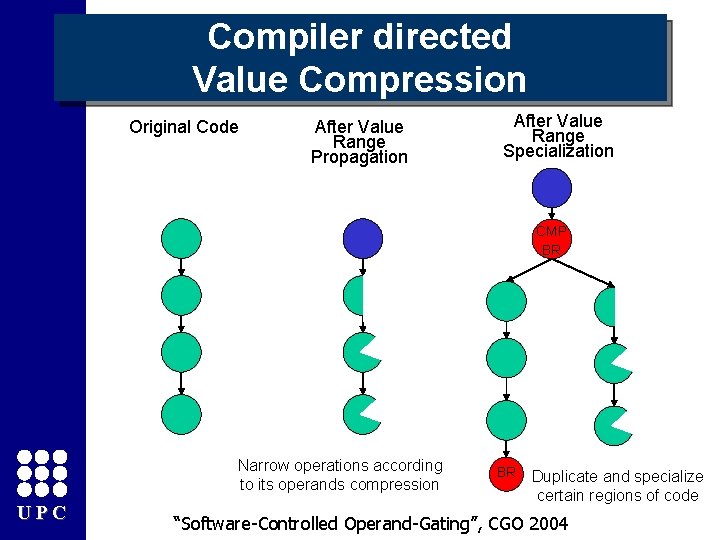

Compiler directed Value Compression Original Code After Value Range Propagation After Value Range Specialization CMP BR Narrow operations according to its operands compression UPC BR Duplicate and specialize certain regions of code “Software-Controlled Operand-Gating”, CGO 2004

- Slides: 6